Interfacing Dolphin to an External System Microcontroller (Rev. B)

Texas InstrumentsThis application note discusses the hardware and firmware implementation details of interfacing an external system (application) microcontroller to the Dolphin chipset. The system microcontroller performs all the application and system level tasks and is needed to set up the operation of the Dolphin chipset.

Texas Instruments has developed evaluation software that interfaces to the Dolphin chipset through hardware UART interface of the DBB03A digital baseband ASIC. However in real end applications, an external system microcontroller is needed to emulate the features of the Dolphin evaluation software. This evaluation software was purely developed for demo purposes. Any catalog low-cost microcontroller can be interfaced to the Dolphin chipset as long as they follow the Dolphin host interface protocol (SWRA043) for communication.

Texas Instruments recommends its ultra-low power MSP430 series of microcontrollers to interface with Dolphin. Specifically the firmware in this application note was developed for MSP430F1121A microcontroller.

TMS320DM365 to TMS320DM368 Migration Guide

Texas InstrumentsAN-1614 LM48510 Speaker AN- (Rev. B)

Texas InstrumentsUsing the TPS62125 in an Inverting Buck-Boost Topology (Rev. B)

Texas InstrumentsThe TPS62125 is a DCS-Control™ topology synchronous buck dc-to-dc converter designed for low-power applications. It features a wide operating input voltage range from 3 V to 17 V, 300-mA output current, and adjustable output voltage of 1.2 V to 10 V. This device is well-suited for applications such as ultra lowpower microprocessors, energy harvesting, and low-power RF applications. Moreover, the TPS62125 can be configured in an inverting buck-boost topology, where the output voltage is inverted or negative with respect to ground. This application note describes the TPS62125 in an inverting buck-boost topology for use in low current negative rails for operational amplifier or optical module biasing and other low-power applications.

A Real Time Speech Subband Coder Using the TMS32010 ( Contains Scanned Text)

Texas InstrumentsUsing the TMS320C6474 Antenna Interface (AIF) for Inter-DSP Communication

Texas InstrumentsPowering the TMS320DM365 using the TPS650061

Texas InstrumentsStellaris DCDC Converter Reference Design

Texas InstrumentsTMS320DM6467 SoC Architecture and Throughput Overview (Rev. B)

Texas InstrumentsAN-300 Simple Circuit Detects Loss of 4-20 mA Signal (Rev. B)

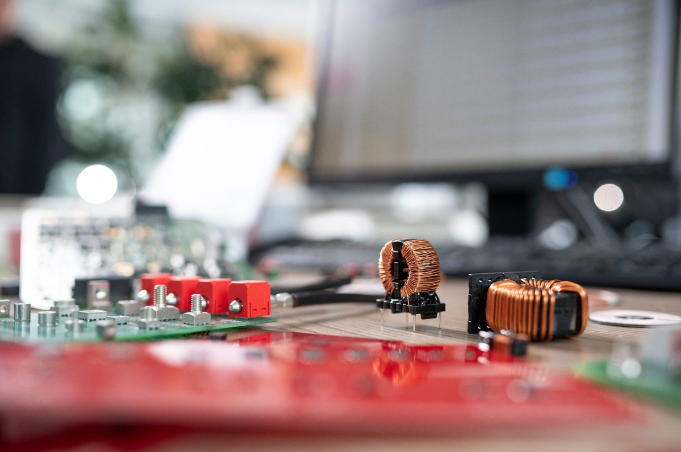

Texas InstrumentsUC3717 and L-C Filter Reduce EMI and Chopping Losses in Step Motor

Texas InstrumentsPowering the TMS320DM335 and TMS320DM355 with the TPS650061

Texas InstrumentsAC Coupling Instrumentation and Difference Amplifiers

Texas InstrumentsMulti-rails supply regulated outputs to power TFT screen from car battery

Texas InstrumentsDN300 -- SmartRF04EB Troubleshooting (Rev. B)

Texas InstrumentsClock jitter analyzed in the time domain, Part 1

Texas InstrumentsNewer high-speed ADCs come outfitted with a large analog-input bandwidth (about three to six times the maximum sampling frequency) so they can be used in undersampling applications. Recent advances in ADC design extend the usable input range significantly so that system designers can eliminate at least one intermediate frequency stage, which reduces cost and power consumption. In the design of an undersampling receiver, special attention has to be given to the sampling clock, because at higher input frequencies the jitter of the clock becomes a dominant factor in limiting the signal-to-noise ratio (SNR).

Part 1 of this three-part article series focuses on how to accurately estimate jitter from a clock source and combine it with the aperture jitter of the ADC. In Part 2, that combined jitter will be used to calculate the ADC’s SNR, which will then be compared against actual measurements. Part 3 will show how to further increase the SNR of the ADC by improving the ADC’s aperture jitter, with a focus on optimizing the slew rate of the clock signal.