Data Sheet

August 31, 2006

FN8240.3

# Terminal Voltage ±2.7V to ±5V, 128 Taps, Up/Down Interface

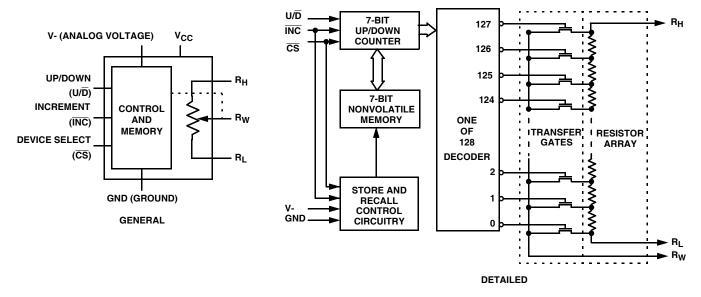

The Intersil ISL95710 is a digitally controlled potentiometer (XDCP). The device consists of a resistor array, wiper switches, a control section, and nonvolatile memory. The wiper position is controlled by a Up/Down interface.

The potentiometer is implemented by a resistor array composed of 127 resistive elements and a wiper switching network. Between each element and at either end are tap points accessible to the wiper terminal. The position of the wiper element is controlled by the  $\overline{\text{CS}}$ ,  $U/\overline{D}$ , and  $\overline{\text{INC}}$  inputs. The position of the wiper can be stored in nonvolatile memory and then be recalled upon a subsequent power-up operation.

The device can be used as a three-terminal potentiometer or as a two-terminal variable resistor in a wide variety of applications including:

- Industrial and automotive control

- · Parameter and bias adjustments

- · Amplifier bias and control

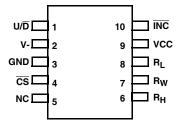

#### **Pinout**

ISL95710 (10 LD MSOP) TOP VIEW

#### **Features**

- Non-Volatile Solid-State Potentiometer

- Up/Down Interface with Chip Select Enable

- DCP Terminal Voltage ±2.7V to ±5.5V

- 128 Wiper Tap Points

- Wiper position stored in nonvolatile memory and recalled on power-up

- 127 Resistive Elements

- Typical R<sub>TOTAL</sub> tempco = ±50ppm/°C

- End to end resistance range ±20%

- Low Power CMOS

- Standby current, 1µA

- Active current, 3mA max

- $V_{CC} = 2.7V$  to 5.5V

- V = -2.7V to -5.5V

- High Reliability

- Endurance, 200,000 data changes per bit

- Register data retention, 50 years

- R<sub>TOTAL</sub> Values = 10kΩ, 50kΩ

- Package

- 10 Ld MSOP

- Pb-free plus anneal (RoHS compliant)

# **Ordering Information**

| PART NUMBER<br>(Notes 1, 2) | PART MARKING | RESISTANCE OPTION $(\Omega)$ | TEMP. RANGE<br>(℃) | PACKAGE<br>(Pb-Free) | PKG. DWG. # |

|-----------------------------|--------------|------------------------------|--------------------|----------------------|-------------|

| ISL95710WIU10Z              | AKR          | 10k                          | -40 to +85         | 10 Ld MSOP           | M10.118     |

| ISL95710UIU10Z              | AKP          | 50k                          | -40 to +85         | 10 Ld MSOP           | M10.118     |

#### NOTES:

- 1. Add "-T" suffix for tape and reel.

- 2. Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

# Block Diagram

# Pin Descriptions

| PIN NUMBER | SYMBOL         | DESCRIPTION                                                                                             |

|------------|----------------|---------------------------------------------------------------------------------------------------------|

| 1          | U/D            | Controls the direction of wiper movement and whether the counter is incremented or decremented          |

| 2          | V-             | Negative bias voltage for the potentiometer wiper control                                               |

| 3          | GND            | Ground                                                                                                  |

| 4          | <del>CS</del>  | Chip select. The device is selected when the CS input is LOW. Also used to initiate a nonvolatile store |

| 5          | NC             | No Connect. Pin is to be left unconnected                                                               |

| 6          | R <sub>H</sub> | A fixed terminal for one end of the potentiometer resistor                                              |

| 7          | RW             | The wiper terminal which is equivalent to the movable terminal of a potentiometer                       |

| 8          | RL             | A fixed terminal for one end of the potentiometer resistor                                              |

| 9          | VCC            | Positive logic supply voltage                                                                           |

| 10         | ĪNC            | Increment input; negative edge triggered                                                                |

#### **Absolute Maximum Ratings**

#### Temperature under bias . . . . . . . . . . . . . . . . -65°C to +135°C Voltage on CS, INC, U/D and VCC with respect to GND . . . . . . . . . . . . -1V to +6V Voltage on V- (referenced to GND) . . . . . . . . -6V I<sub>W</sub> (10 seconds).....±6mA ESD (Mil-Std 883, Method 3015).....>2kV

#### **Thermal Information**

| Thermal Resistance (Typical, Note 3) | $\theta_{JA}$ ( $C/W$ ) |

|--------------------------------------|-------------------------|

| MSOP Package                         | +170                    |

#### **Recommended Operating Conditions**

| Temperature Range (Industrial) | 40℃ to +85℃   |

|--------------------------------|---------------|

| V <sub>CC</sub>                | 2.7V to 5.5V  |

| V                              | 2.7V to -5.5V |

CAUTION: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device (at these or any other conditions above those listed in the operational sections of this specification) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### NOTE:

3.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

#### **Analog Specifications** Over recommended operating conditions unless otherwise stated.

| SYMBOL                                                      | PARAMETER                                                               | TEST CONDITIONS                                                                 | MIN                   | TYP<br>(Note 1) | MAX             | UNIT            |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------|-----------------|-----------------|-----------------|--|

| R <sub>TOTAL</sub>                                          | R <sub>H</sub> to R <sub>L</sub> resistance                             | W option                                                                        |                       | 10              |                 | kΩ              |  |

|                                                             |                                                                         | U option                                                                        |                       | 50              |                 | kΩ              |  |

|                                                             | R <sub>H</sub> to R <sub>L</sub> resistance tolerance                   |                                                                                 | -20                   |                 | +20             | %               |  |

| TC <sub>R</sub><br>(Note 12, 13)                            | Resistance Temperature Coefficient                                      | I <sub>DCP</sub> = 1mA<br>T = -40℃ to +85℃                                      |                       | ±50             |                 | ppm/℃           |  |

| $V_{RH}, V_{RL}$                                            | R <sub>H</sub> ,R <sub>L</sub> terminal voltage                         |                                                                                 | V-                    |                 | V <sub>CC</sub> | V               |  |

| $R_{W}$                                                     | Wiper resistance                                                        | V- = -5.5V; $V_{CC}$ = +5.5V,<br>wiper current = $(V_{CC}-V_{-})/R_{TOTAL}$     |                       | 70              | 200             | Ω               |  |

| C <sub>H</sub> /C <sub>L</sub> /C <sub>W</sub><br>(Note 13) | Potentiometer Capacitance                                               |                                                                                 |                       | 10/10/25        |                 | pF              |  |

| I <sub>LkgDCP</sub>                                         | Leakage on DCP pins                                                     | Voltage at pins; V- to V <sub>CC</sub>                                          | -1                    | 0.1             | 1               | μA              |  |

| VOLTAGE DIV                                                 | VIDER MODE (V- @ R <sub>L</sub> ; V <sub>CC</sub> @ R <sub>H</sub> ; Vo | oltage at R <sub>W</sub> = V <sub>RW</sub> unloaded)                            | 1                     |                 |                 |                 |  |

| INL<br>(Note 6)                                             | Integral non-linearity                                                  |                                                                                 | -1                    |                 | 1               | LSB<br>(Note 2) |  |

| DNL<br>(Note 5)                                             | Differential non-linearity                                              | W, U options                                                                    | -0.5                  |                 | 0.5             | LSB<br>(Note 2) |  |

| ZSerror                                                     | Zero-scale error                                                        | W option                                                                        | 0                     | 1               | 4               | LSB<br>(Note 2) |  |

| (Note 3)                                                    |                                                                         | U option                                                                        | 0                     | 0.5             | 2               |                 |  |

| FSerror                                                     | Full-scale error                                                        | W option                                                                        | -4                    | -1              | 0               | LSB             |  |

| (Note 4)                                                    |                                                                         | U option                                                                        | -2                    | -0.5            | 0               | (Note 2)        |  |

| TC <sub>V</sub> (Notes 7, 13)                               | Ratiometric Temperature Coefficient                                     | DCP Register set at 63d,<br>T = -40℃ to +85℃                                    |                       | ±4              |                 | ppm/℃           |  |

| RESISTOR M                                                  | ODE (Measurements between R <sub>W</sub> and                            | $R_L$ with $R_H$ not connected, or between $R_W$ and $R$                        | H with R <sub>L</sub> | not connecte    | ed)             |                 |  |

| RINL<br>(Note 11)                                           | Integral non-linearity                                                  | DCP register set between 20 hex and 5F hex.<br>Monotonic over all tap positions | -1                    |                 | 1               | MI<br>(Note 8)  |  |

| RDNL<br>(Note 10)                                           | Differential non-linearity                                              | W, U options                                                                    | -0.5                  |                 | 0.5             | MI<br>(Note 8)  |  |

| Roffset                                                     | Offset                                                                  | DCP Register set to 00 hex, W option                                            | 0                     | 2               | 5               | MI              |  |

| (Note 9)                                                    |                                                                         | DCP Register set to 00 hex, U option                                            | 0                     | 0.5             | 2               | (Note 8)        |  |

intersil FN8240.3 August 31, 2006

### **Operating Specifications** Over the recommended operating conditions unless otherwise specified.

| SYMBOL                  | PARAMETER                                           | TEST CONDITIONS                                                                                                                                                                                                                                                                                        | MIN                 | TYP<br>(Note 1)          | MAX                      | UNIT   |

|-------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|--------------------------|--------|

| I <sub>CC1</sub>        | V <sub>CC</sub> supply current, volatile write/read | $\overline{\text{CS}} = \text{V}_{\text{IL}}, \text{U}/\overline{\text{D}} = \text{V}_{\text{IL}} \text{ or V}_{\text{IH}} \text{ and } \overline{\text{INC}} = \text{V}_{\text{IL}} \text{ or V}_{\text{IH}}, \\ \text{R}_{\text{L}}, \text{R}_{\text{H}}, \text{R}_{\text{W}} \text{ not connected}$ |                     |                          | 500                      | μΑ     |

| I <sub>V-1</sub>        | V- supply current, volatile write/read              | $\overline{\text{CS}} = \text{V}_{\text{IL}}, \text{U}/\overline{\text{D}} = \text{V}_{\text{IL}} \text{ or V}_{\text{IH}} \text{ and } \overline{\text{INC}} = \text{V}_{\text{IL}} \text{ or V}_{\text{IH}}, \\ \text{R}_{\text{L}}, \text{R}_{\text{H}}, \text{R}_{\text{W}} \text{ not connected}$ | -100                |                          |                          | μА     |

| I <sub>CC2</sub>        | V <sub>CC</sub> supply current, nonvolatile write   | $U/\overline{D} = V_{IL}$ or $V_{IH}$ and $\overline{INC} = V_{IH}$ , $\overline{CS}$ = transitions from $V_{IL}$ to $V_{IH}$ . $R_L$ , $R_H$ , $R_W$ not connected                                                                                                                                    |                     |                          | 500                      | μΑ     |

| I <sub>V-2</sub>        | V- supply current, nonvolatile write                | $U/\overline{D} = V_{IL}$ or $V_{IH}$ and $\overline{INC} = V_{IH}$ , $\overline{CS}$ = transitions from $V_{IL}$ to $V_{IH}$ . $R_L$ , $R_H$ , $R_W$ not connected                                                                                                                                    | -3                  |                          |                          | mA     |

| I <sub>CCSB</sub>       | V <sub>CC</sub> current (standby)                   | V <sub>CC</sub> = +5.5V, I <sup>2</sup> C Interface in Standby State                                                                                                                                                                                                                                   |                     |                          | 1                        | μΑ     |

|                         |                                                     | V <sub>CC</sub> = +3.6V, I <sup>2</sup> C Interface in Standby State                                                                                                                                                                                                                                   |                     |                          | 1                        | μΑ     |

| I <sub>V-SB</sub>       | V- current (standby)                                | V- = -5.5V, <del>CS</del> = V <sub>IH</sub>                                                                                                                                                                                                                                                            | -5                  |                          |                          | μΑ     |

|                         |                                                     | V- = -3.6V, <del>CS</del> = V <sub>IH</sub>                                                                                                                                                                                                                                                            | -2                  |                          |                          | μΑ     |

| I <sub>LkgDig</sub>     | Leakage current, at pins INC, CS, and U/D           | V <sub>IL</sub> or V <sub>IH</sub> applied at pin                                                                                                                                                                                                                                                      | -10                 |                          | 10                       | μA     |

| I <sub>IL_CS</sub>      | Leakage at CS, input low                            | V <sub>IL</sub> = 0V                                                                                                                                                                                                                                                                                   | -300                |                          |                          | μА     |

| Vpor                    | Power-on recall for both V- and V <sub>CC</sub>     | V-                                                                                                                                                                                                                                                                                                     | -2.5                |                          |                          | V      |

|                         |                                                     | Vcc                                                                                                                                                                                                                                                                                                    |                     |                          | 2.5                      | V      |

| V- Ramp                 | V- ramp rate                                        |                                                                                                                                                                                                                                                                                                        |                     |                          | -0.2                     | V/ms   |

| EEPROM SP               | PECS                                                |                                                                                                                                                                                                                                                                                                        |                     |                          |                          |        |

|                         | EEPROM Endurance                                    |                                                                                                                                                                                                                                                                                                        | 200,000             |                          |                          | Cycles |

|                         | EEPROM Retention                                    | Temperature ≤ +75℃                                                                                                                                                                                                                                                                                     | 50                  |                          |                          | Years  |

| 3-WIRE INTE             | ERFACE SPECS                                        |                                                                                                                                                                                                                                                                                                        |                     |                          |                          |        |

| $V_{IL}$                | INC, CS, and U/D input buffer LOW voltage           |                                                                                                                                                                                                                                                                                                        | -0.3                |                          | 0.3*V <sub>CC</sub>      | V      |

| $V_{IH}$                | INC, CS, and U/D input buffer HIGH voltage          |                                                                                                                                                                                                                                                                                                        | 0.7*V <sub>CC</sub> |                          | V <sub>CC</sub> +<br>0.3 | V      |

| Hysteresis<br>(Note 13) | INC, CS, and U/D input buffer hysteresis            |                                                                                                                                                                                                                                                                                                        |                     | 0.15*<br>V <sub>CC</sub> |                          | V      |

| Cpin                    | INC, CS, and U/D pin capacitance                    |                                                                                                                                                                                                                                                                                                        |                     | 10                       |                          | pF     |

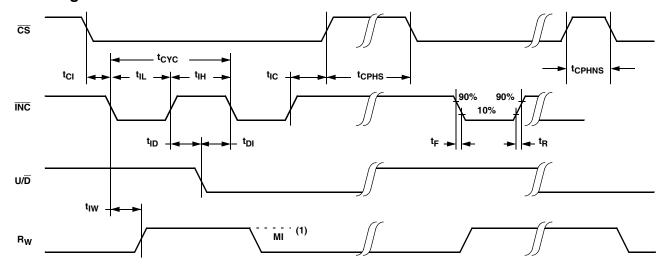

# $\textbf{AC Electrical Specifications} \qquad \text{V}_{CC} = 5 \text{V} \pm 10\%, \ \text{T}_{A} = \text{Full Operating Temperature Range unless otherwise stated}$

| SYMBOL                         | PARAMETER                   | MIN | TYP (Note 1) | MAX | UNIT |

|--------------------------------|-----------------------------|-----|--------------|-----|------|

| t <sub>Cl</sub>                | CS to INC setup             | 100 |              |     | ns   |

| t <sub>ID</sub>                | INC HIGH to U/D change      | 100 |              |     | ns   |

| t <sub>DI</sub>                | U/D to INC setup            | 1   |              |     | μs   |

| t <sub>IL</sub>                | INC LOW period              | 1   |              |     | μs   |

| t <sub>IH</sub>                | INC HIGH period             | 1   |              |     | μs   |

| t <sub>IC</sub>                | INC inactive to CS inactive | 1   |              |     | μs   |

| t <sub>CPHS</sub><br>(Note 14) | CS deselect time (STORE)    | 20  |              |     | ms   |

| t <sub>CPHNS</sub>             | CS deselect time (NO STORE) | 1   |              |     | μs   |

### AC Electrical Specifications V<sub>CC</sub> = 5V ±10%, T<sub>A</sub> = Full Operating Temperature Range unless otherwise stated (Continued)

| SYMBOL                         | PARAMETER                    | MIN | TYP (Note 1) | MAX | UNIT |

|--------------------------------|------------------------------|-----|--------------|-----|------|

| t <sub>IW</sub>                | INC to R <sub>W</sub> change |     | 100          | 500 | μs   |

| t <sub>CYC</sub>               | INC cycle time               | 2   |              |     | μs   |

| t <sub>R,</sub> t <sub>F</sub> | INC input rise and fall time |     |              | 500 | μs   |

#### NOTES:

- 1. Typical values are for  $T_A = +25$ °C and 3.3V supply voltage.

- 2. LSB: [V(R<sub>W</sub>)<sub>127</sub> V(R<sub>W</sub>)<sub>0</sub>]/127. V(R<sub>W</sub>)<sub>127</sub> and V(R<sub>W</sub>)<sub>0</sub> are V(R<sub>W</sub>) for the DCP register set to 7F hex and 00 hex respectively. LSB is the incremental voltage when changing from one tap to an adjacent tap.

- 3. ZS error =  $(V(R_W)_0 V_-)/LSB$ .

- 4. FS error =  $[V(R_W)_{127} V+]/LSB$ .

- 5. DNL =  $[V(R_W)_i V(R_W)_{i-1}]/LSB-1$ , for i = 1 to 127. i is the DCP register setting.

- 6.  $INL = V(R_W)_i (i \cdot LSB V(R_W)_0)/LSB$  for i = 1 to 127.

$$7. \ \ \mathsf{TC_V} = \frac{\mathsf{Max}(\mathsf{V}(\mathsf{RW})_{\hat{\mathsf{I}}}) - \mathsf{Min}(\mathsf{V}(\mathsf{RW})_{\hat{\mathsf{I}}})}{[\mathsf{Max}(\mathsf{V}(\mathsf{RW})_{\hat{\mathsf{I}}}) + \mathsf{Min}(\mathsf{V}(\mathsf{RW})_{\hat{\mathsf{I}}})]/2} x \frac{10^6}{125 \, \mathbb{C}}$$

for i = 16 to 120 decimal. Max ( ) is the maximum value of the wiper voltage and Min ( ) is the minimum value of the wiper voltage over the temperature range.

- 8. MI =  $|R_{127} R_0|/127$ .  $R_{127}$  and  $R_0$  are the measured resistances for the DCP register set to 7F hex and 00 hex respectively.

- Roffset = R<sub>0</sub>/MI, when measuring between RW and RL. Roffset = R<sub>127</sub>/MI, when measuring between RW and RH.

- 10. RDNL =  $(R_i R_{i-1})/MI$  -1, for i = 16 to 127.

- 11. RINL =  $[R_i (MI \cdot i) R_0]/MI$ , for i = 16 to 127.

12.

$$TC_{R} = \frac{[Max(Ri) - Min(Ri)]}{[Max(Ri) + Min(Ri)]/2} \times \frac{10^{6}}{125 \text{ C}}$$

for i = 16 to 127, T = -40 $^{\circ}$ C to +85 $^{\circ}$ C. Max ( ) is the maximum value of the resistance and Min ( ) is the minimum value of the resistance over the temperature range.

- 13. This parameter is not 100% tested.

- 14. t<sub>CPHS</sub> is the minimum cycle time to be allowed for any non-volatile Write by the user. It is the time from a valid STORE condition to the end of the self-timed internal non-volatile write cycle. No CS or INC changes should be allowed.

# Symbol Table

| WAVEFORM | INPUTS                      | OUTPUTS                       |

|----------|-----------------------------|-------------------------------|

|          | Must be steady              | Will be steady                |

|          | May change from Low to High | Will change from Low to High  |

|          | May change from High to Low | Will change from High to Low  |

|          | Don't Care: Changes Allowed | Changing: State Not Known     |

|          | N/A                         | Center Line is High Impedance |

intersil

# A.C. Timing

NOTE (1): MI IN THE TIMING DIAGRAM REFERS TO THE MINIMUM INCREMENTAL CHANGE IN THE WIPER POSITION.

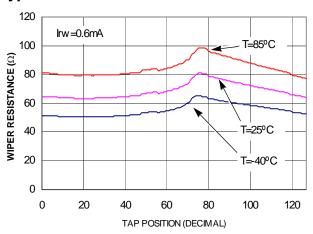

# **Typical Performance Curves**

FIGURE 1. WIPER RESISTANCE vs TAP POSITION [I(RW) =  $V_{CC}/R_{TOTAL}$ ] for 10k $\Omega$  (W)

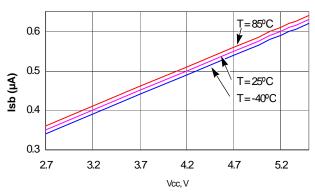

FIGURE 2. STANDBY I<sub>CC</sub> vs V<sub>CC</sub>

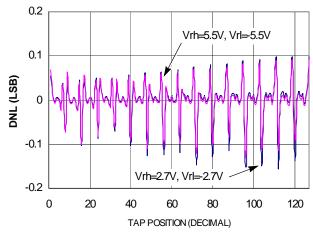

FIGURE 3. DNL vs TAP POSITION IN VOLTAGE DIVIDER MODE FOR 10k $\Omega$  (W)

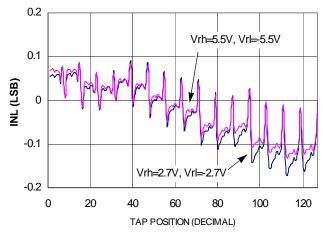

FIGURE 4. INL vs TAP POSITION IN VOLTAGE DIVIDER MODE FOR  $10k\Omega$  (W)

# Typical Performance Curves (Continued)

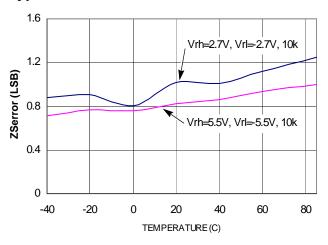

FIGURE 5. ZSerror vs TEMPERATURE

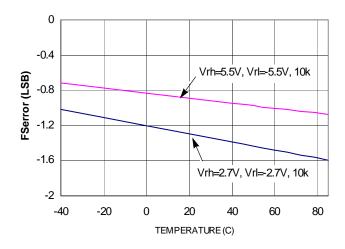

FIGURE 6. FSerror vs TEMPERATURE

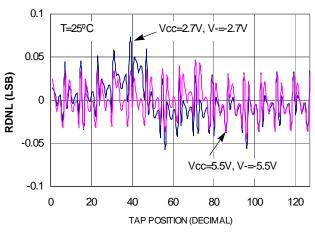

FIGURE 7. DNL vs TAP POSITION IN RHEOSTAT MODE FOR  $10k\Omega$  (W)

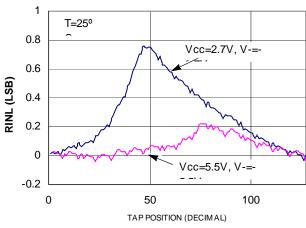

FIGURE 8. INL vs TAP POSITION IN RHEOSTAT MODE FOR  $10k\Omega \ (W)$

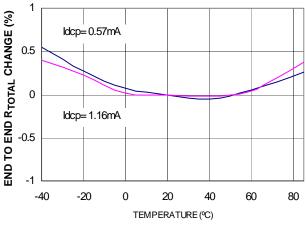

FIGURE 9. END TO END  $R_{TOTAL}$  % CHANGE vs TEMPERATURE

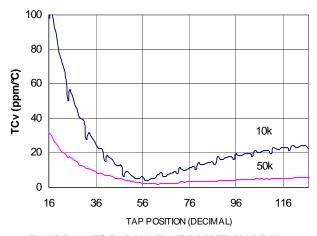

FIGURE 10. TC FOR VOLTAGE DIVIDER MODE IN ppm

FN8240.3 August 31, 2006

### Typical Performance Curves (Continued)

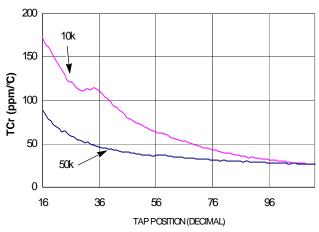

FIGURE 11. TC FOR RHEOSTAT MODE IN ppm

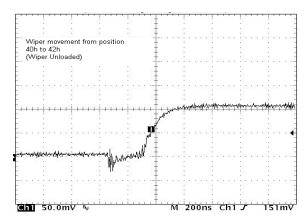

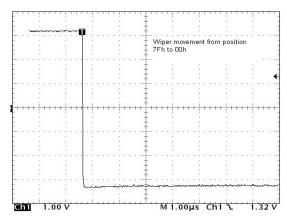

FIGURE 13. WIPER MOVEMENT

# Power Up and Down Requirements

In order to prevent unwanted tap position changes, or an inadvertent store, bring the  $\overline{CS}$  and  $\overline{INC}$  high before or concurrently with the  $V_{CC}$  pin on power-up. The potentiometer voltages must be applied after this sequence is completed. During power-up, the data sheet parameters for the DCP do not fully apply until 1ms after  $V_{CC}$  reaches its final value. The  $V_{CC}$  ramp spec is always in effect.

# Pin Descriptions

#### R<sub>H</sub> and R<sub>L</sub>

The high (R<sub>H</sub>) and low (R<sub>L</sub>) terminals of the ISL95710 are equivalent to the fixed terminals of a mechanical potentiometer. The terminology of R<sub>L</sub> and R<sub>H</sub> references the relative position of the terminal in relation to wiper movement direction selected by the U/ $\overline{D}$  input and not the voltage potential on the terminal.

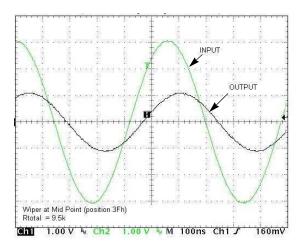

FIGURE 12. FREQUENCY RESPONSE (1.8MHz)

FIGURE 14. LARGE SIGNAL SETTLING TIME

#### $R_{w}$

$R_{W}$  is the wiper terminal and is equivalent to the movable terminal of a mechanical potentiometer. The position of the wiper within the array is determined by the wiper counter.

# Up/Down (U/D)

The  $U/\overline{D}$  input controls the direction of the wiper movement and whether the wiper counter is incriminated or decremented.

# Increment (INC)

The  $\overline{\text{INC}}$  input is negative-edge triggered. Toggling INC will move the wiper and either increment or decrement the wiper counter in the direction indicated by the logic level on the  $U/\overline{D}$  input.

# Chip Select (CS)

The device is selected when the  $\overline{\text{CS}}$  input is LOW. The current wiper counter value is stored in nonvolatile memory when  $\overline{\text{CS}}$  is returned HIGH while the  $\overline{\text{INC}}$  input is also HIGH. After the store operation is complete the ISL95710 will be

FN8240.3 August 31, 2006

placed in the low power standby mode until the device is selected once again.

### **Principles of Operation**

There are three sections of the ISL95710: the input control, wiper counter and decode section; the nonvolatile memory; and the resistor array. The input control section operates as an up/down counter. The output of this wiper counter is decoded to turn on a electronic switch connecting a point on the resistor array to the wiper output. The contents of the wiper counter can be stored in nonvolatile memory and retained for future use. The resistor array is comprised of individual resistors connected in series. At either end of the array and between each resistor is an electronic switch that transfers the potential at that point to the wiper.

The wiper, when at either fixed terminal, acts like its mechanical equivalent and does not move beyond the last position. The wiper counter does not wrap around when clocked to either extreme.

The electronic switches on the device operate in a "make before break" mode when the wiper changes tap positions. If the wiper is moved several positions, multiple taps are connected to the wiper for  $t_{\mbox{\scriptsize IW}}$  ( $\mbox{\scriptsize INC}$  to  $R_{\mbox{\scriptsize W}}$  change). The  $R_{\mbox{\scriptsize TOTAL}}$  value for the device can temporarily be reduced by a significant amount if the wiper is moved several positions.

When the device is powered-down, the last wiper position stored will be maintained in the nonvolatile memory. When power is restored, the contents of the memory are recalled and the wiper is set to the value last stored.

### Instructions and Programming

The  $\overline{\text{INC}}$ , U/ $\overline{\text{D}}$  and  $\overline{\text{CS}}$  inputs control the movement of the wiper along the resistor array. With  $\overline{\text{CS}}$  set LOW the device is selected and enabled to respond to the U/ $\overline{\text{D}}$  and  $\overline{\text{INC}}$  inputs. HIGH to LOW transitions on  $\overline{\text{INC}}$  will increment or decrement (depending on the state of the U/ $\overline{\text{D}}$  input) a seven bit wiper counter. The output of this wiper counter is decoded to select one of 128 wiper positions along the resistive array.

The value of the wiper counter is stored in nonvolatile memory whenever  $\overline{\text{CS}}$  transitions HIGH while the  $\overline{\text{INC}}$  input is also HIGH.

The system may select the ISL95710, move the wiper and deselect the device without having to store the latest wiper position in nonvolatile memory. After the wiper movement is performed as described above and once the new position is reached, the system must keep  $\overline{\text{INC}}$  LOW while taking  $\overline{\text{CS}}$  HIGH. The new wiper position will be maintained until changed by the system or until a power-up/down cycle recalls the previously stored data.

This procedure allows the system to always power-up to a preset value stored in nonvolatile memory; then during system operation minor adjustments could be made. The

adjustments might be based on user preference, system parameter changes due to temperature drift, etc.

The state of  $U/\overline{D}$  may be changed while  $\overline{CS}$  remains LOW. This allows the host system to enable the device and then move the wiper up and down until the proper trim is attained. During initial power-up  $\overline{CS}$  must go high along with or before  $V_{CC}$  to avoid an accidental store generation.

**TABLE 1. MODE SELECTION**

| cs | INC | U/D | MODE                                      |

|----|-----|-----|-------------------------------------------|

| L  | ~_  | Н   | Wiper up                                  |

| L  | ~   | L   | Wiper down                                |

|    | Н   | Х   | Store wiper position                      |

| Н  | Х   | Х   | Standby current                           |

|    | L   | Х   | No store, return to standby               |

| Н  | Н   | Х   | Standby                                   |

| 7  | L   | Н   | Wiper up one position (not recommended)   |

|    | L   | L   | Wiper down one position (not recommended) |

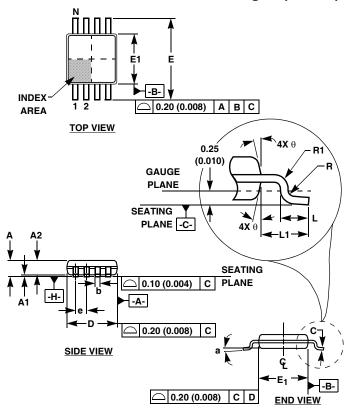

### Mini Small Outline Plastic Packages (MSOP)

# M10.118 (JEDEC MO-187BA)

#### 10 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES         |                 | MILLIM         | MILLIMETERS     |       |

|--------|----------------|-----------------|----------------|-----------------|-------|

| SYMBOL | MIN            | MAX             | MIN            | MAX             | NOTES |

| Α      | 0.037          | 0.043           | 0.94           | 1.10            | -     |

| A1     | 0.002          | 0.006           | 0.05           | 0.15            | -     |

| A2     | 0.030          | 0.037           | 0.75           | 0.95            | -     |

| b      | 0.007          | 0.011           | 0.18           | 0.27            | 9     |

| С      | 0.004          | 0.008           | 0.09           | 0.20            | -     |

| D      | 0.116          | 0.120           | 2.95           | 3.05            | 3     |

| E1     | 0.116          | 0.120           | 2.95           | 3.05            | 4     |

| е      | 0.020          | BSC             | 0.50 BSC       |                 | -     |

| Е      | 0.187          | 0.199           | 4.75           | 5.05            | -     |

| L      | 0.016          | 0.028           | 0.40           | 0.70            | 6     |

| L1     | 0.037          | REF             | 0.95           | REF             | -     |

| N      | 1              | 10              |                | 0               | 7     |

| R      | 0.003          | -               | 0.07           | -               | -     |

| R1     | 0.003          | -               | 0.07           | -               | -     |

| θ      | 5 <sup>0</sup> | 15 <sup>0</sup> | 5 <sup>0</sup> | 15 <sup>0</sup> | -     |

| α      | 0°             | 6 <sup>0</sup>  | 0°             | 6 <sup>0</sup>  | -     |

Rev. 0 12/02

#### NOTES:

- These package dimensions are within allowable dimensions of JEDEC MO-187BA.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1994.

- Dimension "D" does not include mold flash, protrusions or gate burrs and are measured at Datum Plane. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E1" does not include interlead flash or protrusions and are measured at Datum Plane. -H- Interlead flash and protrusions shall not exceed 0.15mm (0.006 inch) per side.

- 5. Formed leads shall be planar with respect to one another within 0.10mm (.004) at seating Plane.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- Dimension "b" does not include dambar protrusion. Allowable dambar protrusion shall be 0.08mm (0.003 inch) total in excess of "b" dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm (0.0027 inch).

- 10. Datums -A and -B to be determined at Datum plane

- 11. Controlling dimension: MILLIMETER. Converted inch dimensions are for reference only

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

intersil