# Low Noise/Low Power/2-Wire Bus

#### Data Sheet

October 12, 2006

FN8192.4

XQANQ

# Quad Digitally Controlled Potentiometers (XDCP<sup>™</sup>)

## FEATURES

- Four potentiometers per package

- 64 resistor taps

- 2-wire serial interface for write, read, and transfer operations of the potentiometer

- 50 $\Omega$  Wiper resistance, typical at 5V.

- Four non-volatile data registers for each potentiometer

- Non-volatile storage of multiple wiper position

- Power-on recall. Loads saved wiper position on power-up.

- Standby current < 1µA typical

- System V<sub>CC</sub>: 2.7V to 5.5V operation

- 10k $\Omega,$  2.5k $\Omega$  End to end resistance

- 100 yr. data retention

- Endurance: 100,000 data changes per bit per register

- Low power CMOS

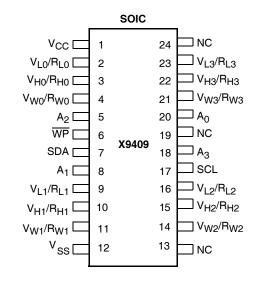

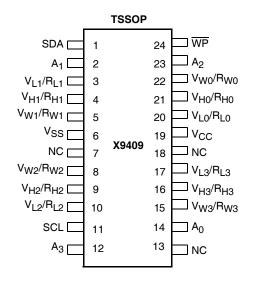

- 24 Ld SOIC, 24 Ld TSSOP

- Pb-free plus anneal available (RoHS compliant)

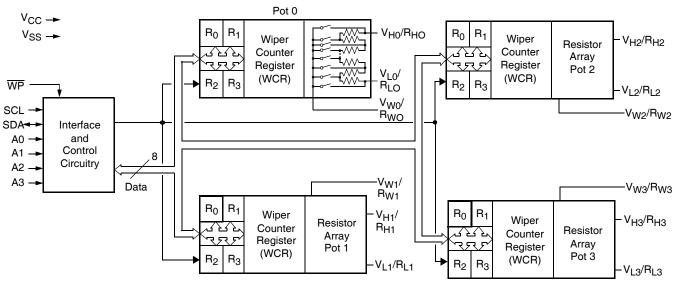

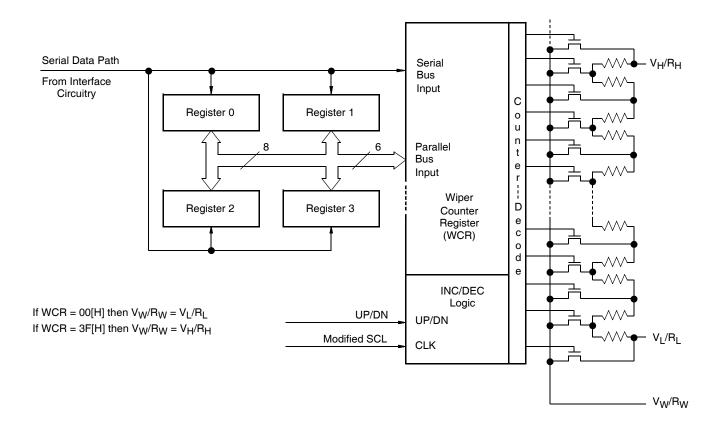

#### **BLOCK DIAGRAM**

#### DESCRIPTION

The X9409 integrates 4 digitally controlled potentiometers (XDCP) on a monolithic CMOS integrated microcircuit.

The digitally controlled potentiometer is implemented using 63 resistive elements in a series array. Between each element are tap points connected to the wiper terminal through switches. The position of the wiper on the array is controlled by the user through the 2-wire bus interface. Each potentiometer has associated with it a volatile Wiper Counter Register (WCR) and 4 nonvolatile Data Registers (DR0:DR3) that can be directly written to and read by the user. The contents of the WCR controls the position of the wiper on the resistor array through the switches. Power-up recalls the contents of DR0 to the WCR.

The XDCP can be used as a three-terminal potentiometer or as a two-terminal variable resistor in a wide variety of applications including control, parameter adjustments, and signal processing.

## **Ordering Information**

| PART NUMBER             | PART MARKING | V <sub>CC</sub> LIMITS<br>(V) | POTENTIOMETER<br>ORGANIZATION<br>(kΩ) | TEMP<br>RANGE<br>(℃) | PACKAGE                        | PKG.<br>DWG. # |

|-------------------------|--------------|-------------------------------|---------------------------------------|----------------------|--------------------------------|----------------|

| V0 400 W00 41 0 7t      | ×0.40014/0.0 | 074 55                        | 10                                    | 40.4.05              |                                |                |

| X9409WS24I-2.7*         | X9409WS G    | 2.7 to 5.5                    | 10                                    | -40 to 85            | 24 Ld SOIC (300 mil)           | M24.3          |

| X9409WS24IZ-2.7* (Note) | X9409WS ZG   |                               |                                       | -40 to 85            | 24 Ld SOIC (300 mil) (Pb-free) | MDP0027        |

| X9409WV24-2.7           | X9409WV F    |                               |                                       | 0 to 70              | 24 Ld TSSOP (4.4mm)            | MDP0044        |

| X9409WV24Z-2.7 (Note)   | X9409WV ZF   |                               |                                       | 0 to 70              | 24 Ld TSSOP (4.4mm) (Pb-free)  | MDP0044        |

| X9409WV24I-2.7*         | X9409WV G    |                               |                                       | -40 to 85            | 24 Ld TSSOP (4.4mm)            | MDP0044        |

| X9409WV24IZ-2.7* (Note) | X9409WV ZG   |                               |                                       | -40 to 85            | 24 Ld TSSOP (4.4mm) (Pb-free)  | MDP0044        |

\*Add "T1" suffix for tape and reel.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### **PIN DESCRIPTIONS**

#### Host Interface Pins

#### Serial Clock (SCL)

The SCL input is used to clock data into and out of the X9409.

#### Serial Data (SDA)

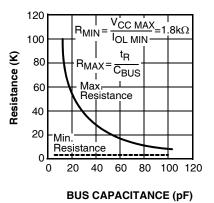

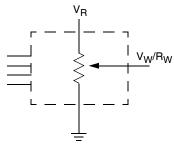

SDA is a bidirectional pin used to transfer data into and out of the device. It is an open drain output and may be wire-ORed with any number of open drain or open collector outputs. An open drain output requires the use of a pull-up resistor. For selecting typical values, refer to the guidelines for calculating typical values on the bus pull-up resistors graph.

#### Device Address (A<sub>0</sub> - A<sub>3</sub>)

The address inputs are used to set the least significant 4 bits of the 8-bit slave address. A match in the slave address serial data stream must be made with the address input in order to initiate communication with the X9409. A maximum of 16 devices may occupy the 2-wire serial bus.

#### **Potentiometer Pins**

#### $V_{H0}/R_{H0} - V_{H3}/R_{H3}, V_{L0}/R_{L0} - V_{L3}/R_{L3}$

The  $V_H/R_H$  and  $V_L/R_L$  inputs are equivalent to the terminal connections on either end of a mechanical potentiometer.

## V<sub>W0</sub>/R<sub>W0</sub> - V<sub>W3</sub>/R<sub>W3</sub>

The wiper outputs are equivalent to the wiper output of a mechanical potentiometer.

#### Hardware Write Protect Input (WP)

The  $\overline{WP}$  pin when low prevents nonvolatile writes to the Data Registers.

#### PIN NAMES

| Symbol                                                                | Description               |

|-----------------------------------------------------------------------|---------------------------|

| SCL                                                                   | Serial Clock              |

| SDA                                                                   | Serial Data               |

| A0-A3                                                                 | Device Address            |

| V <sub>H0</sub> /R <sub>H0</sub> - V <sub>H3</sub> /R <sub>H3</sub> , | Potentiometer Pin         |

| $V_{L0}/R_{L0} - V_{L3}/R_{L3}$                                       | (terminal equivalent)     |

| V <sub>W0</sub> /R <sub>W0</sub> - V <sub>W3</sub> /R <sub>W3</sub>   | Potentiometer Pin         |

|                                                                       | (wiper equivalent)        |

| WP                                                                    | Hardware Write Protection |

| V <sub>CC</sub>                                                       | System Supply Voltage     |

| V <sub>SS</sub>                                                       | System Ground (Digital)   |

| NC                                                                    | No Connection             |

## PIN CONFIGURATION

#### PRINCIPLES OF OPERATION

The X9409 is a highly integrated microcircuit incorporating four resistor arrays and their associated registers and counters and the serial interface logic providing direct communication between the host and the XDCP potentiometers.

#### **Serial Interface**

The X9409 supports a bidirectional bus oriented protocol. The protocol defines any device that sends data onto the bus as a transmitter and the receiving device as the receiver. The device controlling the transfer is a master and the device being controlled is the slave. The master will always initiate data transfers and provide the clock for both transmit and receive operations. Therefore, the X9409 will be considered a slave device in all applications.

#### **Clock and Data Conventions**

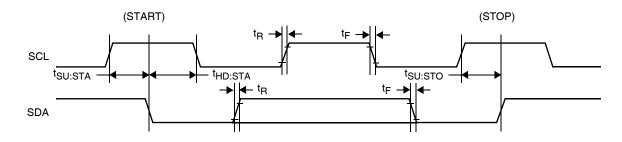

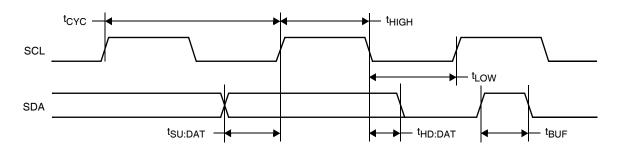

Data states on the SDA line can change only during SCL LOW periods ( $t_{LOW}$ ). SDA state changes during SCL HIGH are reserved for indicating start and stop conditions.

#### **Start Condition**

All commands to the X9409 are preceded by the start condition, which is a HIGH to LOW transition of SDA while SCL is HIGH ( $t_{HIGH}$ ). The X9409 continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition is met.

## **Stop Condition**

All communications must be terminated by a stop condition, which is a LOW to HIGH transition of SDA while SCL is HIGH.

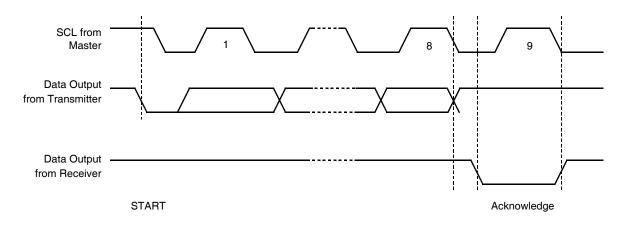

#### Acknowledge

Acknowledge is a software convention used to provide a positive handshake between the master and slave devices on the bus to indicate the successful receipt of data. The transmitting device, either the master or the slave, will release the SDA bus after transmitting eight bits. The master generates a ninth clock cycle and during this period the receiver pulls the SDA line LOW to acknowledge that it successfully received the eight bits of data.

The X9409 will respond with an acknowledge after recognition of a start condition and its slave address and once again after successful receipt of the command byte. If the command is followed by a data byte the X9409 will respond with a final acknowledge.

#### **Array Description**

The X9409 is comprised of four resistor arrays. Each array contains 63 discrete resistive segments that are connected in series. The physical ends of each array are equivalent to the fixed terminals of a mechanical potentiometer ( $V_H/R_H$  and  $V_L/R_L$  inputs).

At both ends of each array and between each resistor segment is a CMOS switch connected to the wiper  $(V_W/R_W)$  output. Within each individual array only one switch may be turned on at a time. These switches are

controlled by the Wiper Counter Register (WCR). The six bits of the WCR are decoded to select, and enable, one of sixty-four switches.

The WCR may be written directly, or it can be changed by transferring the contents of one of four associated Data Registers into the WCR. These Data Registers and the WCR can be read and written by the host system.

#### **Device Addressing**

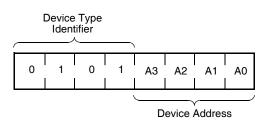

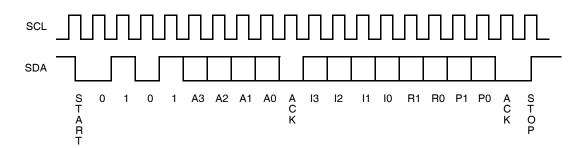

Following a start condition the master must output the address of the slave it is accessing. The most significant four bits of the slave address are the device type identifier (refer to Figure 1 below). For the X9409 this is fixed as 0101[B].

#### Figure 1. Slave Address

The next four bits of the slave address are the device address. The physical device address is defined by the state of the A0 - A3 inputs. The X9409 compares the serial data stream with the address input state; a successful compare of all four address bits is required for the X9409 to respond with an acknowledge. The A<sub>0</sub> - A<sub>3</sub> inputs can be actively driven by CMOS input signals or tied to V<sub>CC</sub> or V<sub>SS</sub>.

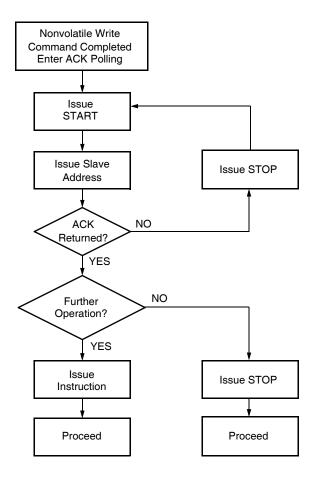

#### Acknowledge Polling

The disabling of the inputs, during the internal nonvolatile write operation, can be used to take advantage of the typical nonvolatile write cycle time. Once the stop condition is issued to indicate the end of the nonvolatile write command the X9409 initiates the internal write cycle. ACK polling can be initiated immediately. This involves issuing the start condition followed by the device slave address. If the X9409 is still busy with the write operation no ACK will be returned. If the X9409 has completed the write operation an ACK will be returned and the master can then proceed with the next operation.

#### Flow 1. ACK Polling Sequence

#### Instruction Structure

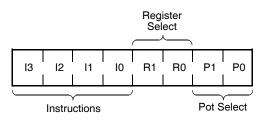

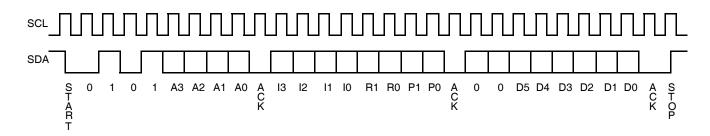

The next byte sent to the X9409 contains the instruction and register pointer information. The format is shown in Figure 2.

#### Figure 2. Instruction Byte Format

The four high order bits define the instruction. The next two bits (R1 and R0) select one of the four registers that is to be acted upon when a register oriented instruction is issued. The last bits (P1, P0) select which one of the four potentiometers is to be affected by the instruction.

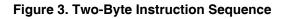

Four of the nine instructions end with the transmission of the instruction byte. The basic sequence is illustrated in Figure 3. These two-byte instructions exchange data between the Wiper Counter Register and one of the data registers. A transfer from a Data Register to a Wiper Counter Register is essentially a write to a static RAM. The response of the wiper to this action will be delayed  $t_{WRL}$ . A transfer from the Wiper Counter Register (current wiper position), to a Data Register is a write to nonvolatile memory and takes a minimum of  $t_{WR}$  to complete. The transfer can occur between one of the four potentiometers and one of its associated registers; or it may occur globally, wherein the transfer occurs between all of the potentiometers and one of their associated registers.

Four instructions require a three-byte sequence to complete. These instructions transfer data between the host and the X9409; either between the host and one of the data registers or directly between the host and the Wiper Counter Register. These instructions are: Read Wiper Counter Register (read the current wiper position of the selected pot), Write Wiper Counter Register (change current wiper position of the selected pot), Read Data Register (read the contents of the selected nonvolatile register) and Write Data Register (write a new value to the selected Data Register). The sequence of operations is shown in Figure 4.

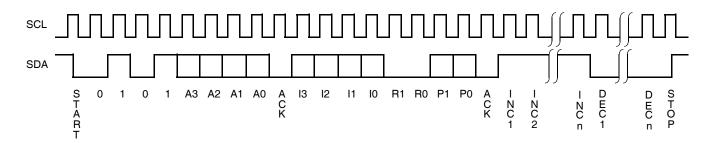

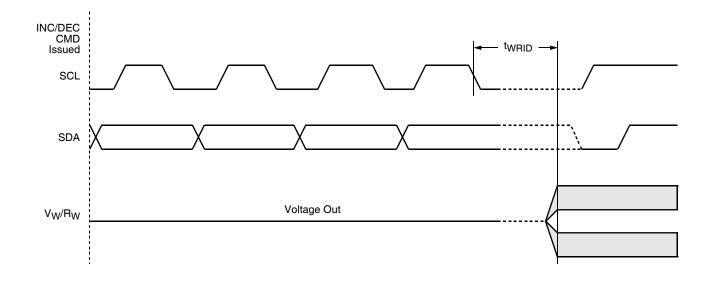

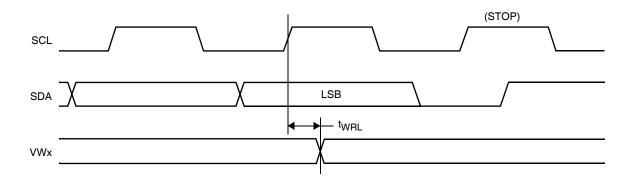

The Increment/Decrement command is different from the other commands. Once the command is issued and the X9409 has responded with an acknowledge, the master can clock the selected wiper up and/or down in one segment steps; thereby, providing a fine tuning capability to the host. For each SCL clock pulse (t<sub>HIGH</sub>) while SDA is HIGH, the selected wiper will move one resistor segment towards the V<sub>H</sub>/R<sub>H</sub> terminal. Similarly, for each SCL clock pulse while SDA is LOW, the selected wiper will move one resistor segment towards the V<sub>L</sub>/R<sub>L</sub> terminal. A detailed illustration of the sequence and timing for this operation are shown in Figures 5 and 6 respectively.

|                                                            |                |                | Ir             | nstru          | ction          | Set            |                |                       |                                                                                                                                     |

|------------------------------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Instruction                                                | l <sub>3</sub> | I <sub>2</sub> | I <sub>1</sub> | I <sub>0</sub> | R <sub>1</sub> | R <sub>0</sub> | P <sub>1</sub> | <b>P</b> <sub>0</sub> | Operation                                                                                                                           |

| Read Wiper Counter<br>Register                             | 1              | 0              | 0              | 1              | 0              | 0              | P <sub>1</sub> | P <sub>0</sub>        | Read the contents of the Wiper Counter Register pointed to by $P_1 - P_0$                                                           |

| Write Wiper Counter<br>Register                            | 1              | 0              | 1              | 0              | 0              | 0              | P <sub>1</sub> | P <sub>0</sub>        | Write new value to the Wiper Counter Register pointed to by $P_1 - P_0$                                                             |

| Read Data Register                                         | 1              | 0              | 1              | 1              | R <sub>1</sub> | R <sub>0</sub> | P <sub>1</sub> | P <sub>0</sub>        | Read the contents of the Data Register pointed to by $P_1 - P_0$ and $R_1 - R_0$                                                    |

| Write Data Register                                        | 1              | 1              | 0              | 0              | R <sub>1</sub> | R <sub>0</sub> | P <sub>1</sub> | P <sub>0</sub>        | Write new value to the Data Register pointed to by $P_1 - P_0$ and $R_1 - R_0$                                                      |

| XFR Data Register to<br>Wiper Counter Register             | 1              | 1              | 0              | 1              | R <sub>1</sub> | R <sub>0</sub> | P <sub>1</sub> | P <sub>0</sub>        | Transfer the contents of the Data Register pointed to by $P_1 - P_0$ and $R_1 - R_0$ to its associated Wiper Counter Register       |

| XFR Wiper Counter<br>Register to Data<br>Register          | 1              | 1              | 1              | 0              | R <sub>1</sub> | R <sub>0</sub> | P <sub>1</sub> | P <sub>0</sub>        | Transfer the contents of the Wiper Counter Register pointed to by $P_1 - P_0$ to the Data Register pointed to by $R_1 - R_0$        |

| Global XFR Data<br>Registers to Wiper<br>Counter Registers | 0              | 0              | 0              | 1              | R <sub>1</sub> | R <sub>0</sub> | 0              | 0                     | Transfer the contents of the Data Registers pointed to by $R_1 - R_0$ of all four pots to their respective Wiper Counter Registers  |

| Global XFR Wiper<br>Counter Registers to<br>Data Register  | 1              | 0              | 0              | 0              | R <sub>1</sub> | R <sub>0</sub> | 0              | 0                     | Transfer the contents of both Wiper Counter Registers to their respective Data Registers pointed to by $R_1 - R_0$ of all four pots |

| Increment/Decrement<br>Wiper Counter Register              | 0              | 0              | 1              | 0              | 0              | 0              | P <sub>1</sub> | P <sub>0</sub>        | Enable Increment/decrement of the WCR Latch pointed to by $P_1 - P_0$                                                               |

#### Table 1. Instruction Set

**Note:** (7) 1/0 = data is one or zero

## Figure 4. Three-Byte Instruction Sequence

## Figure 5. Increment/Decrement Instruction Sequence

Figure 6. Increment/Decrement Timing Limits

Figure 8. Detailed Potentiometer Block Diagram

## DETAILED OPERATION

All XDCP potentiometers share the serial interface and share a common architecture. Each potentiometer has a Wiper Counter Register and 4 Data Registers. A detailed discussion of the register organization and array operation follows.

#### Wiper Counter Register

The X9409 contains four Wiper Counter Registers, one for each XDCP potentiometer. The Wiper Counter Register can be envisioned as a 6-bit parallel and serial load counter with its outputs decoded to select one of sixty-four switches along its resistor array. The contents of the WCR can be altered in four ways: it may be written directly by the host via the Write Wiper Counter Register instruction (serial load); it may be written indirectly by transferring the contents of one of the four associated Data Registers via the XFR Data Register instruction (parallel load); it can be modified one step at a time by the Increment/ Decrement instruction. Finally, it is loaded with the contents of its Data Register zero (DR0) upon power-up.

The WCR is a volatile register; that is, its contents are lost when the X9409 is powered-down. Although the register is automatically loaded with the value in DR0 upon power-up, it should be noted this may be different from the value present at power-down.

#### **Data Registers**

Each potentiometer has four nonvolatile Data Registers. These can be read or written directly by the host and data can be transferred between any of the four Data Registers and the Wiper Counter Register. It should be noted all operations changing data in one of these registers is a nonvolatile operation and will take a maximum of 10ms. If the application does not require storage of multiple settings for the potentiometer, these registers can be used as regular memory locations that could possibly store system parameters or user preference data.

#### **Register Descriptions**

#### Data Registers, (6-Bit), Nonvolatile:

| D5    | D4 | D3 | D2 | D1 | D0    |

|-------|----|----|----|----|-------|

| NV    | NV | NV | NV | NV | NV    |

| (MSB) |    |    |    |    | (LSB) |

Four 6-bit Data Registers for each XDCP. (sixteen 6-bit registers in total).

- {D5~D0}: These bits are for general purpose not volatile data storage or for storage of up to four different wiper values. The contents of Data Register 0 are automatically moved to the wiper counter register on power-up.

#### Wiper Counter Register, (6-Bit), Volatile:

| WP5   | WP4 | WP3 | WP2 | WP1 | WP0   |

|-------|-----|-----|-----|-----|-------|

| V     | V   | V   | V   | V   | V     |

| (MSB) |     |     |     |     | (LSB) |

One 6-bit Wiper Counter Register for each XDCP. (Four 6-bit registers in total.)

- {D5~D0}: These bits specify the wiper position of the respective XDCP. The Wiper Counter Register is loaded on power-up by the value in Data Register  $R_0$ . The contents of the WCR can be loaded from any of the other Data Register or directly by command. The contents of the WCR can be saved in a DR.

#### Instruction Format

**Notes:** (1) "MACK"/"SACK": stands for the acknowledge sent by the master/slave.

- (2) "A3 ~ A0": stands for the device addresses sent by the master.

- (3) "X": indicates that it is a "0" for testing purpose but physically it is a "don't care" condition.

- (4) "I": stands for the increment operation, SDA held high during active SCL phase (high).

- (5) "D": stands for the decrement operation, SDA held low during active SCL phase (high).

#### Read Wiper Counter Register (WCR)

| S<br>T      | de\<br>id |   | e ty<br>tifie |   |        | de\<br>ddre |        |        | S<br>A |   | stru<br>opc |   |   | a |   | CR<br>esse | es     | S<br>A | (5 | sent | -           | -           |             | tion<br>on S |             | ۹)          | M<br>A | S<br>T |

|-------------|-----------|---|---------------|---|--------|-------------|--------|--------|--------|---|-------------|---|---|---|---|------------|--------|--------|----|------|-------------|-------------|-------------|--------------|-------------|-------------|--------|--------|

| A<br>R<br>T | 0         | 1 | 0             | 1 | A<br>3 | A<br>2      | A<br>1 | A<br>0 | C<br>K | 1 | 0           | 0 | 1 | 0 | 0 | P<br>1     | P<br>0 | C<br>K | 0  | 0    | W<br>P<br>5 | W<br>P<br>4 | W<br>P<br>3 | W<br>P<br>2  | W<br>P<br>1 | W<br>P<br>0 | C<br>K | O<br>P |

#### Write Wiper Counter Register (WCR)

| S<br>T      |   | vice<br>den |   |   |        |        | /ice<br>esse |        | S<br>A |   | stru<br>opc |   |   | a | W0<br>ddre |        | es     | S<br>A | (s |   | wip<br>by ı | •           |             |             | SD          | A)          | S<br>A | S<br>T |

|-------------|---|-------------|---|---|--------|--------|--------------|--------|--------|---|-------------|---|---|---|------------|--------|--------|--------|----|---|-------------|-------------|-------------|-------------|-------------|-------------|--------|--------|

| A<br>R<br>T | 0 | 1           | 0 | 1 | A<br>3 | A<br>2 | A<br>1       | A<br>0 | C<br>K | 1 | 0           | 1 | 0 | 0 | 0          | P<br>1 | P<br>0 | C<br>K | 0  | 0 | W<br>P<br>5 | W<br>P<br>4 | W<br>P<br>3 | W<br>P<br>2 | W<br>P<br>1 | W<br>P<br>0 | C<br>K | O<br>P |

## Read Data Register (DR)

| S<br>T      |   | evico<br>den |   |   |        |        | vice<br>esse |        | S<br>A |   |   | uctio<br>ode |   |        | ano<br>ddre |        |        | S<br>A | (5 | sent | •           | •           | osi<br>ve d |             |             | ۹)          | M<br>A | S<br>T |

|-------------|---|--------------|---|---|--------|--------|--------------|--------|--------|---|---|--------------|---|--------|-------------|--------|--------|--------|----|------|-------------|-------------|-------------|-------------|-------------|-------------|--------|--------|

| A<br>R<br>T | 0 | 1            | 0 | 1 | A<br>3 | A<br>2 | A<br>1       | A<br>0 | C<br>K | 1 | 0 | 1            | 1 | R<br>1 | R<br>0      | P<br>1 | P<br>0 | C<br>K | 0  | 0    | W<br>P<br>5 | W<br>P<br>4 | W<br>P<br>3 | W<br>P<br>2 | W<br>P<br>1 | W<br>P<br>0 | C<br>K | O<br>P |

## Write Data Register (DR)

| S           | device type | device                 | instruction | DR and WCR             | wiper position                                                                                                                                                                                                        | S S        | HIGH-VOLTAGE |

|-------------|-------------|------------------------|-------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|

| T           | identifier  | addresses A            | opcode      | addresses              | (sent by master on SDA)                                                                                                                                                                                               | A T        |              |

| A<br>R<br>T | 0 1 0 1     | A A A A C<br>3 2 1 0 K | 1 1 0 0     | R R P P C<br>1 0 1 0 K | W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W W | С О<br>К Р | WRITE CYCLE  |

## Transfer Data Register (DR) to Wiper Counter Register (WCR)

| S<br>T      |   |   | e ty<br>tifie | • |        | dev<br>ddre |        |        | S<br>A |   |   | ictic<br>ode |   |        | l and<br>ddre |        |        | S<br>A | S<br>T |

|-------------|---|---|---------------|---|--------|-------------|--------|--------|--------|---|---|--------------|---|--------|---------------|--------|--------|--------|--------|

| A<br>R<br>T | 0 | 1 | 0             | 1 | A<br>3 | A<br>2      | A<br>1 | A<br>0 | С<br>К | 1 | 1 | 0            | 1 | R<br>1 | R<br>0        | P<br>1 | P<br>0 | C<br>K | O<br>P |

## Write Wiper Counter Register (WCR) to Data Register (DR)

| S<br>T      |   |   | e ty<br>tifie | • |        |        | /ice<br>esse |        | S<br>A |   |   | uctio<br>ode |   |        |        | d W<br>esse |        | S<br>A | S<br>T | HIGH-VOLTAGE |

|-------------|---|---|---------------|---|--------|--------|--------------|--------|--------|---|---|--------------|---|--------|--------|-------------|--------|--------|--------|--------------|

| A<br>R<br>T | 0 | 1 | 0             | 1 | A<br>3 | A<br>2 | A<br>1       | A<br>0 | C<br>K | 1 | 1 | 1            | 0 | R<br>1 | R<br>0 | P<br>1      | P<br>0 | С<br>К | O<br>P | WRITE CYCLE  |

| S<br>T      |   |   | e ty<br>tifie |   |        | dev<br>ddre |        |        | S<br>A |   | istru<br>opc |   |   | a | W0<br>ddre | CR<br>esse | es     | S<br>A |         | -       | eme<br>by i |  | - | -       |         | S<br>T |

|-------------|---|---|---------------|---|--------|-------------|--------|--------|--------|---|--------------|---|---|---|------------|------------|--------|--------|---------|---------|-------------|--|---|---------|---------|--------|

| A<br>R<br>T | 0 | 1 | 0             | 1 | A<br>3 | A<br>2      | A<br>1 | A<br>0 | C<br>K | 0 | 0            | 1 | 0 | 0 | 0          | P<br>1     | P<br>0 | C<br>K | l/<br>D | I/<br>D | •           |  |   | l/<br>D | l/<br>D | O<br>P |

## Global Transfer Data Register (DR) to Wiper Counter Register (WCR)

| S<br>T      |   |   | e ty<br>tifie |   | a      | de\<br>ddre |        |        | S<br>A |   |   | ictic<br>ode |   | a      | _      | R<br>esse | es | S<br>A | S<br>T |

|-------------|---|---|---------------|---|--------|-------------|--------|--------|--------|---|---|--------------|---|--------|--------|-----------|----|--------|--------|

| A<br>R<br>T | 0 | 1 | 0             | 1 | A<br>3 | A<br>2      | A<br>1 | A<br>0 | C<br>K | 0 | 0 | 0            | 1 | R<br>1 | R<br>0 | 0         | 0  | C<br>K | O<br>P |

## Global Transfer Wiper Counter Register (WCR) to Data Register (DR)

| S<br>T      |   |   | e ty<br>tifie | - |        | de\<br>ddre |        |        | S<br>A |   |   | uctio<br>ode |   | ac     | D<br>ddre | •• | es | S<br>A | S<br>T | HIGH-VOLTAGE |

|-------------|---|---|---------------|---|--------|-------------|--------|--------|--------|---|---|--------------|---|--------|-----------|----|----|--------|--------|--------------|

| A<br>R<br>T | 0 | 1 | 0             | 1 | A<br>3 | A<br>2      | A<br>1 | A<br>0 | C<br>K | 1 | 0 | 0            | 0 | R<br>1 | R<br>0    | 0  | 0  | C<br>K | O<br>P | WRITE CYCLE  |

## SYMBOL TABLE

| WAVEFORM | INPUTS                            | OUTPUTS                             |

|----------|-----------------------------------|-------------------------------------|

|          | Must be<br>steady                 | Will be<br>steady                   |

|          | May change<br>from Low to<br>High | Will change<br>from Low to<br>High  |

|          | May change<br>from High to<br>Low | Will change<br>from High to<br>Low  |

|          | Don't Care:<br>Changes<br>Allowed | Changing:<br>State Not<br>Known     |

|          | N/A                               | Center Line<br>is High<br>Impedance |

# Guidelines for Calculating Typical Values of Bus Pull-Up Resistors

#### **ABSOLUTE MAXIMUM RATINGS**

| Temperature under bias                | -65°C to +135°C |

|---------------------------------------|-----------------|

| Storage temperature                   | -65°C to +150°C |

| Voltage on SDA, SCL or any address    |                 |

| input with respect to V <sub>SS</sub> | 1V to +7V       |

| $\Delta V =  V_{H} - V_{L}  \dots$    | 5V              |

| Lead temperature (soldering, 10s)     | +300°C          |

#### COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device (at these or any other conditions above those listed in the operational sections of this specification) is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Temp       | Min.  | Max.  | ] | Device    | Supply Voltage (V <sub>CC</sub> ) Limits |

|------------|-------|-------|---|-----------|------------------------------------------|

| Commercial | 0°C   | +70°C |   | X9409-2.7 | 2.7V to 5.5V                             |

| Industrial | -40°C | +85°C | ] |           |                                          |

#### **ANALOG CHARACTERISTICS** (Over recommended operating conditions unless otherwise stated.)

|                                                |                                           |                 | Lin      | nits            |                   |                                                             |

|------------------------------------------------|-------------------------------------------|-----------------|----------|-----------------|-------------------|-------------------------------------------------------------|

| Symbol                                         | Parameter                                 | Min.            | Тур.     | Max.            | Unit              | Test Conditions                                             |

|                                                | End to end resistance tolerance           |                 |          | ±20             | %                 |                                                             |

|                                                | Power rating                              |                 |          | 15              | mW                | 25°C, each pot @5V, 2.5K                                    |

| Iw                                             | Wiper current                             | -3              |          | +3              | mA                |                                                             |

| R <sub>W</sub>                                 | Wiper resistance                          |                 | 50       | 150             | Ω                 | $I_W = \pm 3$ mA, $V_{CC} = 3V$ to 5V                       |

| V <sub>TERM</sub>                              | Voltage on any $V_H/R_H$ or $V_L/R_L$ pin | V <sub>SS</sub> |          | V <sub>CC</sub> | V                 | $V_{SS} = 0V$                                               |

|                                                | Noise                                     |                 | -120     |                 | dBV               | Ref: 1kHz                                                   |

|                                                | Resolution <sup>(4)</sup>                 |                 | 1.6      |                 | %                 |                                                             |

|                                                | Absolute linearity <sup>(1)</sup>         | -1              |          | +1              | MI <sup>(3)</sup> | V <sub>w(n)(actual)</sub> - V <sub>w(n)(expected)</sub>     |

|                                                | Relative linearity <sup>(2)</sup>         | -0.2            |          | +0.2            | MI <sup>(3)</sup> | $V_{w(n + 1)} - [V_{w(n) + MI}]$                            |

|                                                | Temperature coefficient of RTOTAL         |                 | ±300     |                 | ppm/°C            |                                                             |

|                                                | Ratiometric temp. coefficient             |                 |          | 20              | ppm/°C            |                                                             |

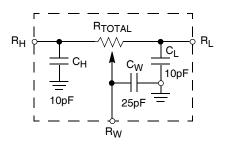

| C <sub>H</sub> /C <sub>L</sub> /C <sub>W</sub> | Potentiometer capacitances                |                 | 10/10/25 |                 | pF                | See Macro Model                                             |

| I <sub>AL</sub>                                | $R_{H}, R_{L}, R_{W}$ leakage current     |                 | 0.1      | 10              | μA                | $V_{IN} = V_{SS}$ to $V_{CC}$ . Device is in stand-by mode. |

Notes: (1) Absolute Linearity is utilized to determine actual wiper voltage versus expected voltage as determined by wiper position when used as a potentiometer.

(2) Relative Linearity is utilized to determine the actual change in voltage between two successive tap positions when used as a potentiometer. It is a measure of the error in step size.

(3) MI = RTOT/63 or  $(V_H - V_L)/63$ , single pot

## D.C. OPERATING CHARACTERISTICS

(Over the recommended operating conditions unless otherwise specified.)

|                  |                                                       |                       | Lin  | nits                  |      |                                                                          |

|------------------|-------------------------------------------------------|-----------------------|------|-----------------------|------|--------------------------------------------------------------------------|

| Symbol           | Parameter                                             | Min.                  | Тур. | Max.                  | Unit | Test Conditions                                                          |

| ICC1             | V <sub>CC</sub> supply current (Active)               |                       |      | 100                   | μA   | f <sub>SCL</sub> = 400kHz, SDA = Open,<br>Other Inputs = V <sub>SS</sub> |

| I <sub>CC2</sub> | V <sub>CC</sub> supply current<br>(Nonvolatile Write) |                       |      | 1                     | mA   | f <sub>SCL</sub> = 400kHz, SDA = Open,<br>Other Inputs = V <sub>SS</sub> |

| I <sub>SB</sub>  | V <sub>CC</sub> current (standby)                     |                       |      | 1                     | μA   | $SCL = SDA = V_{CC}$ , Addr. = $V_{SS}$                                  |

| ILI              | Input leakage current                                 |                       |      | 10                    | μA   | $V_{IN} = V_{SS}$ to $V_{CC}$                                            |

| ILO              | Output leakage current                                |                       |      | 10                    | μA   | $V_{OUT} = V_{SS}$ to $V_{CC}$                                           |

| VIH              | Input HIGH voltage                                    | V <sub>CC</sub> x 0.7 |      | V <sub>CC</sub> + 0.5 | V    |                                                                          |

| V <sub>IL</sub>  | Input LOW voltage                                     | -0.5                  |      | V <sub>CC</sub> x 0.1 | V    |                                                                          |

| V <sub>OL</sub>  | Output LOW voltage                                    |                       |      | 0.4                   | V    | I <sub>OL</sub> = 3mA                                                    |

#### ENDURANCE AND DATA RETENTION

| Parameter         | Min.    | Unit                              |

|-------------------|---------|-----------------------------------|

| Minimum endurance | 100,000 | Data changes per bit per register |

| Data retention    | 100     | Years                             |

#### CAPACITANCE

| Symbol                          | Test                                        | Max. | Unit | Test Conditions |

|---------------------------------|---------------------------------------------|------|------|-----------------|

| C <sub>I/O</sub> <sup>(4)</sup> | Input/output capacitance (SDA)              | 8    | pF   | $V_{I/O} = 0V$  |

| C <sub>IN</sub> <sup>(4)</sup>  | Input capacitance (A0, A1, A2, A3, and SCL) | 6    | pF   | $V_{IN} = 0V$   |

#### **POWER-UP TIMING**

| Symbol                                        | Parameter                     | Min. | Max. | Unit |

|-----------------------------------------------|-------------------------------|------|------|------|

| t <sub>r</sub> V <sub>CC</sub> <sup>(6)</sup> | V <sub>CC</sub> power-up rate | 0.2  | 50   | V/ms |

POWER-UP REQUIREMENTS (Power-up sequencing can affect correct recall of the wiper registers)

The preferred power-on sequence is as follows: First V<sub>CC</sub>, then the potentiometer pins, R<sub>H</sub>, R<sub>L</sub>, and R<sub>W</sub>. The V<sub>CC</sub> ramp rate specification should be met, and any glitches or slope changes in the V<sub>CC</sub> line should be held to <100mV if possible. If V<sub>CC</sub> powers down, it should be held below 0.1V for more than 1 second before powering up again in order for proper wiper register recall. Also, V<sub>CC</sub> should not reverse polarity by more than 0.5V. Recall of wiper position will not be complete until V<sub>CC</sub> reaches its final value.

**Notes:** (4) This parameter is periodically sampled and not 100% tested

(5) t<sub>PUR</sub> and t<sub>PUW</sub> are the delays required from the time the (last) power supply (V<sub>CC</sub>) is stable until the specific instruction can be issued. These parameters are periodically sampled and not 100% tested.

(6) Sample tested only.

## A.C. TEST CONDITIONS

| Input pulse levels            | V <sub>CC</sub> x 0.1 to V <sub>CC</sub> x 0.9 |

|-------------------------------|------------------------------------------------|

| Input rise and fall times     | 10ns                                           |

| Input and output timing level | V <sub>CC</sub> x 0.5                          |

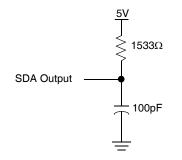

## EQUIVALENT A.C. LOAD CIRCUIT

## Circuit #3 SPICE Macro Model

AC TIMING (over recommended operating condition)

| Symbol              | Parameter                                             | Min. | Max. | Unit |

|---------------------|-------------------------------------------------------|------|------|------|

| f <sub>SCL</sub>    | Clock frequency                                       |      | 400  | kHz  |

| <sup>t</sup> CYC    | Clock cycle time                                      | 2500 |      | ns   |

| thigh               | Clock high time                                       | 600  |      | ns   |

| <sup>t</sup> LOW    | Clock low time                                        | 1300 |      | ns   |

| <sup>t</sup> SU:STA | Start setup time                                      | 600  |      | ns   |

| <sup>t</sup> HD:STA | Start hold time                                       | 600  |      | ns   |

| <sup>t</sup> s∪:sto | Stop setup time                                       | 600  |      | ns   |

| <sup>t</sup> SU:DAT | SDA data input setup time                             | 100  |      | ns   |

| <sup>t</sup> HD:DAT | SDA data input hold time                              | 30   |      | ns   |

| t <sub>R</sub>      | SCL and SDA rise time                                 |      | 300  | ns   |

| t <sub>F</sub>      | SCL and SDA fall time                                 |      | 300  | ns   |

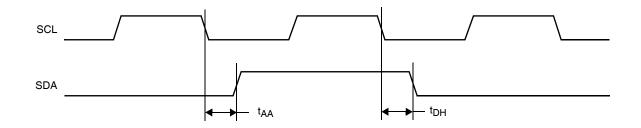

| t <sub>AA</sub>     | SCL low to SDA data output valid time                 |      | 900  | ns   |

| <sup>t</sup> DH     | SDA data output hold time                             | 50   |      | ns   |

| т <sub>I</sub>      | Noise suppression time constant at SCL and SDA inputs | 50   |      | ns   |

| <sup>t</sup> BUF    | Bus free time (prior to any transmission)             | 1300 |      | ns   |

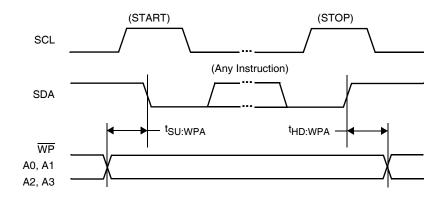

| <sup>t</sup> SU:WPA | WP, A0, A1, A2 and A3 setup time                      | 0    |      | ns   |

| <sup>t</sup> HD:WPA | WP, A0, A1, A2 and A3 hold time                       | 0    |      | ns   |

#### HIGH-VOLTAGE WRITE CYCLE TIMING

| Symbol          | Parameter                                          | Тур. | Max. | Unit |

|-----------------|----------------------------------------------------|------|------|------|

| <sup>t</sup> WR | High-voltage write cycle time (store instructions) | 5    | 10   | ms   |

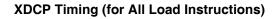

## **XDCP TIMING**

| Symbol            | Parameter                                                                         | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------------------------------------------------|------|------|------|------|

| twrpo             | Wiper response time after the third (last) power supply is stable                 |      | 2    | 10   | μs   |

| twRL              | Wiper response time after instruction issued (all load instructions)              |      | 2    | 10   | μs   |

| <sup>t</sup> WRID | Wiper response time from an active SCL/SCK edge (increment/decrement instruction) |      | 2    | 10   | μs   |

Note: (9) A device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

## TIMING DIAGRAMS

## **START and STOP Timing**

## Input Timing

## **Output Timing**

## **APPLICATIONS INFORMATION**

#### **Basic Configurations of Electronic Potentiometers**

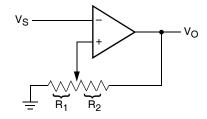

Three terminal Potentiometer; Variable voltage divider

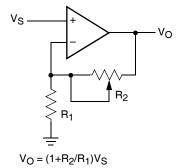

#### NONINVERTING AMPLIFIER

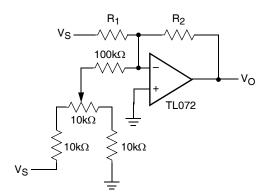

#### OFFSET VOLTAGE ADJUSTMENT

Two terminal Variable Resistor; Variable current

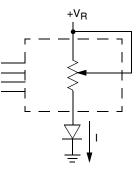

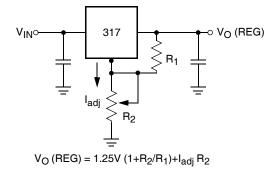

VOLTAGE REGULATOR

COMPARATOR WITH HYSTERESIS

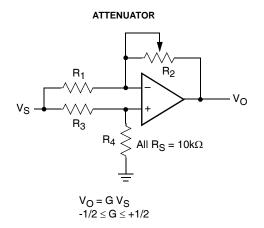

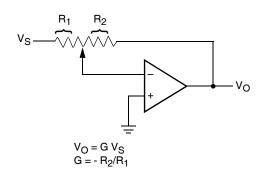

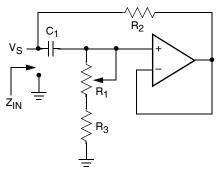

## **Application Circuits (continued)**

$V_S$   $V_S$   $V_C$   $V_C$

FILTER

INVERTING AMPLIFIER

EQUIVALENT L-R CIRCUIT

$$\begin{split} Z_{IN} = R_2 + s \; R_2 \; (R_1 + R_3) \; C_1 = R_2 + s \; \text{Leq} \\ (R_1 + R_3) >> R_2 \end{split}$$

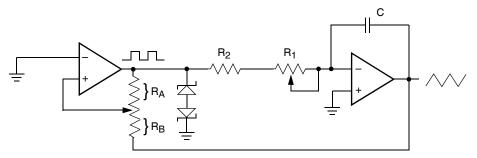

#### FUNCTION GENERATOR

$\begin{array}{l} \mbox{frequency} \propto R_1,\,R_2,\,C \\ \mbox{amplitude} \propto R_A,\,R_B \end{array}$

## XDCP Timing (for Increment/Decrement Instruction)

#### Write Protect and Device Address Pins Timing

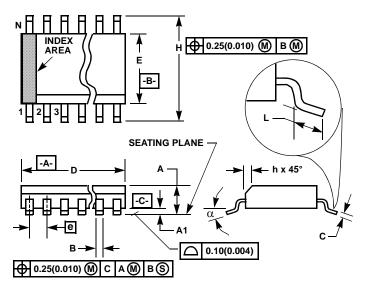

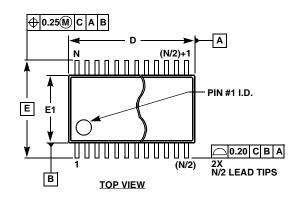

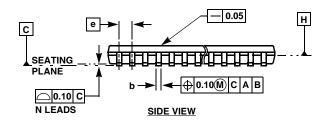

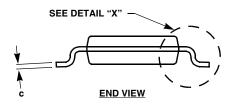

# Small Outline Plastic Packages (SOIC)

#### NOTES:

- 1. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. The lead width "B", as measured 0.36mm (0.014 inch) or greater

- above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch)

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

#### **M24.3** (JEDEC MS-013-AD ISSUE C) 24 LEAD WIDE BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INC    | HES    | MILLI    |       |       |

|--------|--------|--------|----------|-------|-------|

| SYMBOL | MIN    | MAX    | MIN      | MAX   | NOTES |

| А      | 0.0926 | 0.1043 | 2.35     | 2.65  | -     |

| A1     | 0.0040 | 0.0118 | 0.10     | 0.30  | -     |

| В      | 0.013  | 0.020  | 0.33     | 0.51  | 9     |

| С      | 0.0091 | 0.0125 | 0.23     | 0.32  | -     |

| D      | 0.5985 | 0.6141 | 15.20    | 15.60 | 3     |

| Е      | 0.2914 | 0.2992 | 7.40     | 7.60  | 4     |

| е      | 0.05   | BSC    | 1.27 BSC |       | -     |

| Н      | 0.394  | 0.419  | 10.00    | 10.65 | -     |

| h      | 0.010  | 0.029  | 0.25     | 0.75  | 5     |

| L      | 0.016  | 0.050  | 0.40     | 1.27  | 6     |

| Ν      | 2      | 4      |          | 24    | 7     |

| α      | 0°     | 8°     | 0°       | 8°    | -     |

Rev. 1 4/06

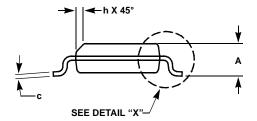

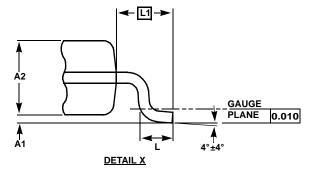

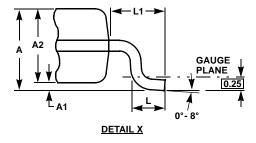

#### **MDP0027**

SMALL OUTLINE PACKAGE FAMILY (SO)

| SYMBOL | SO-8  | SO-14 | SO16<br>(0.150") | SO16 (0.300")<br>(SOL-16) | SO20<br>(SOL-20) | SO24<br>(SOL-24) | SO28<br>(SOL-28) | TOLERANCE | NOTES |

|--------|-------|-------|------------------|---------------------------|------------------|------------------|------------------|-----------|-------|

| Α      | 0.068 | 0.068 | 0.068            | 0.104                     | 0.104            | 0.104            | 0.104            | MAX       | -     |

| A1     | 0.006 | 0.006 | 0.006            | 0.007                     | 0.007            | 0.007            | 0.007            | ±0.003    | -     |

| A2     | 0.057 | 0.057 | 0.057            | 0.092                     | 0.092            | 0.092            | 0.092            | ±0.002    | -     |

| b      | 0.017 | 0.017 | 0.017            | 0.017                     | 0.017            | 0.017            | 0.017            | ±0.003    | -     |

| С      | 0.009 | 0.009 | 0.009            | 0.011                     | 0.011            | 0.011            | 0.011            | ±0.001    | -     |

| D      | 0.193 | 0.341 | 0.390            | 0.406                     | 0.504            | 0.606            | 0.704            | ±0.004    | 1, 3  |

| Е      | 0.236 | 0.236 | 0.236            | 0.406                     | 0.406            | 0.406            | 0.406            | ±0.008    | -     |

| E1     | 0.154 | 0.154 | 0.154            | 0.295                     | 0.295            | 0.295            | 0.295            | ±0.004    | 2, 3  |

| е      | 0.050 | 0.050 | 0.050            | 0.050                     | 0.050            | 0.050            | 0.050            | Basic     | -     |

| L      | 0.025 | 0.025 | 0.025            | 0.030                     | 0.030            | 0.030            | 0.030            | ±0.009    | -     |

| L1     | 0.041 | 0.041 | 0.041            | 0.056                     | 0.056            | 0.056            | 0.056            | Basic     | -     |

| h      | 0.013 | 0.013 | 0.013            | 0.020                     | 0.020            | 0.020            | 0.020            | Reference | -     |

| Ν      | 8     | 14    | 16               | 16                        | 20               | 24               | 28               | Reference | -     |

NOTES:

Rev. L 2/01

1. Plastic or metal protrusions of 0.006" maximum per side are not included.

2. Plastic interlead protrusions of 0.010" maximum per side are not included.

3. Dimensions "D" and "E1" are measured at Datum Plane "H".

4. Dimensioning and tolerancing per ASME Y14.5M-1994

## X9409

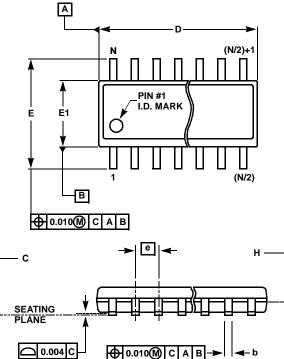

# Thin Shrink Small Outline Package Family (TSSOP)

## MDP0044

THIN SHRINK SMALL OUTLINE PACKAGE FAMILY

| SYMBOL | 14 LD | 16 LD | 20 LD | 24 LD | 28 LD | TOLERANCE    |

|--------|-------|-------|-------|-------|-------|--------------|

| Α      | 1.20  | 1.20  | 1.20  | 1.20  | 1.20  | Max          |

| A1     | 0.10  | 0.10  | 0.10  | 0.10  | 0.10  | ±0.05        |

| A2     | 0.90  | 0.90  | 0.90  | 0.90  | 0.90  | ±0.05        |

| b      | 0.25  | 0.25  | 0.25  | 0.25  | 0.25  | +0.05/-0.06  |

| С      | 0.15  | 0.15  | 0.15  | 0.15  | 0.15  | +0.05/-0.06  |

| D      | 5.00  | 5.00  | 6.50  | 7.80  | 9.70  | ±0.10        |

| E      | 6.40  | 6.40  | 6.40  | 6.40  | 6.40  | Basic        |

| E1     | 4.40  | 4.40  | 4.40  | 4.40  | 4.40  | ±0.10        |

| е      | 0.65  | 0.65  | 0.65  | 0.65  | 0.65  | Basic        |

| L      | 0.60  | 0.60  | 0.60  | 0.60  | 0.60  | ±0.15        |

| L1     | 1.00  | 1.00  | 1.00  | 1.00  | 1.00  | Reference    |

|        |       |       |       |       |       | Rev. E 12/02 |

#### NOTES:

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15mm per side.

- Dimension "E1" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm per side.

- 3. Dimensions "D" and "E1" are measured at dAtum Plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com