Data Sheet September 11, 2008 FN6640.1

## 400MHz Slew Rate Enhanced Rail-to-Rail Output Gain Block

The ISL55036 is a hex, rail-to-rail output, fixed gain amplifier (G = 4) with a -3dB bandwidth of 400MHz and slew rate of 2500V/µs into a 150 $\Omega$  load. The ISL55036 features single supply operation over a voltage range of 3VDC to 5.5VDC. The inputs are capable of sensing ground with an output swing of VCC - 0.3V into a 150 $\Omega$  load tied to V+/2. The part includes a fast-acting global disable/power-down circuit. The ISL55036 is available in a 24 Ld TQFN package. Operation is specified over the -40 $\Omega$  to +85 $\Omega$  temperature range.

## Ordering Information

| PART NUMBER       | PART<br>MARKING | PACKAGE<br>(Pb-free) | PKG.<br>DWG.# |

|-------------------|-----------------|----------------------|---------------|

| ISL55036IRTZ      | 55036 IRTZ      | 24 Ld TQFN           | L24.4x5C      |

| ISL55036IRTZ-T13* | 55036 IRTZ      | 24 Ld TQFN           | L24.4x5C      |

<sup>\*</sup>Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

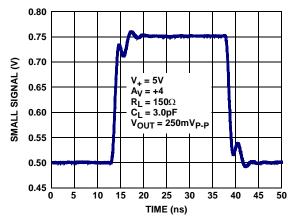

FIGURE 1. SMALL SIGNAL STEP RESPONSE

#### **Features**

- 400MHz -3dB Bandwidth

- 2500V/ $\mu$ s Typical Slew Rate,  $R_L = 150\Omega$

- Supplies from 3V to 5.5V

- Rail-to-Rail Output (R = 1k)

- · Input Ground Sensing

- Fast 25ns Disable

- Low Cost

- Pb-Free (RoHS Compliant)

## **Applications**

- Video RGB Line Driver

- LCD Based Projectors Pixel Control

## **Pinout**

# Pin Descriptions

| 24 LD TQFN | PIN NAME         | EQUIVALENT<br>CIRCUIT | DESCRIPTION                                                                                                                        |

|------------|------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 1          | IN+_2            | Circuit 1             | Amplifier 2 non-inverting input                                                                                                    |

| 2          | IN+_3            | Circuit 1             | Amplifier 3 non-inverting input                                                                                                    |

| 3          | GND_IN(1, 2, 3)  | Circuit 4             | Common reference input for Amplifiers 1, 2, 3                                                                                      |

| 4          | EN(4, 5, 6)      | Circuit 2             | Enable pin internal pull-down; Logic "1" selects the disabled state; Logic "0" selects the enabled state. Channels 4, 5, 6         |

| 5          | V+(4, 5, 6)      | Circuit 5             | Positive power supply for Channels 4, 5, 6.                                                                                        |

| 6          | IN+_4            | Circuit 1             | Amplifier 4 non-inverting input                                                                                                    |

| 7          | IN+_5            | Circuit 1             | Amplifier 5 non-inverting input                                                                                                    |

| 8          | IN+_6            | Circuit 1             | Amplifier 6 non-inverting input                                                                                                    |

| 9          | GND_IN(4, 5, 6)  | Circuit 5             | Common reference input for Amplifiers 4, 5, 6                                                                                      |

| 10         | GND_PWR(4, 5, 6) | Circuit 5             | Power supply ground for Channels 4, 5, 6.                                                                                          |

| 11         | GND_OUT(4, 5, 6) | Circuit 3             | Output power supply ground for Channels 4, 5, 6.                                                                                   |

| 12         | OUT_6            | Circuit 3             | Amplifier 6 output                                                                                                                 |

| 13         | OUT_5            | Circuit 3             | Amplifier 5 output                                                                                                                 |

| 14         | OUT_4            | Circuit 3             | Amplifier 4 output                                                                                                                 |

| 15         | V+_OUT(4, 5, 6)  | Circuit 3             | Output power supply for Channels 4, 5, 6.                                                                                          |

| 16         | GND_PWR(1, 2, 3) | Circuit 4             | Power supply ground Channels 1, 2, 3.                                                                                              |

| 17         | GND_OUT(1, 2, 3) | Circuit 3             | Output power supply ground Channels 1, 2, 3.                                                                                       |

| 18         | OUT_3            | Circuit 3             | Amplifier 3 output                                                                                                                 |

| 19         | OUT_2            | Circuit 3             | Amplifier 2 output                                                                                                                 |

| 20         | OUT_1            | Circuit 3             | Amplifier 1 output                                                                                                                 |

| 21         | V+_OUT(1, 2, 3)  | Circuit 3             | Output power supply Channels 1, 2, 3.                                                                                              |

| 22         | EN(1, 2, 3)      | Circuit 2             | Enable pin internal pull-down; Logic "1" selects the disabled state; Logic "0" selects the enabled state. Channels 1, 2, 3         |

| 23         | V+(1, 2, 3)      | Circuit 4             | Positive power supply for Channels 1, 2, 3.                                                                                        |

| 24         | IN+_1            | Circuit 1             | Amplifier 1 non-inverting input                                                                                                    |

|            | Thermal Pad      | Circuit 6             | Thermal heat sink pad makes electrical contact the IC substrate and must be connected to same ground potential as the ground pins. |

## **Absolute Maximum Ratings** $(T_A = +25^{\circ}C)$

| Supply Voltage from V+ to GND 5.75V |

|-------------------------------------|

| Supply Turn On Voltage Slew Rate    |

| EN Input Current                    |

| Input Voltage                       |

| Continuous Output Current           |

| ESD Rating:                         |

| Human Body Model                    |

| Machine Model300V                   |

## **Thermal Information**

| Thermal Resistance (Typical, Note 1)             | θ <sub>JA</sub> (℃/W) |

|--------------------------------------------------|-----------------------|

| 24 Ld TQFN Package                               | 42                    |

| Storage Temperature                              |                       |

| Pb-free reflow profile                           | ee link below         |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                       |

## **Operating Conditions**

Ambient Operating Temperature .......-40 $^\circ$ to +85 $^\circ$ C Operating Junction Temperature .....+125 $^\circ$ C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

1. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

**Electrical Specifications**  $V_{+} = 5V$ ,  $T_{A} = +25$ °C,  $R_{L} = 1k$  to  $V_{+}/2$ ,  $A_{V} = 4$ ,  $V_{IN} = 0.1$  VDC, Unless Otherwise Specified.

| PARAMETER                | DESCRIPTION                              | CONDITIONS                                                  | MIN<br>(Note 3) | TYP  | MAX<br>(Note 3) | UNIT      |

|--------------------------|------------------------------------------|-------------------------------------------------------------|-----------------|------|-----------------|-----------|

| INPUT CHARA              | ACTERISTICS                              |                                                             |                 |      |                 |           |

| TCVOS                    | Offset Voltage Temperature Coefficient   | Measured from -40℃ to +85℃                                  |                 | -3   |                 | μV/℃      |

| IB                       | Input Bias Current                       | V <sub>IN</sub> = 0V                                        | -10             | -5.5 | -2.5            | μA        |

| R <sub>IN</sub>          | Input Resistance                         |                                                             |                 | 7    |                 | $M\Omega$ |

| C <sub>IN</sub>          | Input Capacitance                        |                                                             |                 | 0.5  |                 | pF        |

| OUTPUT CHA               | RACTERISTICS                             |                                                             |                 |      |                 |           |

| Vos                      | Output Offset Voltage                    | Note 2                                                      | -14             | -2   | 10              | mV        |

| A <sub>CL</sub>          | Closed Loop Gain                         | $R_L = 1k$ , 150 $\Omega$ , $V_{OUT} = 0.5V$ to 4V          | 3.9             | 4    | 4.1             | V/V       |

| R <sub>OUT</sub>         | Output Resistance                        | A <sub>V</sub> = +4                                         |                 | 30   |                 | mΩ        |

| V <sub>OP</sub>          | Positive Output Voltage Swing            | $R_L = 1k\Omega$ to 2.5V                                    |                 | 4.86 |                 | V         |

|                          |                                          | $R_L = 150\Omega$ to 2.5V                                   |                 | 4.65 |                 | V         |

| V <sub>ON</sub>          | Negative Output Voltage Swing            | $R_L = 1k\Omega$ to 2.5V                                    |                 | 27   |                 | mV        |

|                          |                                          | $R_L = 150\Omega$ to 2.5V                                   |                 | 140  |                 | mV        |

| I <sub>SC</sub> (source) | Output Short Circuit Current             | $R_L = 10\Omega$ to GND, $V_{IN} = 1.5V$                    | 60              | 95   |                 | mA        |

| I <sub>SC</sub> (sink)   | Output Short Circuit Current             | $R_L = 10\Omega \text{ to } + 2.5V, V_{IN} = 0V$            | 70              | 105  |                 | mA        |

| POWER SUPP               | PLY                                      |                                                             |                 |      |                 |           |

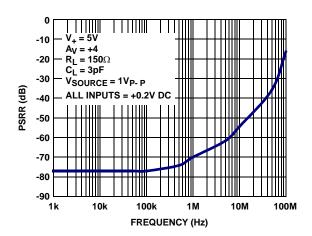

| PSRR                     | Power Supply Rejection Ratio @ 1kHz      | $V+ = 5V$ ; $V_{SOURCE} = 1V_{P-P}$ ;<br>f = 1kHz sine wave |                 | 78   |                 | dB        |

| I <sub>S-ON</sub>        | Supply Current - Enabled per Amplifier   | R <sub>L</sub> = Open                                       | 6.0             | 7.2  | 8.5             | mA        |

| I <sub>S-OFF</sub>       | Supply Current - All Amplifiers Disabled | R <sub>L</sub> = Open                                       | 0.5             | 1.1  | 2               | mA        |

| ENABLE                   |                                          |                                                             |                 |      | 1               |           |

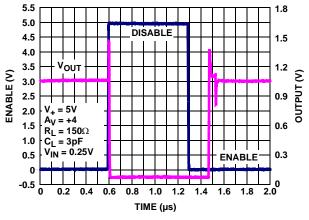

| t <sub>EN</sub>          | Enable Time                              | $R_L = 150\Omega, V_{IN} = 0.25V$                           |                 | 250  |                 | ns        |

| t <sub>DS</sub>          | Disable Time                             | $R_L = 150\Omega, V_{IN} = 0.25V$                           |                 | 25   |                 | ns        |

| V <sub>IH-ENB</sub>      | ENABLE Pin Voltage for Power-Up          |                                                             |                 | 0.8  |                 | V         |

| V <sub>IL-ENB</sub>      | ENABLE Pin Voltage for Shut-Down         |                                                             |                 | 2    |                 | V         |

#### ISL55036

# $\textbf{Electrical Specifications} \qquad V_{+} = 5 \text{V}, \ T_{A} = +25 \text{C}, \ R_{L} = 1 \text{k to V}_{+} / 2, \ A_{V} = 4, \ V_{IN} = 0.1 \text{VDC}, \ \text{Unless Otherwise Specified.} \ \textbf{(Continued)}$

| PARAMETER                               | DESCRIPTION                                                            | CONDITIONS                                                                      | MIN<br>(Note 3) | TYP  | MAX<br>(Note 3) | UNIT   |

|-----------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------|------|-----------------|--------|

| I <sub>IH-ENB</sub>                     | ENABLE Pin Input Current High                                          | V <sub>EN</sub> = 5V                                                            | 1               | 5.5  | 20              | μA     |

| I <sub>IL-ENB</sub>                     | ENABLE Pin Input for Current Low                                       | V <sub>EN</sub> = 0V                                                            | -4              |      | 4               | μA     |

| AC PERFORM                              | ANCE                                                                   |                                                                                 |                 |      |                 |        |

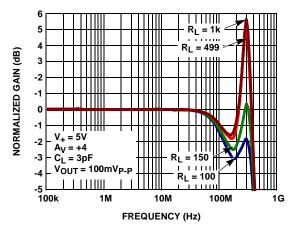

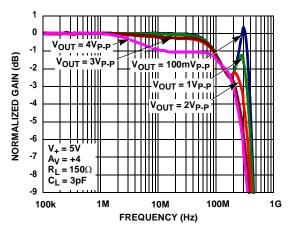

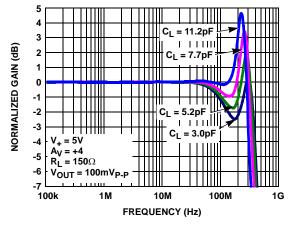

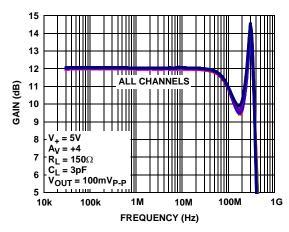

| BW                                      | -3dB Bandwidth                                                         | $R_L = 150\Omega, C_L = 3pF$                                                    |                 | 400  |                 | MHz    |

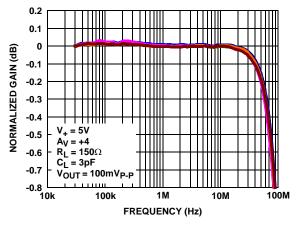

| BW                                      | ±0.1dB Bandwidth                                                       | $R_L = 150\Omega, C_L = 3pF$                                                    |                 | 40   |                 | MHz    |

| Peak                                    | Peaking                                                                | $R_L = 150\Omega$ , $C_L = 3pF$                                                 |                 | 1    |                 | dB     |

| dG                                      | Differential Gain                                                      | $V_{IN} = 0.1V$ to 1.0V, $V_{OUT} = 100 \text{mV}_{P-P}$ ,                      |                 | 0.06 |                 | %      |

| dP                                      | Differential Phase                                                     | $f = 3.58MHz, R_L = 150\Omega$                                                  |                 | 0.01 |                 | ٥      |

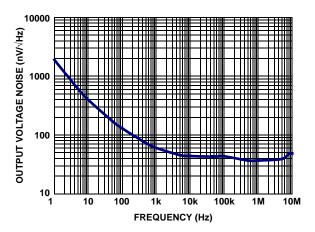

| e <sub>N-OUT</sub>                      | Output Noise Voltage                                                   | f = 10kHz                                                                       |                 | 50   |                 | nV/√Hz |

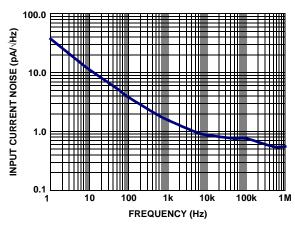

| i <sub>N</sub>                          | Input Noise Current                                                    | f = 10kHz                                                                       |                 | 0.9  |                 | pA/√Hz |

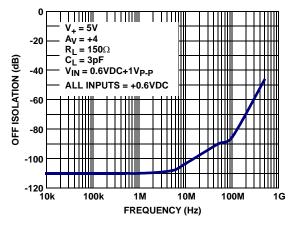

| ISO                                     | Off-State Isolation<br>f <sub>O</sub> = 10MHz                          | $V_{IN} = 0.6 \text{VDC} + 1 V_{P-P}, C_L = 3 \text{pF},$<br>$R_L = 150 \Omega$ |                 | -100 |                 | dB     |

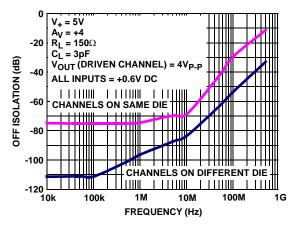

| X-TALK                                  | Die to Die Crosstalk<br>f <sub>O</sub> = 10MHz                         | $V_{IN} = 0.6VDC + 1V_{P-P}, C_L = 3pF,$<br>$R_L = 150\Omega$                   |                 | -85  |                 | dB     |

|                                         | Same Die Channel-to-Channel<br>Crosstalk, f <sub>O</sub> = 10MHz       |                                                                                 |                 | -65  |                 | dB     |

| PSRR                                    | Power Supply Rejection Ratio<br>f <sub>O</sub> = 10MHz                 | $V_{SOURCE} = 1V_{P-P}$ , $C_L = 3pF$ , $R_L = 150\Omega$                       |                 | -55  |                 | dB     |

| TRANSIENT R                             | ESPONSE                                                                |                                                                                 |                 |      |                 |        |

| SR                                      | Slew Rate 25% to 75%                                                   | $R_L = 150\Omega$ , $V_{OUT} = 0.5V$ to 4.5V                                    |                 | 2500 |                 | V/µs   |

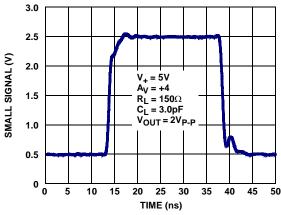

| t <sub>r</sub> , t <sub>f</sub> Large   | Rise Time, t <sub>r</sub> 20% to 80%                                   | $V_{OUT} = 4V_{P-P}, R_L = 150\Omega, C_L = 3pF$                                |                 | 1.4  | 4               | ns     |

| Signal                                  | Fall Time, t <sub>f</sub> 20% to 80%                                   |                                                                                 |                 | 1    |                 | ns     |

|                                         | Rise Time, t <sub>r</sub> 20% to 80%                                   | $V_{OUT} = 2V_{P-P}, R_L = 150\Omega, C_L = 3pF$                                |                 | 0.8  |                 | ns     |

|                                         | Fall Time, t <sub>f</sub> 20% to 80%                                   |                                                                                 |                 | 0.7  |                 | ns     |

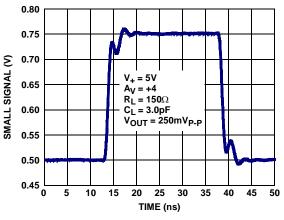

| t <sub>r</sub> , t <sub>f</sub> , Small | Rise Time, t <sub>r</sub> 20% to 80%                                   | $V_{OUT} = 0.2V_{P-P}, R_L = 150\Omega, C_L = 3pF$                              |                 | 0.75 |                 | ns     |

| Signal                                  | Fall Time, t <sub>f</sub> 20% to 80%                                   |                                                                                 |                 | 0.7  |                 | ns     |

| OS                                      | Overshoot                                                              | 200mV step                                                                      |                 | 5    |                 | %      |

| t <sub>PD</sub>                         | Propagation Delay                                                      | 200mV step                                                                      |                 | 0.6  |                 | ns     |

| t <sub>S</sub>                          | 1% Settling Time                                                       | 2V step                                                                         |                 | 12   |                 | ns     |

| <sup>t</sup> EN                         | ENABLE to Output Turn-on Delay Time;<br>10% EN - 10% V <sub>OUT</sub>  | $V_{OUT} = 1$ VDC, $R_L = 150\Omega$ , $C_L = 3$ pF                             |                 | 250  |                 | ns     |

|                                         | ENABLE to Output Turn-off Delay Time;<br>10% EN - 10% V <sub>OUT</sub> | $V_{OUT} = 1VDC$ , $R_L = 150\Omega$ , $C_L = 3pF$                              |                 | 25   |                 | ns     |

## NOTES:

- 2.  $V_{OS}$  is extrapolated from 2 output voltage measurements, with  $V_{IN}$  = 62.5mV and  $V_{IN}$  = 125mV,  $R_L$  = 1k.

- 3. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

## **Typical Performance Curves**

FIGURE 2. GAIN vs FREQUENCY FOR VARIOUS R<sub>LOAD</sub>

FIGURE 4. -3dB BANDWIDTH vs V<sub>OUT</sub>

FIGURE 6. 0.1 dB GAIN FLATNESS

FIGURE 3. GAIN vs FREQUENCY FOR VARIOUS CLOAD

FIGURE 5. GAIN vs FREQUENCY - ALL CHANNELS

FIGURE 7. PSRR vs FREQUENCY

FIGURE 8. OFF ISOLATION vs FREQUENCY

FIGURE 9. CHANNEL-TO-CHANNEL CROSSTALK vs FREQUENCY

FIGURE 10. OUTPUT NOISE VOLTAGE vs FREQUENCY

FIGURE 11. INPUT REFERRED NOISE CURRENT vs FREQUENCY

FIGURE 12. ENABLE/DISABLE TIMING

FIGURE 13. SMALL SIGNAL STEP RESPONSE

FIGURE 14. SMALL SIGNAL (2VP-P) STEP RESPONSE

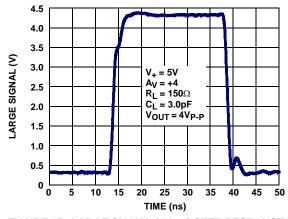

FIGURE 15. LARGE SIGNAL (4V<sub>P-P</sub>) STEP RESPONSE

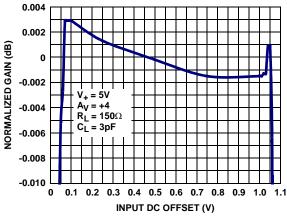

FIGURE 16. DIFFERENTIAL GAIN

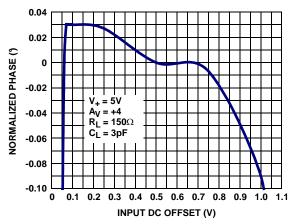

FIGURE 17. DIFFERENTIAL PHASE

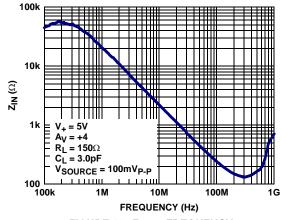

FIGURE 18. Z<sub>IN</sub> vs FREQUENCY

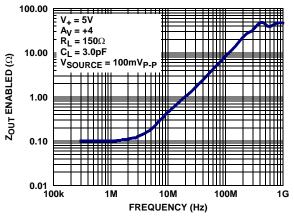

FIGURE 19. Z<sub>OUT</sub> (ENABLED) vs FREQUENCY

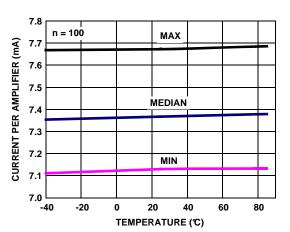

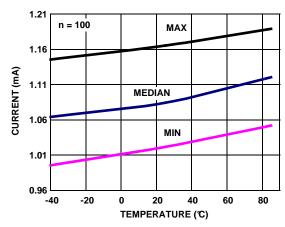

FIGURE 21. ENABLED SUPPLY CURRENT vs TEMPERATURE,  $V_S = \pm 2.5V$

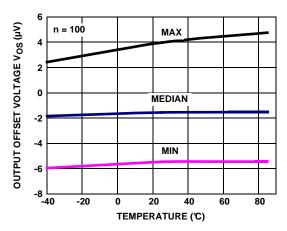

FIGURE 23. OUTPUT OFFSET VOLTAGE  $V_{OS}$  vs TEMPERATURE,  $V_{S}$  = ±2.5V,  $R_{L}$  = 1k

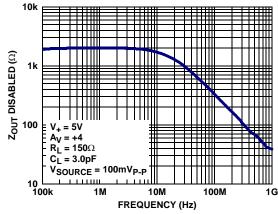

FIGURE 20. Z<sub>OUT</sub> (DISABLED) vs FREQUENCY

FIGURE 22. DISABLED SUPPLY CURRENT vs TEMPERATURE,  $V_S = \pm 2.5V$

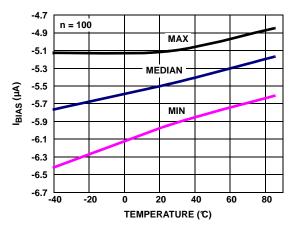

FIGURE 24.  $I_{BIAS}$  vs TEMPERATURE,  $V_{S} = \pm 2.5V$

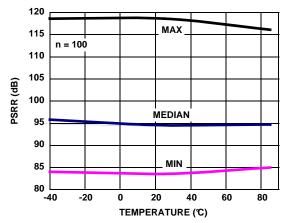

FIGURE 25. PSRR vs TEMPERATURE 4.5V TO 5.5V

## Application Information

#### General

The ISL55036 single supply, fixed gain hex amplifier is well suited for a variety of video applications. The device features a PNP ground-sensing input stage and a bipolar rail-to-rail output stage.

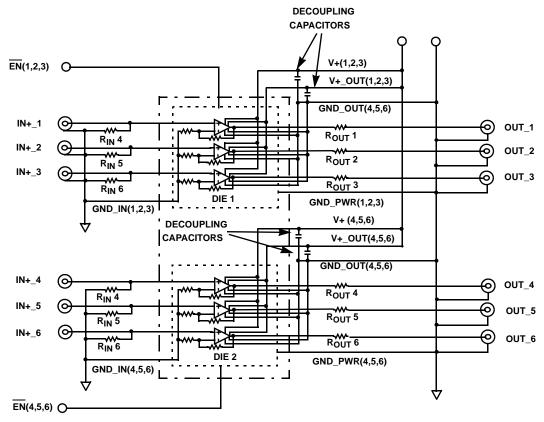

The ISL55036 is designed for general purpose video, communication, instrumentation, and industrial applications. The 6 fixed gain amplifiers operate independently, however, they are organized into 2 triple amplifier groups as shown in Figure 26. Each group has its own set of power supply pins, ground pins, enable-disable logic and input ground reference pins.

#### **Ground Connections**

For the best isolation performance and crosstalk rejection, all GND pins must connect directly to the GND plane. In addition, the electrically conductive thermal pad should also connect directly to ground.

#### **Power Considerations**

Each triple amplifier group has its own power supply and ground pins. There are dedicated V<sub>+</sub> OUT and GND V<sub>OUT</sub> pins to power only the output stage. A separate set of power and ground pins power the rest of each of the triple op amps (V<sub>+</sub> and PWR GND). Providing separate power pins provides a way to prevent high speed transient currents in the output stage from bleeding into the sensitive amplifier input and gain stages. To maximize crosstalk isolation, each power supply pin should have its own de-coupling capacitors connected as close to the pin as possible (0.1 $\mu$ F in parallel with 1nF recommended).

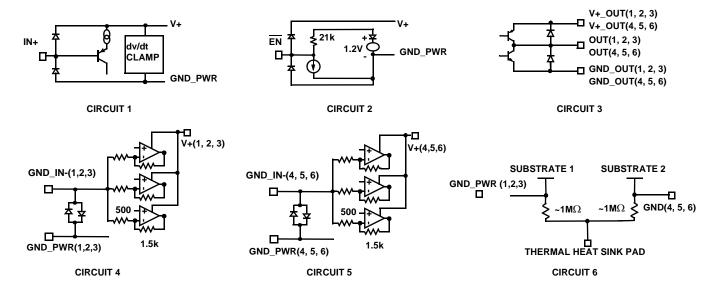

The ESD protection circuits use internal diodes from all pins to the  $V_+$  and ground pins. In addition, a dv/dt-triggered clamp is connected between the  $V_+$  and  $V_-$  pins, as shown in the Equivalent Circuits 1 through 4 on page 2. The dv/dt triggered

clamp imposes a maximum supply turn-on slew rate of  $1V/\mu s$ . Damaging currents can flow for power supply rates-of-rise in excess of  $1V/\mu s$ , such as during hot plugging. Under these conditions, additional methods should be employed to ensure the maximum rate of rise is not exceeded.

#### EN and Power-Down States

The  $\overline{EN}$  pin is active low. An internal pull-down resistor ensures the device will be active with no connection to the  $\overline{EN}$  pin. The power-down state is established within approximately 25ns, if a logic high (>2V) is placed on the  $\overline{EN}$  pin. In the power-down state, supply current is reduced significantly by shutting the three amplifiers off. The output presents a relatively high impedance (~2k $\Omega$ ) to the output pin. Multiplexing several outputs together is possible using the enable/disable function as long as the application can tolerate the limited power-down output impedance.

#### Limiting the Output Current

No output short circuit current limit exists on these parts. All applications need to limit the output current to less than 40mA. Adequate thermal heat sinking of the parts is also required.

## PC Board Layout

The AC performance of this circuit depends greatly on the care taken in designing the PC board. The following are recommendations to achieve optimum high frequency performance from your PC board.

- The use of low inductance components, such as chip resistors and chip capacitors, is strongly recommended.

- Minimize signal trace lengths. Trace inductance and capacitance can easily limit circuit performance. Avoid sharp corners. Use rounded corners when possible. Vias in the signal lines add inductance at high frequency and should be avoided. PCB traces greater than 1" begin to exhibit transmission line characteristics with signal rise/fall times of 1ns or less. High frequency performance may be

FN6640.1 September 11, 2008

FIGURE 26. BASIC APPLICATION CIRCUIT

degraded for traces greater than one inch, unless controlled impedance ( $50\Omega$  or  $75\Omega$ ) strip lines or microstrips are used.

- Match channel-to-channel analog I/O trace lengths and layout symmetry. This will minimize propagation delay mismatches.

- Maximize use of AC de-coupled PCB layers. All signal I/O lines should be routed over continuous ground planes (i.e. no split planes or PCB gaps under these lines). Avoid vias in the signal I/O lines.

- Use proper value and location of termination resistors.

Termination resistors should be as close to the device as possible.

- When testing, use good quality connectors and cables, matching cable types and keeping cable lengths to a minimum.

- A minimum of 2 power supply decoupling capacitors are recommended (1000pF, 0.01µF) as close to the devices as possible. Avoid vias between the capacitor and the device because vias add unwanted inductance. Larger capacitors

- can be farther away. When vias are required in a layout, they should be routed as far away from the device as possible.

- The NIC pins are placed on both sides of the input pins.

These pins are not internally connected to the die. It is recommended these pins be tied to ground to minimize crosstalk.

# The QFN Package Requires Additional PCB Layout Rules for the Thermal Pad

The thermal pad is electrically connected to power supply ground through the high resistance IC substrate. Its primary function is to provide heat sinking for the IC. However, because of the connection to the power ground pins through the substrate, the thermal pad must be tied to the power supply ground to prevent unwanted current flow through the thermal pad. Maximum AC performance is achieved if the thermal pad has good contact to the IC ground pins. Heat sinking requirements can be satisfied using thermal vias directly beneath the thermal pad to a heat dissipating layer of a square at least 1" on a side.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

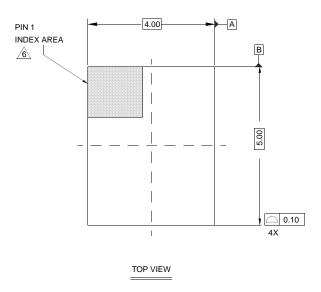

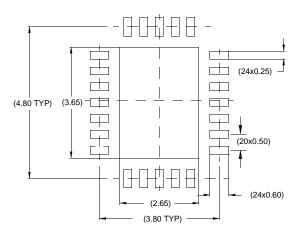

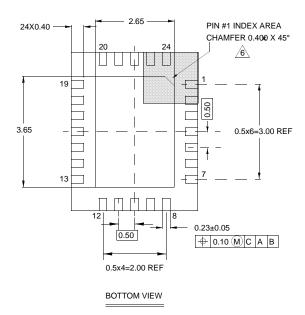

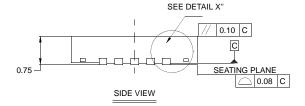

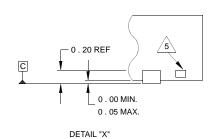

## **Package Outline Drawing**

#### L24.4x5C

# 24 LEAD THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 1, 10/07

TYPICAL RECOMMENDED LAND PATTERN

## NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.18mm and 0.28mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

either a mold or mark feature.