Data Sheet January 12, 2009 FN8092.5

## μP Supervisor with Watchdog Timer, Power-Fail Comparator, Manual Reset and Adjustable Power-On Reset

Designed with high reset threshold accuracy and low power consumption, the ISL88705, ISL88706, ISL88707, ISL88708, ISL88716 and ISL88813 devices are microprocessor supervisors that are designed to monitor power-supply and battery functions in microprocessor systems. They can help to lower system cost, reduce board space requirements and increase the reliability of systems.

These devices provide essential functions such as supply voltage supervision by asserting a reset output during power-up and power-down as well as during brownout conditions. An auxiliary voltage monitor is provided for detecting power failures warning the system of low battery conditions or presence detection. In addition, an independent watchdog timer helps to monitor microprocessor activity every 1.6s (typical). An active-low manual reset is offered and reset signals remain asserted until VDD returns to proper operating levels.

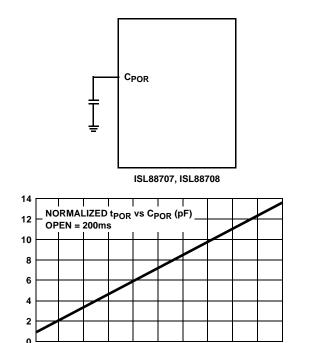

Users can increase the nominal 200ms power-on reset time-out delay by adding an external capacitor to the  $C_{\mbox{\footnotesize{POR}}}$  pin on the ISL88707 and ISL88708.

#### **Features**

- Fixed-Voltage Options Allow Precise Monitoring of +3.0V, +3.3V, and +5.0V Power Supplies

- Additional Voltage Monitor for Power-Fail Detection or Low-Battery Warning

- Monitors Voltages Down to 1.25V

- Adjustable Power-Fail Input Threshold

- Watchdog Timer Capability With 1.6s Time-out

- Both RST and RSTOutputs Available

- 140ms Minimum Reset Pulse Width with Option to Customize Using an External Capacitor

- · Manual Reset Input on all Devices

- Reset Signal Valid Down to ŊD = 1V

- Accurate ±1.8% Voltage Threshold

- Immune to Power-Supply Transients

- Ultra Low 10µA Maximum Supply Current at 3V

- Pb-Free (RoHS Compliant)

## **Applications**

- Portable/Battery Powered Equipment

- Notebook/Desktop Computer Systems

- · Designs Using DSPs, Microcontrollers or Microprocessors

- Controllers

- · Intelligent Instruments

- Communications Systems

- Industrial Equipment

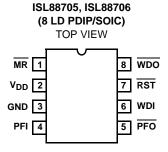

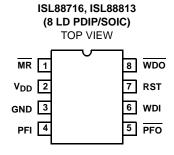

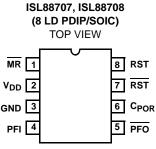

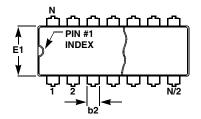

#### **Pinouts**

# **Ordering Information**

| PART NUMBER<br>(Note) | PART<br>MARKING  | V <sub>TH</sub> | TEMP RANGE<br>(℃) | PACKAGE<br>(Pb-Free)      | PKG. DWG. # |

|-----------------------|------------------|-----------------|-------------------|---------------------------|-------------|

| ISL88705IP846Z        | 88705 I46Z       | 4.64V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88813IP846Z        | 88813 I46Z       | 4.64V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88707IP846Z        | 88707 I46Z       | 4.64V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88706IP844Z        | 88706 I44Z       | 4.38V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88708IP844Z        | 88708 I44Z       | 4.38V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88706IP831Z        | 88706 I31Z       | 3.09V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88708IP831Z        | 88708 I31Z       | 3.09V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88706IP829Z        | 88706 I29Z       | 2.92V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88708IP829Z        | 88708 I29Z       | 2.92V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88706IP826Z        | 88706 I26Z       | 2.63V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88716IP826Z        | 88716 I26Z       | 2.63V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88708IP826Z        | 88708 I26Z       | 2.63V           | -40 to +85        | 8 Ld PDIP**               | MDP0031     |

| ISL88705IB846Z*       | 88705 I46Z       | 4.64V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88813IB846Z*       | 88813 I46Z       | 4.64V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88707IB846Z*       | 88707 I46Z       | 4.64V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88706IB844Z*       | 88706 I44Z       | 4.38V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88708IB844Z*       | 88708 I44Z       | 4.38V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88706IB831Z*       | 88706 I31Z       | 3.09V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88708IB831Z*       | 88708 I31Z       | 3.09V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88706IB829Z*       | 88706 I29Z       | 2.92V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88708IB829Z*       | 88708 I29Z       | 2.92V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88706IB826Z*       | 88706 I26Z       | 2.63V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88716IB826Z*       | 88716 I26Z       | 2.63V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88708IB826Z*       | 88708 I26Z       | 2.63V           | -40 to +85        | 8 Ld SOIC (Tape and Reel) | M8.15       |

| ISL88705EVAL1         | Evaluation Board |                 |                   |                           |             |

|                       | •                |                 |                   |                           |             |

<sup>\*</sup>Add "-TK" suffix for Tape and Reel Packaging. Please refer to TB347 for details on reel specifications.

<sup>\*\*</sup>Pb-free PDIPs can be used for through-hole wave solder processing only. They are not intended for use in Reflow solder processing applications. NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

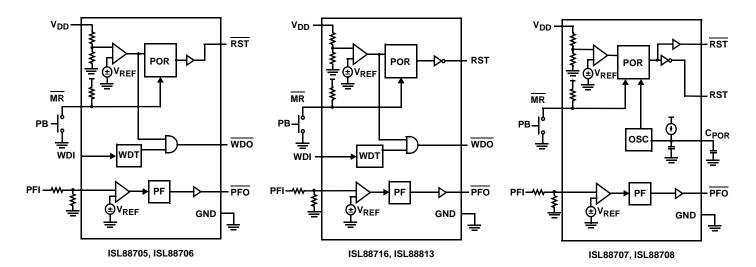

# Functional Block Diagrams

3

# Pin Descriptions

| ISL88705,<br>ISL88706 | ISL88716,<br>ISL88813 | ISL88707,<br>ISL88708 | NAME             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|-----------------------|-----------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | 1                     | 1                     | MR               | <b>Manual Reset Input.</b> A reset signal is generated when this input is pulled low. The $\overline{\text{MR}}$ input is an active low debounced input to which a user can connect a push-button to add manual reset capability or drive with a signal. The $\overline{\text{MR}}$ pin has an internal 20kΩ pull-up.                                                                                                                                                                                                                           |

| 2                     | 2                     | 2                     | V <sub>DD</sub>  | <b>Power Supply Terminal.</b> The voltage at this pin is compared against an internal factory-programmed voltage trip point, $V_{TH1}$ . A reset is first asserted when the device is initially powered up to ensure that the power supply has stabilized. Thereafter, reset is again asserted whenever $V_{DD}$ falls below $V_{TH1}$ . The device is designed with hysteresis to help prevent chattering due to noise and is immune to brief power-supply transients. The voltage threshold $V_{TH1}$ is specified in the part number suffix. |

| 3                     | 3                     | 3                     | GND              | Ground Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4                     | 4                     | 4                     | PFI              | Power-Fail Input This is an auxiliary monitored voltage input with a 1.25V threshold that causes PFO state to follow the PFI input state.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5                     | 5                     | 5                     | PFO              | <b>Power-Fail Output.</b> This output goes high if the voltage on PFI is greater than 1.25V, otherwise PFO stays low.                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                       |                       | 6                     | C <sub>POR</sub> | Adjustable POR Time-out Delay Input. Connecting an external capacitor from C <sub>POR</sub> to ground allows the user to increase the Power-On Reset time-out (t <sub>POR</sub> ) from the nominal 200ms.                                                                                                                                                                                                                                                                                                                                       |

| 6                     | 6                     |                       | WDI              | <b>Watchdog Input.</b> The Watchdog Input takes an input from a microprocessor and ensures that it periodically toggles the WDI pin, otherwise the internal nominal 1.6s watchdog timer runs out, then reset is asserted and WDO is pulled low. The internal Watchdog Timer is cleared whenever the WDI sees a rising or falling edge or the device is manually reset. Floating WDI or connecting WDI to a high-impedance three-state buffer disables the watchdog feature.                                                                     |

| 7                     |                       | 7                     | RST              | Active-Low Reset Output. The RST output is an active low output with an internal PMOS pull-up that is pulled low to GND when reset is asserted. Reset is asserted whenever:  1. The device is first powered up 2. V <sub>DD</sub> falls below its minimum voltage sense level or 3. MR is asserted.  The reset output continues to be asserted for typically 200ms after V <sub>DD</sub> rises above the reset threshold or MR input goes from low to high. A watchdog time-out will not trigger a reset unless WDO is connected to MR.         |

|                       | 7                     | 8                     | RST              | <b>Active-High Reset Output.</b> The RST pin functions identically to its complementary $\overline{RST}$ output but is an active high push-pull output. RST is set high to $V_{DD}$ when reset is asserted. See the $\overline{RST}$ in "Pin Descriptions" on page 4 for more details on conditions that cause a reset.                                                                                                                                                                                                                         |

| 8                     | 8                     |                       | WDO              | <b>Watchdog Output</b> . This output is pulled low when the nominal 1.6s internal Watchdog Timer expires and periodically resets until the watchdog is cleared. WDO also goes low during low $V_{DD}$ conditions. Whenever $V_{DD}$ is below the reset threshold, WDO stays low. However, unlike RESET, WDO does not have a minimum pulse width. As soon as $V_{DD}$ rises above the reset threshold, WDO goes high with no delay.                                                                                                              |

FN8092.5 January 12, 2009

## **Absolute Maximum Ratings**

| Temperature Under Bias                 | 40℃ to +125℃ |

|----------------------------------------|--------------|

| Storage Temperature                    | 65℃ to +150℃ |

| Voltage on any Pin with Respect to GND | 1.0V to +7V  |

| DC Output Current                      | 5mA          |

#### **Recommended Operating Conditions**

5

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)             | θJA (℃/W)      |

|--------------------------------------------------|----------------|

| PDIP Package* (4-layer test board)               | 83             |

| SOIC Package (4-layer test board)                | 110            |

| Pb-free Reflow Profile                           | see link below |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp | )              |

|                                                  |                |

\*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTE:

1. θ<sub>JA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

## **Electrical Specifications**

Over the recommended operating conditions unless otherwise specified. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| SYMBOL            | PARAMETER                                                  | CONDITIONS                             | MIN                   | TYP                   | MAX   | UNITS |

|-------------------|------------------------------------------------------------|----------------------------------------|-----------------------|-----------------------|-------|-------|

| V <sub>DD</sub>   | Supply Voltage Range                                       |                                        | 2.0                   |                       | 5.5   | V     |

| I <sub>DD</sub>   |                                                            | V <sub>DD</sub> = 5V, WDT Inactive     |                       | 10                    | 19    | μA    |

|                   |                                                            | V <sub>DD</sub> = 3V, WDT Inactive     |                       | 8                     | 10    | μA    |

| ILI               | Input Leakage Current (PFI)                                |                                        |                       |                       | 100   | nA    |

| ILO               | Output Leakage Current                                     |                                        |                       |                       | 100   | nA    |

| OLTAGE TH         | HRESHOLDS                                                  |                                        | 1                     |                       |       |       |

| V <sub>TH1</sub>  | Fixed V <sub>DD</sub> Voltage Trip Point                   |                                        | 4.556                 | 4.640                 | 4.724 | V     |

|                   |                                                            |                                        | 4.301                 | 4.380                 | 4.459 | V     |

|                   |                                                            |                                        | 3.034                 | 3.090                 | 3.146 | V     |

|                   |                                                            |                                        | 2.867                 | 2.920                 | 2.973 | V     |

|                   |                                                            |                                        | 2.583                 | 2.630                 | 2.677 | V     |

|                   | Hysteresis at V <sub>TH1</sub> Input<br>Temperature = +25℃ | V <sub>TH1</sub> = 4.64V               |                       | 46                    |       | mV    |

|                   |                                                            | V <sub>TH1</sub> = 4.38V               |                       | 44                    |       | mV    |

|                   |                                                            | V <sub>TH1</sub> = 3.09V               |                       | 37                    |       | mV    |

|                   |                                                            | V <sub>TH1</sub> = 2.92V               |                       | 29                    |       | mV    |

|                   |                                                            | V <sub>TH1</sub> = 2.63V               |                       | 31                    |       | mV    |

| RST AND RS        | ST .                                                       |                                        |                       |                       |       |       |

| V <sub>OL</sub>   | Reset Output Voltage Low                                   | $V_{DD} \ge 3.3V$ , Sinking 2.5mA      |                       | 0.05                  | 0.40  | V     |

|                   |                                                            | V <sub>DD</sub> < 3.3V, Sinking 1.5mA  |                       | 0.05                  | 0.40  | V     |

| V <sub>OH</sub>   | RST Output Voltage High                                    | $V_{DD} \ge 3.3V$ , Sourcing 2.5mA     | V <sub>DD</sub> - 0.6 | V <sub>DD</sub> - 0.4 |       | V     |

|                   |                                                            | V <sub>DD</sub> < 3.3V, Sourcing 1.5mA | V <sub>DD</sub> - 0.6 | V <sub>DD</sub> - 0.4 |       | V     |

|                   | RST Output Voltage High                                    | $V_{DD} \ge 3.3V$ , Sourcing 0.8mA     | V <sub>DD</sub> - 0.6 | V <sub>DD</sub> - 0.4 |       | V     |

|                   |                                                            | V <sub>DD</sub> < 3.3V, Sourcing 0.5mA | V <sub>DD</sub> - 0.6 | V <sub>DD</sub> - 0.4 |       | V     |

| t <sub>RPD</sub>  | V <sub>TH</sub> to Reset Asserted Delay                    |                                        |                       | 45                    |       | μs    |

| t <sub>POR</sub>  | POR Time-Out Delay                                         | C <sub>POR</sub> is open               | 140                   | 200                   | 260   | ms    |

| C <sub>LOAD</sub> | Load Capacitance on Reset Pins                             |                                        |                       | 5                     |       | pF    |

FN8092.5

January 12, 2009

#### **Electrical Specifications**

Over the recommended operating conditions unless otherwise specified. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. (Continued)

| SYMBOL                 | PARAMETER                    | CONDITIONS                             | MIN                   | TYP                   | MAX                   | UNITS |

|------------------------|------------------------------|----------------------------------------|-----------------------|-----------------------|-----------------------|-------|

| MANUAL RE              | SET                          | '                                      | "                     | '                     |                       |       |

| $V_{MRL}$              | MR Input Voltage Low         |                                        |                       |                       | 0.8                   | V     |

| $V_{MRH}$              | MR Input Voltage High        |                                        | V <sub>DD</sub> - 0.6 |                       |                       | V     |

| t <sub>MR</sub>        | MR Minimum Pulse Width       |                                        | 550                   |                       |                       | ns    |

| R <sub>PU</sub>        | Internal MR Pull-Up Resistor |                                        |                       | 20                    |                       | kΩ    |

| WATCHDOG               | TIMER (Note 2)               | <u>'</u>                               | 1                     | 1                     |                       |       |

| t <sub>WDT</sub>       | Watchdog Time-out Period     |                                        | 1.0                   | 1.6                   | 2.0                   | s     |

| t <sub>WDPS</sub>      | WDI Minimum Pulse Width      |                                        | 100                   |                       |                       | ns    |

| $V_{IL}$               | Watchdog Input Voltage Low   |                                        |                       |                       | 0.3 x V <sub>DD</sub> | V     |

| V <sub>IH</sub>        | Watchdog Input Voltage High  |                                        | 0.7 x V <sub>DD</sub> |                       |                       | V     |

| V <sub>WDOL</sub>      | WDO Output Voltage Low       | $V_{DD} \ge 3.3V$ , Sinking 2.5mA      |                       | 0.05                  | 0.40                  | V     |

|                        |                              | V <sub>DD</sub> < 3.3V, Sinking 1.5mA  |                       | 0.05                  | 0.40                  | V     |

| V <sub>WDOH</sub>      | WDO Output Voltage High      | $V_{DD} \ge 3.3V$ , Sourcing 2.5mA     | V <sub>DD</sub> - 0.6 | V <sub>DD</sub> - 0.4 |                       | V     |

|                        |                              | V <sub>DD</sub> < 3.3V, Sourcing 1.5mA | V <sub>DD</sub> - 0.6 | V <sub>DD</sub> - 0.4 |                       | V     |

| I <sub>WDT</sub>       | Watchdog Input Current       |                                        |                       |                       | 1                     | μΑ    |

| POWER-FAIL             | DETECTION                    | <u>'</u>                               | 1                     | 1                     |                       |       |

| V <sub>THPFI</sub>     | PFI Input Threshold Voltage  | MR = Open                              | 1.20                  | 1.25                  | 1.30                  | V     |

| PFIV <sub>THHYST</sub> | Hysteresis Voltage           |                                        |                       | 20                    |                       | mV    |

| V <sub>PFOL</sub>      | PFO Output Voltage Low       | $V_{DD} \ge 3.3V$ , Sinking 2.5mA      |                       | 0.05                  | 0.40                  | V     |

|                        |                              | V <sub>DD</sub> < 3.3V, Sinking 1.5mA  |                       | 0.05                  | 0.40                  | V     |

| $V_{PFOH}$             | PFO Output Voltage High      | $V_{DD} \ge 3.3V$ , Sourcing 2.5mA     | V <sub>DD</sub> - 0.6 | V <sub>DD</sub> - 0.4 |                       | V     |

|                        |                              | V <sub>DD</sub> < 3.3V, Sourcing 1.5mA | V <sub>DD</sub> - 0.6 | V <sub>DD</sub> - 0.4 |                       | V     |

NOTE:

2. Applies to ISL88705, ISL88706, ISL88716, and ISL88813.

## Principles of Operation

The ISL88705, ISL88706, ISL88707, ISL88708, ISL88716, ISL88813 devices provide those functions needed for monitoring critical voltages such as power-supply and battery functions in microprocessor systems. Features of these supervisors include Power-On Reset control, Supply Voltage Supervision, Power-Fail Detection and Manual Reset Assertion. The integration of all these features along with high reset threshold accuracy and low power consumption make these devices ideal for portable or battery-powered equipment.

6

#### Power-On Reset (POR)

Applying power to the device activates a POR circuit which asserts reset (i.e. RST goes high while  $\overline{\text{RST}}$  goes low). These signals provide several benefits:

- It prevents the system microprocessor from starting to operate with insufficient voltage.

- It prevents the processor fromoperating prior to stabilization of the oscillator.

- It ensures that the monitored device is held out of operation until internal registers are properly loaded.

- It allows time for an FPGA to download its configuration prior to initialization of the circuit.

The reset signals remain active until  $V_{DD}$  rises above the minimum voltage sense level for time period  $t_{POR}$ . This ensures that the supply voltage has stabilized to sufficient operating levels.

FN8092.5 January 12, 2009

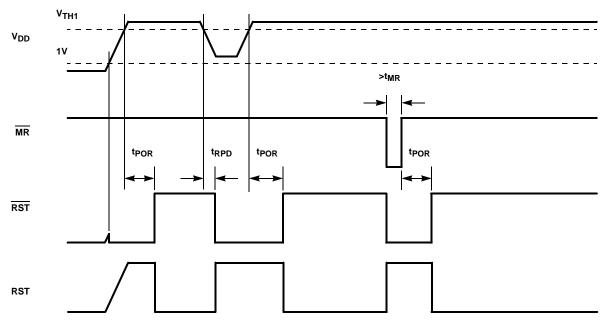

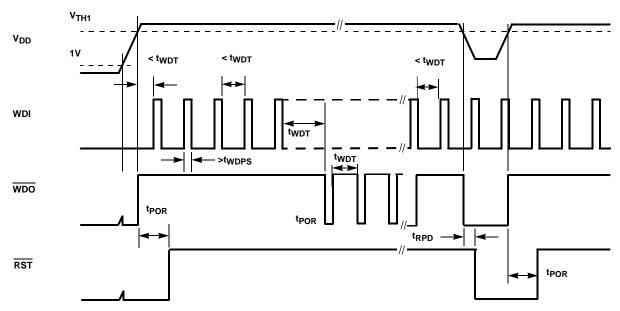

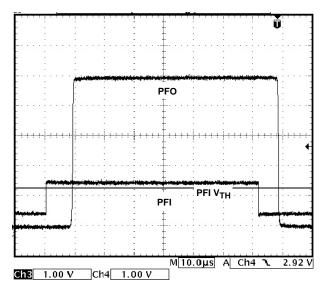

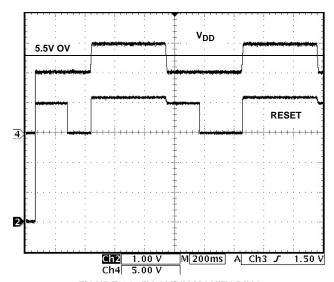

FIGURE 1. POWER-SUPPLY MONITORING TIMING DIAGRAM (WDI TRI-STATED)

## Low Voltage Monitoring

These devices monitor both the voltage level of  $V_{DD}$  and an auxiliary voltage on PFI.

When IC is initially biased reset is asserted until the  $V_{DD}$  voltage is greater than the specific IC fixed-voltage trip point for the  $t_{POR}$  duration of 200ms. At any subsequent time that  $V_{DD}$  does not exceed its voltage threshold, reset is once again asserted, i.e. RST is high and  $\overline{RST}$  is low (see Figure 1).

#### Power Failure Monitor

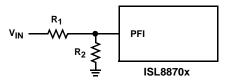

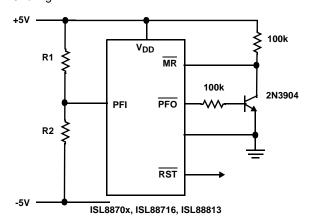

These devices also have a Power-Failure Monitor that helps to monitor an additional critical voltage on the Power-Fail Input (PFI) pin. For example, the PFI pin could be used to provide an early power-fail warning, detect a low-battery condition, presence detection or simply monitor a power supply other than +5V. The 1.25V threshold detector can be adjusted using an external resistor divider network to provide custom voltage monitoring of voltages greater than 1.25V, according to Equation 1 (see Figure 2).

$$PFIV_{TH} = 1.25 \left( \frac{R_1 + R_2}{R_2} \right)$$

(EQ. 1)

PFO goes low whenever PFI is less than the 1.25V (or user-set) threshold voltage.

FIGURE 2. CUSTOM  $V_{\mbox{\scriptsize TH}}$  WITH RESISTOR DIVIDER ON PFI

If using a voltage divider on the PFI input to critique an external voltage and intending to use the MR input to initiate resets then avoid having the PFI voltage less than PFI Vth +2.2V as unintended PFO transition may occur when MR is transitioning high.

#### Adjusting t<sub>POR</sub>

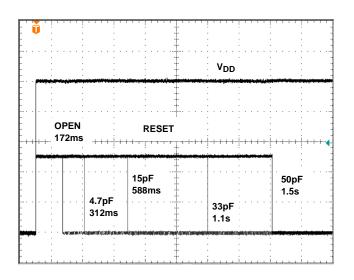

On the ISL88707 and ISL88708, users can adjust the Power-On Reset time-out delay ( $t_{POR}$ ) to many times the nominal  $t_{POR}$  of 200ms. To do this, connect a capacitor between  $C_{POR}$  and ground (see Figure 3). For example, connecting a 50pF capacitor to CPOR will increase  $t_{POR}$  from 200ms to ~1.4s. Care should be taken in PCB layout and capacitor placement in order to reduce stray capacitance as much as possible, which contributes to  $t_{POR}$  error.

FIGURE 3. ADJUSTING tPOR WITH A CAPACITOR

50 60

C<sub>POR</sub> (pF)

80

30 40

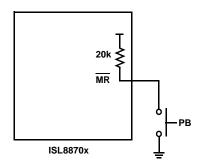

#### Manual Reset

The manual-reset input  $(\overline{MR})$  allows the user to trigger a reset by using a push-button switch. The  $\overline{MR}$  input is an active low debounced input. By connecting a push-button directly from  $\overline{MR}$  to ground, the designer adds manual system reset capability (see Figure 4). Reset is asserted if the  $\overline{MR}$  pin is pulled low to less than 100mV for the minimum  $\overline{MR}$  pulse width or longer while the push-button is closed. After  $\overline{MR}$  is released, the reset outputs remain asserted for tpOR (200ms) and then released.

FIGURE 4. CONNECTING A MANUAL RESET PUSH-BUTTON

#### Watchdog Timer

The Watchdog Timer circuit checks microprocessor activity by monitoring the WDI input pin. The microprocessor must periodically toggle the WDI pin within  $t_{WDT}$  (typically ~1.6s), otherwise the  $\overline{WDO}$  pin pulls low (see Figure 5). The  $\overline{WDO}$  then signals reset periodically (typically ~1.9s) for ~220ms until the WDI is again toggled. Internally, the 1.6s timer is cleared by either a reset or by toggling the WDI input, which can detect pulses longer than 50ns.

Whenever there is a low-voltage  $V_{DD}$  condition,  $\overline{WDO}$  goes low. Unlike the reset outputs, however,  $\overline{WDO}$  does not have a minimum reset pulse width (tpOR).  $\overline{WDO}$  goes high as soon as  $V_{DD}$  rises above its voltage trip point (see Figure 5). With WDI open or connected to a tristated high impedance input, the Watchdog Timer is disabled and only pulls low when  $V_{DD} < V_{TH1}$ .

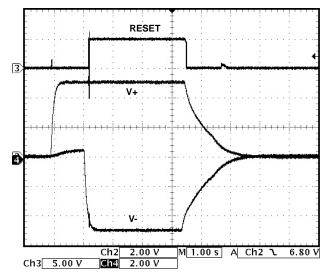

FIGURE 5. WATCHDOG TIMING DIAGRAM

## **Typical Performance Curves**

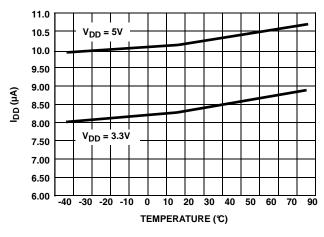

FIGURE 6. I<sub>DD</sub> vs TEMPERATURE

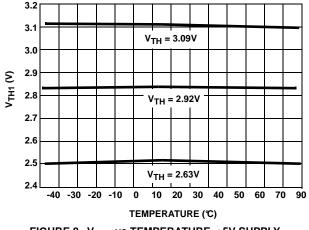

FIGURE 8. V<sub>TH1</sub> vs TEMPERATURE < 5V SUPPLY

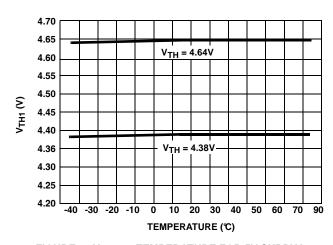

FIGURE 7. V<sub>TH1</sub> vs TEMPERATURE FOR 5V SUPPLY

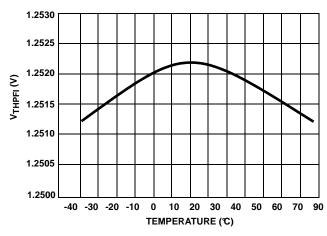

FIGURE 9. V<sub>THPFI</sub> vs TEMPERATURE

# Typical Performance Curves (Continued)

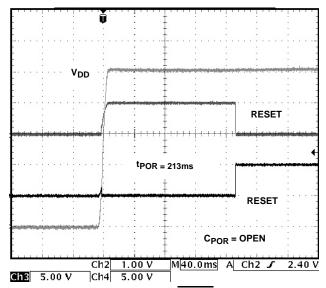

FIGURE 10. RESET AND RESET ASSERTION

FIGURE 11. RESET ASSERTION vs CPOR

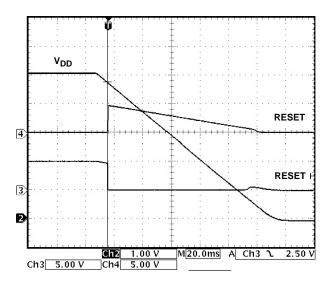

FIGURE 12. RESET AND RESET DEASSERTION

FIGURE 13. 5V PFI TO PFO RESPONSE

### Typical Performance Curves (Continued)

FIGURE 14. 5V OV/UV MONITORING

## ISL88705EVAL1 and Applications

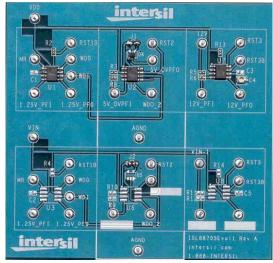

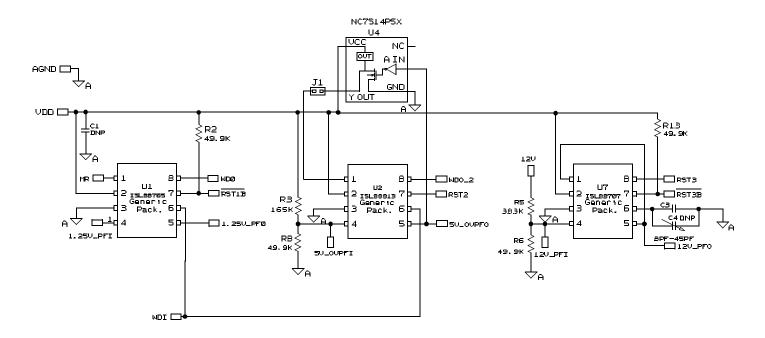

The ISL88705EVAL1 supports all six of the ISL88705, ISL88706, ISL88707, ISL88708, ISL88716, ISL88813 devices, enabling evaluation of basic functional operation and common application implementations. Figures 15 and 17 illustrate the ISL88705EVAL1 in photographic and schematic forms respectively.

The ISL88705EVAL1 is divided into two banks; each bank having one each of the three available pinouts. The top bank is fully populated and immediately usable whereas the bottom bank is unpopulated. Samples of other sample variants can be evaluated singularly or in combination with any other variant to provide a specific voltage monitoring solution. The left position has the ISL88705IB846Z monitoring the  $V_{DD}$  rail voltage for a minimum of 4.64V with reset signaling. In addition, the power fail input (PFI) is being compared to the internal PFI voltage reference of 1.25V and the power fail output  $(\overline{PFO})$  will report the PFI condition. This feature can be used for monitoring an auxiliary voltage, providing an early warning of a brown-out or power failure or presence detection in a system.

The middle position has the ISL88813IB846Z installed and is set-up as a 5V window detector with jumper J1 installed. The V<sub>DD</sub> monitors for UV and the PFI for OV via the R<sub>3</sub>, R<sub>4</sub> divider. The PFO output is inverted and connected to the manual reset input (MR) via U4. Hence, a reset signal is generated when 4.64V < V<sub>DD</sub> > 5.38V. With J1 removed, the PFO will be an OV indicator but no reset signal will be generated. Both of these positions share a common Watchdog input (WDI) signal although each has its own Watchdog output (WDO).

The right position has the ISL88707IB846Z and is set-up as a +12V and +5V UV monitor with reset signal. The PFI allows monitoring of any voltage above the 1.25V PFI reference and with a resistor divider this is used to monitor the 12V. The ISL88707 and ISL88708 have the unique feature of an adjustable time to reset ( $t_{POR}$ ) signal generation capability via the  $C_{POR}$  pin with an external capacitor to GND. This evaluation platform has an adjustable SMD capacitor,  $C_4$  (8pF to 45pF) that allows easy evaluation of this feature. Also unique to the ISL88707 and ISL88708 are both the RESET and  $\overline{RESET}$  outputs, all other variants having only one or the other.

Figures 10, 11, 12, 13 and 14 illustrate the basic IC functions and performance of the 3 implementations.

FIGURE 15. ISL88705EVAL1

#### Bipolar Voltage Sensing

Any of the ISL88705, ISL88706, ISL88707, ISL88708, ISL88716, ISL88813 devices can be used to sense and report the presence of both a positive and negative voltage via the PFI and  $\overline{PFO}$ , as shown in Figure 16. The  $V_{DD}$  monitors the positive voltage as normal and the PFI monitors the presence of the negative supply. As the differential voltage across the  $R_1,\,R_2$  divider is increased, the resistor values must be chosen such that the PFI node is <1.25V when the -V supply is satisfactory and the positive supply is at its maximum specified value. This allows the positive supply to fluctuate within its acceptable range without signaling a reset. Driving the  $\overline{MR}$  with the inverted  $\overline{PFO}$  signal as shown provides for reset generation when -V is not satisfactorily present. Reset will remain asserted as long as  $\overline{PFO}$  is high.

FIGURE 16. ±5V MONITORING

#### Special Application Considerations

Using good decoupling practices will prevent transients (i.e., due to switching noises and short duration droops in the supply voltage) from causing unwanted resets.

When using the  $C_{POR}$  pin, avoid stray capacitance during layout as much as possible in order to minimize its effect on the  $t_{POR}$  timing.

If using a voltage resistor divider on the PFI input to critique an external voltage and intending to use the  $\overline{\text{MR}}$  input to initiate resets then avoid having the PFI voltage less than PFI Vth +2.2V as unintended PFO transition may occur when  $\overline{\text{MR}}$  is transitioning high.

FIGURE 17. ISL88705EVAL1 SCHEMATIC (TOP BANK)

FN8092.5 January 12, 2009

13

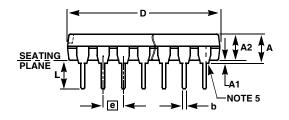

# Plastic Dual-In-Line Packages (PDIP)

#### **MDP0031**

#### PLASTIC DUAL-IN-LINE PACKAGE

|        | INCHES |        |        |        |        |               |       |

|--------|--------|--------|--------|--------|--------|---------------|-------|

| SYMBOL | PDIP8  | PDIP14 | PDIP16 | PDIP18 | PDIP20 | TOLERANCE     | NOTES |

| Α      | 0.210  | 0.210  | 0.210  | 0.210  | 0.210  | MAX           |       |

| A1     | 0.015  | 0.015  | 0.015  | 0.015  | 0.015  | MIN           |       |

| A2     | 0.130  | 0.130  | 0.130  | 0.130  | 0.130  | ±0.005        |       |

| b      | 0.018  | 0.018  | 0.018  | 0.018  | 0.018  | ±0.002        |       |

| b2     | 0.060  | 0.060  | 0.060  | 0.060  | 0.060  | +0.010/-0.015 |       |

| С      | 0.010  | 0.010  | 0.010  | 0.010  | 0.010  | +0.004/-0.002 |       |

| D      | 0.375  | 0.750  | 0.750  | 0.890  | 1.020  | ±0.010        | 1     |

| E      | 0.310  | 0.310  | 0.310  | 0.310  | 0.310  | +0.015/-0.010 |       |

| E1     | 0.250  | 0.250  | 0.250  | 0.250  | 0.250  | ±0.005        | 2     |

| е      | 0.100  | 0.100  | 0.100  | 0.100  | 0.100  | Basic         |       |

| eA     | 0.300  | 0.300  | 0.300  | 0.300  | 0.300  | Basic         |       |

| eB     | 0.345  | 0.345  | 0.345  | 0.345  | 0.345  | ±0.025        |       |

| L      | 0.125  | 0.125  | 0.125  | 0.125  | 0.125  | ±0.010        |       |

| N      | 8      | 14     | 16     | 18     | 20     | Reference     |       |

Rev. C 2/07

#### NOTES:

- 1. Plastic or metal protrusions of 0.010" maximum per side are not included.

- 2. Plastic interlead protrusions of 0.010" maximum per side are not included.

- 3. Dimensions E and eA are measured with the leads constrained perpendicular to the seating plane.

- 4. Dimension eB is measured with the lead tips unconstrained.

- 5. 8 and 16 lead packages have half end-leads as shown.

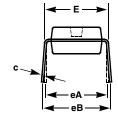

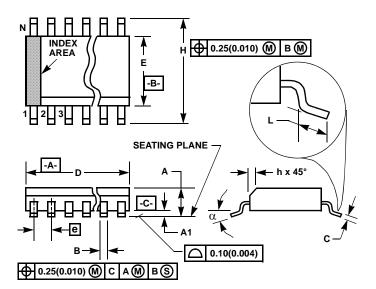

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M8.15 (JEDEC MS-012-AA ISSUE C) 8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INCHES |        | MILLIN   |      |       |

|--------|--------|--------|----------|------|-------|

| SYMBOL | MIN    | MAX    | MIN      | MAX  | NOTES |

| Α      | 0.0532 | 0.0688 | 1.35     | 1.75 | -     |

| A1     | 0.0040 | 0.0098 | 0.10     | 0.25 | -     |

| В      | 0.013  | 0.020  | 0.33     | 0.51 | 9     |

| С      | 0.0075 | 0.0098 | 0.19     | 0.25 | -     |

| D      | 0.1890 | 0.1968 | 4.80     | 5.00 | 3     |

| Е      | 0.1497 | 0.1574 | 3.80     | 4.00 | 4     |

| е      | 0.050  | BSC    | 1.27 BSC |      | -     |

| Н      | 0.2284 | 0.2440 | 5.80     | 6.20 | -     |

| h      | 0.0099 | 0.0196 | 0.25     | 0.50 | 5     |

| L      | 0.016  | 0.050  | 0.40     | 1.27 | 6     |

| N      | 8      |        |          | 8    | 7     |

| α      | 0°     | 8°     | 0°       | 8°   | -     |

Rev. 1 6/05

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com