# System Lens Drivers

# Microstep system Lens Driver for Digital Still Cameras

2.7V to 3.6V

2.7V to 5.5V

1.5Ω(Typ.)

0.9Ω(Typ.)

±500mA(Max.)

-20°C to +85°C

1MHz to 27.5MHz

# BU24026GU

#### General Description

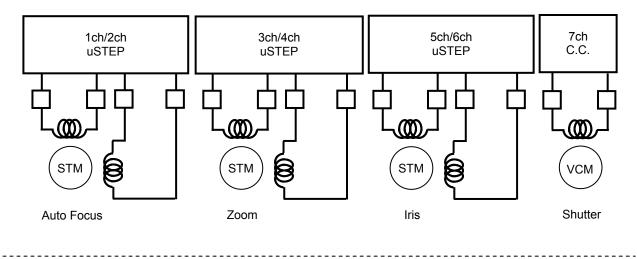

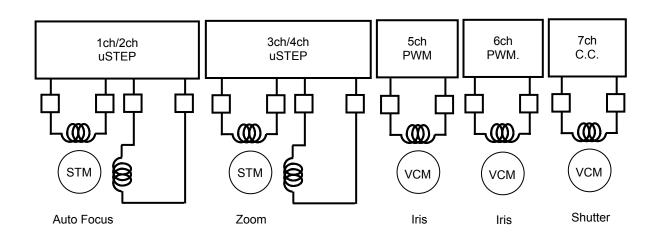

BU24026GU is the system Lens Driver corresponding to the Microstep driving, making it possible to configure the sophisticated, high precision and low noise lens driver system. Microstep controller is incorporated into IC, making it possible to cut down CPU power. In addition, drivers for DC motor and voice coil motor are built in. Multifunctional lens can be applied.

#### Features

- Built-in 7 channels Driver block.

1-6ch: Voltage control type H-bridge

- 7ch: Current control type H-bridge Built-in 2 channels PI driving circuit

- Built-in 2 channels Pronving circuit

Built-in 3 channels Waveforming circuit

#### Applications

Digital still cameras

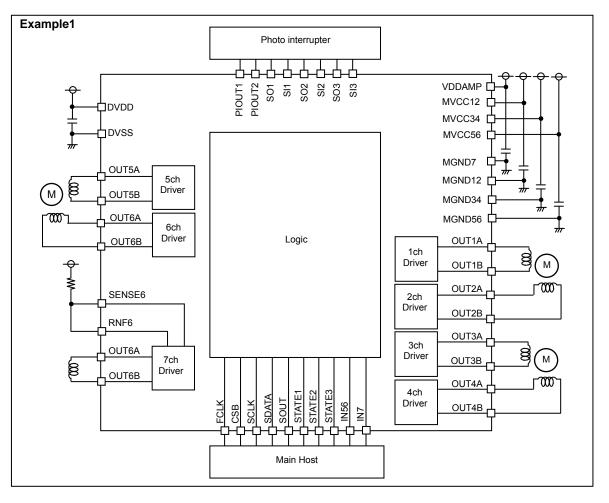

#### Typical Application Circuit

#### •Key Specifications

- Digital power supply voltage:

- Driver power supply voltage:

- Output current (1-7ch):

- Input clock frequency:

- FET ON resistance (1-6ch):

- FET ON resistance (7ch):

- Operating temperature range:

#### Package

VCSP85H3

3.80mm x 3.80mm x 1.00mm

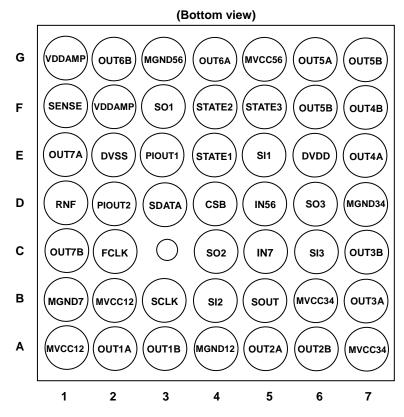

# Pin Configuration

## Pin Description

| In Desci              | iption   |                 |                                                                               |                       |          |                 |                                                       |

|-----------------------|----------|-----------------|-------------------------------------------------------------------------------|-----------------------|----------|-----------------|-------------------------------------------------------|

| Land<br>Matrix<br>No. | Pin name | Power<br>supply | Function                                                                      | Land<br>Matrix<br>No. | Pin name | Power<br>supply | Function                                              |

| E6                    | DVDD     | -               | Digital power supply                                                          | A3                    | OUT1B    | MVCC12          | 1-channel driver B output                             |

| E2                    | DVSS     | -               | Ground                                                                        | A5                    | OUT2A    | MVCC12          | 2-channel driver A output                             |

| C2                    | FCLK     | DVDD            | main clock logic input                                                        | A6                    | OUT2B    | MVCC12          | 2-channel driver B output                             |

| D4                    | CSB      | DVDD            | Serial control chip select input                                              | A7, B6(*)             | MVCC34   | -               | 3-4channel<br>driver power supply                     |

| B3                    | SCLK     | DVDD            | Serial control clock input                                                    | D7                    | MGND34   | -               | 3-4channel<br>driver ground                           |

| D3                    | SDATA    | DVDD            | Serial control data input                                                     | B7                    | OUT3A    | MVCC34          | 3-channel<br>driver A output                          |

| B5                    | SOUT     | DVDD            | Serial control data output                                                    | C7                    | OUT3B    | MVCC34          | 3-channel<br>driver B output                          |

| E4                    | STATE1   | DVDD            | STATE1 1,2ch<br>condition logic output                                        | E7                    | OUT4A    | MVCC34          | 4-channel<br>driver A output                          |

| F4                    | STATE2   | DVDD            | STATE2 3,4ch<br>condition logic output                                        | F7                    | OUT4B    | MVCC34          | 4-channel<br>driver B output                          |

| F5                    | STATE3   | DVDD            | STATE 3 5,6ch<br>condition logic output 5,6ch<br>control logic input          | G5                    | MVCC56   | -               | 5-6channel<br>driver power supply                     |

| D5                    | IN56     | DVDD            | 5,6ch control logic input                                                     | G3                    | MGND56   | -               | 5-6channel<br>driver ground                           |

| C5                    | IN7      | DVDD            | 7ch control logic input                                                       | G6                    | OUT5A    | MVCC56          | 5-channel<br>driver A output                          |

| E3                    | PIOUT1   | DVDD            | PI driving output1                                                            | F6,G7(*)              | OUT5B    | MVCC56          | 5-channel<br>driver B output                          |

| D2                    | PIOUT2   | DVDD            | PI driving output2                                                            | G4                    | OUT6A    | MVCC56          | 6-channel<br>driver A output                          |

| E5                    | SI1      | DVDD            | 1ch<br>waveforming input(With<br>adjustment function of<br>threshold voltage) | G2                    | OUT6B    | MVCC56          | 6-channel<br>driver B output                          |

| B4                    | SI2      | DVDD            | 2ch waveforming input                                                         | D1                    | RNF      | -               | 7-channel<br>driver power supply                      |

| C6                    | SI3      | DVDD            | 3ch waveforming input                                                         | B1                    | MGND7    | -               | 7-channel driver ground                               |

| F3                    | SO1      | DVDD            | 1ch waveforming output                                                        | F2,G1(*)              | VDDAMP   | -               | Power supply of constant<br>current<br>driver control |

| C4                    | SO2      | DVDD            | 2ch waveforming output                                                        | F1                    | SENSE    | VDDAMP          | Negative input for constant<br>current driver control |

| D6                    | SO3      | DVDD            | 3ch waveforming output                                                        | E1                    | OUT7A    | RNF             | 7-channel<br>driver A output                          |

| A1, B2(*)             | MVCC12   | -               | 1-2channel<br>driver power supply                                             | C1                    | OUT7B    | RNF             | 7-channel<br>driver B output                          |

| A4                    | MGND12   | -               | 1-2channel driver ground                                                      | C3                    | INDEX    | -               | Index pin                                             |

| A2                    | OUT1A    | MVCC12          | 1-channel driver A output                                                     |                       |          |                 |                                                       |

(\*)It is not possible to use corner pin only. (Corner pins are A1, A7, G1, and G7.) Please use A1-B2, A7-B6, F2-G1, F6-G7 pair respectively or using B2, B6, F2, F6 only.

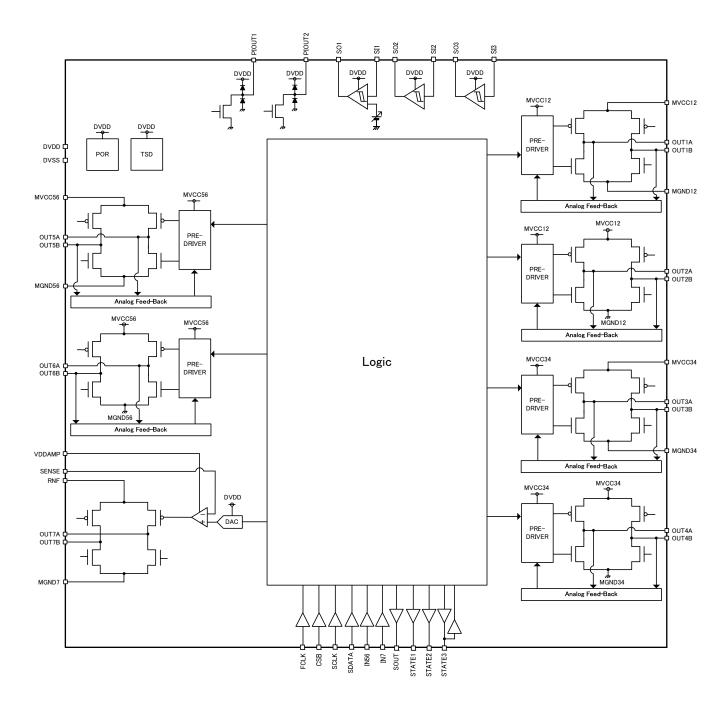

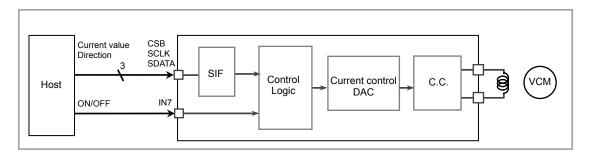

# Block Diagram

# Description of Blocks

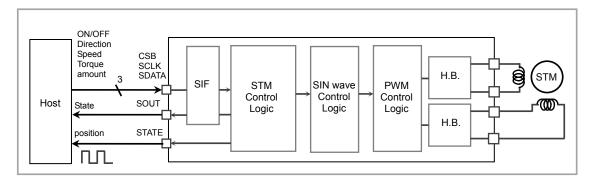

Stepping motor driver (1-6ch Driver)

Built-in the stepping motor driver of PWM driving type. 3 stepping motor can be driven.

Built-in the voltage feedback circuit of D-class type

(1) Control

( i )Autonomous control

The stepping motor is rotated by the setting of registers for the stepping motor control.

The state of rotation command(executing:1, finished:0), Cache register, and motor position are outputted from the serial output(SOUT pin). Also, the signal(MO output) synchronized with the motor rotation is outputted from STATE pin. It is possible to select the mode of stepping motor control from Micro-step(1024 portion), 1-2 phase excitation, 2 phase excitation

Built-in Cache registers.

As Cache registers enable to set the subsequent process while the motor is in operation,

it is possible to set the continuous operation.

## Description of Blocks

## Voltage driver (7ch driver)

Built-in the constant current driver.

The voltage of RNF pin and the external resistor(RRNF)are determined to the output current, and the internal high-precision amplifier(CMOS gate input)is exerted on the constant current control.

If any resistance component exists in the wirings of RNF pin and the external resistor(RRNF), the precision can be degraded.

To avoid that, pay utmost attention to the wirings.

#### (1) Control

## ( i )External pin control

The constant current driving is executed by the setting of register for the output current value and the direction and the control of IN7 pin for ON/OFF.

## ●Absolute Maximum Ratings(Ta=25°C)

| Parameter                   | Symbol | Limits                     | Unit | Remark                     |

|-----------------------------|--------|----------------------------|------|----------------------------|

|                             | DVDD   | -0.3 to 4.5                | V    |                            |

| Power supply voltage        | MVCC   | -0.3 to 7.0                | V    |                            |

|                             | VDDAMP | -0.3 to 7.0                | V    |                            |

| Input voltage               | VIN    | -0.3 to supply voltage+0.3 | V    |                            |

|                             | IIN    | ±500                       | mA   | Driver block (by MVCC pin) |

| Input/output current        |        | +100                       | mA   | by PIOUT pin               |

| Storage temperature range   | TSTG   | -55 to 125                 | °C   |                            |

| Operating temperature range | TOPE   | -20 to 85                  | °C   |                            |

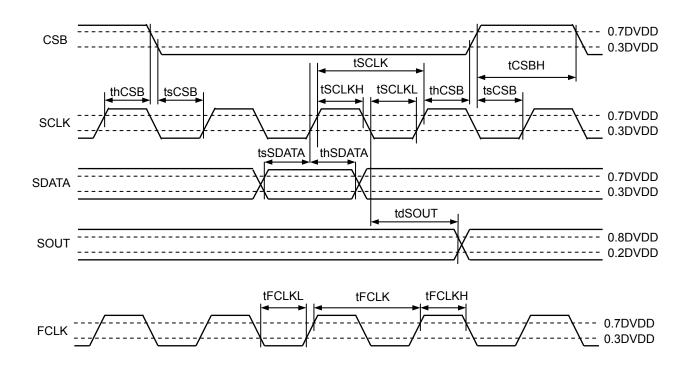

| Permissible dissipation *1  | PD     | 1370                       | mW   |                            |

\*1 To use at a temperature higher than Ta=25 °C, derate 13.7mW per 1 °C (At mounting 50mm x 58mm x 1.75mm glass epoxy board.)

# ●Recommended Operating Rating (Ta=25°C)

| Parameter                                                  | Symbol | Limits     | Unit | Remark          |

|------------------------------------------------------------|--------|------------|------|-----------------|

| Digital power supply voltage                               | DVDD   | 2.7 to 3.6 | V    | DVDD≦MVCC       |

| Driver power supply voltage                                | MVCC   | 2.7 to 5.5 | V    |                 |

| Constant current control<br>Amplifier power supply voltage | VDDAMP | 2.7 to 5.5 | V    |                 |

| Clock operating frequency                                  | FCLK   | 1 to 27.5  | MHz  | Reference clock |

# •Electrical Characteristics

(Unless otherwise specified,Ta=25°C, DVDD=3.0V,MVCC=5.0V,VDDAMP=5.0V,DVSS=MGND=0.0V)

| Parameter                                              | Symbol | NAINI       | Limits   | NAAX        | Unit | Condition                                       |

|--------------------------------------------------------|--------|-------------|----------|-------------|------|-------------------------------------------------|

| <current consumption=""></current>                     |        | MIN.        | TYP.     | MAX.        |      |                                                 |

| Quiescence (DVDD)                                      | ISSD   | _           | 30       | 100         | uA   | CMD_RS=0                                        |

| (MVCC)                                                 | ISSVM  | _           | 0        | 10          | uA   |                                                 |

| Operation (DVDD)                                       | IDDD   | _           | 8.5      | 15.0        | mA   | CMD_RS=1                                        |

| <logic block=""></logic>                               |        |             |          |             |      |                                                 |

| Low-level input voltage                                | VIL    | DVSS        | _        | 0.3DVDD     | V    |                                                 |

| High-level input voltage                               | VIH    | 0.7DVDD     | -        | DVDD        | V    |                                                 |

| Low-level input current                                | IIL    | 0           | -        | 10          | uA   | VIL=DVSS                                        |

| High-level input current                               | ΠΗ     | 0           | -        | 10          | uA   | VIH=DVDD                                        |

| Low-level output voltage                               | VOL    | DVSS        | -        | 0.2DVDD     | V    | IOL=1.0mA                                       |

| High-level output voltage                              | VOH    | 0.8DVDD     | -        | DVDD        | V    | IOH=1.0mA                                       |

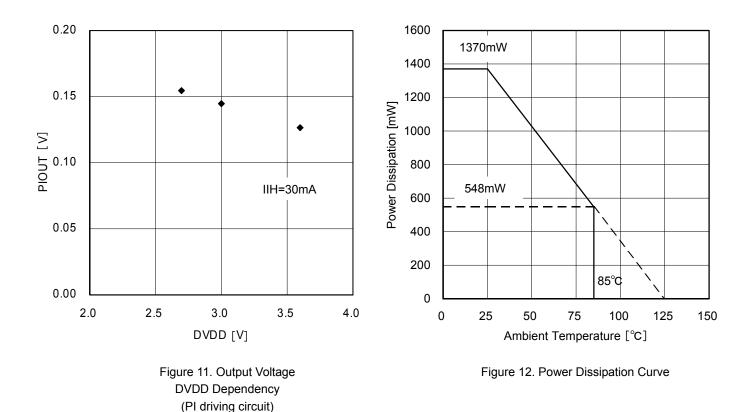

| <pi circuit="" driving=""></pi>                        |        |             |          |             |      |                                                 |

| Output voltage                                         | PIVO   | -           | 0.28     | 0.50        | V    | IIH=50mA                                        |

| <waveforming 1ch="" circuit=""></waveforming>          |        |             |          |             |      |                                                 |

| Detective voltage range                                | Vth    | 0.5         | -        | 2.5         | V    | SI1                                             |

| Detective voltage error                                | V      | 1/2DVDD-0.1 | 1/2DVDD  | 1/2DVDD+0.1 | V    | Waveforming Vth = 20h setting                   |

| <waveforming 2,3ch="" circuit=""></waveforming>        |        | <u> </u>    | <u> </u> |             |      |                                                 |

| High-level threshold voltage                           | VthH1  | -           | -        | 1.9         | v    | SI2,SI3(DVDD=3.25V)<br>Hys ON                   |

| Low-level threshold voltage                            | VthL1  | 0.6         | -        | -           | v    | SI2,SI3(DVDD=3.25V)<br>Hys ON                   |

| Hysteresis width                                       | HYS    | 0.2         | -        | 0.6         | v    | SI2,SI3(DVDD=3.25V)<br>Hys ON                   |

| threshold voltage                                      | VthH2  | 1.0         | -        | 1.85        | v    | SI2,SI3(DVDD=3.25V)<br>Hys OFF                  |

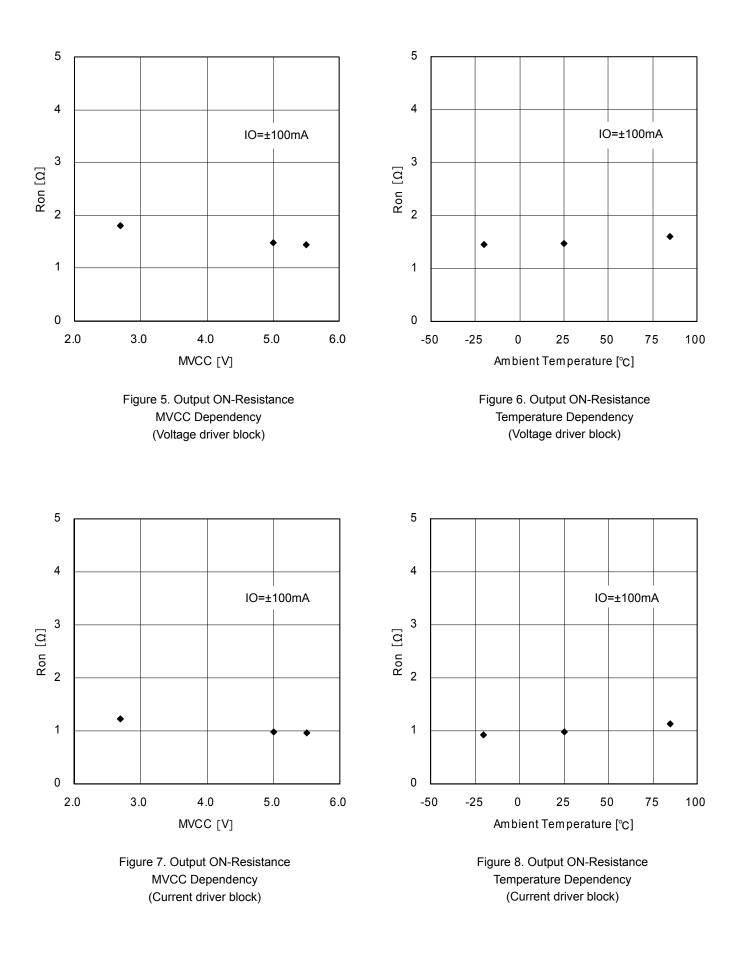

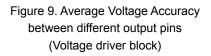

| < Voltage driver block >                               |        |             | I        |             |      | L                                               |

| ON-resistance                                          | Ron    | -           | 1.5      | 2.0         | Ω    | IO=±100mA<br>(the sum of high and low<br>sides) |

| OFF-leak current                                       | IOZ    | -10         | 0        | 10          | uA   | Output Hiz setting                              |

| Turn-ON time                                           | tON    | -           | 0.15     | 1.0         | uS   |                                                 |

| Turn-OFF time                                          | tOFF   | -           | 0.1      | 0.5         | uS   |                                                 |

| Average voltage accuracy between different output pins | Vdiff  | -5          | -        | +5          | %    | Vdiff = 2.0V setting.                           |

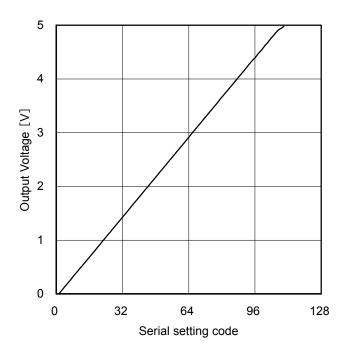

| <current block="" driver=""></current>                 | -      |             |          | 1           |      |                                                 |

| ON-resistance                                          | Ron    | -           | 0.9      | 1.5         | Ω    | IO=±100mA<br>(the sum of high and low<br>sides) |

| OFF-leak current                                       | IOZ    | -10         | 0        | 10          | uA   | Output Hiz setting                              |

| Output voltage                                         | VO     | 188         | 200      | 212         | mV   | DAC setting : 1010_0111<br>RRNF=1Ω              |

| Turn-ON time                                           | tON    | -           | 0.15     | 1.0         | uS   |                                                 |

| Turn-OFF time                                          | tOFF   | -           | 0.1      | 0.5         | uS   |                                                 |

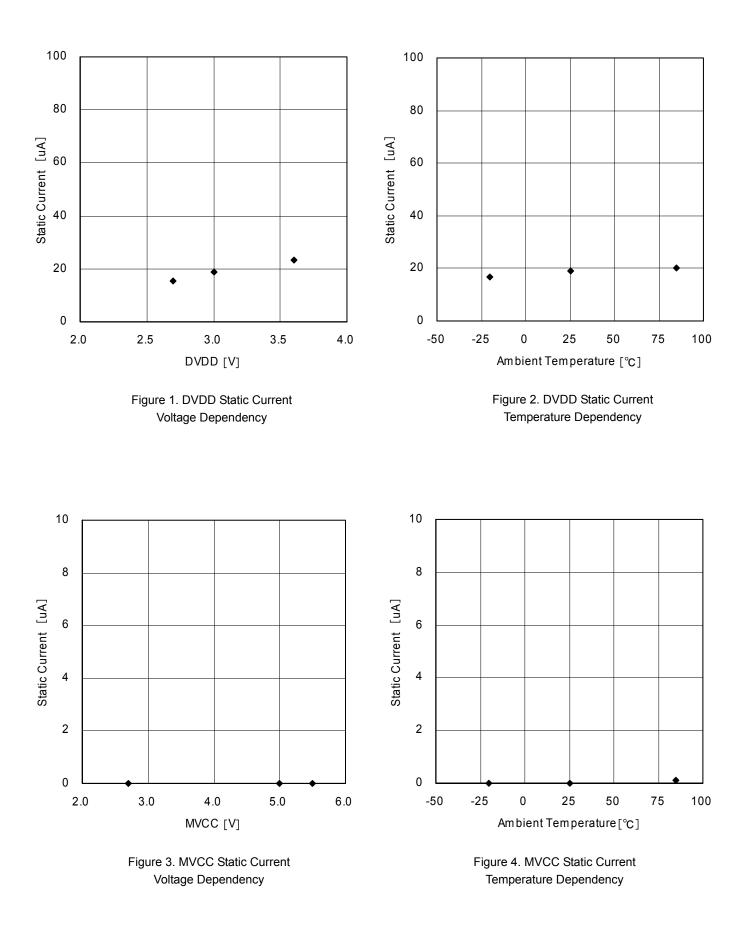

# Typical Performance Curves

(Unless otherwise specified,Ta=25°C,DVDD=3.0V,MVCC=5.0V,DVSS=MGND=0.0V)

## Typical Performance Curves

(Unless otherwise specified,Ta=25°C,DVDD=3.0V,MVCC=5.0V,DVSS=MGND=0.0V)

# Typical Performance Curves

(Unless otherwise specified,Ta=25°C,DVDD=3.0V,MVCC=5.0V,DVSS=MGND=0.0V)

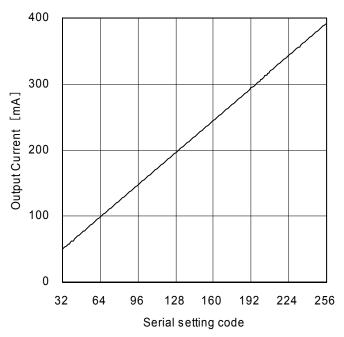

Figure 10. Output Current (Current driver block, RRNF =  $1.0 \Omega$ , RL =  $5.0 \Omega$ )

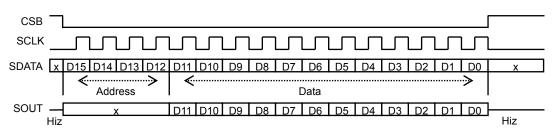

# Timing Chart

(Unless otherwise specified, Ta=25°C, DVDD=3.0V)

| Parameter               | Symbol  | Specification      |

|-------------------------|---------|--------------------|

| SCLK input cycle        | tSCLK   | more than 125 nsec |

| SCLK L-level input time | tSCLKL  | more than 50 nsec  |

| SCLK H-level input time | tSCLKH  | more than 50 nsec  |

| SDATA setup time        | tsSDATA | more than 50 nsec  |

| SDATA hold time         | thSDATA | more than 50 nsec  |

| CSB H-level input time  | tCSBH   | more than 800 nsec |

| CSB setup time          | tsCSB   | more than 50 nsec  |

| CSB hold time           | thCSB   | more than 50 nsec  |

| SOUT output delay time  | tdSOUT  | more than 50 nsec  |

| FCLK input cycle        | tFCLK   | more than 36 nsec  |

| FCLK L-level input time | tFCLKL  | more than 18 nsec  |

| FCLK H-level input time | tFCLKH  | more than 18 nsec  |

(note1) FCLK is asynchronous with SCLK. (note2) Duty of FCLK, SCLK are free.

### Serial interface

Control commands are framed by 16-bit serial input (MSB first) and input through the CSB, SCLK, and SDATA pins. 4 higher-order bits specify addresses, while the remaining 12 bits specify data.

Data of every bit is input through the SDATA pin, retrieved on the rising edges of SCLK.

Data becomes valid in the CSB Low area. The loading timing is different in the resistor. (as shown in "Note 5,6")

Furthermore, the interface will be synchronized with the falling edges of SCLK to output the SOUT data of the 12 bits.

#### <Register map>

|    |                 | 10   |    |         |        |                    |                                                                                                                         |                                                                    | Data                  | 44.01      |             |             |                                                           |                |             |  |  |

|----|-----------------|------|----|---------|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------|------------|-------------|-------------|-----------------------------------------------------------|----------------|-------------|--|--|

| AC | dre             | ss[3 | -  |         |        |                    |                                                                                                                         |                                                                    | Data                  |            |             |             |                                                           |                |             |  |  |

|    | 14              | 13   | 12 | 11      | 10     | 9                  | 8                                                                                                                       | 7                                                                  | 6                     | 5          | 4           | 3           | 2                                                         | 1              | 0           |  |  |

| 0  | 0               | 0    | 0  | Mode    | · ·    | SelA               |                                                                                                                         |                                                                    |                       |            |             |             |                                                           |                |             |  |  |

|    |                 |      |    | 0       | 0      | 0 0 Ach_Cycle[7:0] |                                                                                                                         |                                                                    |                       |            |             |             |                                                           |                |             |  |  |

| 0  | 0               | 0    | 1  | 0       | 0      | 1                  | 0                                                                                                                       |                                                                    |                       |            | Ach_Cy      | cle[15:8]   |                                                           | 1              |             |  |  |

|    |                 |      |    | 1       | 1      | 1                  | 0                                                                                                                       | 0                                                                  | 0                     | APOS       |             | 0           | 0                                                         | 0              | ASTOP       |  |  |

| 0  | 0               | 1    | 0  | EnA     | RtA    |                    | Ach_Pulse[9:0]                                                                                                          |                                                                    |                       |            |             |             |                                                           |                |             |  |  |

| 0  | 0               | 1    | 1  | Ach sta |        |                    |                                                                                                                         | 0                                                                  | Ach c                 |            | ulse numbe  |             |                                                           |                |             |  |  |

| 0  | 1               | 0    | 0  | Mode    |        | SelB               |                                                                                                                         | 0                                                                  |                       |            | Bch differe |             | oltage[6:0]                                               |                |             |  |  |

|    |                 |      |    | 0       | 0      | 0                  | 0                                                                                                                       |                                                                    |                       |            | Bch Cy      |             |                                                           |                |             |  |  |

| 0  | 1               | 0    | 1  | 0       | 0      | 1                  | 0                                                                                                                       |                                                                    |                       |            | Bch Cyc     |             |                                                           |                |             |  |  |

|    |                 |      |    | 1       | 1      | 1                  | 0                                                                                                                       | 0                                                                  | 0                     |            | S[1:0]      | 0           | 0                                                         | 0              | BSTOP       |  |  |

| 0  | 1               | 1    | 0  | EnB     | RtB    |                    |                                                                                                                         |                                                                    |                       |            | ulse[9:0]   |             |                                                           |                |             |  |  |

| 0  | 1               | 1    | 1  | Bch sta |        |                    |                                                                                                                         |                                                                    | Bch c                 |            | ulse numbe  |             |                                                           |                |             |  |  |

| 1  | 0               | 0    | 0  | Mode    |        | SelC               |                                                                                                                         | 0                                                                  |                       |            | Cch differe |             | oltage[6:0]                                               |                |             |  |  |

|    |                 |      |    | 0       | 0      | 0                  | 0                                                                                                                       |                                                                    |                       |            | Cch_Cy      |             |                                                           |                |             |  |  |

|    | _               |      |    | 0       | 0      | 1                  | 0                                                                                                                       |                                                                    |                       |            |             | cle[15:8]   |                                                           |                |             |  |  |

| 1  | 0               | 0    | 1  | ) 1     | ) 1    | 1                  | 0                                                                                                                       | 1                                                                  | 5_PWM                 |            |             |             | 5ch_differe                                               |                |             |  |  |

|    |                 |      |    |         |        | 1                  | 1                                                                                                                       | 0                                                                  | 6_PWM                 |            |             |             | 6ch_differe                                               |                |             |  |  |

|    |                 |      |    | 1       | 1      | 1                  | 0                                                                                                                       | 0                                                                  | 0                     | C_PO       |             | 0           | 0                                                         | 0              | CSTOP       |  |  |

| 1  | 0               | 1    | 0  | EnC     | RtC    |                    |                                                                                                                         |                                                                    |                       | _          | ulse[9:0]   |             |                                                           |                |             |  |  |

| 1  | 0               | 1    | 1  | Cch sta |        |                    |                                                                                                                         |                                                                    |                       |            | ulse numbe  |             |                                                           |                |             |  |  |

| 1  | 1               | 0    | 0  | 0       | 0      | Chopp              |                                                                                                                         | CacheM                                                             |                       | SEL56[2:0] |             | P_CTRL      |                                                           | LK_DIV[2       | ::0]        |  |  |

|    |                 |      |    | 0       | 0      | 0                  | 0                                                                                                                       | 0                                                                  | 0                     | 0          | 0           | 0           | 0                                                         |                | 1 PI_CTRL2  |  |  |

|    |                 |      |    | 0       | 0      | 1                  | 0                                                                                                                       | 0                                                                  | 5_PULSE_CNT           | -          | BASE[1:0]   |             |                                                           | 6_PULSE        | E_BASE[1:0] |  |  |

|    |                 |      |    | 0       | 1      | 0                  | 0                                                                                                                       |                                                                    |                       |            | 5_PULSE_0   |             |                                                           |                |             |  |  |

|    |                 |      |    | 0       | 1      | 0                  | 1                                                                                                                       |                                                                    |                       |            | PULSE_      |             |                                                           |                |             |  |  |

|    |                 |      |    | 0       | 1      | 1                  | 0                                                                                                                       | 0                                                                  | EXT_EN                | 0          | EXT_RT      |             |                                                           | UM[3:0]        |             |  |  |

|    |                 | 0    |    | 1       | 0      | 0                  | 0                                                                                                                       |                                                                    | EXT_                  |            |             |             |                                                           | PAT0           |             |  |  |

| 1  | 1               | 0    | 1  | 1       | 0      | 0                  | 1                                                                                                                       |                                                                    | EXT_                  |            |             |             | -                                                         | PAT2           |             |  |  |

|    |                 |      |    | 1       | 0      | 1                  | 0                                                                                                                       |                                                                    | EXT_                  |            |             |             |                                                           | PAT4           |             |  |  |

|    |                 |      |    | 1       | 0      | 1                  | -                                                                                                                       | 1      EXT_PAT7      EXT_PAT6        0      EXT_PAT9      EXT_PAT8 |                       |            |             |             |                                                           |                |             |  |  |

|    |                 |      |    | 1<br>1  | 1      | 0                  | 0                                                                                                                       |                                                                    | EXT_PAT9<br>EXT_PAT11 |            |             |             |                                                           | PAT6<br>PAT10  |             |  |  |

|    |                 |      |    |         |        | 1                  | 0                                                                                                                       |                                                                    | EXT I                 |            |             |             |                                                           | PAT10<br>PAT12 |             |  |  |

|    |                 |      |    | 1       | 1      |                    | -                                                                                                                       |                                                                    |                       |            |             |             |                                                           |                |             |  |  |

|    |                 |      |    | 0       | 0      | 0                  | 1      EXT_PAT15      EXT_PAT14        0      0      Constant current driver reference voltage adjustment 8bit DAC[7:0] |                                                                    |                       |            | .01         |             |                                                           |                |             |  |  |

|    |                 |      |    | -       | -      | -                  | 0                                                                                                                       |                                                                    |                       |            |             | 0 Nonage ad | justment 8                                                |                |             |  |  |

|    |                 |      |    | 0       | 1<br>0 | 0                  | 0                                                                                                                       | 0                                                                  | 0                     | 0          | -           | •           |                                                           |                | [RL[1:0]    |  |  |

| 1  | 1               | 1    | 0  | 1       | 0      | 0                  | 1                                                                                                                       | 0                                                                  | 0                     |            |             |             | foming circuit 1 Vthh[5:0]<br>efoming circuit 1 Vthl[5:0] |                |             |  |  |

|    |                 |      |    | 1       | 0      | 1                  | 0                                                                                                                       | 0                                                                  | 0                     | 0          | 0           |             |                                                           | HYS3           | HYS2        |  |  |

|    |                 |      |    | 1       | 1      | 0                  | 0                                                                                                                       | 0                                                                  | 0                     | 0          | 0           | 0           | 0                                                         | 0              | CMD_RS      |  |  |

|    |                 |      |    | I       | I      | U                  | U                                                                                                                       | U                                                                  | U                     | U          | U           | U           | U                                                         | U              |             |  |  |

|    | dress<br>n thos |      |    |         |        |                    |                                                                                                                         |                                                                    | Setting p             | orohibited |             |             |                                                           |                |             |  |  |

(Note 1) The notations A, B, C in the register map correspond to Ach, Bch and Cch respectively.

(Note 2) The Ach is defined as 1ch and 2ch driver output, the Bch as 3ch and 4ch driver output, and Cch as 5ch and 6ch driver output. (Note 3) After resetting (Power ON reset, and CMD\_RS), "initial setting" is saved in all registers. (Note 4) The addresses 4'b0011, 4'b0111, and 4'b1011 have data (status[1:0], operation pulse number[9:0]), which are internal register values and output from the SOUT pin.

(Note 5) For Mode, different output voltage, Cycle, En, and Rt registers, data that are written before the access to the Pulse register becomes valid, and determined at the rising edge of CSB after the access to the Pulse register. (The Mode, different output voltage, Cycle, En, Rt, and Pulse registers contain Cache registers, but any registers other than those do not contain with such registers.)

(Note 6) For POS, STOP, PWM\_Ct, and different output voltage registers, data are determined at the rising edge of CSB,

and for any registers other than those, data are determined at the rising edge of 16th SCLK .

# Application Example

# BU24026GU

# ●I/O equivalence circuit

| Pin                                                                                               | Equivalent circuit | Pin                              | Equivalent circuit |

|---------------------------------------------------------------------------------------------------|--------------------|----------------------------------|--------------------|

| FCLK<br>CSB<br>SCLK<br>SDATA<br>IN56<br>IN7<br>SI2<br>SI3<br>* SI2,SI3 are the<br>Schmitt inputs. |                    | SENSE                            | VDDAMP VDDAMP      |

| SOUT<br>STATE1<br>STATE2<br>SO1<br>SO2<br>SO3                                                     |                    | PIOUT1<br>PIOUT2                 |                    |

| OUT1A<br>OUT1B<br>OUT2A<br>OUT2B                                                                  |                    | OUT3A<br>OUT3B<br>OUT4A<br>OUT4B |                    |

| OUT5A<br>OUT5B<br>OUT6A<br>OUT6B                                                                  |                    | OUT7A<br>OUT7B<br>RNF            |                    |

| STATE3                                                                                            |                    | SI1                              |                    |

#### Operational Notes

1) Absolute maximum ratings

If applied voltage, operating temperature range, or other absolute maximum ratings are exceeded, the LSI may be damaged. Do not apply voltages or temperatures that exceed the absolute maximum ratings. If you expect that any voltage or temperature could be exceeding the absolute maximum ratings, take physical safety measures such as fuses to prevent any conditions exceeding the absolute maximum ratings from being applied to the LSI.

2) GND potential

Maintain the GND pin at the minimum voltage even under any operating conditions.

Actually check to be sure that none of the pins have voltage lower than that of GND pin, including transient phenomena.

3) Thermal design

With consideration given to the permissible dissipation under actual use conditions, perform thermal design so that adequate margins will be provided.

- 4) Short circuit between pins and malfunctions To mount the LSI on a board, pay utmost attention to the orientation and displacement of the LSI. Faulty mounting to apply a voltage to the LSI may cause damage to the LSI. Furthermore, the LSI may also be damaged if any foreign matters enter between pins, between pin and power supply, or between pin and GND of the LSI.

- 5) Operation in strong magnetic field Make a thorough evaluation on use of the LSI in a strong magnetic field. Not doing so may malfunction the LSI.

- 6) Power ON sequence To turn ON the DVDD, be sure to reset at CMD\_RS register.

- 7) Thermal shutdown

The temperature protection circuit (TSD circuit) is a circuit absolutely intended to shut down this IC from thermal runaway, not intended to protect or warrant the IC. Consequently, do not use the IC on the assumption that it will continuously use or operate after operating this circuit.

PI drive circuit The output voltage of output PIOUT will not exceed the voltage of the power supply voltage DVDD.

status of this document

The Japanese version of this document is formal specification. A customer may use this translation version only for a reference to help reading the formal version.

If there are any differences in translation version of this document formal version takes priority

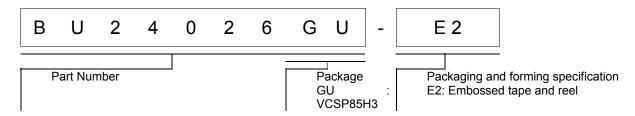

# Ordering Information

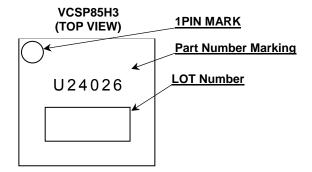

Marking Diagram

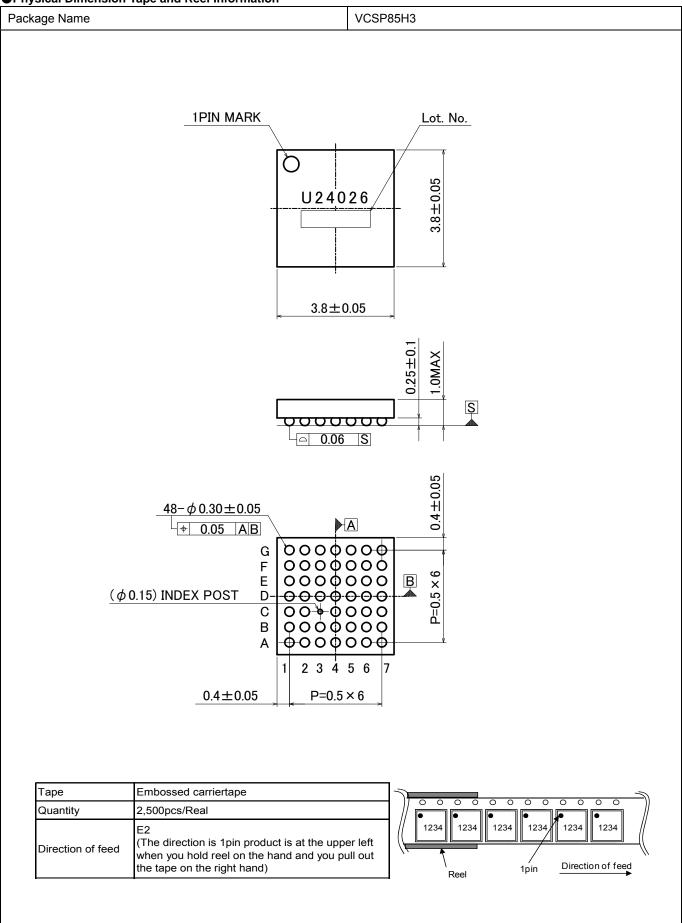

## Physical Dimension Tape and Reel Information

## Revision History

| <br>        |          |             |  |  |  |  |  |  |  |

|-------------|----------|-------------|--|--|--|--|--|--|--|

| Date        | Revision | Changes     |  |  |  |  |  |  |  |

| 26.Sep.2012 | 001      | New Release |  |  |  |  |  |  |  |

# Notice

#### General Precaution

- Before you use our Products, you are requested to carefully read this document and fully understand its contents. ROHM shall not be in any way responsible or liable for failure, malfunction or accident arising from the use of any ROHM's Products against warning, caution or note contained in this document.

- All information contained in this document is current as of the issuing date and subject to change without any prior notice. Before purchasing or using ROHM's Products, please confirm the latest information with a ROHM sales representative.

#### Precaution on using ROHM Products

- 1) Our Products are designed and manufactured for application in ordinary electronic equipments (such as AV equipment, OA equipment, telecommunication equipment, home electronic appliances, amusement equipment, etc.). If you intend to use our Products in devices requiring extremely high reliability (such as medical equipment, transport equipment, traffic equipment, aircraft/spacecraft, nuclear power controllers, fuel controllers, car equipment including car accessories, safety devices, etc.) and whose malfunction or failure may cause loss of human life, bodily injury or serious damage to property ("Specific Applications"), please consult with the ROHM sales representative in advance. Unless otherwise agreed in writing by ROHM in advance, ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of any ROHM's Products for Specific Applications.

- 2) ROHM designs and manufactures its Products subject to strict quality control system. However, semiconductor products can fail or malfunction at a certain rate. Please be sure to implement, at your own responsibilities, adequate safety measures including but not limited to fail-safe design against the physical injury, damage to any property, which a failure or malfunction of our Products may cause. The following are examples of safety measures:

- [a] Installation of protection circuits or other protective devices to improve system safety

- [b] Installation of redundant circuits to reduce the impact of single or multiple circuit failure

- 3) Our Products are designed and manufactured for use under standard conditions and not under any special or extraordinary environments or conditions, as exemplified below. Accordingly, ROHM shall not be in any way responsible or liable for any damages, expenses or losses arising from the use of any ROHM's Products under any special or extraordinary environments or conditions. If you intend to use our Products under any special or extraordinary environments or conditions (as exemplified below), your independent verification and confirmation of product performance, reliability, etc, prior to use, must be necessary:

- [a] Use of our Products in any types of liquid, including water, oils, chemicals, and organic solvents

- [b] Use of our Products outdoors or in places where the Products are exposed to direct sunlight or dust

- [c] Use of our Products in places where the Products are exposed to sea wind or corrosive gases, including Cl<sub>2</sub>, H<sub>2</sub>S, NH<sub>3</sub>, SO<sub>2</sub>, and NO<sub>2</sub>

- [d] Use of our Products in places where the Products are exposed to static electricity or electromagnetic waves

- [e] Use of our Products in proximity to heat-producing components, plastic cords, or other flammable items

- [f] Sealing or coating our Products with resin or other coating materials

- [g] Use of our Products without cleaning residue of flux (even if you use no-clean type fluxes, cleaning residue of flux is recommended); or Washing our Products by using water or water-soluble cleaning agents for cleaning residue after soldering

- [h] Use of the Products in places subject to dew condensation

- 4) The Products are not subject to radiation-proof design.

- 5) Please verify and confirm characteristics of the final or mounted products in using the Products.

- 6) In particular, if a transient load (a large amount of load applied in a short period of time, such as pulse) is applied, confirmation of performance characteristics after on-board mounting is strongly recommended. Avoid applying power exceeding normal rated power; exceeding the power rating under steady-state loading condition may negatively affect product performance and reliability.

- 7) De-rate Power Dissipation (Pd) depending on Ambient temperature (Ta). When used in sealed area, confirm the actual ambient temperature.

- 8) Confirm that operation temperature is within the specified range described in the product specification.

- 9) ROHM shall not be in any way responsible or liable for failure induced under deviant condition from what is defined in this document.

#### Precaution for Mounting / Circuit board design

- 1) When a highly active halogenous (chlorine, bromine, etc.) flux is used, the residue of flux may negatively affect product performance and reliability.

- 2) In principle, the reflow soldering method must be used; if flow soldering method is preferred, please consult with the ROHM representative in advance.

For details, please refer to ROHM Mounting specification

#### Precautions Regarding Application Examples and External Circuits

- If change is made to the constant of an external circuit, please allow a sufficient margin considering variations of the characteristics of the Products and external components, including transient characteristics, as well as static characteristics.

- 2) You agree that application notes, reference designs, and associated data and information contained in this document are presented only as guidance for Products use. Therefore, in case you use such information, you are solely responsible for it and you must exercise your own independent verification and judgment in the use of such information contained in this document. ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of such information.

#### Precaution for Electrostatic

This Product is electrostatic sensitive product, which may be damaged due to electrostatic discharge. Please take proper caution in your manufacturing process and storage so that voltage exceeding the Products maximum rating will not be applied to Products. Please take special care under dry condition (e.g. Grounding of human body / equipment / solder iron, isolation from charged objects, setting of lonizer, friction prevention and temperature / humidity control).

#### Precaution for Storage / Transportation

- 1) Product performance and soldered connections may deteriorate if the Products are stored in the places where:

- [a] the Products are exposed to sea winds or corrosive gases, including Cl2, H2S, NH3, SO2, and NO2

- [b] the temperature or humidity exceeds those recommended by ROHM

- [c] the Products are exposed to direct sunshine or condensation

- [d] the Products are exposed to high Electrostatic

- Even under ROHM recommended storage condition, solderability of products out of recommended storage time period may be degraded. It is strongly recommended to confirm solderability before using Products of which storage time is exceeding the recommended storage time period.

- 3) Store / transport cartons in the correct direction, which is indicated on a carton with a symbol. Otherwise bent leads may occur due to excessive stress applied when dropping of a carton.

- 4) Use Products within the specified time after opening a humidity barrier bag. Baking is required before using Products of which storage time is exceeding the recommended storage time period.

#### Precaution for Product Label

QR code printed on ROHM Products label is for ROHM's internal use only.

#### Precaution for Disposition

When disposing Products please dispose them properly using an authorized industry waste company.

#### Precaution for Foreign Exchange and Foreign Trade act

Since our Products might fall under controlled goods prescribed by the applicable foreign exchange and foreign trade act, please consult with ROHM representative in case of export.

#### Precaution Regarding Intellectual Property Rights

- 1) All information and data including but not limited to application example contained in this document is for reference only. ROHM does not warrant that foregoing information or data will not infringe any intellectual property rights or any other rights of any third party regarding such information or data. ROHM shall not be in any way responsible or liable for infringement of any intellectual property rights or other damages arising from use of such information or data.:

- 2) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of ROHM or any third parties with respect to the information contained in this document.

#### Other Precaution

- The information contained in this document is provided on an "as is" basis and ROHM does not warrant that all information contained in this document is accurate and/or error-free. ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties resulting from inaccuracy or errors of or concerning such information.

- 2) This document may not be reprinted or reproduced, in whole or in part, without prior written consent of ROHM.

- 3) The Products may not be disassembled, converted, modified, reproduced or otherwise changed without prior written consent of ROHM.

- 4) In no event shall you use in any way whatsoever the Products and the related technical information contained in the Products or this document for any military purposes, including but not limited to, the development of mass-destruction weapons.

- 5) The proper names of companies or products described in this document are trademarks or registered trademarks of ROHM, its affiliated companies or third parties.