### **Typical Applications**

The HMC892LP5E is ideal for:

- Test & Measurement Equipment

- Military RADAR & EW/ECM

- SATCOM & Space

- Industrial & Medical Equipment

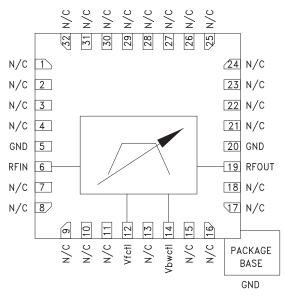

### **Functional Diagram**

#### **Features**

Fast Tuning Response; 200 ns

Excellent Wideband Rejection; >30 dB

Single Chip Replacement

for Mechanically Tuned Designs

32 Lead 5x5 mm SMT Package

#### **General Description**

The HMC892LP5E is a MMIC band pass filter which features a user selectable passband frequency. The 3 dB filter bandwidth is approximately 9%. The 20 dB filter bandwidth is approximately 23%. The center frequency can be varied between 4 and 7.7 GHz by applying an analog tune voltage between 0 and 14V. This tunable filter can be used as a much smaller alternative to physically large switched filter banks and cavity tuned filters. The HMC892LP5E has excellent microphonics due to the monolithic design, and provides a dynamically adjustable solution in advanced communications applications.

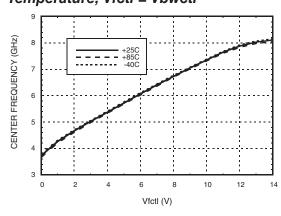

### Electrical Specifications, $T_A = +25$ °C, $V_{fctl} = V_{bwctl}$ Unless Otherwise Stated

| Parameter                                                            | Min. | Тур.                     | Max. | Units  |

|----------------------------------------------------------------------|------|--------------------------|------|--------|

| F <sub>center</sub> Tuning Range                                     | 4    |                          | 7.7  | GHz    |

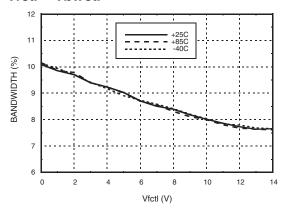

| 3 dB Bandwidth                                                       |      | 9                        |      | %      |

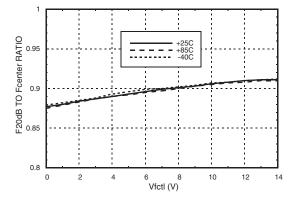

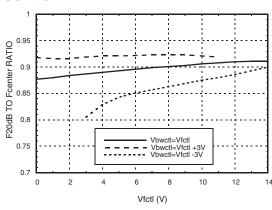

| Low Side Rejection Frequency (Rejection >20 dB)                      |      | 0.9*F <sub>center</sub>  |      | GHz    |

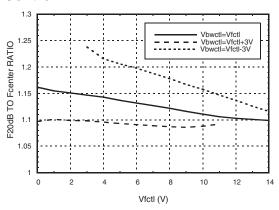

| High Side Rejection Frequency (Rejection >20 dB)                     |      | 1.13*F <sub>center</sub> |      | GHz    |

| Re-entry Frequency (Rejection <30 dB)                                |      | 2.5*F <sub>center</sub>  |      | GHz    |

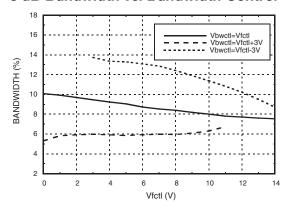

| 3 dB Bandwidth Control (V <sub>bwctl</sub> )                         |      | ±3                       |      | %      |

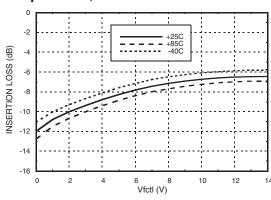

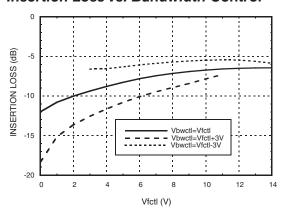

| Insertion Loss                                                       |      | 8                        |      | dB     |

| Return Loss                                                          |      | 9                        |      | dB     |

| Maximum Input Power for Linear Operation                             |      |                          | 10   | dBm    |

| Frequency Control Voltage (V <sub>fctl</sub> )                       | 0    |                          | 14   | V      |

| Source/Sink Current (I <sub>fctl</sub> )                             |      |                          | ±1   | mA     |

| Bandwidth Control Voltage (V <sub>bwctl</sub> )                      | 0    |                          | 14   | V      |

| Source/Sink Current (I <sub>bwctl</sub> )                            |      |                          | ±1   | mA     |

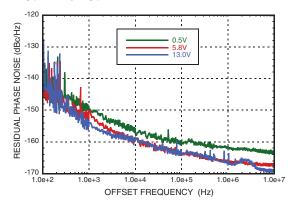

| Residual Phase Noise [1] (1 MHz Offset)                              |      | -165                     |      | dBc/Hz |

| F <sub>center</sub> Drift Rate                                       |      | -0.65                    |      | MHz/°C |

| Tuning Characteristics <sup>[2]</sup> tFULLBAND (0% Vfctl to 90% RF) |      | 200                      |      | ns     |

<sup>[1]</sup> Optimum residual phase noise performance requires the use of a low noise driver circuit.

<sup>[2]</sup> Tuning speed is dependent on driver circuit. Data measured with a high speed op-amp driver and includes driver slew rate delay.

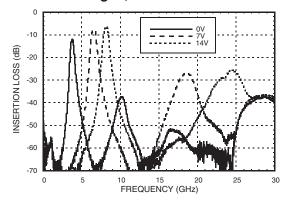

### Broadband Insertion Loss vs. Control Voltages, Vfctl = Vbwctl

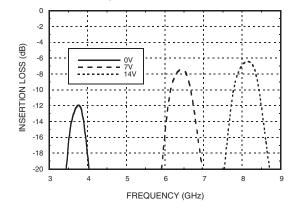

### Insertion Loss vs. Control Voltages, Vfctl = Vbwctl

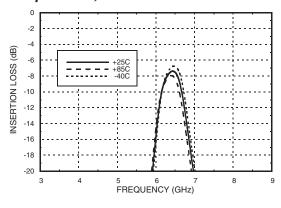

## Insertion Loss vs. Temperature, Vfctl = Vbwctl = 7V

## FILTER - TUNABLE, BAND PASS SMT 4.0 - 7.7 GHz

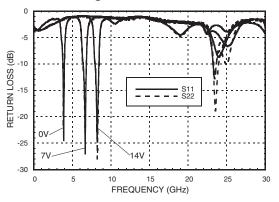

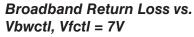

## Broadband Return Loss vs. Control Voltages, Vfctl = Vbwctl

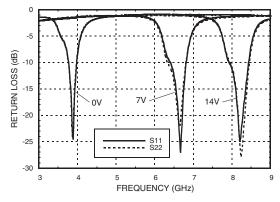

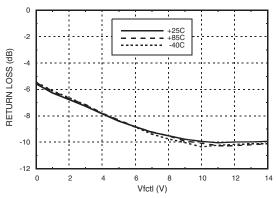

## Return Loss vs. Control Voltages, Vfctl = Vbwctl

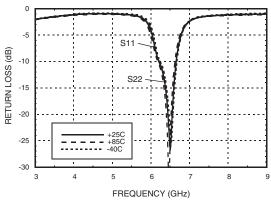

## Return Loss vs. Temperature, Vfctl = Vbwctl = 7V

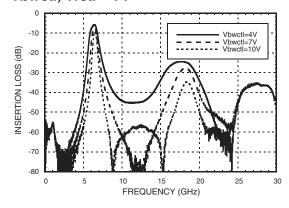

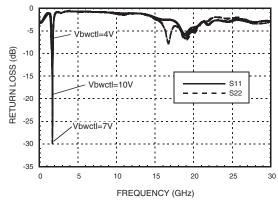

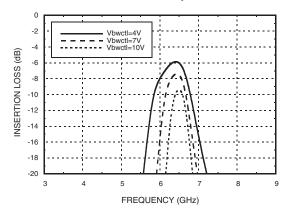

### Broadband Insertion Loss vs. Vbwctl, Vfctl = 7V

# 4.0 - 7.7 GHz

FILTER - TUNABLE, BAND PASS SMT

#### Insertion Loss vs. Vbwctl, Vfctl = 7V

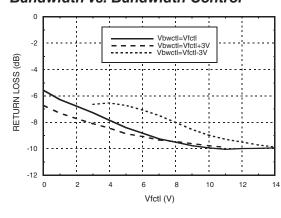

#### Return Loss vs. Vbwctl, Vfctl = 7V

## Center Frequency vs. Temperature, Vfctl = Vbwctl

## Insertion Loss vs. Temperature, Vfctl = Vbwctl

## 3 dB Bandwidth vs. Temperature, Vfctl = Vbwctl

## Low Side Rejection Ratio vs. Temperature, Vfctl = Vbwctl [1]

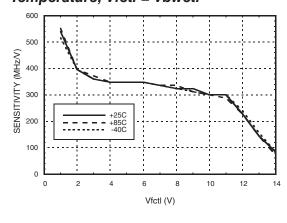

## Tuning Sensitivity vs. Temperature, Vfctl = Vbwctl

### FILTER - TUNABLE, BAND PASS SMT 4.0 - 7.7 GHz

## Maximum Return Loss in a 2 dB Bandwidth vs. Temperature, Vfctl = Vbwctl

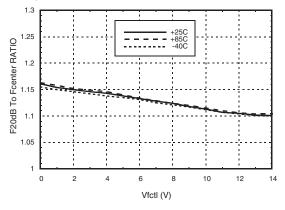

## High Side Rejection Ratio vs. Temperature, Vfctl = Vbwctl [1]

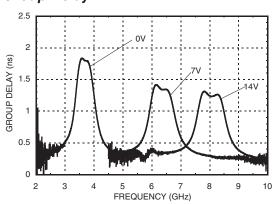

#### **Group Delay**

[1] Rejection ratio is defined as the ratio of the frequency at which the relative insertion loss is 20 dB to fcenter

#### 3 dB Bandwidth vs. Bandwidth Control

#### Insertion Loss vs. Bandwidth Control

## Low Side Rejection Ratio vs. Bandwidth Control [1]

High Side Rejection Ratio vs. Bandwidth Control [1]

## Maximum Return Loss in a 2 dB Bandwidth vs. Bandwidth Control

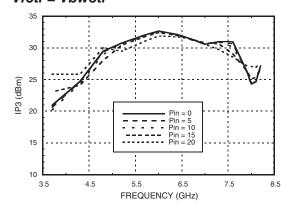

Input IP3 vs. Power Input Vfctl = Vbwctl

[1] Rejection ratio is defined as the ratio of the frequency at which the relative insertion loss is 20 dB to fcenter

#### **Residual Phase Noise** Vfctl = Vbwctl

### **Absolute Maximum Ratings**

| Frequency Control Voltage (Vfctl)  | -0.5 to +15V   |

|------------------------------------|----------------|

| Bandwidth Control Voltage (Vbwctl) | -0.5 to +15V   |

| RF Power Input                     | 26 dBm         |

| Storage Temperature                | -65 to +150 °C |

| ESD Rating (HBM)                   | Class 1B       |

#### ELECTROSTATIC SENSITIVE DEVICE **OBSERVE HANDLING PRECAUTIONS**

#### Reliability Information

| Junction Temperature to Maintain<br>1 Million Hour MTTF     | 150 °C        |  |

|-------------------------------------------------------------|---------------|--|

| Nominal Junction Temperature<br>(T= 85 °C and Pin = 10 dBm) | 90 °C         |  |

| Operating Temperature                                       | -40 to +85 °C |  |

|                                                             |               |  |

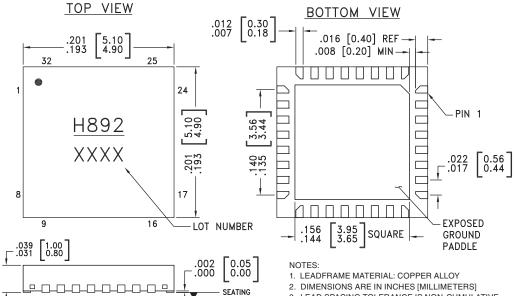

### **Outline Drawing**

- 2. DIMENSIONS ARE IN INCHES [MILLIMETERS]

- 3. LEAD SPACING TOLERANCE IS NON-CUMULATIVE.

- Pin BURR LENGTH SHALL BE 0.15mm MAXIMUM. Pin BURR HEIGHT SHALL BE 0.05mm MAXIMUM.

- 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm.

- ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

- 7. REFER TO HITTITE APPLICATION NOTE FOR SUGGESTED LAND PATTERN.

### Package Information

☐ .003[0.08] C

| Part Number | Package Body Material                              | Lead Finish   | MSL Rating | Package Marking [1] |

|-------------|----------------------------------------------------|---------------|------------|---------------------|

| HMC892LP5E  | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1 [2]   | <u>H892</u><br>XXXX |

- [1] 4-Digit lot number XXXX

- [2] Max peak reflow temperature of 260 °C

### **Pin Descriptions**

| Pin Number                            | Function | Description                                                                                                                              | Interface Schematic |

|---------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1 - 4, 7 - 11, 13<br>15 - 18, 21 - 32 | N/C      | The pins are not connected internally; however, all data shown herein was measured with these pins connected to RF/DC ground externally. |                     |

| 5, 20                                 | GND      | These pins and exposed paddle must be connected to RF/DC ground.                                                                         | GND O               |

| 6                                     | RFIN     | This pin is DC coupled and matched to 50 Ohms.<br>External voltage must not be applied to this pin.                                      | RFIN 250α 3nH       |

| 12                                    | Vfctl    | Center frequency control voltage.                                                                                                        | Vfctl 3nH 25000     |

| 14                                    | Vbwctl   | Bandwidth control voltage.                                                                                                               | Vbwctl 3nH 2500     |

| 19                                    | RFOUT    | This pin is DC coupled and matched to 50 Ohms.<br>External voltage must not be applied to this pin.                                      | 250n 3nH            |

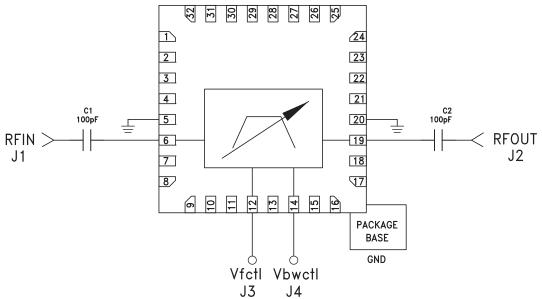

### **Application Circuit**

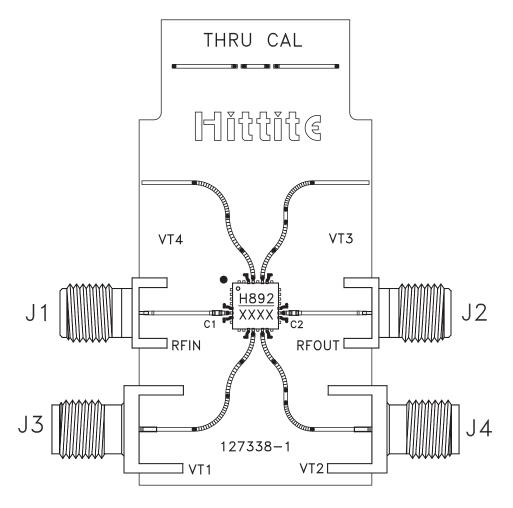

#### **Evaluation PCB**

#### List of Materials for Evaluation PCB 128531 [1]

| Item                 | Item Description            |  |

|----------------------|-----------------------------|--|

| J1, J2               | SMA - SRI                   |  |

| J3, J4               | SMA - Johnson               |  |

| C1, C2               | 100 pF Capacitor, 0402 Pkg. |  |

| U1 HMC892LP5E Filter |                             |  |

| PCB [2]              | 127338 Evaluation PCB       |  |

<sup>[1]</sup> Reference this number when ordering complete evaluation PCB[2] Circuit Board Material: Arlon 25FR or Rogers 25FR

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohms impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.