### Wide Input Voltage Range, High Efficiency 8-Channel Fault Tolerant LED Driver

### **Features and Benefits**

- Eight integrated high current sinks for LED strings; can be tied together for even higher currents

- Fixed frequency current mode control with integrated gate driver / boost controller; powerful gate driver to drive an external N-channel MOSFET allows significant scaling capability on the number of LEDs per string

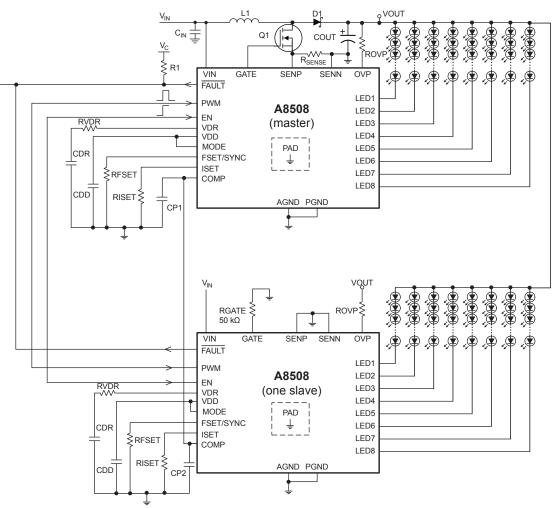

- Parallel operation capability with one boost controller (master) and up to three additional slave controllers; can run up to 32 strings of LEDs while populating only a single master boost regulator

- Active current sharing between LED strings for 0.7% accuracy and 0.8% matching

- Wide input voltage range: 9 to 40 V

- Internal bias supply for single-supply operation (typically  $V_{IN} = 12 \text{ or } 24 \text{ V}$ )

- Fset / Sync function to either set the boost converter switching frequency or synchronize at up to 800 kHz

- Protection Features

- Open or shorted LED pin protection

- Open Schottky protection

- Pulse-by-pulse current limit

- <sup>o</sup> Overtemperature protection (OTP)

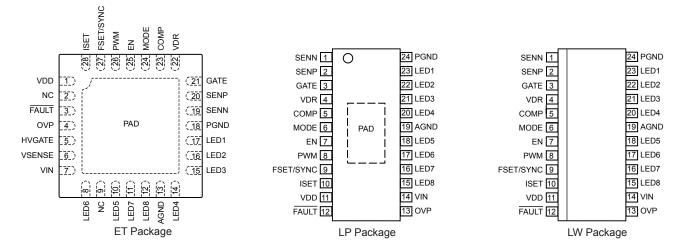

#### Packages (Not to scale)

24-pin TSSOP with Exposed Thermal Pad (LP package) 28-contact QFN with Exposed Thermal Pad (ET package)

### Description

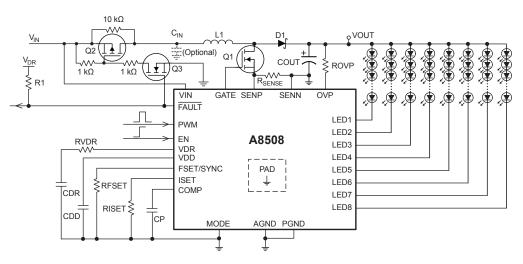

The A8508 is a multi-output white LED driver for backlighting LCD panels. It integrates a current-mode boost controller and eight individual current sinks.

The boost controller architecture allows for significant scaling of boost voltage to optimize the solution for the required number of LEDs per string. The FSET/SYNC pin either sets the required boost switching frequency or synchronizes the value in the range of 300 to 800 kHz.

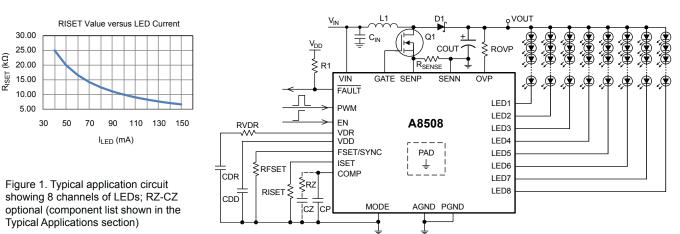

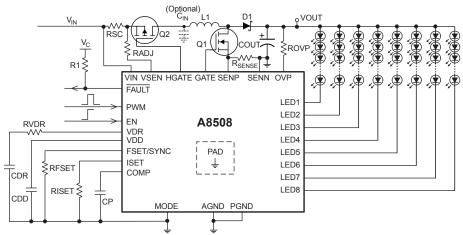

The LED sink current value is set by an external ISET resistor (see figure 1). The eight LED sinks can also be combined to achieve even higher current per LED string.

The A8508 provides protection against output shorts and overvoltage, open or shorted LED pins, and overtemperature. A dual-level, pulse-by-pulse current limit function provides soft start and protects the external current switch against high current overloads. As an option, the A8508 can drive an external P-FET interfaced to the FAULT pin to disconnect the input supply from the system in the event of short-to-ground in the boost converter.

The A8508 is available in a 24-pin TSSOP package (suffix LP) with an exposed thermal pad for enhanced thermal dissipation. Contact factory for additional options, including: a 24-pin SOICW (LW) or a a  $5 \times 5$  mm 28-contact QFN (ET) with exposed thermal pad. All packages are lead (Pb) free, with 100% matte tin leadframe plating.

### **Typical Application**

24-pin SOICW

(LW package)

#### Selection Guide

| Part Number               | Package                                 | Packing <sup>1</sup>        |

|---------------------------|-----------------------------------------|-----------------------------|

| A8508GETTR-T <sup>2</sup> | 28-contact QFN with exposed thermal pad | Contact factory             |

| A8508GLPTR-T              | 24-pin TSSOP with exposed thermal pad   | 4000 pieces per 13-in. reel |

| A8508GLWTR-T <sup>2</sup> | 24-pin SOICW                            | Contact factory             |

<sup>1</sup>Contact Allegro<sup>®</sup> for additional packing options. <sup>2</sup>Contact factory for availability.

#### Absolute Maximum Ratings\*

| Characteristic                                                              | Symbol               | Notes               | Rating      | Unit |

|-----------------------------------------------------------------------------|----------------------|---------------------|-------------|------|

| LEDx Pin Voltage                                                            | V <sub>LEDx</sub>    |                     | –0.3 to 55  | V    |

| OVP Pin Voltage                                                             | V <sub>OVP</sub>     |                     | -0.3 to 60  | V    |

| VIN Pin Voltage                                                             | V <sub>IN</sub>      |                     | -0.3 to 40  | V    |

| FAULT Pin Voltage                                                           | V <sub>FAULT</sub>   |                     | -0.3 to 40  | V    |

| COMP, EN, FSET/SYNC, ISET,<br>MODE, PWM, SENN, SENP, and VDD<br>Pin Voltage | _                    |                     | -0.3 to 5.5 | V    |

| GATE, VDR Pin Voltage                                                       | _                    |                     | –0.3 to 8   | V    |

| Operating Ambient Temperature                                               | T <sub>A</sub>       | G temperature range | -40 to 105  | °C   |

| Maximum Junction Temperature                                                | T <sub>J</sub> (max) |                     | 150         | °C   |

| Storage Temperature                                                         | T <sub>stg</sub>     |                     | –55 to 150  | °C   |

\*Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### Thermal Characteristics may require derating at maximum conditions, see application information

| Characteristic             | Symbol          | Test Conditions*                                   | Value | Unit |

|----------------------------|-----------------|----------------------------------------------------|-------|------|

|                            |                 | Package ET, on 4-layer PCB based on JEDEC standard | 32    | °C/W |

| Package Thermal Resistance | $R_{\theta JA}$ | Package LP, on 4-layer PCB based on JEDEC standard | 28    | °C/W |

|                            |                 | Package LW, on 4-layer PCB based on JEDEC standard | 44    | °C/W |

\*Additional thermal information available on the Allegro website

#### **Table of Contents**

| _ |                                           |        | Current sense resistor routing                    | 13       |

|---|-------------------------------------------|--------|---------------------------------------------------|----------|

|   | Specifications                            | 2      | Pulse-by-pulse current limit                      | 14       |

|   | Functional Block Diagram                  | 3      | Secondary boost switch limit                      | 14       |

|   | Pin-out Diagram and Terminal List         | 4      | Output overvoltage and undervoltage protection    | 14       |

|   | Electrical Characteristics Table          | 5      | LED Open Detect                                   | 15       |

|   | Functional Description<br>Enabling the IC | 8<br>8 | Undervoltage Protection (UVP)<br>LED short detect | 15<br>16 |

|   | Powering up: LED pin short-to-GND check   | 8      | Input UVLO                                        | 16       |

|   | Soft start function                       | 9      | VDD and VDR                                       | 16       |

|   | Frequency selection                       | 10     | Shutdown                                          | 17       |

|   | Synchronization                           | 10     | Fault protection during operation                 | 17       |

|   | LED current setting and LED dimming       | 11     | Application Information                           | 19       |

|   | PWM dimming                               | 12     | Paralleling more than one A8508                   | 19       |

|   | Analog dimming                            | 12     | Design Example                                    | 21       |

|   | Boost switch overcurrent protection       | 13     | Typical Applications                              | 24       |

|   | Setting the current sense resistor        | 13     | Package Outline Drawing                           | 27       |

|   |                                           |        |                                                   |          |

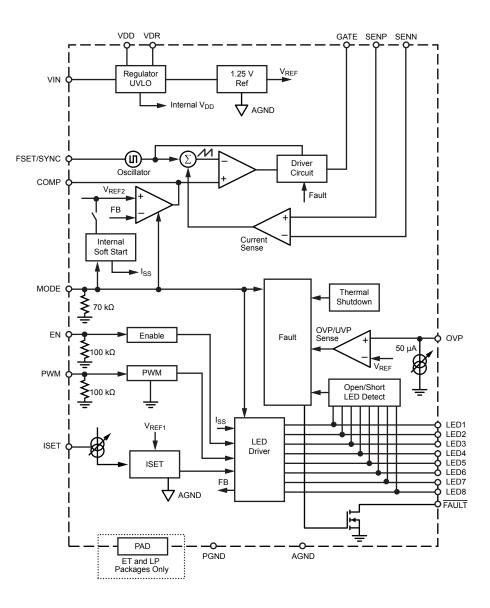

### **Functional Block Diagram**

## Wide Input Voltage Range, High Efficiency 8-Channel Fault Tolerant LED Driver

#### **Pin-out Diagrams**

#### **Terminal List Table**

| News                                                         | Nur                                         | nber                                         | Europática.                                                                                                                                                                                                                |  |  |  |  |  |

|--------------------------------------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Name                                                         | ET                                          | LP, LW                                       | Function                                                                                                                                                                                                                   |  |  |  |  |  |

| AGND                                                         | 13                                          | 19                                           | LED ground.                                                                                                                                                                                                                |  |  |  |  |  |

| COMP                                                         | 23                                          | 5                                            | Output of the error amplifier and compensation node. Connect a compensation network from this pin to ground.                                                                                                               |  |  |  |  |  |

| EN                                                           | 25                                          | 7                                            | Enable for the A8508.                                                                                                                                                                                                      |  |  |  |  |  |

| FAULT                                                        | 3                                           | 12                                           | This pin is used to indicate a fault condition. Connect a pull-up resistor between this pin and the required logic level voltage. The pin is an open drain type configuration that will be pulled low when a fault occurs. |  |  |  |  |  |

| FSET/SYNC                                                    | 27                                          | 9                                            | Frequency/synchronization pin. A resistor RFSET from this pin to ground sets the switching frequency. This pin can also be used to synchronize two or more converters in the system.                                       |  |  |  |  |  |

| GATE                                                         | 21                                          | 3                                            | Gate pin for driving external N-channel FET.                                                                                                                                                                               |  |  |  |  |  |

| HVGATE                                                       | 5                                           | n.a.                                         | Input disconnect switch: gate driver                                                                                                                                                                                       |  |  |  |  |  |

| ISET                                                         | 28                                          | 10                                           | Connect the RISET resistor between this pin and ground to set the 100% LED current.                                                                                                                                        |  |  |  |  |  |

| LED1<br>LED2<br>LED3<br>LED4<br>LED5<br>LED6<br>LED7<br>LED8 | 17<br>16<br>15<br>14<br>10<br>8<br>11<br>12 | 23<br>22<br>21<br>20<br>18<br>17<br>16<br>15 | Connect the cathode of each LED string to these pins.                                                                                                                                                                      |  |  |  |  |  |

| MODE                                                         | 24                                          | 6                                            | This pin is used to determine the mode of operation. MODE high tied to VDD allows parallel operation, and MODE low i used for single IC operation.                                                                         |  |  |  |  |  |

| OVP                                                          | 4                                           | 13                                           | This pin is used to sense an Overvoltage (OVP) condition. Connect the ROVP resistor from VOUT to this pin to adjust the overvoltage protection.                                                                            |  |  |  |  |  |

| PAD                                                          | _                                           | -                                            | For QFN and TSSOP packages, this exposed pad provides enhanced thermal dissipation. This pad must be connected to the ground plane(s) of the PCB with at least 8 vias, directly in the PAD solder pad.                     |  |  |  |  |  |

| PGND                                                         | 18                                          | 24                                           | Power ground for the internal gate driver circuit.                                                                                                                                                                         |  |  |  |  |  |

| PWM                                                          | 26                                          | 8                                            | PWM dimming pin. Used to control the LED intensity by using pulse width modulation. The typical PWM dimming frequency is in the range of 100 to 1000 Hz.                                                                   |  |  |  |  |  |

| SENN                                                         | 19                                          | 1                                            | Negative sense line for boost switch current sensing.                                                                                                                                                                      |  |  |  |  |  |

| SENP                                                         | 20                                          | 2                                            | Positive sense line for boost switch current sensing.                                                                                                                                                                      |  |  |  |  |  |

| VDD                                                          | 1                                           | 11                                           | Output of internal LDO regulator. Connect a 0.1 µF decoupling capacitor between this pin and ground.                                                                                                                       |  |  |  |  |  |

| VDR                                                          | 22                                          | 4                                            | Output of the gate driver bias voltage regulator. Connect a 0.22 $\mu$ F capacitor in series with a 7.5 $\Omega$ resistor between this pin and ground.                                                                     |  |  |  |  |  |

| VIN                                                          | 7                                           | 14                                           | Input power to the A8508.                                                                                                                                                                                                  |  |  |  |  |  |

| VSENSE                                                       | 6                                           | n.a.                                         | Input disconnect switch: current sense                                                                                                                                                                                     |  |  |  |  |  |

### **ELECTRICAL CHARACTERISTICS**<sup>1</sup> Valid at $V_{IN} = 12 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ , • indicates specifications guaranteed by design and characterization over the full operating temperature range with $T_A = T_{.1} = -40^{\circ}\text{C}$ to 105°C; unless otherwise noted

| Characteristics                            | Symbol                 | ol Test Conditions                                  |       | Min. | Тур. | Max. | Unit |

|--------------------------------------------|------------------------|-----------------------------------------------------|-------|------|------|------|------|

| Input Voltage Specifications               |                        |                                                     |       |      |      |      |      |

| Operating Input Voltage Range              | V <sub>IN</sub>        |                                                     | •     | 9    | -    | 40   | V    |

| UVLO Start Threshold                       | V <sub>UVLO(th)</sub>  | V <sub>IN</sub> rising                              | •     | -    | -    | 8.5  | V    |

| UVLO Hysteresis                            | V <sub>UVLO(hys)</sub> | V <sub>IN</sub> falling                             |       | _    | 400  | _    | mV   |

| Input Currents                             |                        |                                                     | · _ · |      |      |      |      |

| Input Quiescent Current                    | Ι <sub>Q</sub>         | $EN = V_{IH}$ ; f <sub>SW</sub> = 800 kHz, no load  |       | -    | 7    | -    | mA   |

| Input Sleep Supply Current                 | I <sub>QSLEEP</sub>    | V <sub>IN</sub> = 12 V, EN = FSET/SYNC = 0 V        | •     | -    | 0.5  | 10.0 | μA   |

| Input Logic Levels (EN, PWM, MO            | DE, FSET/SYN           | C)                                                  |       |      |      |      |      |

| Input Logic Level-Low                      | V <sub>IL</sub>        | 9 V < V <sub>IN</sub> < 40 V                        | •     | _    | _    | 400  | mV   |

| Input Logic Level-High                     | V <sub>IH</sub>        | 9 V < V <sub>IN</sub> < 40 V                        | •     | 1.5  | _    | _    | V    |

| EN and PWM Pins Pull-Down<br>Resistor      | R <sub>pulldown</sub>  | EN, PWM= 5 V                                        |       | -    | 100  | -    | kΩ   |

| MODE Pin Pull-Down Resistor                | R <sub>MODE</sub>      | MODE=2.5 V                                          |       | -    | 70   | -    | kΩ   |

| Error Amplifier                            |                        |                                                     |       |      |      |      |      |

| Open Loop Voltage Gain                     | A <sub>VOL</sub>       |                                                     |       | -    | 47   | -    | dB   |

| Transconductance                           | g <sub>m</sub>         | $\Delta I_{\text{COMP}} = \pm 10 \ \mu \text{A}$    |       | -    | 990  | -    | µA/V |

| Source Current                             | I <sub>EA(SRC)</sub>   | $V_{COMP}$ = 1.5 V                                  |       | -    | -360 | -    | μA   |

| Sink Current MODE High                     | I <sub>EA(SINK)H</sub> | $V_{COMP}$ = 1.5 V, MODE = $V_{IH}$                 |       | -    | 80   | -    | μA   |

| Sink Current MODE Low                      | I <sub>EA(SINK)L</sub> | $V_{COMP}$ = 1.5 V, MODE = $V_{IL}$                 |       | -    | 360  | -    | μA   |

| COMP Pin Pull-Down Resistor                | R <sub>COMP</sub>      | FAULT = 0                                           |       | -    | 1.5  | -    | kΩ   |

| Soft Start COMP Level                      | V <sub>COMPSS</sub>    |                                                     |       | -    | 200  | -    | mV   |

| Overvoltage Protection                     |                        |                                                     |       |      |      |      |      |

| Overvoltage Threshold                      | V <sub>OVP(th)</sub>   | OVP connected to VOUT                               | •     | 1.11 | 1.25 | 1.4  | V    |

| OVP Sense Current                          | I <sub>OVPH</sub>      |                                                     | •     | 45   | 49   | 53   | μA   |

|                                            | V <sub>UVP(LOW)</sub>  | Falling                                             |       | -    | 100  | -    | mV   |

| Output Undervoltage Threshold VUVP(HIGH)   |                        | Rising                                              |       | -    | 120  | -    | mV   |

| Boost Switch Gate Driver                   |                        |                                                     |       |      |      |      |      |

| Gate Driver Voltage                        | V <sub>DRV</sub>       | Measured at GATE pin                                |       | -    | 7    | -    | V    |

| Driver Pull-up and Pull-down<br>Resistance | R <sub>GATEUD</sub>    | Measured at V <sub>GATE</sub> =V <sub>DRV</sub> / 2 |       | -    | 4.5  | -    | Ω    |

| Driver to Ground Resistance                | R <sub>GATEG</sub>     | EN = 0, VIN = 0                                     |       | -    | 200  | -    | kΩ   |

| Sense Positive                             | V <sub>SENSEP</sub>    |                                                     | •     | 85   | 100  | 115  | mV   |

| Secondary Sense Positive                   | V <sub>SENSESEC</sub>  |                                                     |       | -    | 165  | -    | mV   |

Continued on the next page ...

## **ELECTRICAL CHARACTERISTICS**<sup>1</sup> (continued) Valid at $V_{IN} = 12 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ , • indicates specifications guaranteed by design and characterization over the full operating temperature range with $T_A = T_J = -40^{\circ}\text{C}$ to 105°C; unless otherwise noted

| Characteristics                                     | Symbol                 | Test Conditions                                                                          |   | Min. | Тур.  | Max. | Unit |

|-----------------------------------------------------|------------------------|------------------------------------------------------------------------------------------|---|------|-------|------|------|

| Boost Switch Gate Driver (contin                    | ued)                   |                                                                                          |   |      |       |      |      |

| Soft Start Boost Current Limit<br>Reference Voltage | V <sub>SWSS(LIM)</sub> | Reference voltage for boost switch current limit during soft start.                      |   | -    | 39    | -    | mV   |

| Minimum Switch On-Time                              | t <sub>SWONTIME</sub>  |                                                                                          |   | -    | -     | 110  | ns   |

| Minimum Switch Off-Time                             | t <sub>SWOFFTIME</sub> |                                                                                          |   | -    | -     | 85   | ns   |

| Oscillator Frequency                                |                        |                                                                                          |   |      |       |      |      |

|                                                     |                        | R <sub>FSET</sub> = 7.5 kΩ                                                               | • | 725  | 800   | 875  | kHz  |

| Oscillator Frequency                                | f <sub>SW</sub>        | R <sub>FSET</sub> = 10 kΩ                                                                | • | 540  | 600   | 660  | kHz  |

|                                                     |                        | R <sub>FSET</sub> = 20 kΩ                                                                |   | -    | 300   | -    | kHz  |

| FSET/SYNC Pin Voltage                               | V <sub>FSET</sub>      | R <sub>FSET</sub> = 8.25 kΩ                                                              |   | -    | 1.00  | -    | V    |

| Synchronization                                     |                        |                                                                                          |   |      |       |      |      |

| Synchronized PWM Frequency                          | f <sub>SWSYNC</sub>    |                                                                                          | • | 300  | -     | 800  | kHz  |

| Synchronization Input<br>Minimum Off-Time           | t <sub>PWSYNCOFF</sub> |                                                                                          |   | 150  | -     | -    | ns   |

| Synchronization Input<br>Minimum On-Time            | t <sub>PWSYNCON</sub>  |                                                                                          | • | 150  | -     | -    | ns   |

| LED Current Sinks                                   | ·                      |                                                                                          |   |      |       |      |      |

| LEDx Accuracy                                       | Err <sub>LED</sub>     | I <sub>SET</sub> = 100 μA                                                                |   | _    | 0.7   | _    | %    |

| LEDx Matching                                       | ΔLEDx                  | I <sub>SET</sub> = 100 μA                                                                |   | _    | 0.8   | 2.5  | %    |

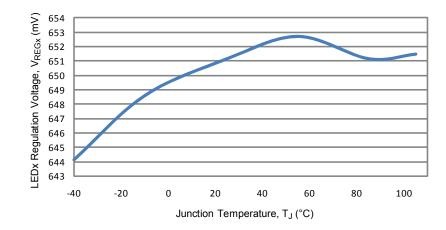

| LEDx Regulation Voltage                             | V <sub>LED</sub>       | $V_{LED1}$ through $V_{LED8}$ all equal, $I_{SET}$ = 100 $\mu$ A                         |   | -    | 650   | -    | mV   |

| I <sub>SET</sub> to I <sub>LEDx</sub> Current Gain  | A <sub>ISET</sub>      | Ι <sub>SET</sub> = 100 μΑ                                                                |   | _    | 1160  | _    | A/A  |

| ISET Pin Voltage                                    | V <sub>ISET</sub>      |                                                                                          |   | -    | 1.000 | -    | V    |

| Allowable ISET Current                              | I <sub>SET</sub>       |                                                                                          | • | 34   | -     | 130  | μA   |

| LEDx Pin Short Detect                               | V <sub>LEDSC</sub>     | While LED sinks are in regulation, sensed from LEDx pin to GND                           |   | 4.6  | -     | -    | V    |

| Soft Start LEDx Current Gain                        | I <sub>LEDSS</sub>     | Current through each enabled LEDx pin<br>during soft start, $R_{ISET}$ = 12.4 k $\Omega$ |   | -    | 44    | -    | A/A  |

| PWM High to LED-On Delay                            | t <sub>dPWM(on)</sub>  | Time between PWM enable and LEDx current reaching 90% of maximum                         | • | -    | 0.5   | 1.1  | μs   |

| PWM Low to LED-Off Delay                            | t <sub>dPWM(off)</sub> | Time between PWM enable going low and LEDx current reaching 10% of maximum               | • | -    | -     | 500  | ns   |

Continued on the next page ...

6

## **ELECTRICAL CHARACTERISTICS**<sup>1</sup> (continued) Valid at $V_{IN} = 12 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ , • indicates specifications guaranteed by design and characterization over the full operating temperature range with $T_A = T_J = -40^{\circ}\text{C}$ to 105°C; unless otherwise noted

| Characteristics                          | Symbol                | ol Test Conditions                                    |  | Min. | Тур. | Max. | Unit |

|------------------------------------------|-----------------------|-------------------------------------------------------|--|------|------|------|------|

| FAULT Pin                                |                       |                                                       |  |      |      |      |      |

| FAULT Pin Pull-Down Voltage              | V <sub>FAULT</sub>    | $I_{FAULT}$ = 1 mA (400 Ω internal switch resistance) |  | -    | 0.4  | -    | V    |

| FAULT Pin Leakage Current                | I <sub>FAULTLKG</sub> | V <sub>FAULT</sub> = 5 V                              |  | -    | -    | 1    | μA   |

| Thermal Protection (TSD)                 |                       |                                                       |  |      |      |      |      |

| Thermal Shutdown Threshold <sup>2</sup>  | T <sub>SD</sub>       | Temperature rising                                    |  | -    | 165  | -    | °C   |

| Thermal Shutdown Hysteresis <sup>2</sup> | T <sub>SDHYS</sub>    |                                                       |  | -    | 20   | -    | °C   |

<sup>1</sup>For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive

current is defined as going into the node or pin (sinking).

<sup>2</sup>Ensured by design and characterization, not production tested.

### **Functional Description**

### Enabling the IC

The IC turns on when a logic high signal is applied on the EN pin, and the input voltage present on the VIN pin is greater than the 8.5 V necessary to clear the UVLO ( $V_{UVLOrise}$ ) threshold. Before the LEDs are enabled, the A8508 driver goes through a system check to determine if there are any possible fault conditions that might prevent the system from functioning correctly.

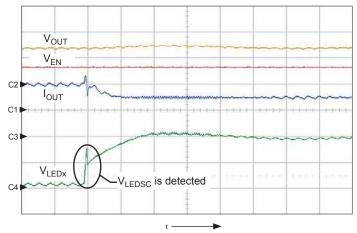

### Powering up: LED pin short-to-GND check

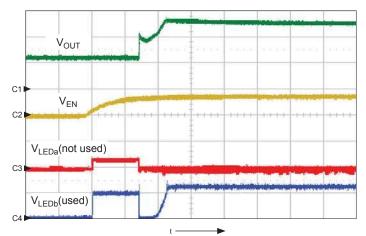

After the VIN pin goes above the UVLO threshold, and a high signal is present on the EN pin, the IC proceeds to check if any LEDx pins are shorted to GND and/or are not used. Each unused pin should be connected to GND with a 4.75 k $\Omega$  pull-down resistor.

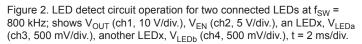

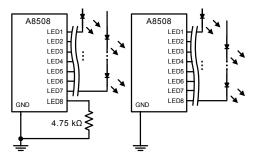

After the voltage threshold on the LEDx pins exceeds 120 mV, a timer of 1536 clock cycles (2 ms at 800 kHz switching frequency, see figure 2) is applied during which the A8508 determines the status of the pins. Any unused pin connected to GND with the pull-down resistor will be taken out of regulation at this point and will not contribute to the boost regulation loop (see figure 3). A typical example is shown in figure 4. When a pin is connected to GND through a 4.75 k $\Omega$  resistor, the voltage on that LEDx pin during the LED detection period is about 200 mV. This is shown in figure 2.

If an LEDx pin is shorted to ground such that LEDx pin voltage is < 100 mV, the A8508 will not proceed with soft start until the short is removed from the LEDx pin. This prevents the A8508

Figure 3. LED detect circuit operation for an LED pin that is not being used; shows V<sub>OUT</sub> (ch1, 10 V/div.), V<sub>EN</sub> (ch2, 5 V/div.), an unused LEDx with a 4.75 k $\Omega$  resistor from this pin to GND, V<sub>LEDa</sub> (ch3, 500 mV/div.), and a used LEDx, V<sub>LEDb</sub> (ch4, 500 mV/div.), t = 2 ms/div.

Figure 4. Channel select setup: (left) channel LED8 not used, (right) using all channels.

Figure 5. LED detect circuit operation: device powers-up after the short is removed from the LED pin; shows V<sub>OUT</sub> (ch1, 10 V/div.), V<sub>EN</sub> (ch2, 5 V/ div.), an LEDx with short, V<sub>LEDa</sub> (ch3, 500 mV/div.), and an LEDx without short, V<sub>LEDb</sub> (ch4, 500 mV/div.), t = 2 ms/div.

## Wide Input Voltage Range, High Efficiency 8-Channel Fault Tolerant LED Driver

from powering-up and putting an uncontrolled amount of current through the LEDs. After the short is removed the affected LEDx pin will rise up to the 500 mV level. When the LEDx pin voltage exceeds the 260 mV threshold, the IC detects connected LEDs and proceeds with LED detection and soft start. Figure 2 shows a case when two LED channels are enabled. During the LED detection period, voltage on both LEDx pins > 260 mV. Figure 5 shows a case with LEDa temporarily shorted to ground and LEDb in normal operation.

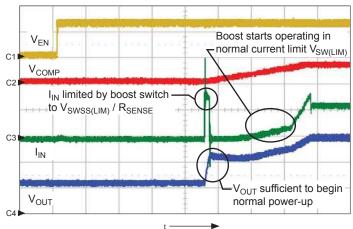

### Soft start function

During soft start the LED current gain is reduced to  $(I_{LEDSS})$ . As an example, for a 120 mA output current, the soft-start LED current would be set to about 4.5 mA (see figure 7). Also during soft start the boost switch sense voltage is reduced to the  $I_{SWSS(LIM)}$  level, to limit the initial inrush current generated by the charging of the output capacitors. The actual current limit  $(I_{LIM})$  is equal to:

$$I_{\rm LIM} = V_{\rm SWSS(LIM)} / R_{\rm SENSE}$$

(1)

where  $V_{SWSS(LIM)}$  is found in the Electrical Characteristics table, and  $R_{SENSE}$  is the current sense resistor value.

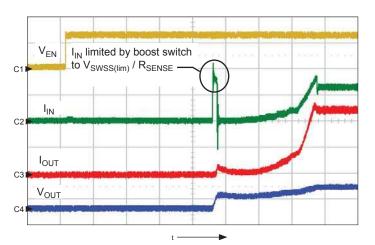

Figure 6. Start-up operation, individual LEDx current = 60 mA, boost sense resistor =  $0.020 \Omega$ ; shows V<sub>EN</sub> (ch1, 2 V/div.), I<sub>IN</sub> (ch2, 1 A/div.), I<sub>OUT</sub> (ch3, 200 mA/div.), and V<sub>OUT</sub> (ch4, 20 V/div.), t = 500 µs/div.

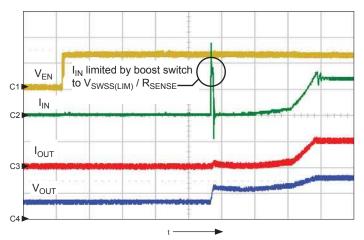

When the converter senses that there is enough voltage on the LEDx pins, the converter proceeds to increase the LED current to the preset regulation current and the boost switch current sense voltage limit is switched to the  $I_{SW(LIM)}$  level to allow the A8508 to deliver the necessary output power to the LEDs (figure 8).

Figure 7. Start-up operation, individual LEDx current = 120 mA, boost sense resistor = 0.010  $\Omega$ ; shows V<sub>EN</sub> (ch1, 2 V/div.), I<sub>IN</sub> (ch2, 2 A/div.), I<sub>OUT</sub> (ch3, 1 A/div.), and V<sub>OUT</sub> (ch4, 20 V/div.), t = 500 µs/div.

Figure 8. Normal start-up behavior; shows VEN (ch1, 2 V/div.), V<sub>COMP</sub> (ch2, 2 V/div.), I<sub>IN</sub> (ch3, 1 V/div.), and V<sub>OUT</sub> (ch4, 10 V/div.), t = 500  $\mu$ s/div.

### **Frequency selection**

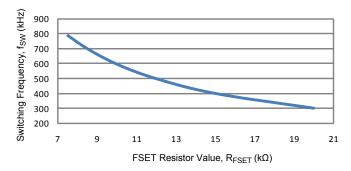

The switching frequency on the boost regulator is set by connecting a resistor, RFSET, between the FSET/SYNC pin and ground. The switching frequency range is 300 to 800 kHz, with example values of:

| R <sub>FSET</sub> Value<br>(kΩ) | Swtiching Frequency, f <sub>SW</sub><br>(kHz) |

|---------------------------------|-----------------------------------------------|

| 7.5                             | 800                                           |

| 10                              | 600                                           |

The relationship of  $R_{\rm FSET}$  and  $f_{\rm SW}$  is shown in figure 9.

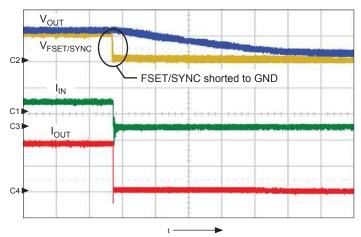

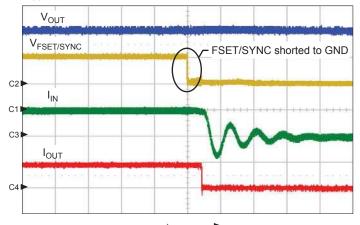

The FSET/SYNC pin has short-to-ground protection. If the FSET/SYNC pin is held low for more than 4  $\mu$ s typical, the A8508 will stop switching and disable the LEDx pins (see figures 10 and 11). If the FSET/SYNC pin is released at any time after 7  $\mu$ s, the A8508 will proceed to soft start but will not perform the LED detection phase.

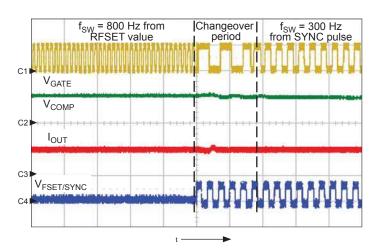

### Synchronization

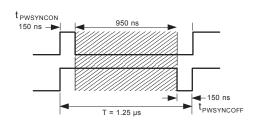

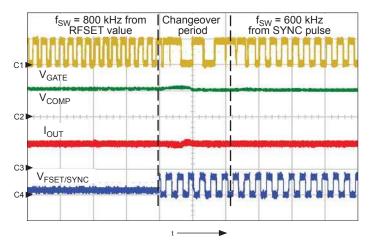

The A8508 can also be synchronized by using an external clock connected to the FSET/SYNC pin. The synchronization function of IC was designed to work with a push-pull type of clock driver. The amplitude of the clock signal should be between 1.5 and 3.3 V. The synchronization clock should have duty cycles that meet the minimum on/off times. Figure 12 shows the timing for a synchronization clock into the A8508 at 800 kHz. The 150 ns minimum on-time and 150 ns minimum off-time are

Figure 9. Switching Frequency as determined by R<sub>FSET</sub> value.

Figure 10. Shutdown when the FSET/SYNC pin is shorted to ground; shows V<sub>OUT</sub> (ch1, 10 V/div.), V<sub>FSET/SYNC</sub> (ch2, 1 V/div.), I<sub>IN</sub> (ch3, 2 A/div.), and I<sub>OUT</sub> (ch4, 500 mA/div.), t = 200  $\mu$ s/div.

Figure 11. Zoomed-in view of figure 9, showing quick shutdown when FSET/SYNC shorted to ground, preventing IC running at very high frequency; shows V<sub>OUT</sub> (ch1, 10 V/div.), V<sub>FSET/SYNC</sub> (ch2, 1 V/div.), I<sub>IN</sub> (ch3, 2 A/div.), and I<sub>OUT</sub> (ch4, 1 A/div.), t = 10 µs/div.

Figure 12. SYNC pulse minimum on and off time requirements, for an 800-kHz clock.

indicated by the specifications for  $t_{PWSYNCON}$  and  $t_{PWSYNCOFF}$ . Thus any pulse with a duty cycle of 19% to 85% at 800 kHz will synchronize the IC.

It is recommended to also use the RFSET resistor with the external clock signal. If a synchronization clock is lost during operation, the IC will revert to the preset switching frequency that is set by the RFSET resistor. In this configuration the preset frequency does not have any restrictions other than the normal operating range of 300 to 800 kHz. During the changeover period the IC stops switching for an approximately 5  $\mu$ s period to allow the synchronization detection circuitry to switch over to the external preset switching frequency.

Although examples shown in figures 13 and 14 are extreme cases of clock-to-resistor frequency changes, it is recommended that actual applications not have such large switching frequency changes. In most applications the RFSET resistor and clock frequency should be very close to each other in terms of frequency. Setting the frequencies close together will prevent the system from experiencing large changes on frequency-dependent signals and components, such as the inductor ripple current and the compensation resistor and capacitor.

### LED current setting and LED dimming

The maximum LED current can be up to 150 mA per channel. The LED current is set through the RISET resistor connected between the ISET pin and ground. The  $I_{LED}$  current is set according to the following formula:

$$R_{\rm ISET} = (1.000 / I_{\rm LED}) \times 1160$$

(2)

where  $R_{ISET}$  is in  $\Omega$ , and  $I_{LED}$  is in A. This sets the maximum current through the LEDs, referred to as the *100% current*. Standard  $R_{ISET}$  values are as follows:

| Standard Resistor Value<br>Closest to R <sub>ISET</sub><br>(kΩ) | LED current per LED, I <sub>LED</sub><br>(mA) |

|-----------------------------------------------------------------|-----------------------------------------------|

| 7.87                                                            | 150                                           |

| 9.53                                                            | 120                                           |

| 11.5                                                            | 100                                           |

| 14.3                                                            | 80                                            |

| 19.1                                                            | 60                                            |

Figure 13. Synchronization feature with 200 kHz difference between R<sub>FSET</sub> and external clock signal. The synchronization frequency is 600 kHz, and the resistor preset frequency is 800 kHz. Note that there is very little disturbance in the LED current at the time of changeover; shows V<sub>GATE</sub> (ch1, 5 V/div.), V<sub>COMP</sub> (ch2, 1 V/div.), I<sub>OUT</sub> (ch3, 1 A/div.), and V<sub>FSET/SYNC</sub> (ch4, 5 V/div.), t = 5  $\mu$ s/div.

Figure 14. Synchronization feature with 500 kHz difference between R<sub>FSET</sub> and external clock signal, illustrating the flexibility of the RFSET/SYNC pin; synchronization frequency is 300 kHz, and the resistor preset frequency is 800 kHz; shows V<sub>GATE</sub> (ch1, 5 V/div.), V<sub>COMP</sub> (ch2, 1 V/div.), I<sub>OUT</sub> (ch3, 1 A/div.), and V<sub>FSET/SYNC</sub> (ch4, 5 V/div.), t = 10 µs/div.

The cited values are for 1% tolerance resistors. If the calculated value was not present, the next lowest value of 1% resistor was chosen.

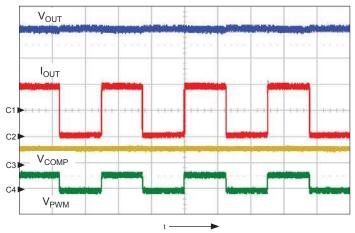

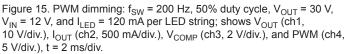

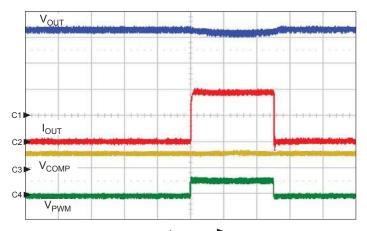

### **PWM** dimming

Applying an external PWM signal on the PWM pin performs PWM dimming. When the PWM pin is pulled high, the A8508 enables the LEDx pins to sink 100% current. When PWM is pulled low, the boost converter and LEDx sinks are turned off. The compensation (COMP) pin is floated, and critical internal circuits are kept active.

The typical PWM dimming frequencies fall between 100 and 1000 Hz. Figures 15 and 16 show examples of dimming at 50% and 0.5% duty cycles.

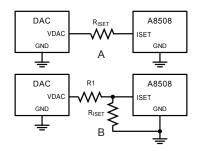

### Analog dimming

The A8508 can also be dimmed by using an external DAC or other voltage source applied either directly to the ground side of the RISET resistor or through an external resistor to the ISET pin (see figure 17). The ISET current can be varied in the range between 34  $\mu$ A and 130  $\mu$ A.

• For a single-resistor configuration (panel A of figure 17), the ISET current is controlled by the following formula:

$$I_{\text{SET}} = \frac{V_{\text{ISET}} - V_{\text{DAC}}}{R_{\text{ISET}}}$$

(3)

where  $V_{\mbox{\scriptsize ISET}}$  is the ISET pin voltage and  $V_{\mbox{\scriptsize DAC}}$  is the DAC output voltage.

• For a dual-resistor configuration (panel B of figure 17), the ISET current is controlled by the following formula:

$$I_{\text{SET}} = \frac{V_{\text{ISET}}}{R_{\text{ISET}}} - \frac{V_{\text{DAC}} - V_{\text{ISET}}}{R_1}$$

(4)

The advantage of this circuit is that the DAC voltage can be higher or lower, thus adjusting the LED current to a higher or lower value of the preset LED current set by the  $R_{ISET}$  resistor:

- $V_{DAC} = 1.00$  V: output is strictly controlled by  $R_{ISET}$

- $^{\rm o}$   $V_{DAC}$  > 1.00 V: LED current is reduced

- $^{\rm o}$   $V_{DAC}$  < 1.00 V: LED current is increased

Figure 16. PWM dimming:  $f_{SW} = 200$  Hz, 0.5% duty cycle,  $V_{OUT} = 30$  V,  $V_{IN} = 15$  V,  $I_{LED} = 120$  mA per LED string; shows  $V_{OUT}$  (ch1, 10 V/div.),  $I_{OUT}$  (ch2, 500 mA/div.),  $V_{COMP}$  (ch3, 2 V/div.), and  $V_{PWM}$  (ch4, 5 V/div.), t = 10 µs/div.

Figure 17. Typical application simplified diagram of voltage LED current control using a DAC to control LED current.

### Boost switch overcurrent protection

The boost switch is protected with pulse-by-pulse current limiting set by the external RSENSE resistor. There also is a secondary current limit that is sensed on the boost switch.

#### Setting the current sense resistor

The current sense resistor (see figure 18) is set according to the following formula:

$$I_{\rm LIM} = \frac{V_{\rm SENP}}{R_{\rm SENSE}} \tag{5}$$

where  $V_{SENP}$  is found in the Electrical Characteristics table, and  $R_{SENSE}$  is the current sense resistor value.

The current limit is calculated by the following formula:

$$I_{\rm LIM} = I_{\rm IN}(\rm max) + \frac{\Delta I_{\rm L}}{2}$$

(6)

where  $I_{IN}(max)$  is the maximum input current, and  $\Delta I_L$  is the inductor current ripple.

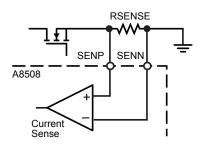

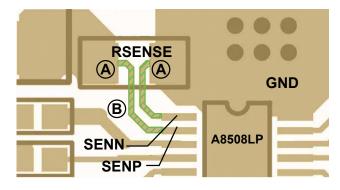

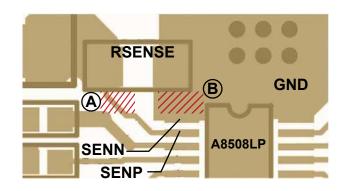

#### Current sense resistor routing

The current sense resistor must be routed as a differential pair to minimize measurement accuracy errors. For most current sense resistors the resistance is measured between the inside edges of the mounting pads of the RSENSE resistor.

Figure 19 shows correct differential current sensing connections to the A8508. The individual current sense traces are kept short and side-by-side to get proper signal voltage levels. The trace for the positive sense pin (SENP) must be routed to the inside edge of the mounting pad on the high side of RSENSE. The trace for the negative sense pin (SENN) must be routed to the inside edge of the mounting pad on the ground side of RSENSE.

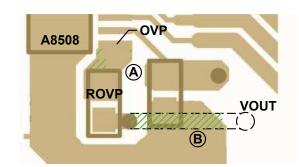

It should be noted that when designing the PCB layout, the trace for the negative sense pin (SENN) is often automatically merged with the ground flood fill and with the mounting pad on the ground side of RSENSE (shown in figure 20). However, the trace must be kept separate and dedicated, and careful attention must be given when routing the PCB.

Figure 18. Simplified schematic of the current sense resistor connections to the current sense amplifier.

Figure 20. Incorrect layout of current sense resistor traces: (A) do not connect to outside edge of pad, (B) do not merge trace into ground

#### Pulse-by-pulse current limit

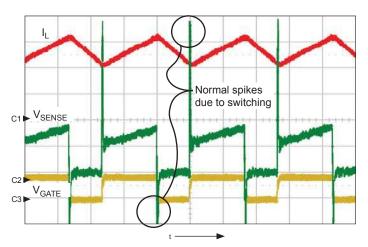

Figure 21 illustrates the normal waveform for the current sense signal. The pulse-by-pulse current limit is designed to limit the current through the external MOSFET to prevent failure. When the  $V_{\text{SENSEP}}$  threshold is reached, the IC stops switching to allow the inductor current to fall. Operation of pulse-by-pulse current limiting is shown in figure 22.

Figure 21. Current sense signal (V<sub>SENSE</sub>) during normal operation, showing large spikes that are filtered out by a blanking period to avoid false overcurrent tripping; R<sub>SENSE</sub> = 10 mΩ; shows inductor current I<sub>L</sub> (ch1, 1 A/div.), V<sub>SENSE</sub> (ch2, 20 mV/div.), and gate voltage of the main boost switch V<sub>GATE</sub> (ch3), t = 500 ns/div.

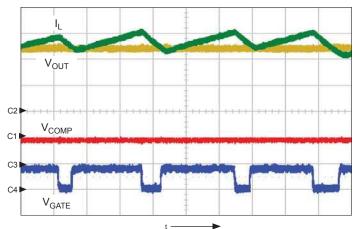

Figure 22. Typical pulse-by-pulse current limit; shows I<sub>L</sub> (ch1, 2 A/div.), V<sub>OUT</sub> (ch2, 10 V/div.), V<sub>COMP</sub> (ch3, 2 V/div.), and V<sub>GATE</sub> (ch4), t = 500 ns/div.

#### Secondary boost switch limit

In case there is an inductor short during operation ,the A8508 has a secondary switch current limit. When this threshold is reached, the IC immediately shuts down. The level of this current limit is set above the pulse-by-pulse current limit to protect the switch from destructive currents when the boost inductor is shorted.

# Output overvoltage and undervoltage protection

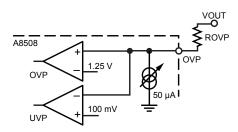

The OVP pin on the A8508 controls both the overvoltage (OVP) and undervoltage (UVP) protection features. The pin circuit is shown in figure 23. The OVP protection protects the boost converter from excessive voltage levels when the feedback control loop is broken, usually caused by an open connection from output voltage to the LEDs. The UVP function provides output voltage-to-ground short protection when an external disconnect switch is used. For more detailed information on disconnect switch application, see the Undervoltage Protection (UVP) section.

For proper operation of this pin, due to the relatively low voltage level, special care has to be taken during PCB layout. Figure 24 is an example of a proper PCB layout.

Figure 23. Simplified schematic of the Overvoltage Protection section.

Figure 24. OVP resistor connections; (A) connection should be short, (B) connection to VOUT can be long, and ROVP should be as close to the OVP pin as possible.

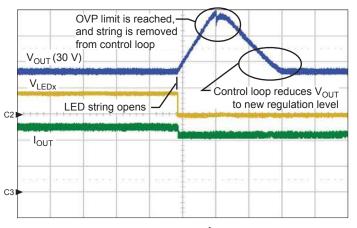

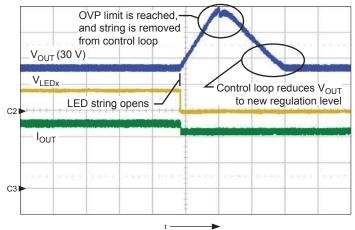

#### LED Open Detect

When any LED string opens, the boost control circuit increases the output voltage until it reaches the overvoltage protection level. The OVP event causes any LED string that is below regulation level to be disabled. After disabling the open string, the output voltage returns to normal operating voltage. An EN low signal will reset the LED string regulation lock.

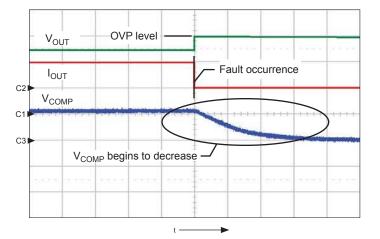

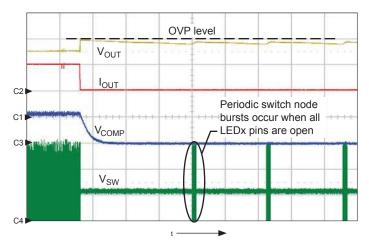

Figure 25 shows a typical overvoltage condition when the output voltage is disconnected from the LED load. Figure 26 shows an

extended view of the same situation. Figure 27 shows an OVP condition created by a single open LED string.

#### **Undervoltage Protection (UVP)**

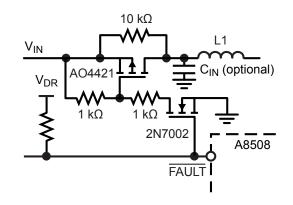

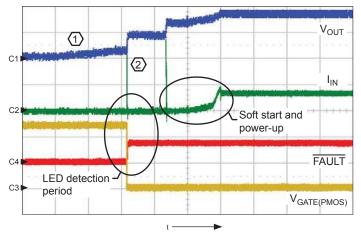

If the output voltage is shorted to ground the OVP pin will sense an undervoltage condition (UVP). When UVP is sensed, the IC sets the Fault flag low which, if used to interface to the outputdisconnect switch, will shut off the P-FET device. Figure 28 is a schematic showing the input disconnect switch implementation.

Figure 25. OVP operation with all LEDx pins open. V<sub>OUT</sub> rises to the overvoltage level and stays there until the IC is shut down; shows V<sub>OUT</sub> (ch1, 20 V/div.), I<sub>OUT</sub> (ch2, 1 A/div.), and V<sub>COMP</sub> (ch3, 2 V/div.), t = 2 ms/div.

Figure 26. Extended view of the OVP condition in figure 25; shows  $V_{OUT}$  (ch1, 20 V/div.),  $I_{OUT}$  (ch2, 1 A/div.),  $V_{COMP}$  (ch3, 1 V/div.), and switch node ( $V_{SW}$ ) (ch4, 20 V/div.), t = 10 ms/div.

Figure 27. OVP condition created by an open LED string; shows V<sub>OUT</sub> (ch1, 2 V/div.), pin voltage V<sub>LEDx</sub> (ch2, 5 V/div.), and I<sub>OUT</sub> (ch3, 200 mA/div.), t = 2 ms/div.

Figure 28. Simplified schematic of an external disconnect switch implementation.

The waveforms in figure 29 show the operation of the disconnect feature.

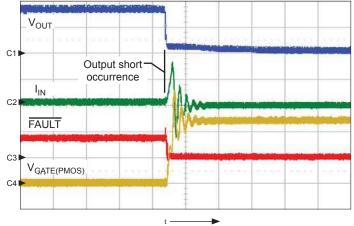

#### LED short detect

All LEDx pins are rated for 55 V, thus allowing LEDx pin-to-VOUT short protection in case of a connector short. Any LEDx pin that has a voltage exceeding  $V_{LEDSC}$  will be removed from operation. This is to prevent the IC dissipating too much power by having a large voltage present on the LEDx pins.

#### Input UVLO

When  $V_{IN}$  rises above the UVLO threshold  $(V_{UVLO(th)})$ , the A8508 is enabled. It is disabled when  $V_{IN}$  falls below  $V_{UVLO(th)} - V_{UVLO(hys)}$  for more than 2  $\mu$ s. This lag is to avoid shutdown because of momentary glitches in the power supply.

#### VDD and VDR

The VDD pin provides the regulated bias supply for the internal circuits. A capacitor with a value in the range 0.1 to 1  $\mu$ F should be used to decouple the internal analog and digital circuitry.

Figure 29. Input disconnect switch shutdown during an output short condition; shows V<sub>OUT</sub> (ch1, 20 V/div.), I<sub>IN</sub> (ch2, 10 A/div.), FAULT (ch3, 5 V/div.), and PMOS device V<sub>GATE</sub> (ch4, 5 V/div.), t = 50 µs/div.

Figure 30. Typical shorted LED: when voltage exceeds V<sub>LEDSC</sub>, the LED is disabled and remains disabled until either the EN pin is toggled or the power cycled; shows V<sub>OUT</sub> (ch1, 20 V/div.), V<sub>EN</sub> (ch2, 5 V/div.), I<sub>OUT</sub> (ch3, 0.5 A/div.), and V<sub>LEDx</sub> (ch4, 10 V/div.), t = 10  $\mu$ s/div.

## Wide Input Voltage Range, High Efficiency 8-Channel Fault Tolerant LED Driver

The VDR circuit provides power to the gate driver of the A8508. For best stability, use a decoupling capacitor in series with a resistor between the VDR pin and GND. The recommended value for the decoupling capacitor is  $0.22 \ \mu$ F. The value of the series resistor is typically between 5 and 10  $\Omega$ . If necessary, a larger resistor value may be used to limit the rising slope of the gate signal, in order to reduce EMI.

#### Shutdown

If the EN pin is pulled low, the IC will shut down immediately.

#### Fault protection during operation

The A8508 device constantly monitors the state of the system to determine if any fault conditions occur during normal operation. The response to a triggered fault condition is summarized in table 1. The possible fault conditions that the part can detect are:

- Open LED pin

- Shorted inductor with second level switch current protection

- VOUT short-to-ground

- ISET pin short-to-ground

- FSET pin short-to-ground

- Shorted LED

- Open Schottky diode

- Short Schottky diode protection with second level switch current protection

- Thermal shutdown (TSD)

- Overvoltage protection (OVP)

Figure 31. Input disconnect switch power-up: (1) V<sub>OUT</sub> charges via 10 k $\Omega$  resistor, (2) I<sub>IN</sub> current spike from charging COUT when the PMOS is enabled; shows V<sub>OUT</sub> (ch1, 20 V/div.), I<sub>IN</sub> (ch2, 2 A/div.), FAULT (ch3, 5 V/div.), and PMOS device V<sub>GATE</sub> (ch4, 5 V/div.), t = 2 ms/div.

#### Table 1. Fault Modes

| Fault Name                                                              | Туре         | Active              | Fault<br>Flag<br>Set | Description                                                                                                                                                                                                                                                                                                     | Boost                          | Sink<br>driver                                      |

|-------------------------------------------------------------------------|--------------|---------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------|

| Primary switch current<br>protection (pulse-by-<br>pulse current limit) | Auto-restart | Always              | No                   | This fault condition is triggered by the pulse-by-pulse current limit when the SENSP pin voltage exceeds $V_{\mbox{SENSEP}}.$                                                                                                                                                                                   | Off for<br>a single<br>cycle   | On                                                  |

| Secondary switch current limit                                          | Latched      | Always              | Yes                  | When the current through the boost switch exceeds the secondary current limit ( $V_{SENSESEC}$ ) the IC immediately shuts down the LED drivers and the boost. To re-enable the A8508 the EN pin must be toggled.                                                                                                | Off                            | Off                                                 |

| LEDx pin short to GND protection                                        | Auto-restart | Startup             | Yes                  | This fault prevents the IC from starting-up if any of the LEDx pins are shorted. The IC stops soft start from starting while any of the LEDx pins are determined to be shorted. After the short is removed, soft start is allowed to start.                                                                     | Off                            | Off                                                 |

| LEDx pin open                                                           | Auto-restart | Normal<br>operation | No                   | When an LEDx pin is open the device will determine which LEDx<br>pin is open by increasing the output voltage until OVP is reached.<br>Any LED string below regulation will be turned off. The device then<br>goes back to normal operation by reducing the output voltage to the<br>appropriate voltage level. | On                             | Off for<br>open<br>pins. On<br>for all<br>others    |

| LED short protection                                                    | Auto-restart | Always              | No                   | This fault occurs when the LED pin voltage exceeds $V_{LEDSC}$ . When the LED short protection is detected, the LED string that is above the threshold will be removed from operation.                                                                                                                          | On                             | Off for<br>shorted<br>pins. On<br>for all<br>others |

| FSET pin short<br>protection                                            | Auto-restart | Always              | No                   | This fault occurs when the FSET pin current goes above 150% of the maximum current. The boost stops switching, and the IC disables the LED sinks until the fault is removed. When the fault is removed the IC tries to restart with soft start.                                                                 |                                | On in<br>soft<br>start<br>current                   |

| ISET pin short<br>protection                                            | Auto-restart | Always              | No                   | This fault occurs when the ISET pin current goes above 150% of the maximum current. The boost stops switching and the IC disables the LED sinks until the fault is removed. When the fault is removed the IC tries to regulate to the preset LED current.                                                       | Off                            | Off                                                 |

| Overvoltage protection                                                  | Auto-restart | Always              | No                   | The fault occurs when the OVP pin voltage exceeds the $V_{\text{OVP}(th)}$ threshold. The A8508 immediately stops switching to try to reduce the output voltage. If the output voltage decreases then the A8508 restarts switching to regulate the output voltage.                                              | Stop<br>during<br>OVP<br>event | On                                                  |

| Output undervoltage protection                                          | Auto-restart | Always              | Yes                  | This fault occurs when the OVP pin senses less than 100 mV on the pin. The IC disables the external P-FET switch, if one is used.                                                                                                                                                                               | Off                            | Off                                                 |

| Overtemperature protection                                              | Auto-restart | Always              | Yes                  | The fault occurs when the die temperature exceeds the overtemperature threshold, typically 165°C.                                                                                                                                                                                                               | Off                            | Off                                                 |

| VIN UVLO                                                                | Auto-restart | Always              | No                   | This fault occurs when $V_{\text{IN}}$ drops below $V_{\text{UVLO}(\text{th})}(\text{max}),$ 8.5 V. This fault resets all latched faults.                                                                                                                                                                       | Off                            | Off                                                 |

### **Application Information**

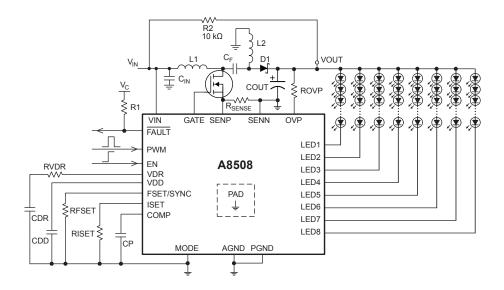

### Paralleling more than one A8508

The A8508 can be paralleled together by using a single boost converter (master) to provide output power for up to a total of four A8508s (slaves). The MODE pin of each device must be tied to the VDD pin of the same device for proper mode selection. In this mode, the FAULT pins and the COMP pins become a bidirection signal bus for the system to communicate.

At initial power-up, each IC will release a pull-down resistor on the COMP pin and start in soft start mode. When 200 mV is detected on the COMP pin, the master will then switch to normal mode. Also, for proper operation all of the FAULT pins must be tied together to prevent the parallel ICs from powering-up into a shorted LEDx pin situation. While the FAULT pins are pulled low, the system will not proceed with start-up.

Below is a simple list of necessary connections between the master and slave(s), to ensure proper parallel operation (refer to Application C in the Typical Applications section):

- COMP pin

- VOUT node

- FAULT pin

- EN pin

- PWM pin

Each one of these must be connected to the corresponding signal on the slave devices.

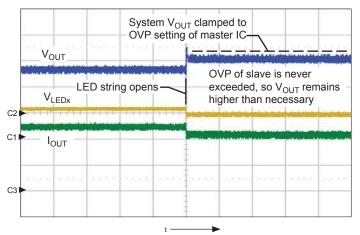

#### OVP setting for parallel operation

A notable exception to the list is the OVP pin. In this system each OVP pin must be set with a dedicated resistor. To make sure that the system will operate properly, the overvoltage protection on the master IC should be set higher than on the slave IC. The A8508 checks open LED condition upon hitting the OVP voltage. If the master OVP voltage is set lower than the slave OVP, the slave OVP pin will not trip to permit the open LED check. This in turn will not remove the corresponding LEDx pins from regulation. Therefore, the output voltage will stay at the master OVP limit and never decrease the output voltage to the lower regulation level.

The required slave OVP resistor value can be calculated using the following formula:

$$R_{\text{OVP(slave)}} = \frac{V_{\text{OUT(OVP)}} - 1.25 \text{ V}}{I_{\text{OVPH}}(\text{min})}$$

(7)

where  $V_{OUT(OVP)}$  is the required OVP voltage level, and  $I_{OVPH}(min)$  is the current into the OVP pin found in the Electrical Characteristics table. The minimum value should be used in this calculation.

The required master OVP voltage level can be calculated using the following formula:

$$V_{\text{OVP(master)}} = R_{\text{OVP(slave)}} \times I_{\text{OVPH}}(\text{max}) + 1.25$$

(8)

where  $V_{OVP(master)}$  is the minimum OVP voltage level of the master IC,  $I_{OVPH}(max)$  is current into the OVP pin found in the Electrical Characteristics table. The maximum value should be used in this calculation.

The required master OVP resistor value can be calculated using the following formula:

$$R_{\rm OVP(master)} = \frac{V_{\rm OVP(master)} - 1.25 \text{ V}}{I_{\rm OVPH}(\min)}$$

(9)

where  $V_{OVP(master)}$  is the minimum required master OVP voltage level, and  $I_{OVPH}(min)$  is the current into the OVP pin found in the Electrical Characteristics table. The minimum value should be used in this calculation.

Following the above formulas will guarantee that there is no overlap in OVP voltage levels in the system. All slave A8508s in the system can have the same OVP voltage setting. Figure 32 shows a proper master-slave OVP setting, and figure 33 shows the result of setting the master OVP too low.

## Wide Input Voltage Range, High Efficiency 8-Channel Fault Tolerant LED Driver

Figure 32. Proper OVP setting for the master and slave configuration. The master OVP is set higher than the slave, shows  $V_{OUT}$  (ch1, 2 V/div.), pin voltage  $V_{LEDx}$  (ch2, 2 V/div.), and  $I_{OUT}$  (ch3, 200 mA/div.), t = 2 ms/div.

Figure 33. OVP on the master IC is set too low and the IC does not respond properly to the open LED condition on the slave IC; shows V<sub>OUT</sub> (ch1, 10 V/div.), V<sub>LEDx</sub> (ch2, 2 V/div.), and I<sub>OUT</sub> (ch3, 200 mA/div.), t = 100 ms/div.

### **Design Example**

This section provides a method for selecting component values when designing an application using the A8508.

Assumptions: For the purposes of this example, the following are given as the application requirements:

- V<sub>IN</sub>: 10 to 16 V

- Quantity of LED channels, #CHANNELS: 8

- Quantity of series LEDs per channel, #SERIESLEDS : 10

- LED current per channel, I<sub>LED</sub>: 120 mA

- $V_{f(120)}$  at 120 mA: 3.2 V (max)

- f<sub>SW</sub>: 600 kHz

- T<sub>A</sub>(max): 65°C

- PWM dimming frequency: 200 Hz, 1% duty cycle

Step 1: Connect LEDs to pins LED1 through LED8.

Step 2: Determine the LED current by setting resistor  $R_{ISET}$ . To do so, apply equation 2:

$$R_{\text{ISET}} = (1.000 / I_{\text{LED}}) \times 1160$$

= (1.000 V / 0.120 A) × 1160

= 9.67 kΩ

Choose a 9.53 k $\Omega$  resistor.

STEP 3: Determine the OVP resistor. The OVP resistor is connected between the OVP pin and the output voltage of the converter. The first step is to determine the maximum voltage based on the LED requirements. Then the regulation voltage of 600 mV should be added, along with 2 V for noise and regulation. Given the regulation voltage ( $V_{LED}$ ) of the A8508 is 850 mV, the minimum required voltage can be determined as follows:

$$V_{\text{OUT(OVP)}} = \#\text{SERIESLEDS} \times V_{\text{f(120)}} + V_{\text{LED}} + 2 \text{ V}$$

(10)

= 10 × 3.2 V + 0.650 V + 2 V

$V_{\text{OUT(OVP)(min)}} = 34.65 \text{ V}$

The OVP resistor (ROVP) value can be calculated as:

$$R_{\text{OVP}} = \frac{V_{\text{OUT}(\text{OVP})(\min)} - V_{\text{OVP}(\text{th})}(\min)}{I_{\text{OVPH}}(\min)}$$

(11)

=  $\frac{34.65 \text{ V} - 1.11 \text{ V}}{45 \mu \text{A}}$

= 745 k\Omega; use the nearest standard value, 750 kΩ

where both I<sub>OVP(th)</sub>(min) and V<sub>OVP(th)</sub>(min) are found in the

Electrical Characteristics table. Choose a value of resistor that is the closest value higher than the calculated  $R_{OVP}$ . In this design example, a value of 750 k $\Omega$  is selected.

Below is the actual value of the minimum OVP trip level with the selected resistor, applying equation 8:

$$V_{\text{OVP}} = R_{\text{OVP}} \times I_{\text{OVPH}} + 1.25 \text{ V}$$

= 750 k $\Omega \times 49 \mu\text{A} + 1.25 \text{ V}$

= 38.75 V

STEP 4: Determine the inductor. The inductor must be chosen such that it can handle the necessary input current. In most applications, due to stringent EMI requirements, the inductor must operate in continuous conduction mode throughout the whole input voltage range.

STEP 4a: Determine the maximum duty cycle of the system:

$$D(\max) = 1 - \frac{V_{\rm IN}(\min) \times \eta}{V_{\rm OUT(OVP)} + V_{\rm f(boost)}}$$

(12)

=  $1 - \frac{10 \text{ V} \times 0.9}{34.65 \text{ V} + 0.4 \text{ V}}$

= 74.5%

A good approximation of efficiency ( $\eta$ ) is 90%. The voltage drop of the boost diode can be approximated to be about 0.4 V.

STEP 4b: Determine the maximum and minimum input current to the system. The minimum input current dictates the inductor value. The maximum current rating dictates the current rating of the inductor.

To calculate the maximum input current, first determine the required output current:

$$I_{OUT} = #CHANNELS \times I_{LED}$$

(13)

= 8 × 120 mA

= 0.960 A

Then substitute into the formula for maximum input current:

$$I_{\rm IN}(\rm max) = \frac{V_{\rm OUT} \times I_{\rm OUT}}{V_{\rm IN}(\rm min) \times \eta}$$

(14)

=  $\frac{34.65 \text{ V} \times 0.960 \text{ A}}{10 \text{ V} \times 0.90}$

= 3.7 A

### Wide Input Voltage Range, High Efficiency 8-Channel Fault Tolerant LED Driver

The minimum input current can be calculated as:

$$I_{\rm IN}(\rm min) = \frac{V_{\rm OUT} \times I_{\rm OUT}}{V_{\rm IN}(\rm max) \times \eta}$$

(15)

=  $\frac{34.65 \, \rm V \times 0.960 \, \rm A}{16 \, \rm V \times 0.90}$

= 2.31 A

STEP 4c: Determining the inductor value. To assure that the inductor operates in continuous conduction mode, the value of inductor must be set such that 1/2 of the inductor ripple current is not greater than the average minimum input current.

As a first pass, take  $I_{ripple}$  to be 30% of the maximum inductor current:

$$\Delta I_{\rm L} = I_{\rm IN}({\rm max}) \times (I_{\rm ripple} / I_{\rm IN}({\rm max}))$$

(16)

= 3.72 A × 0.30

= 1.1 A

Check to make sure that 1/2 of the inductor ripple current is less than  $I_{IN}(min)$ :

$$I_{\rm IN}(\rm min) > \frac{1}{2} \times \Delta I_{\rm L}$$

2.31 A > 0.56 A

The inductor value can be calculated as:

$$L = \frac{V_{\rm IN}(\rm min)}{\Delta I_{\rm L} \times f_{\rm SW}} \times D(\rm max)$$

$$= \frac{10 \,\rm V}{1.1 \,\rm A \times 600 \,\rm kHz} \times 0.745$$

$$= 10.62 \,\rm \mu H$$

(17)

A good inductor value to use would be  $L_{used} = 10 \mu H$ . STEP 4d: Determining the inductor current rating. The inductor current rating must be greater than the  $I_{IN}(max)$  value plus the ripple current  $\Delta I_L$ , calculated as:

$$I_{L}(\min) = I_{IN}(\max) + \frac{1}{2} \times \Delta I_{Lused}$$

(18)

= 3.72 A + 0.56 A

= 4.28 A

STEP 4e: Choosing the RSENSE resistor. The sense resistor value can be calculated as follows:

$$R_{\text{SENSE}} = \frac{V_{\text{SENSEP}}}{I_{\text{L}}(\text{min})}$$

$$= \frac{0.086 \text{ V}}{4.28 \text{ A}}$$

$$= 0.02 \Omega$$

(19)

$0.018\;\Omega$  is a good value to use for the resistor.

STEP 4f: This step is used to verify that there is sufficient slope compensation for the inductor chosen. The internal slope compensation value is determined by the following formula:

Slope Compensation =

$$2.81 \times 10^{-7} \times f_{SW}$$

(20) where  $f_{SW}$  is in Hz. Substituting:

=  $0.168 \text{ V/}\mu\text{s}$ With  $R_{\text{SENSE}} = 0.02 \Omega$  this translates to:

$$0.168/0.02 = 8.4$$

A/µs

Next invert equation 17 and insert the inductor value used in the design:

$$\Delta I_{\text{Lused}} = \frac{V_{\text{IN}}(\text{min})}{L_{\text{used}} \times f_{\text{SW}}} \times D(\text{max})$$

(21)

10 17

where  $f_{SW}\, is$  in MHz. Substituting:

$$= \frac{10 \text{ V}}{10 \text{ }\mu\text{H} \times 600 \text{ }\text{kHz}} \times 0.745$$

$$= 1.24 \text{ A}$$

$$\Delta I_{\text{Lused}} \times 1 \times 10^{-6}$$

$$= \frac{1.24 \text{ A} \times (1 - D(\text{max}))}{1 \text{ }f_{\text{SW}}} \times (1 - D(\text{max}))$$

$$= \frac{1.24 \text{ }\text{A} \times 1 \times 10^{-6}}{1 \text{ }600 \text{ }\text{\text{kHz}}} \times (1 - 0.745)$$

$$= 2.91 \text{ }\text{A}/\mu\text{s}$$

(22)

Note: that the  $1 \times 10^{-6}$  is a constant multiplier. This slope should be smaller than the internal slope compensation.

STEP 5: To determine the resistor values for a switching frequency use figure 9.

STEP 6: Choosing the proper switching diode. The switching diode must be chosen for three characteristics when it is used in LED lighting circuitry: reverse voltage rating, current rating, and reverse current characteristic of the diode.

The reverse voltage rating should be such that, during any operation condition, the voltage rating of the device is larger than the maximum output voltage. In this case, the maximum output voltage is  $V_{\rm OUT(OVP)}.$

The peak current through the diode is:

$$I_{d(peak)} = I_{IN}(max) + \Delta I_{Lused}$$

(23)

= 3.72 A + 0.56 A

= 4.28 A

The other major component in determining the switching diode is the reverse current characteristic of the diode. This characteristic is especially important when PWM dimming is implemented. During PWM off-time the boost converter is not switching. This results in a slow bleeding-off of the output voltage due to leakage currents ( $I_R$ ).  $I_R$ , or reverse current, can be a huge contributor especially at high temperatures. On the diode that was selected in this design, the current varies between 1 and 100  $\mu$ A.

STEP 7: Choosing the output capacitors. The output capacitors must be chosen such that they can provide filtering for both the boost converter and for the PWM dimming function. The biggest factor that contributes to the size of the output capacitor is PWM dimming frequency and the PWM duty cycle. Another major contributor is leakage current ( $I_{LK}$ ). This current is the combination of the OVP current sense as well as the reverse current of the switching diode.

In this design the PWM dimming frequency is 200 Hz and the minimum duty cycle is 1%. Typically the voltage variation on the output during PWM dimming must be less than 250 mV ( $V_{COUT}$ ) so that no audible hum can be heard:

$$C_{\text{OUT}} = I_{\text{LK}} \times \frac{1 - D_{\text{PWM}(\text{min})}}{f_{\text{PWM}} \times V_{\text{COUT}}}$$

$$= 300 \,\mu\text{A} \times \frac{1 - 0.01}{200 \,\text{Hz} \times 0.250 \,\text{V}}$$

$$= 5.94 \,\mu\text{F}$$

(24)

A capacitor larger than 5.94  $\mu$ F should be selected due to degradation of capacitance at high voltages on the capacitor. Two ceramic 4.7  $\mu$ F 50 V capacitors are a good choice to fulfill this requirement.

The rms current through the capacitor is given by:

$$I_{\text{COUTrms}} = I_{\text{OUT}} \sqrt{\frac{D(\max) + \frac{\Delta I_{\text{Lused}}}{I_{\text{IN}}(\max) \times 12}}{1 - D(\max)}}$$

$$= 0.960 \text{ A} \sqrt{\frac{0.745 + \frac{1.24 \text{ A}}{3.72 \text{ A} \times 12}}{1 - 0.745}}$$

$$= 1.67 \text{ A}$$

(25)

The output capacitor must have a current rating of at least 1.67 A. The output capacitors selected in this design have a combined rms current rating of 2 A.

STEP 8: Selection of input capacitor. The input capacitor must be selected such that it provides a good filtering of the input voltage waveform. A good rule of thumb is to set the input voltage ripple  $(\Delta V_{IN})$  to be 1% of the minimum input voltage. The minimum input capacitor requirements are as follows:

$$C_{\rm IN} = \frac{\Delta I_{\rm Lused}}{8 \times f_{\rm SW} \times \Delta V_{\rm IN}}$$

(26)

$$= \frac{1.24 \text{ A}}{8 \times 600 \text{ kHz} \times 0.1 \text{ V}}$$

$$= 2.65 \,\mu\text{F}$$

The rms current through the capacitor is given by:

$$I_{\rm INrms} = \frac{I_{\rm OUT} \times \frac{\Delta I_{\rm Lused}}{I_{\rm IN}(\rm max)}}{(1 - D(\rm max))\sqrt{12}}$$

$$= \frac{0.960 \text{ A} \times \frac{1.24 \text{ A}}{3.72 \text{ A}}}{(1 - 0.765)\sqrt{12}}$$

$$= 0.363 \text{ A}$$

(27)

A good ceramic input capacitor with ratings of 50 V, 4.7  $\mu F$  will suffice for this application.

Corresponding capacitors include:

| Vendor | Value       | Part number        |

|--------|-------------|--------------------|

| Murata | 4.7 µF 50 V | GRM32ER71H475KA88L |

| Murata | 2.2 µF 50 V | GRM31CR71H225KA88L |

### **Typical Applications**

The following is the component list for the typical application circuit shown in figure 1.

| Designator         | Description         | Part Number        | Manufacturer      |

|--------------------|---------------------|--------------------|-------------------|

| CDD                | 0.1 µF / 10 V       | GRM2195C1H104JA01D | Murata            |

| CDR                | 0.22 µF / 10 V      | GRM188R61A224KA01D | Murata            |

| C <sub>IN</sub>    | 4.7 µF / 50 V       | GRM32ER71H475KA88L | Murata            |

| COUT               | 10 µF / 50 V        | GRM32ER71H475KA88L | Murata            |

| CP                 | 1 µF / 16V          | GRM188R61A474K     | Murata            |

| CZ                 | DNP                 |                    |                   |

| D1                 | 60 V / 5 A Schottky | CMSH5-60-AMI       | Central Semi      |

| L1                 | 10 µH / 5 A         | 74477110           | Wurth Electronics |

| Q1                 | NMOS                | FQD13N06LTM        | Faichild          |

| R1                 | 100 kΩ              |                    | DigiKey           |

| RFSET              | 8.45 kΩ 1%          |                    |                   |

| RISET              | 12.4 kΩ 1%          |                    |                   |

| ROVP               | 732 kΩ 1%           |                    |                   |

| R <sub>SENSE</sub> | 0.015 Ω             |                    |                   |

| RZ                 | DNP                 |                    |                   |

| U1                 | A8508               | A8508              | Allegro           |

Application A. Typical schematic for boost application with disconnect switch application

Application B. Typical application showing SEPIC configuration

### Wide Input Voltage Range, High Efficiency 8-Channel Fault Tolerant LED Driver

Application C. Parallel operation of two A8508s; overvoltage protection on master must be set higher than the OVP on the slave

Application D. Input disconnect switch configuration for fault protection. Option available only in QFN package. Contact factory for details.

## Wide Input Voltage Range, High Efficiency 8-Channel Fault Tolerant LED Driver

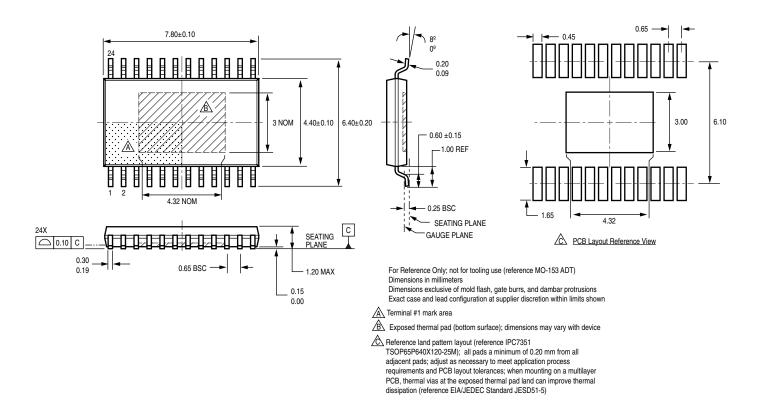

### Package Outline Drawing

Package LP, 24-Pin TSSOP with Exposed Thermal Pad

Contact factory for ET and LW packages.

#### **Revision History**

| Revision | Current<br>Revision Date | Description of Revision                  |  |

|----------|--------------------------|------------------------------------------|--|

| Rev. 1   | July 9, 2012             | Update typical component recommendations |  |

|          |                          |                                          |  |

Copyright ©2011-2012, Allegro MicroSystems, Inc.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.