# 10.7Gb/s Modulator Driver Amplifier

### **Key Features and Performance**

- Single-ended Input / Output

- Small Signal Gain 19dB

- Small Signal Bandwidth 10GHz

- Wide Drive Range (3V to 11V)

- 25ps Edge Rates (20/80)

- Power Dissipation 2.25Watts

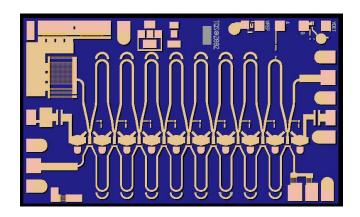

- Die Size: 3.3 x 2 x 0.1 mm

### **Description**

The TriQuint TGA4807 is part of a series of optical driver amplifiers suitable for a variety of driver applications.

The TGA4807 is a medium power wideband AGC amplifier MMIC die that typically provides 19dB small signal gain with 19dB AGC range. RF ports are DC coupled enabling the user to customize system corner frequencies.

The TGA4807 is an excellent choice for applications requiring high drive levels. The TGA4807 has demonstrated capability to amplify a 2V input signal to 11Vpp saturated.

The TGA4807 requires off-chip decoupling, a DC block and a bias tee. The TGA4807 is available in die form.

Lead-free and RoHS compliant

### **Primary Applications**

Mach-Zehnder Modulator Driver for Metro and Long Haul.

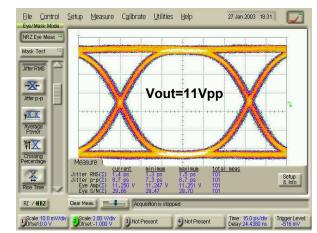

### **Measured Performance**

TGA4807 Fixtured Data Vd(Rfout)=7V, Id=250mA, (Pdc=1.75W) Vout=11Vpp, Vin = 2Vpp Scale: 2V/div, 15ps/div

10.7Gb/s Vin=2V

### **MAXIMUM RATINGS**

| SYMBOL           | PARAMETER <u>6</u> /             | VALUE         | NOTES         |

|------------------|----------------------------------|---------------|---------------|

|                  | POSITIVE SUPPLY VOLTAGE          |               |               |

| Vd               | Drain Voltage at RF output       | 7 V           |               |

|                  | POSITIVE SUPPLY CURRENT          |               |               |

| ld               | Drain Current                    | 285 mA        | <u>1</u> /    |

| P <sub>d</sub>   | POWER DISSIPATION                | 2.2 W         | <u>2</u> /    |

|                  | NEGATIVE GATE                    |               |               |

| Vg               | Voltage                          | 0 V to –3 V   |               |

| lg               | Gate Current                     | 5 mA          |               |

|                  | CONTROL GATE                     |               |               |

| Vctrl            | Voltage                          | Vd/2 to −3 V  | <u>3</u> /    |

| Ictrl            | Gate Current                     | 5 mA          |               |

|                  | RF INPUT                         |               |               |

| $P_{IN}$         | Sinusoidal Continuous Wave Power | 23 dBm        |               |

| T <sub>CH</sub>  | OPERATING CHANNEL TEMPERATURE    | 200 °C        | <u>4</u> / 5/ |

|                  | MOUNTING TEMPERATURE             | 320 °C        |               |

|                  | (30 SECONDS)                     |               |               |

| T <sub>STG</sub> | STORAGE TEMPERATURE              | -65 to 150 °C |               |

### Notes:

- 1/ Assure the combination of Vd and Id does not exceed maximum power dissipation rating.

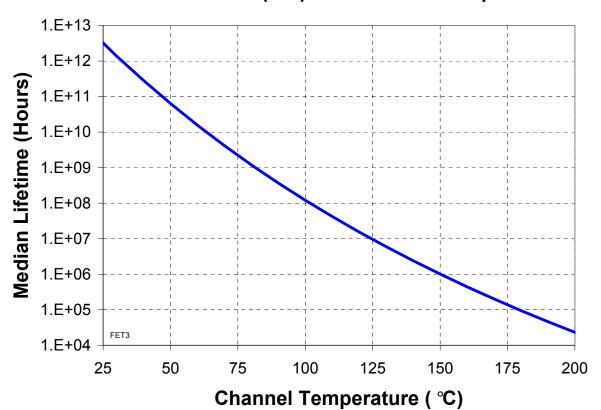

- 2/ When operated at this bias condition with a base plate temperature of 70 °C, the median life is 3.4E6 hours.

- 3/ Assure Vctrl never exceeds Vd during bias on and off sequences, and normal operation.

- 4/ These ratings apply to each individual FET.

- 5/ Junction operating temperature will directly affect the device median time to failure (Tm). For maximum life, it is recommended that junction temperatures be maintained at the lowest possible levels.

- 6/ These ratings represent the maximum operable values for the device.

#### THERMAL INFORMATION

| Parameter                                                           | Test Condition           | P <sub>diss</sub> (W) | T <sub>Base</sub> (°C) | T <sub>CH</sub><br>(°C) | θ <sub>JC</sub> | Tm<br>(HRS) |

|---------------------------------------------------------------------|--------------------------|-----------------------|------------------------|-------------------------|-----------------|-------------|

| θ <sub>JC</sub> Thermal Resistance (channel to backside of carrier) | VD(RFout)=7V<br>Id=250mA | 1.75                  | 70                     | 122                     | 30              | 1.2E7       |

### Notes:

- 1. Assumes worst case power dissipation condition where no RF is applied at the input (no power is dissipated in the load).

- 2. Thermal transfer is conducted thru the bottom of the TGA4807 into the mounting carrier. Design the mounting interface to assure adequate thermal transfer to the base plate.

### Median Lifetime (Tm) vs. Channel Temperature

#### DC PROBE TEST

(TA = 25 °C, nominal)

| NOTES          | SYMBOL              | LIMITS |     | UNITS |

|----------------|---------------------|--------|-----|-------|

|                |                     | MIN    | MAX |       |

| <u>1</u> /, 2/ | V <sub>BVGS</sub>   | 13     |     | V     |

| <u>1</u> /, 2/ | $ V_{\text{BVGD}} $ | 13     |     | V     |

### Notes:

1/ Verified at die level on-wafer probe.

$\underline{\underline{2}}$ /  $V_{BVGS}$  and  $V_{BVDS}$  are negative.

### **Definitions:**

$V_{BVGS}$ : Breakdown voltage, Gate to Source  $V_{BVGD}$ : Breakdown voltage, Gate to Drain

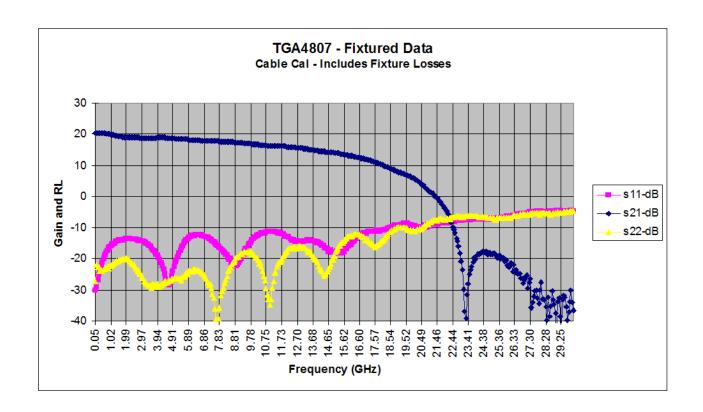

# RF SPECIFICATIONS $(T_A = 25^{\circ}C \text{ Nominal})$

| NOTE                   | TEST                            | MEASUREMENT<br>CONDITIONS |      | VALUE |     | UNITS |

|------------------------|---------------------------------|---------------------------|------|-------|-----|-------|

|                        |                                 |                           | MIN  | TYP   | MAX |       |

|                        | SMALL SIGNAL BW                 |                           |      | 10    |     | GHz   |

| <u>1</u> /, <u>2</u> / | SMALL-SIGNAL                    | 2 GHz                     | 18   |       |     |       |

|                        | GAIN MAGNITUDE                  | 4 GHz                     | 17   |       |     |       |

|                        |                                 | 6 GHz                     | 16   |       |     | dB    |

|                        |                                 | 10 GHz                    | 15   |       |     |       |

|                        |                                 | 14 GHz                    | 12   |       |     |       |

|                        |                                 |                           |      |       |     |       |

| <u>1</u> /, <u>2</u> / | SMALL SIGNAL AGC RANGE          | 2, 4, 6, 10, and<br>14GHz |      | 20    |     | dB    |

| <u>1</u> /, <u>2</u> / | INPUT RETURN LOSS<br>MAGNITUDE  | 2, 4, 6, 10, and<br>14GHz |      | 10    |     | dB    |

| <u>1</u> /, <u>2</u> / | OUTPUT RETURN LOSS<br>MAGNITUDE | 2, 4, 6, 10, and<br>14GHz |      | 12    |     | dB    |

| <u>3</u> /, <u>4</u> / | SATURATED OUTPUT<br>POWER       | 2, 4, 6, 10, and<br>14GHz | 25   |       |     | dBm   |

| <u>3</u> /, <u>4</u> / | EYE AMPLITUDE                   | Vd(Rfout) = 7V            | 11.0 |       |     | Vpp   |

|                        |                                 | Vd(Rfout) = 6V            | 10.0 |       |     |       |

|                        |                                 | Vd(Rfout) = 5V            | 9.0  |       |     |       |

|                        |                                 | Vd(Rfout) = 4V            | 8.0  |       |     |       |

| <u>3</u> /, <u>5</u> / | ADDITIVE JITTER                 |                           |      | 5     |     | ps    |

| <u>3</u> /             | RISE TIME                       |                           |      | 25    |     | ps    |

#### Notes:

- 1/ Verified at package level RF probe.

- 2/ Bias: V<sup>+</sup> = 7 V, adjust Vg1 to achieve Id = 250 mA, Vctrl = +1 V

- 3/ Verified by design, TGA4807 assembled onto a demonstration board shown on page 9 then tested using the application circuit and bias procedure detailed on pages 7 and 8.

- 4/ Vin = 2 V, Data Rate = 12.5 Gb/s, Vctrl and Vg are adjusted for maximum output.

- 5/ Computed using RSS Method where Jpp additive = SQRT(Jpp out<sup>2</sup> Jpp in<sup>2</sup>)

# **Typical Small Signal S-Parameters**

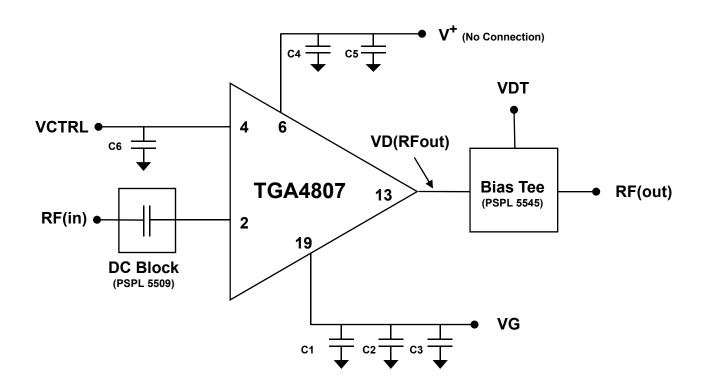

# **TGA4807 Application Circuit**

### Notes:

Recommended Components are detailed on page 9.

## **Bias Procedure for 11V Output**

### Bias ON

- 1. Disable the RF source (PPG)

- 2. Set VdT=0V Vctrl=0V and Vq=0V

- 3. Set Vg=-1.5V

- 4. Increase VdT to 8V observing Id.

- Assure Id=0mA

- 5. Set Vctrl=+1.2V

- Id should still be 0mA

- 6. Make Vg more positive until Idd=250mA.

- Typical value for Vg is -0.2V

- 7. Measure  $V^+$ , adjust VdT such that  $V^+$  is 7V.

- This will set Vd(RFout) to approximately 7V.

- Idd will increase slightly

- 8. Adjust Vg such that Idd=250mA.

- 9. Enable the RF source (PPG)

- Set Vin=2V

- 10. <u>Output Swing Adjust:</u> Adjust <u>Vctrl</u> slightly positive to increase output swing or adjust Vctrl slightly negative to decrease the output swing.

- Typical value for Vctrl is +1.2V for Vo=11V.

- 11. <u>Crossover Adjust: Adjust:</u> Vg slightly positive to push the crossover down or adjust Vg slightly negative to push the crossover up.

- Typical value for Vg is -0.57V to center crossover with Vo=11V.

### Notes:

Assure Vctrl never exceeds Vd during Bias ON and Bias OFF sequences and during normal operation.

### **Bias OFF**

- 1. Disable the output of the PPG

- 2. Set Vctrl=0V

- 3. Set VdT=0V

- 4. Set Vg=0V

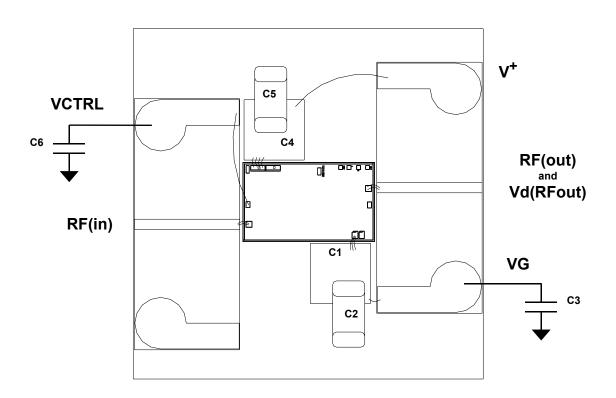

# **Recommended Assembly Diagram**

### **Recommended Components:**

| DESIGNATOR | DESCRIPTION                 | MANUFACTURER | PART NUMBER     |

|------------|-----------------------------|--------------|-----------------|

| C1, C4     | 1500pF Capacitor SLC        | Presidio     | SL5050X7R1522H5 |

| C2, C5     | 0.1uF Capacitor MLC Ceramic | AVX          | 0603YC104KAT    |

| C3         | 10uF Capacitor MLC Ceramic  | AVX          | 0603YC102KAT    |

| C6         | 0.01 uF Capacitor MLC       | AVX          | 0603YC103KAT    |

GaAs MMIC devices are susceptible to damage from Electrostatic Discharge. Proper precautions should be observed during handling, assembly and test.

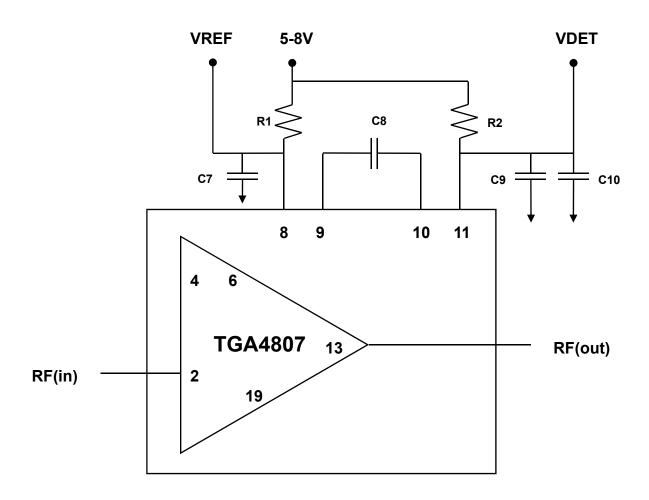

# **TGA4807 Detector Application Circuit**

### **Recommended Components:**

| DESIGNATOR | DESCRIPTION                   | MANUFACTURER | PART NUMBER       |

|------------|-------------------------------|--------------|-------------------|

| R1, R2     | 40K ohm Resistor Chip Silicon | MSI          | MSBC 2ST-40001F-E |

| C7, C8, C9 | 100pF Capacitor SLC Ceramic   | AVX          | GB015810KA6       |

| C10        | .01uF Capacitor MLC Ceramic   | AVX          | VL303X7R103M16VG5 |

## **Assembly Process Notes**

### **Assembly Notes:**

#### Reflow Attachment:

Use AuSn (80/20) solder with limited exposure to temperatures at or above 300□C Use alloy station or conveyor furnace with reducing atmosphere No fluxes should be utilized Coefficient of thermal expansion matching is critical for long-term reliability Storage in dry nitrogen atmosphere

#### Adhesive Attachment:

Organic attachment can be used in low-power applications

Curing should be done in a convection oven; proper exhaust is a safety concern

Microwave or radiant curing should not be used because of differential heating

Coefficient of thermal expansion matching is critical

### Component Pickup and Placement:

Vacuum pencil and/or vacuum collet preferred method of pick up Avoidance of air bridges during placement Force impact critical during auto placement

#### Interconnect:

Thermosonic ball bonding is the preferred interconnect technique Force, time, and ultrasonics are critical parameters Aluminum wire should not be used Discrete FET devices with small pad sizes should be bonded with 0.0007-inch wire Maximum stage temperature: 200 C

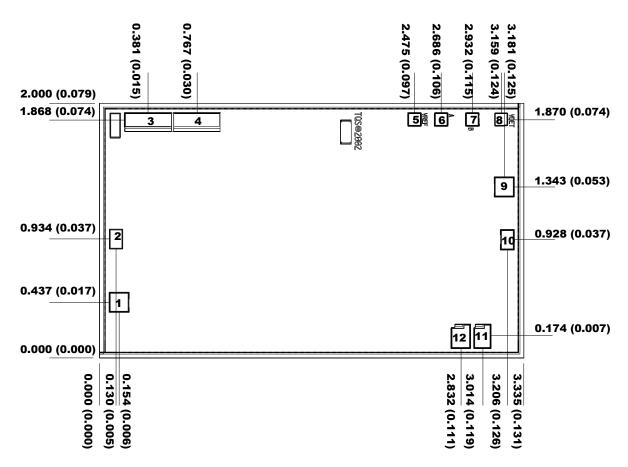

# **TGA4807 Mechanical Drawing**

**Units: millimeters (inches)** Thickness: 0.100 (0.004)

Chip edge to bond pad dimensions are shown to center of bond pad

Chip size tolerance: +/- 0.051 (0.002)

### **RF GND IS BACKSIDE OF MMIC**

| Bond pad #1  | (RF In)     | 0.155 x 0.155 (0.006 x 0.006) |

|--------------|-------------|-------------------------------|

| Bond pad #2  | (Vctrl)     | 0.106 x 0.157 (0.004 x 0.006) |

| Bond pad #3  | (V+) ´      | 0.368 x 0.109 (0.014 x 0.004) |

| Bond pad #4  | (V+ aux)    | 0.368 x 0.109 (0.014 x 0.004) |

| Bond pad #5  | (Vref)      | 0.095 x 0.095 (0.004 x 0.004) |

| Bond pad #6  | (A)         | 0.095 x 0.095 (0.004 x 0.004) |

| Bond pad #7  | (B)         | 0.095 x 0.095 (0.004 x 0.004) |

| Bond pad #8  | (V det)     | 0.095 x 0.095 (0.004 x 0.004) |

| Bond pad #9  | (RF Out)    | 0.155 x 0.155 (0.006 x 0.006) |

| Bond pad #10 | (Vctrl aux) | 0.106 x 0.157 (0.004 x 0.006) |

| Bond pad #11 | (Vg aux)    | 0.155 x 0.155 (0.006 x 0.006) |

| Bond pad #12 | (Va)        | 0.155 x 0.155 (0.006 x 0.006) |