**Freescale Semiconductor**

# **HC11**

## MC68HC11F1

## **Technical Data**

© Freescale Semiconductor, Inc., 2004. All rights reserved.

Home Page: www.freescale.com email: support@freescale.com USA/Europe or Locations Not Listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH **Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com Japan: Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com Asia/Pacific: Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

## **TABLE OF CONTENTS**

Paragraph

Title

Page

#### **SECTION 1INTRODUCTION**

#### **SECTION 2 PIN DESCRIPTIONS**

| 2.1    | $V_{DD}$ and $V_{SS}$                                 | 2-2 |

|--------|-------------------------------------------------------|-----|

| 2.2    | Reset (RESET)                                         |     |

| 2.3    | E-Clock Output (E)                                    |     |

| 2.4    | Crystal Driver and External Clock Input (XTAL, EXTAL) | 2-3 |

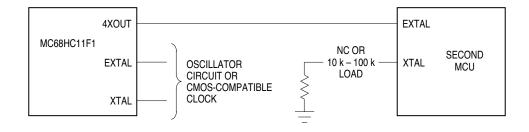

| 2.5    | Four Times E-Clock Frequency Output (4XOUT)           | 2-5 |

| 2.6    | Interrupt Request (IRQ)                               | 2-5 |

| 2.7    | Non-Maskable Interrupt (XIRQ)                         | 2-5 |

| 2.8    | MODA and MODB (MODA/LIR and MODB/V <sub>STBY</sub> )  | 2-6 |

| 2.9    | V <sub>RH</sub> and V <sub>RL</sub>                   | 2-6 |

| 2.10   | R/W                                                   | 2-6 |

| 2.11   | Port Signals                                          | 2-6 |

| 2.11.1 | Port A                                                |     |

| 2.11.2 | Port B                                                | 2-8 |

| 2.11.3 | Port C                                                | 2-8 |

| 2.11.4 | Port D                                                | 2-8 |

| 2.11.5 | Port E                                                | 2-9 |

| 2.11.6 | Port F                                                | 2-9 |

| 2.11.7 | Port G                                                | 2-9 |

|        |                                                       |     |

#### **SECTION 3 CENTRAL PROCESSING UNIT**

| 3.1     | CPU Registers                 |  |

|---------|-------------------------------|--|

| 3.1.1   | Accumulators A, B, and D      |  |

| 3.1.2   | Index Register X (IX)         |  |

| 3.1.3   | Index Register Y (IY)         |  |

| 3.1.4   | Stack Pointer (SP)            |  |

| 3.1.5   | Program Counter (PC)          |  |

| 3.1.6   | Condition Code Register (CCR) |  |

| 3.1.6.1 | Carry/Borrow (C)              |  |

| 3.1.6.2 | Overflow (V)                  |  |

| 3.1.6.3 | Zero (Z)                      |  |

| 3.1.6.4 | Negative (N)                  |  |

| 3.1.6.5 | Interrupt Mask (I)            |  |

| 3.1.6.6 | Half Carry (H)                |  |

| 3.1.6.7 | X Interrupt Mask (X)          |  |

| 3.1.6.8 | Stop Disable (S)              |  |

#### TABLE OF CONTENTS (Continued) Title

#### Paragraph

Page

| 3.2   | Data Types           |  |

|-------|----------------------|--|

| 3.3   | Opcodes and Operands |  |

| 3.4   | Addressing Modes     |  |

| 3.4.1 | Immediate            |  |

| 3.4.2 | Direct               |  |

| 3.4.3 | Extended             |  |

| 3.4.4 | Indexed              |  |

| 3.4.5 | Inherent             |  |

| 3.4.6 | Relative             |  |

| 3.5   | Instruction Set      |  |

|       |                      |  |

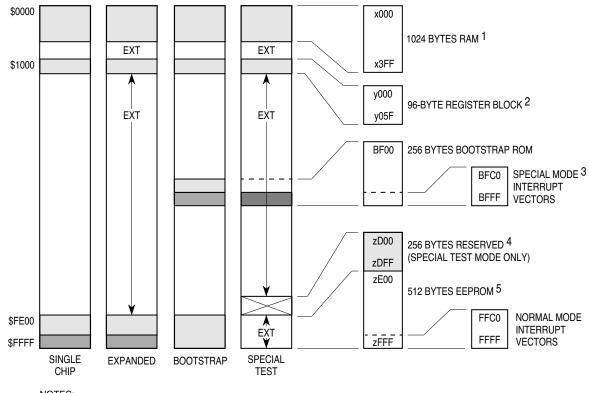

#### SECTION 40PERATING MODES AND ON-CHIP MEMORY

| 4.1     | Operating Modes                           | 4-1  |

|---------|-------------------------------------------|------|

| 4.1.1   | Single-Chip Operating Mode                | 4-1  |

| 4.1.2   | Expanded Operating Mode                   |      |

| 4.1.3   | Special Test Mode                         |      |

| 4.1.4   | Special Bootstrap Mode                    |      |

| 4.2     | On-Chip Memory                            |      |

| 4.2.1   | Mapping Allocations                       | 4-2  |

| 4.2.2   | Memory Map                                |      |

| 4.2.2.1 | RAM                                       |      |

| 4.2.2.2 | Bootloader ROM                            | 4-4  |

| 4.2.2.3 | EEPROM                                    |      |

| 4.2.3   | Registers                                 |      |

| 4.3     | System Initialization                     |      |

| 4.3.1   | Mode Selection                            | 4-7  |

| 4.3.1.1 | HPRIO Register                            |      |

| 4.3.2   | Initialization                            |      |

| 4.3.2.1 | CONFIG Register                           | 4-9  |

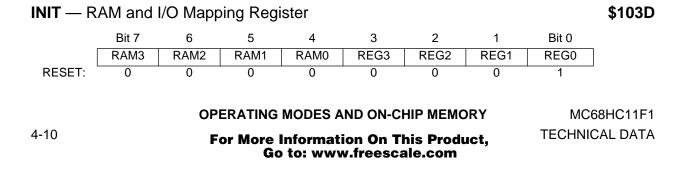

| 4.3.2.2 | INIT Register                             |      |

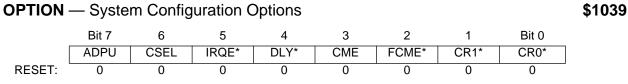

| 4.3.2.3 | OPTION Register                           |      |

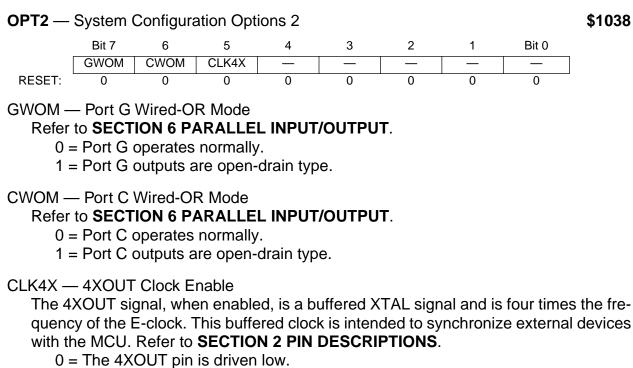

| 4.3.2.4 | OPT2 Register                             |      |

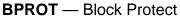

| 4.3.2.5 | Block Protect Register (BPROT)            |      |

| 4.4     | EEPROM and CONFIG Register                |      |

| 4.4.1   | EEPROM                                    |      |

| 4.4.1.1 | EEPROM Programming                        |      |

| 4.4.1.2 | EEPROM Bulk Erase                         | 4-15 |

| 4.4.1.3 | EEPROM Row Erase                          | 4-15 |

| 4.4.1.4 | EEPROM Byte Erase                         | 4-16 |

| 4.4.2   | PPROG EEPROM Programming Control Register | 4-16 |

| 4.4.3   | CONFIG Register Programming               | 4-17 |

TECHNICAL DATA

#### TABLE OF CONTENTS (Continued) Title

#### Paragraph

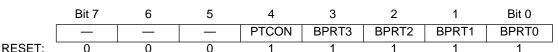

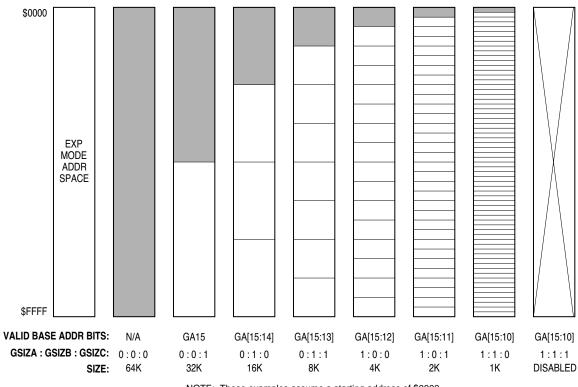

| 4.5   | Chip Selects4-1                | 8 |

|-------|--------------------------------|---|

| 4.5.1 | Program Chip Select4-1         | 8 |

| 4.5.2 | I/O Chip Selects               | 8 |

| 4.5.3 | General-Purpose Chip Select4-1 | 9 |

#### **SECTION 5 RESETS AND INTERRUPTS**

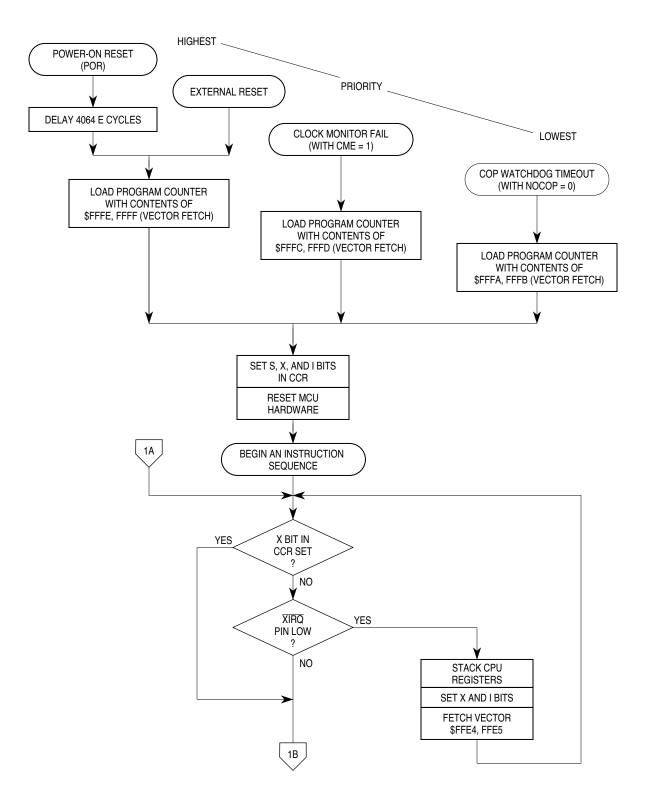

| 5.1    | Resets                                                | 5-1  |

|--------|-------------------------------------------------------|------|

| 5.1.1  | Power-On Reset                                        | 5-1  |

| 5.1.2  | External Reset (RESET)                                |      |

| 5.1.3  | Computer Operating Properly (COP) Reset               | 5-2  |

| 5.1.4  | Clock Monitor Reset                                   |      |

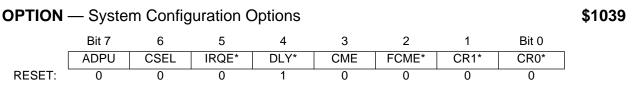

| 5.1.5  | OPTION Register                                       | 5-3  |

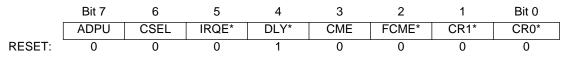

| 5.1.6  | CONFIG Register                                       | 5-4  |

| 5.2    | Effects of Reset                                      | 5-4  |

| 5.2.1  | Central Processing Unit                               | 5-5  |

| 5.2.2  | Memory Map                                            | 5-5  |

| 5.2.3  | Parallel I/O                                          | 5-5  |

| 5.2.4  | Timer                                                 | 5-5  |

| 5.2.5  | Real-Time Interrupt (RTI)                             | 5-5  |

| 5.2.6  | Pulse Accumulator                                     | 5-6  |

| 5.2.7  | Computer Operating Properly (COP)                     | 5-6  |

| 5.2.8  | Serial Communications Interface (SCI)                 | 5-6  |

| 5.2.9  | Serial Peripheral Interface (SPI)                     | 5-6  |

| 5.2.10 | Analog-to-Digital Converter                           | 5-6  |

| 5.2.11 | System                                                | 5-6  |

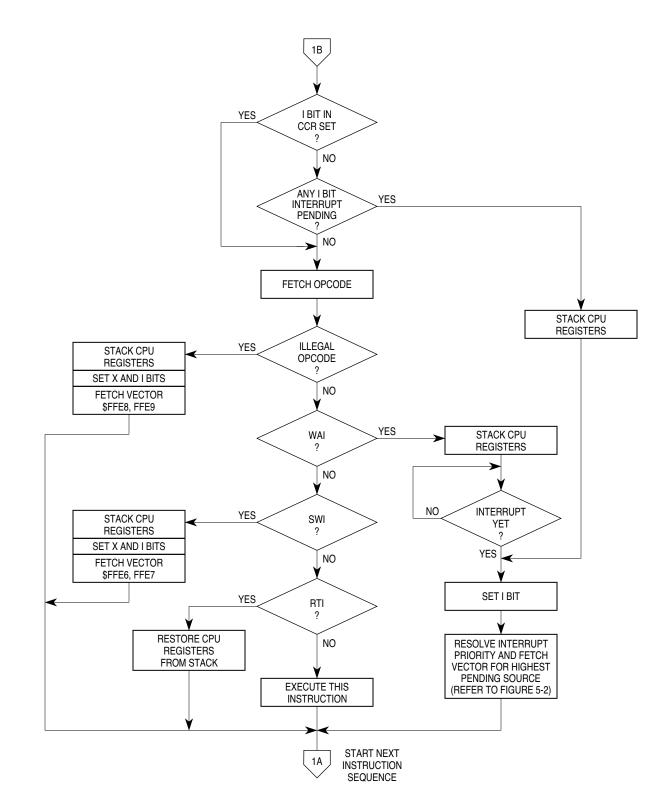

| 5.3    | Reset and Interrupt Priority                          |      |

| 5.3.1  | Highest Priority Interrupt and Miscellaneous Register | 5-7  |

| 5.4    | Interrupts                                            |      |

| 5.4.1  | Interrupt Recognition and Register Stacking           |      |

| 5.4.2  | Non-Maskable Interrupt Request (XIRQ)                 | 5-10 |

| 5.4.3  | Illegal Opcode Trap                                   | 5-10 |

| 5.4.4  | Software Interrupt                                    | 5-11 |

| 5.4.5  | Maskable Interrupts                                   | 5-11 |

| 5.4.6  | Reset and Interrupt Processing                        | 5-11 |

| 5.5    | Low Power Operation                                   | 5-16 |

| 5.5.1  | WAIT                                                  | 5-17 |

| 5.5.2  | STOP                                                  | 5-17 |

#### **SECTION 6 PARALLEL INPUT/OUTPUT**

| 6.1 | Port A |  | 6- | 1 |

|-----|--------|--|----|---|

|-----|--------|--|----|---|

#### TABLE OF CONTENTS (Continued) Title

#### Paragraph

Page

| Port B                         | 6-2                                            |

|--------------------------------|------------------------------------------------|

| Port C                         | 6-2                                            |

| Port D                         | 6-3                                            |

| Port E                         | 6-4                                            |

|                                |                                                |

| Port G                         | 6-5                                            |

| System Configuration Options 2 | 6-5                                            |

|                                | Port C<br>Port D<br>Port E<br>Port F<br>Port G |

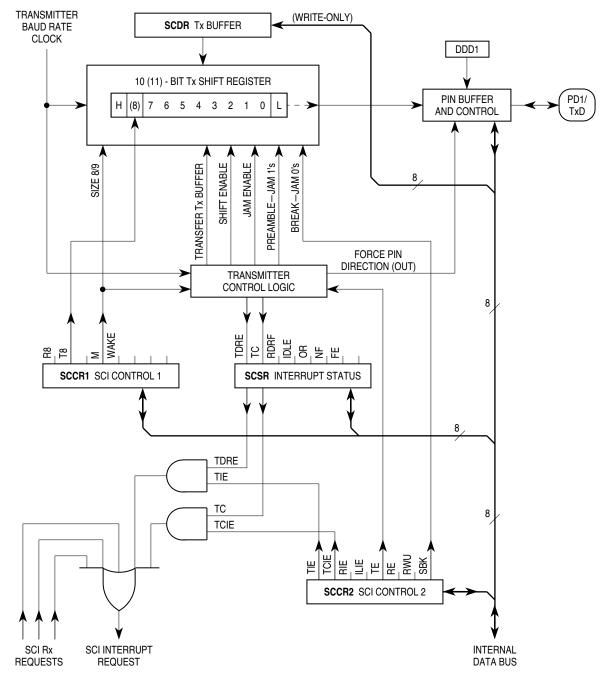

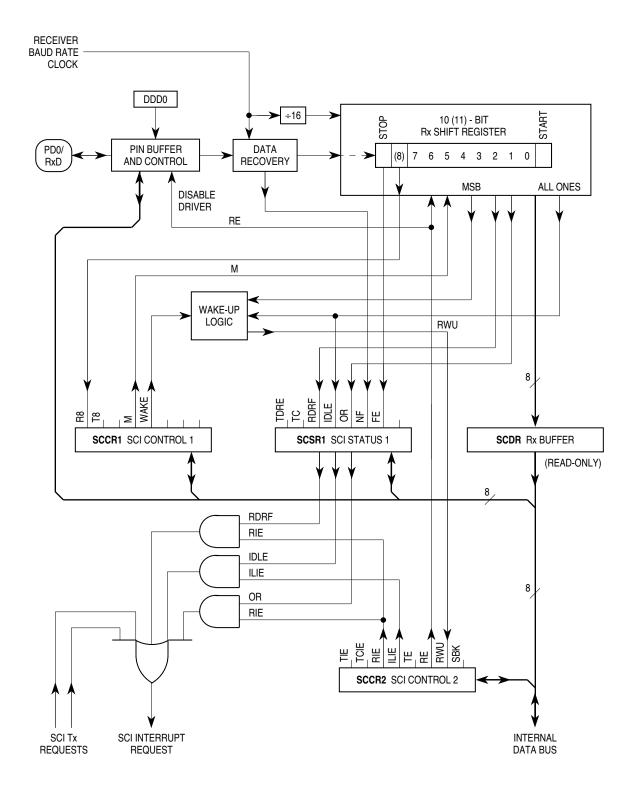

#### SECTION 7 SERIAL COMMUNICATIONS INTERFACE

| Data Format                              | 7-1                                                                                                                                                                                                                                       |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          |                                                                                                                                                                                                                                           |

|                                          |                                                                                                                                                                                                                                           |

|                                          |                                                                                                                                                                                                                                           |

|                                          |                                                                                                                                                                                                                                           |

|                                          |                                                                                                                                                                                                                                           |

| SCI Error Detection                      |                                                                                                                                                                                                                                           |

| SCI Registers                            | 7-5                                                                                                                                                                                                                                       |

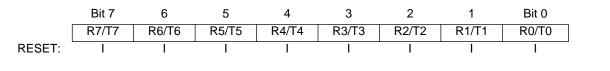

| Serial Communications Data Register      |                                                                                                                                                                                                                                           |

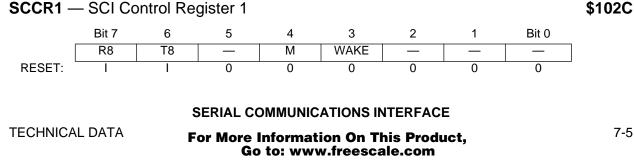

| Serial Communications Control Register 1 | 7-5                                                                                                                                                                                                                                       |

| Serial Communications Control Register 2 | 7-6                                                                                                                                                                                                                                       |

| Serial Communication Status Register     | 7-7                                                                                                                                                                                                                                       |

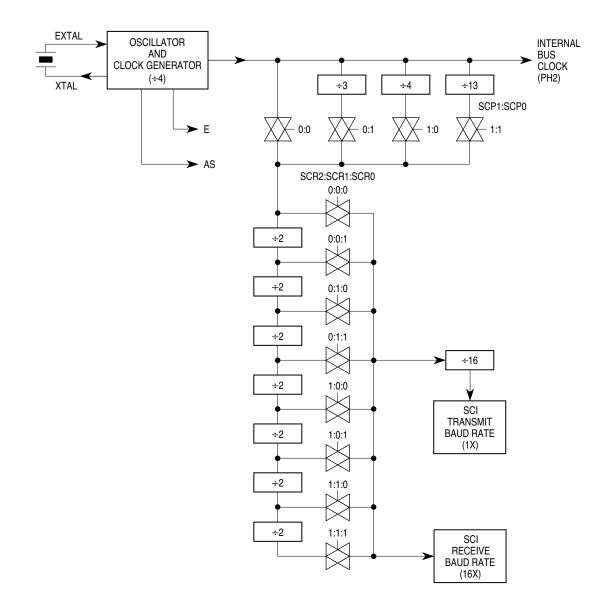

| Baud Rate Register                       | 7-8                                                                                                                                                                                                                                       |

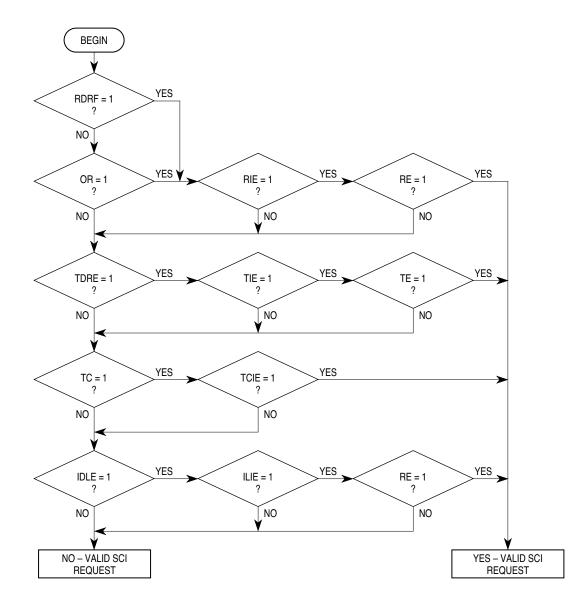

| Status Flags and Interrupts              |                                                                                                                                                                                                                                           |

| Receiver Flags                           |                                                                                                                                                                                                                                           |

|                                          | SCI Registers<br>Serial Communications Data Register<br>Serial Communications Control Register 1<br>Serial Communications Control Register 2<br>Serial Communication Status Register<br>Baud Rate Register<br>Status Flags and Interrupts |

#### SECTION 8 SERIAL PERIPHERAL INTERFACE

| 8.1   | Functional Description            | 8-1 |

|-------|-----------------------------------|-----|

| 8.2   | SPI Transfer Formats              |     |

| 8.2.1 | Clock Phase and Polarity Controls |     |

| 8.3   | SPI Signals                       |     |

| 8.3.1 | Master In Slave Out               |     |

| 8.3.2 | Master Out Slave In               |     |

| 8.3.3 | Serial Clock                      |     |

| 8.3.4 | Slave Select                      |     |

| 8.4   | SPI System Errors                 |     |

| 8.5   | SPI Registers                     |     |

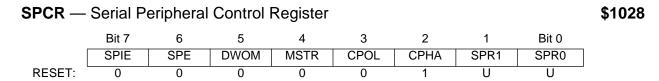

| 8.5.1 | Serial Peripheral Control         |     |

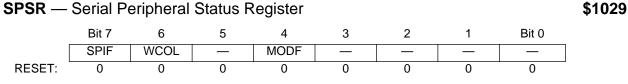

| 8.5.2 | Serial Peripheral Status          |     |

| 8.5.3 | Serial Peripheral Data Register   |     |

TECHNICAL DATA

#### TABLE OF CONTENTS (Continued) Title

Paragraph

#### Page

#### **SECTION 9 TIMING SYSTEM**

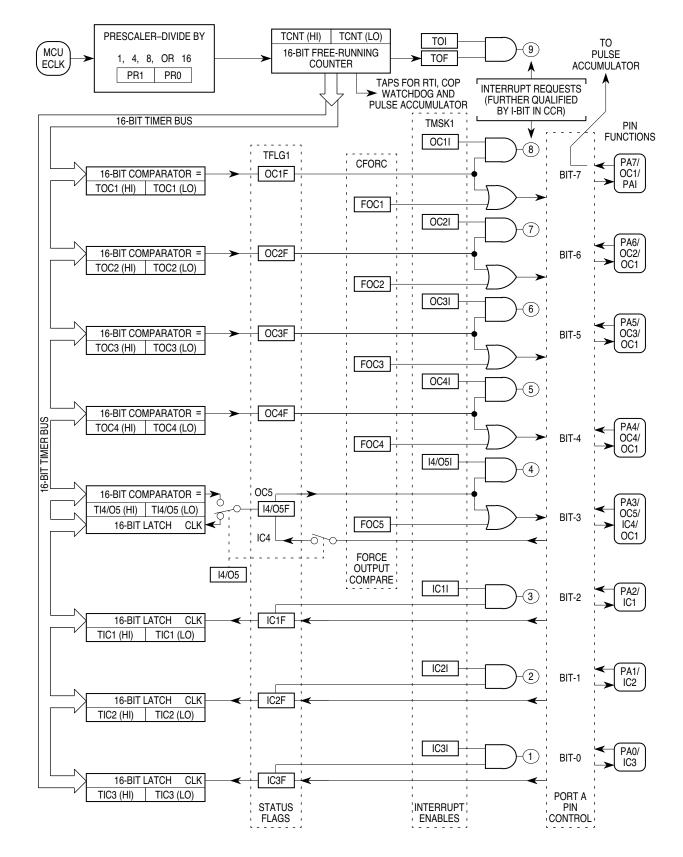

| 9.1    | Timer Structure                                 | 9-3  |

|--------|-------------------------------------------------|------|

| 9.2    | Input Capture                                   | 9-5  |

| 9.2.1  | Timer Control Register 2                        |      |

| 9.2.2  | Timer Input Capture Registers                   | 9-6  |

| 9.2.3  | Timer Input Capture 4/Output Compare 5 Register | 9-6  |

| 9.3    | Output Compare                                  | 9-6  |

| 9.3.1  | Timer Output Compare Registers                  | 9-7  |

| 9.3.2  | Timer Compare Force Register                    | 9-8  |

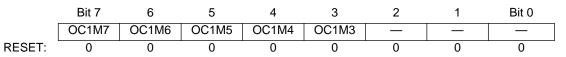

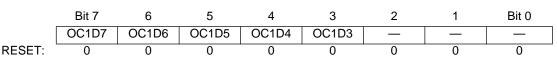

| 9.3.3  | Output Compare Mask Registers                   | 9-8  |

| 9.3.4  | Output Compare Data Register                    | 9-9  |

| 9.3.5  | Timer Counter Register                          |      |

| 9.3.6  | Timer Control Register 1                        |      |

| 9.3.7  | Timer Interrupt Mask Register 1                 |      |

| 9.3.8  | Timer Interrupt Flag Register 1                 |      |

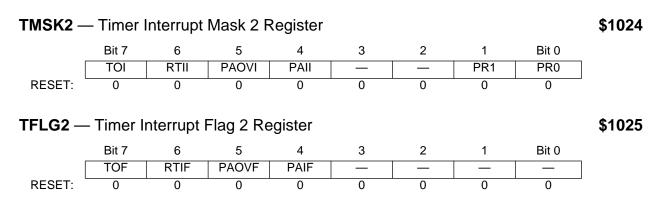

| 9.3.9  | Timer Interrupt Mask Register 2                 |      |

| 9.3.10 | Timer Interrupt Flag Register 2                 |      |

| 9.4    | Real-Time Interrupt                             | 9-12 |

| 9.4.1  | Timer Interrupt Mask Register 2                 | 9-13 |

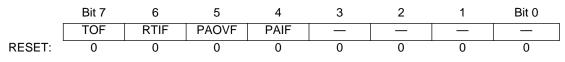

| 9.4.2  | Timer Interrupt Flag Register 2                 |      |

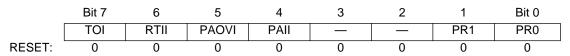

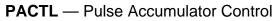

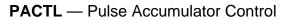

| 9.4.3  | Pulse Accumulator Control Register              | 9-14 |

| 9.5    | Computer Operating Properly Watchdog Function   | 9-15 |

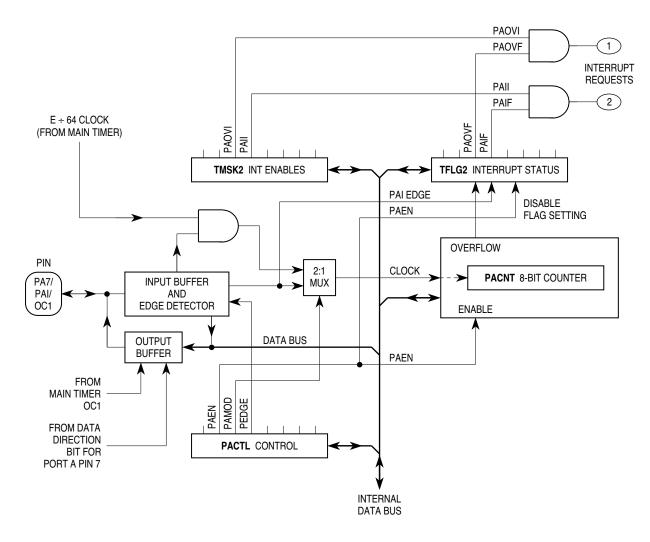

| 9.6    | Pulse Accumulator                               | 9-15 |

| 9.6.1  | Pulse Accumulator Control Register              |      |

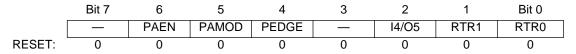

| 9.6.2  | Pulse Accumulator Count Register                |      |

| 9.6.3  | Pulse Accumulator Status and Interrupt Bits     | 9-18 |

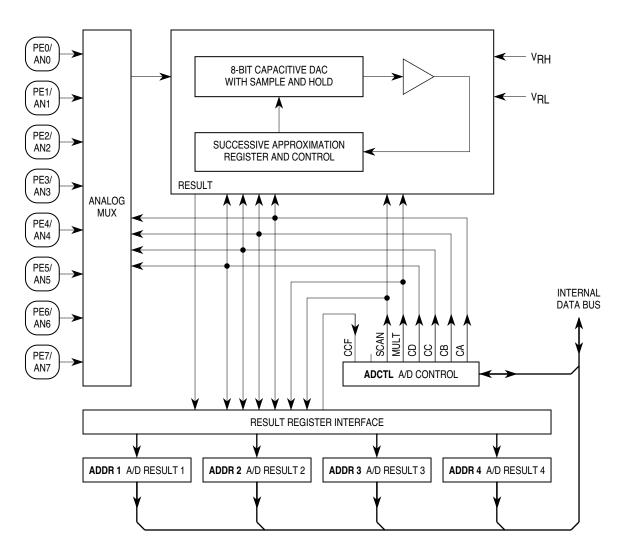

## SECTION 10 ANALOG-TO-DIGITAL CONVERTER

| Overview                                |                                                                                                                                                                                                                                                                                     |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multiplexer                             |                                                                                                                                                                                                                                                                                     |

| Analog Converter                        |                                                                                                                                                                                                                                                                                     |

| Digital Control                         |                                                                                                                                                                                                                                                                                     |

| Result Registers                        |                                                                                                                                                                                                                                                                                     |

|                                         |                                                                                                                                                                                                                                                                                     |

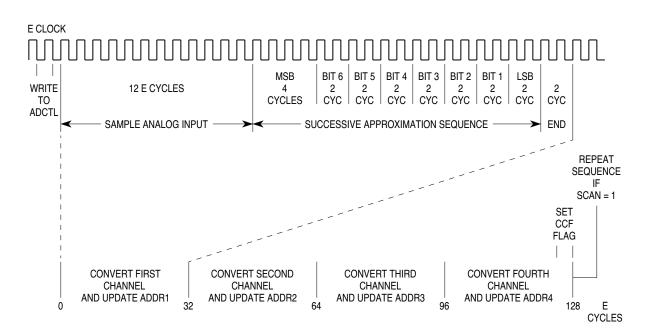

| Conversion Sequence                     |                                                                                                                                                                                                                                                                                     |

| A/D Converter Power-Up and Clock Select |                                                                                                                                                                                                                                                                                     |

| Conversion Process                      |                                                                                                                                                                                                                                                                                     |

| Channel Assignments                     |                                                                                                                                                                                                                                                                                     |

| Single-Channel Operation                |                                                                                                                                                                                                                                                                                     |

| Multiple-Channel Operation              |                                                                                                                                                                                                                                                                                     |

|                                         | Overview<br>Multiplexer<br>Analog Converter<br>Digital Control<br>Result Registers<br>A/D Converter Clocks<br>Conversion Sequence<br>A/D Converter Power-Up and Clock Select<br>Conversion Process<br>Channel Assignments<br>Single-Channel Operation<br>Multiple-Channel Operation |

#### TABLE OF CONTENTS (Continued) Title

#### Paragraph

| 10.7 | Operation in STOP and WAIT Modes10 | )-7 |

|------|------------------------------------|-----|

| 10.8 | A/D Control/Status Registers10     | )-7 |

| 10.9 | A/D Converter Result Registers10   | )-8 |

#### **APPENDIX A ELECTRICAL CHARACTERISTICS**

#### APPENDIX BMECHANICAL DATA AND ORDERING INFORMATION

| B.1 | Pin Assignments      | B-1 |

|-----|----------------------|-----|

| B.2 | Package Dimensions   | B-2 |

| B.3 | Ordering Information | B-3 |

#### APPENDIX CDEVELOPMENT SUPPORT

| C.1 | MC68HC11F1 Development Tools                                 | . C-1 |

|-----|--------------------------------------------------------------|-------|

| C.2 | MC68HC11EVS — Evaluation System                              | . C-1 |

| C.3 | M68MMDS11 — Modular Development System for M68HC11 Devices . | C-1   |

## LIST OF ILLUSTRATIONS

## Figure

#### Title

| 1-1  | MC68HC11F1 Block Diagram1-2                        |

|------|----------------------------------------------------|

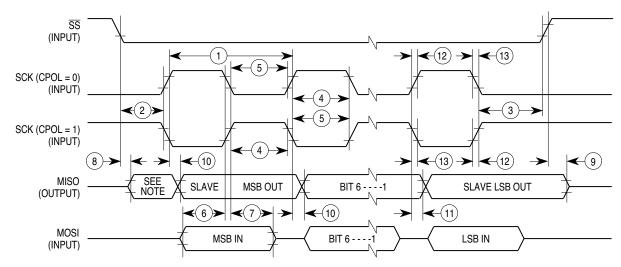

| 2-1  | Pin Assignments for MC68HC11F1 68-Pin PLCC         |

| 2-2  | Pin Assignments for MC68HC11F1 80-Pin QFP          |

| 2-3  | External Reset Circuit                             |

| 2-4  | Common Crystal Connections                         |

| 2-5  | External Oscillator Connections                    |

| 2-6  | One Crystal Driving Two MCUs                       |

| 2-7  | 4XOUT Signal Driving a Second MCU                  |

| 3-1  | Programming Model                                  |

| 3-2  | Stacking Operations                                |

| 4-1  | MC68HC11F1 Memory Map                              |

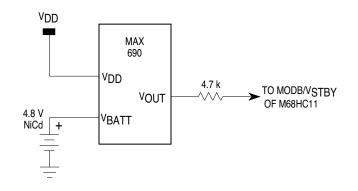

| 4-2  | RAM Standby MODB/V <sub>STBY</sub> Connections     |

| 4-3  | Address Map for I/O and Program Chip Selects       |

| 4-4  | Address Map for General-Purpose Chip Select        |

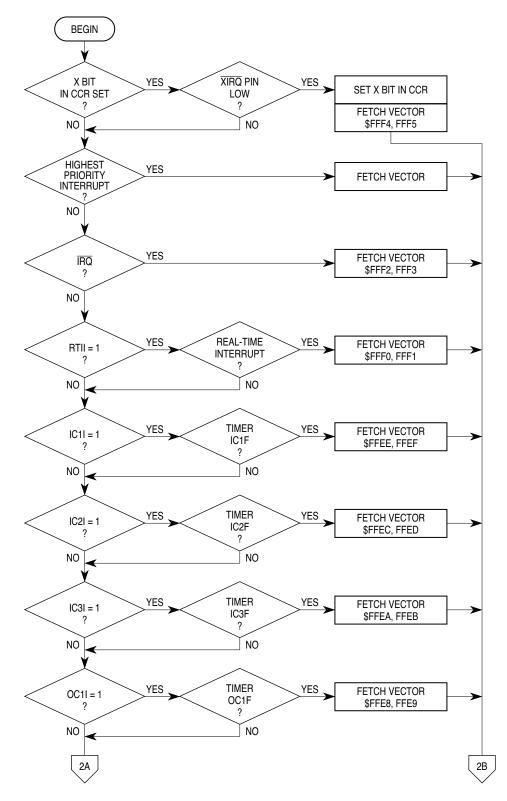

| 5-1  | Processing Flow Out of Reset (1 of 2)              |

| 5-2  | Processing Flow Out of Reset (2 of 2)              |

| 5-3  | Interrupt Priority Resolution (1 of 2)             |

| 5-4  | Interrupt Priority Resolution (2 of 2)             |

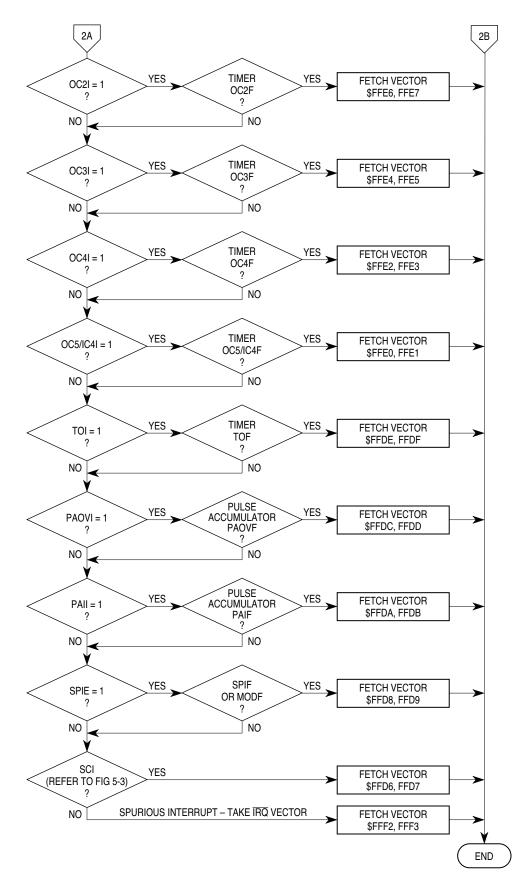

| 5-5  | Interrupt Source Resolution Within SCI             |

| 7-1  | SCI Transmitter Block Diagram                      |

| 7-2  | SCI Receiver Block Diagram                         |

| 7-3  | SCI Baud Rate Generator Block Diagram7-10          |

| 7-4  | Interrupt Source Resolution Within SCI             |

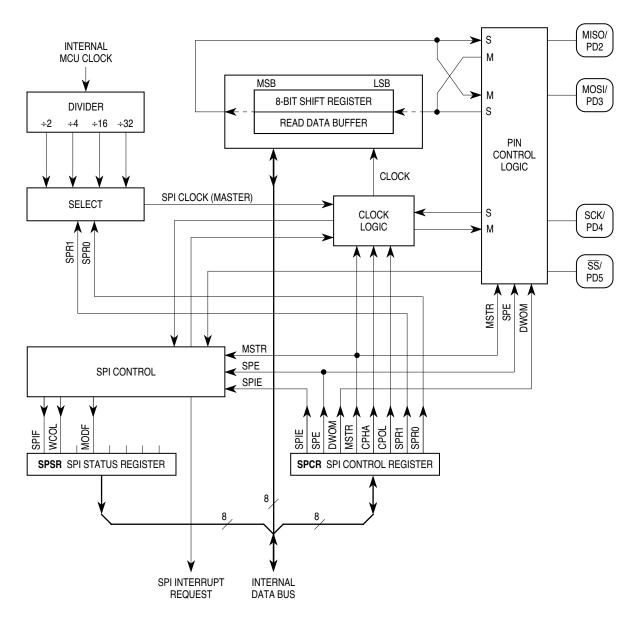

| 8-1  | SPI Block Diagram                                  |

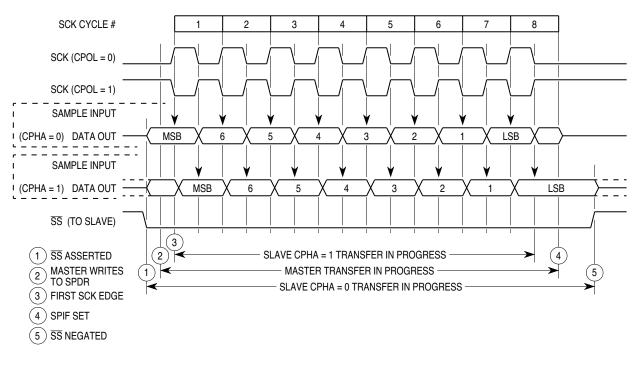

| 8-2  | SPI Transfer Format                                |

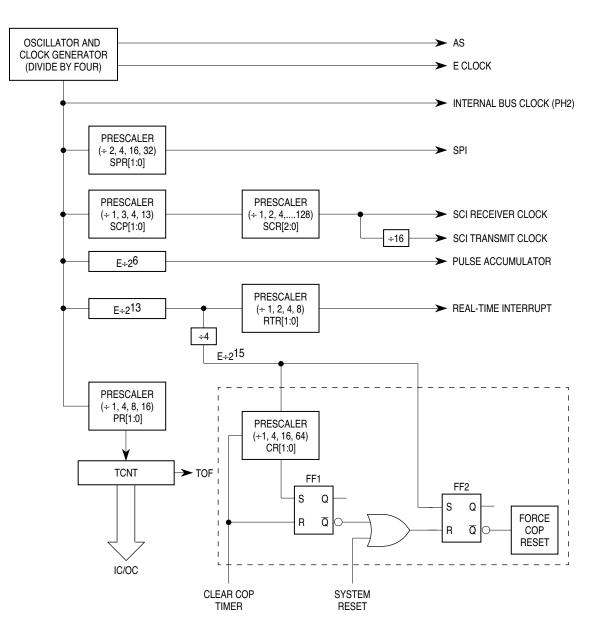

| 9-1  | Timer Clock Divider Chains                         |

| 9-2  | Capture/Compare Block Diagram                      |

| 9-3  | Pulse Accumulator                                  |

| 10-1 | A/D Converter Block Diagram                        |

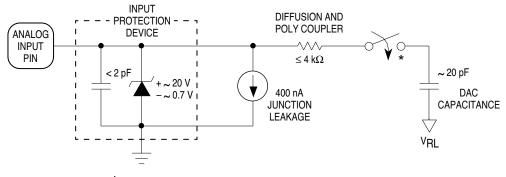

| 10-2 | Electrical Model of an A/D Input Pin (Sample Mode) |

| 10-3 | A/D Conversion Sequence                            |

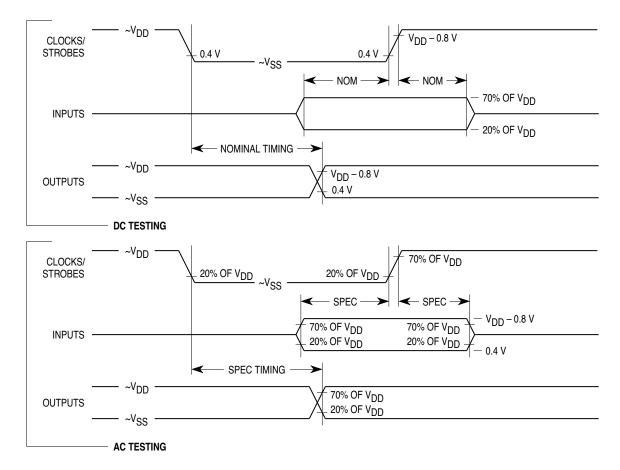

| A-1  | Test MethodsA-4                                    |

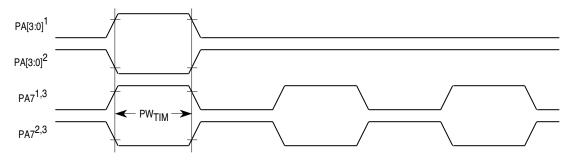

| A-2  | Timer InputsA-5                                    |

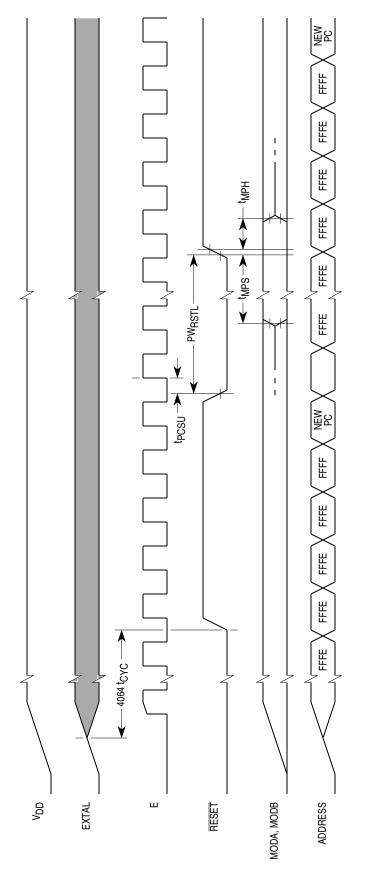

| A-3  | POR External Reset Timing DiagramA-6               |

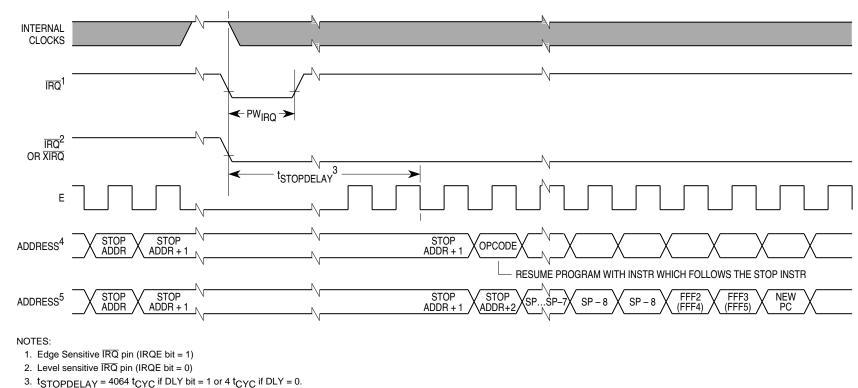

| A-4  | STOP Recovery Timing DiagramA-7                    |

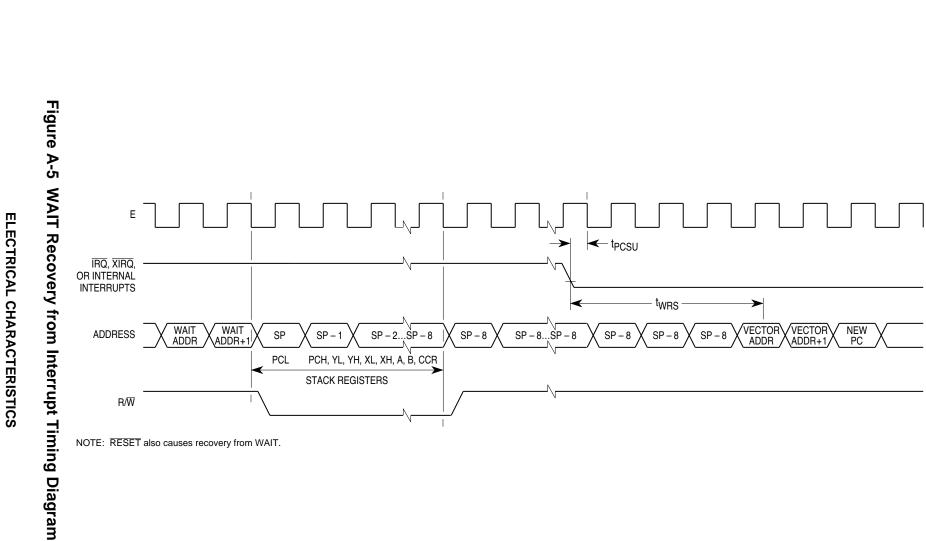

| A-5  | WAIT Recovery from Interrupt Timing DiagramA-8     |

| A-6  | Interrupt Timing DiagramA-9                        |

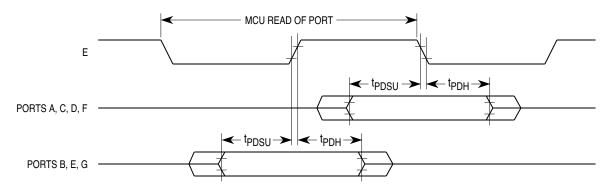

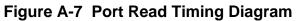

| A-7  | Port Read Timing DiagramA-10                       |

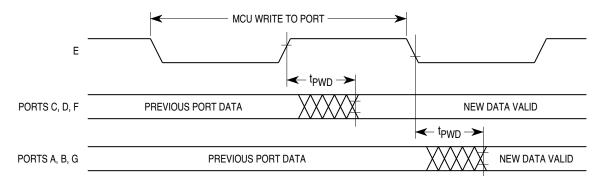

| A-8  | Port Write Timing DiagramA-10                      |

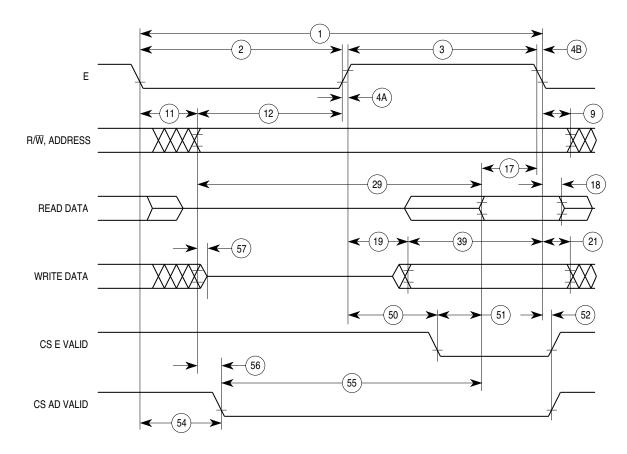

| A-9  | Expansion Bus TimingA-13                           |

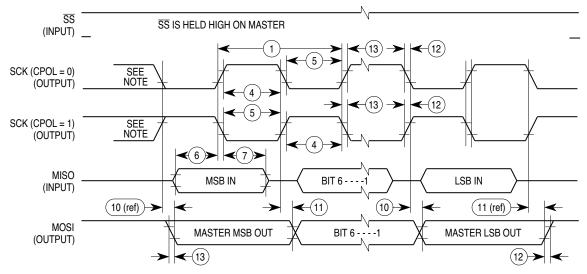

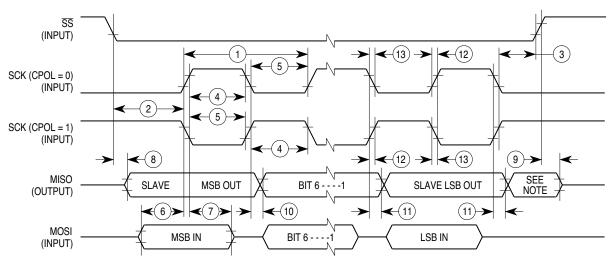

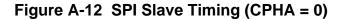

| A-10 | SPI Master Timing (CPHA = 0)A-15                   |

#### LIST OF ILLUSTRATIONS (Continued) Title

## Figure

Page

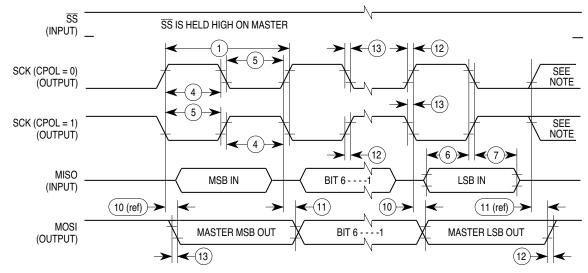

| A-11 | SPI Master Timing (CPHA = 1)     | A-15 |

|------|----------------------------------|------|

|      | SPI Slave Timing (CPHA = 0)      |      |

|      | SPI Slave Timing (CPHA = 1)      |      |

| B-1  | MC68HC11F1 68-Pin PLCC           | B-1  |

| B-2  | MC68HC11F1 80-Pin Quad Flat Pack | B-2  |

TECHNICAL DATA

## LIST OF TABLES

#### Table

#### Title

#### Page

| 2-1  | Port Signal Functions                         |

|------|-----------------------------------------------|

| 3-1  | Reset Vector Comparison                       |

| 3-2  | Instruction Set                               |

| 4-1  | Register and Control Bit Assignments          |

| 4-2  | Write Access Limited Registers                |

| 4-3  | Hardware Mode Select Summary                  |

| 4-4  | EEPROM Mapping                                |

| 4-5  | RAM and Register Mapping                      |

| 4-6  | EEPROM Block Protection                       |

| 4-7  | EEPROM Erase Mode Control                     |

| 4-8  | Chip Select Clock Stretch Control             |

| 4-9  | Program Chip Select Size Control              |

| 4-10 | General-Purpose Chip Select Starting Address  |

| 4-11 | General-Purpose Chip Select Size Control      |

| 4-12 | Chip Select Control Parameter Summary         |

| 5-1  | COP Timer Rate Selection                      |

| 5-2  | Reset Cause, Operating Mode, and Reset Vector |

| 5-3  | Highest Priority Interrupt Selection          |

| 5-4  | Interrupt and Reset Vector Assignments5-9     |

| 5-5  | Stacking Order on Entry to Interrupts         |

| 6-1  | I/O Port Configuration                        |

| 7-1  | Baud Rate Prescaler Selection                 |

| 7-2  | Baud Rate Selection7-9                        |

| 8-1  | SPI Clock Rates                               |

| 9-1  | Timer Summary                                 |

| 9-2  | Timer Output Compare Configuration            |

| 9-3  | Timer Prescaler Selection                     |

| 9-4  | RTI Rate Selection                            |

| 9-5  | Pulse Accumulator Timing                      |

| 9-6  | Pulse Accumulator Edge Detection Control      |

| 10-1 | A/D Converter Channel Assignments             |

| 10-2 | A/D Converter Channel Selection 10-8          |

| A-1  | Maximum RatingsA-1                            |

| A-2  | Thermal CharacteristicsA-2                    |

| A-3  | DC Electrical CharacteristicsA-3              |

| A-4  | Control TimingA-5                             |

| A-5  | Peripheral Port TimingA-10                    |

| A-6  | Analog-To-Digital Converter Characteristics   |

| A-7  | Expansion Bus TimingA-12                      |

| A-8  | Serial Peripheral Interface TimingA-14        |

| A-9  | EEPROM CharacteristicsA-17                    |

#### LIST OF TABLES (Continued) Title

### Table

Page

| B-1 | Device Ordering InformationB-3 | 3 |

|-----|--------------------------------|---|

| C-1 | MC68HC11F1 Development ToolsC- | 1 |

TECHNICAL DATA

## **SECTION 1INTRODUCTION**

The MC68HC11F1 high-performance microcontroller unit (MCU) is an enhanced derivative of the M68HC11 family of microcontrollers and includes many advanced features. This MCU, with a nonmultiplexed expanded bus, is characterized by high speed and low power consumption. The fully static design allows operation at frequencies from 4 MHz to dc.

#### 1.1 Features

- M68HC11 Central Processing Unit (CPU)

- Power Saving STOP and WAIT Modes

- 512 Bytes Electrically Erasable Programmable Read-Only Memory (EEPROM)

- 1024 Bytes RAM, Data Retained During Standby

- Nonmultiplexed Address and Data Buses

- Enhanced 16-Bit Timer

- Three Input Capture (IC) Channels

- Four Output Compare (OC) Channels

- One Additional Channel, Selectable as Fourth IC or Fifth OC

- 8-Bit Pulse Accumulator

- Real-Time Interrupt Circuit

- Computer Operating Properly (COP) Watchdog

- Enhanced Asynchronous Nonreturn to Zero (NRZ) Serial Communications Interface (SCI)

- Enhanced Synchronous Serial Peripheral Interface (SPI)

- Eight-Channel 8-Bit Analog-to-Digital (A/D) Converter

- Four Chip-Select Signal Outputs with Programmable Clock Stretching

- Two I/O Chip Selects

- One Program Chip Select

- One General-Purpose Chip Select

- Available in 68-Pin Plastic Leaded Chip Carrier (PLCC) and 80-Pin Plastic Quad Flat Pack (QFP)

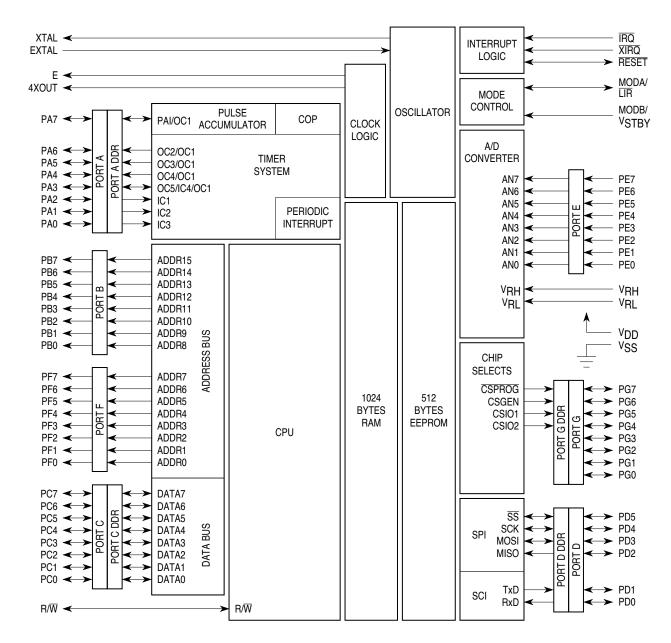

Figure 1-1 MC68HC11F1 Block Diagram

#### **SECTION 2 PIN DESCRIPTIONS**

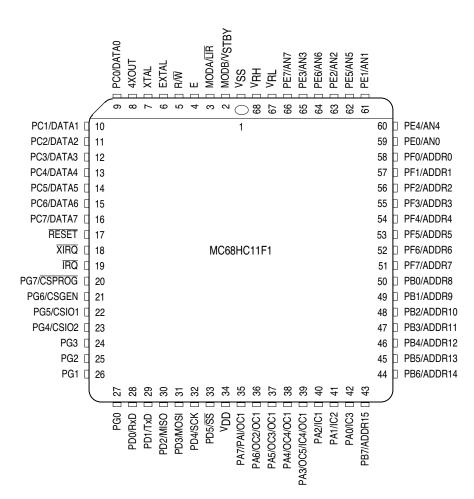

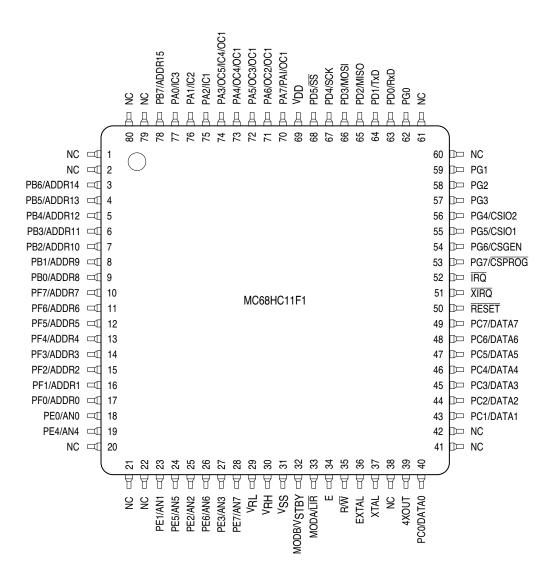

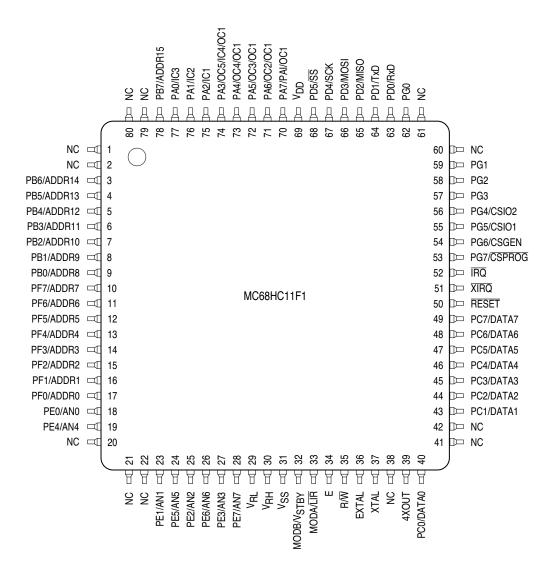

The MC68HC11F1 MCU is available in a 68-pin plastic leaded chip carrier (PLCC) and an 80-pin plastic quad flat pack (QFP). Most pins on this MCU serve two or more functions, as described in the following paragraphs. **Figure 2-1** shows the pin assignments for the PLCC. **Figure 2-2** shows the pin assignments for the QFP.

Figure 2-1 Pin Assignments for MC68HC11F1 68-Pin PLCC

Figure 2-2 Pin Assignments for MC68HC11F1 80-Pin QFP

#### 2.1 V<sub>DD and</sub> V<sub>SS</sub>

Power is supplied to the MCU through  $V_{DD}$  and  $V_{SS}$ .  $V_{DD}$  is the power supply, and  $V_{SS}$  is ground. The MCU operates from a single 5-volt (nominal) power supply. Very fast signal transitions occur on the MCU pins. The short rise and fall times place high, short duration current demands on the power supply. To prevent noise problems, provide good power-supply bypassing at the MCU. Also, use bypass capacitors that have good high-frequency characteristics and situate them as close to the MCU as possible. Bypass requirements vary, depending on how heavily the MCU pins are loaded.

Go to: www.freescale.com

MC68HC11F1 TECHNICAL DATA

#### 2.2 Reset (RESET)

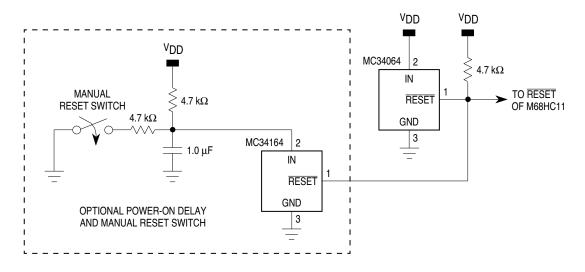

An active low bidirectional control signal, RESET, acts as an input to initialize the MCU to a known start-up state. It also acts as an open-drain output to indicate that an internal failure has been detected in either the clock monitor or COP watchdog circuit. The CPU distinguishes between internal and external reset conditions by sensing whether the reset pin rises to a logic one in less than two E-clock cycles after a reset has occurred. It is not advisable to connect an external resistor-capacitor (RC) power-up delay circuit to the reset pin of M68HC11 devices because the circuit charge time constant can cause the device to misinterpret the type of reset that occurred. Refer to **SECTION 5 RESETS AND INTERRUPTS** for further information.

**Figure 2-3** illustrates a reset circuit that uses an external switch. Other circuits can be used, however, it is important to incorporate a low voltage interrupt (LVI) circuit to prevent operation at insufficient voltage levels which could result in erratic behavior or corruption of RAM.

Figure 2-3 External Reset Circuit

#### 2.3 E-Clock Output (E)

E is the output connection for the internally generated E clock. The signal from E is used as a timing reference. The frequency of the E-clock output is one fourth that of the input frequency at the EXTAL pin. When E-clock output is low, an internal process is taking place. When it is high, data is being accessed. All clocks, including the E clock, are halted when the MCU is in STOP mode. The E clock can be turned off in single-chip modes to reduce the effects of radio frequency interference (RFI). Refer to **SECTION 9 TIMING SYSTEM**.

#### 2.4 Crystal Driver and External Clock Input (XTAL, EXTAL)

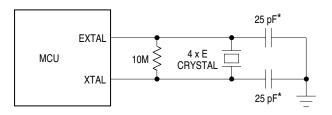

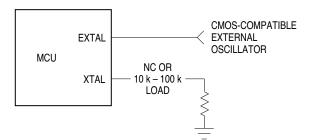

These two pins provide the interface for either a crystal or a CMOS-compatible clock to control the internal clock generator circuitry. Either a crystal oscillator or a CMOS compatible clock can be used. The resulting E-clock rate is the input frequency divided by four.

**PIN DESCRIPTIONS**

**TECHNICAL DATA**

The XTAL pin is normally left unterminated when an external CMOS compatible clock is connected to the EXTAL pin. However, a 10 k $\Omega$  to 100 k $\Omega$  load resistor connected from the XTAL output to ground can be used to reduce RFI noise emission.

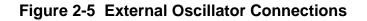

The XTAL output is normally used to drive a crystal. The XTAL output can be buffered with a high-impedance buffer, or it can be used to drive the EXTAL input of another M68HC11 device. Refer to **Figure 2-6**.

In all cases, use caution when designing circuitry associated with the oscillator pins. Load capacitances shown in the oscillator circuits include all stray layout capacitances. Refer to **Figure 2-4**, **Figure 2-5**, and **Figure 2-6**.

\* Values include all stray capacitances.

#### Figure 2-4 Common Crystal Connections

\* Values include all stray capacitances.

#### Figure 2-6 One Crystal Driving Two MCUs

MC68HC11F1 TECHNICAL DATA

Semiconductor, Inc.

2-4

#### 2.5 Four Times E-Clock Frequency Output (4XOUT)

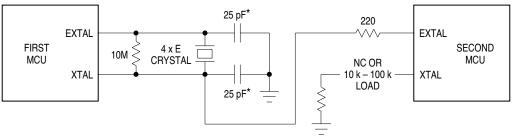

Although the circuit shown in **Figure 2-6** will work for any M68HC11 MCU, the MC68HC11F1 has an additional clock output that is four times the E-clock frequency. This output (4XOUT) can be used to directly drive the EXTAL input of another M68HC11 MCU. Refer to **Figure 2-7**. The 4XOUT output is enabled after reset and can be disabled by clearing the CLK4X bit in the OPT2 register.

Figure 2-7 4XOUT Signal Driving a Second MCU

#### 2.6 Interrupt Request (IRQ)

The  $\overline{IRQ}$  input provides a means of generating asynchronous interrupt requests for the CPU. Either falling-edge triggering or low-level triggering is selected by the IRQE bit in the OPTION register.  $\overline{IRQ}$  is always configured for level-sensitive triggering at reset. Connect an external pull-up resistor, typically 4.7 k $\Omega$ , to V<sub>DD</sub> when  $\overline{IRQ}$  is used in a level-sensitive wired-OR configuration. Refer to **SECTION 5 RESETS AND INTER-RUPTS**.

#### 2.7 Non-Maskable Interrupt (XIRQ)

The  $\overline{XIRQ}$  input provides a means of requesting a non-maskable interrupt after reset initialization. During reset, the X bit in the condition code register (CCR) is set and any interrupt is masked until MCU software enables it. Because the  $\overline{XIRQ}$  input is level sensitive, it can be connected to a multiple-source wired-OR network with an external pull-up resistor to V<sub>DD</sub>.  $\overline{XIRQ}$  is often used as a power loss detect interrupt.

Whenever  $\overline{XIRQ}$  or  $\overline{IRQ}$  are used with multiple interrupt sources ( $\overline{IRQ}$  must be configured for level-sensitive operation if there is more than one source of  $\overline{IRQ}$  interrupt), each source must drive the interrupt input with an open-drain type of driver to avoid contention between outputs. There should be a single pull-up resistor near the MCU interrupt input pin (typically 4.7 k $\Omega$ ). There must also be an interlock mechanism at each interrupt source so that the source holds the interrupt line low until the MCU recognizes and acknowledges the interrupt request. If one or more interrupt sources are still pending after the MCU services a request, the interrupt line will still be held low and the MCU will be interrupted again as soon as the interrupt mask bit in the condition code register (CCR) is cleared (normally upon return from an interrupt). Refer to **SEC-TION 5 RESETS AND INTERRUPTS**.

#### 2.8 MODA and MODB (MODA/LIR and MODB/VSTBY)

During reset, MODA and MODB select one of the four operating modes. Refer to **SEC-TION 4 OPERATING MODES AND ON-CHIP MEMORY**.

After the operating mode has been selected, the  $\overline{\text{LIR}}$  pin provides an open-drain output to indicate that execution of an instruction has begun. The LIR pin is configured for wired-OR operation (only pulls low). A series of E-clock cycles occurs during execution of each instruction. The  $\overline{\text{LIR}}$  signal is asserted (drives low) during the first E-clock cycle of each instruction (opcode fetch). This output is provided for assistance in program debugging.

The V<sub>STBY</sub> pin is used to input RAM standby power. The MCU is powered from the V<sub>DD</sub> signal unless the difference between the level of V<sub>STBY</sub> and V<sub>dd</sub> is greater than one MOS threshold (about 0.7 volts). When these voltages differ by more than 0.7 volts, the internal 768-byte RAM and part of the reset logic are powered from V<sub>STBY</sub> rather than V<sub>DD</sub>. This allows RAM contents to be retained without V<sub>DD</sub> power applied to the MCU. Reset must be driven low before V<sub>DD</sub> is removed and must remain low until V<sub>DD</sub> has been restored to a valid level.

#### 2.9 $V_{RH}$ and $V_{RL}$

These pins provide the reference voltage for the analog-to-digital converter. Bypass capacitors should be used to minimize noise on these signals. Any noise on  $V_{RH}$  and  $V_{RL}$  will directly affect A/D accuracy.

#### 2.10 R/W

In expanded and test modes, R/W indicates the direction of transfers on the external data bus. A logic level one on this pin indicates that a read cycle is in progress. A logic zero on this pin indicates that a write cycle is in progress and that no external device should drive the data bus.

The E-clock can be used to enable external devices to drive data onto the data bus during the second half of a read bus cycle (E clock high). R/W can then be used to control the direction of data transfers. R/W drives low when data is being written to the external data bus. R/W will remain low during consecutive data bus write cycles, such as when a double-byte store occurs.

#### 2.11 Port Signals

For the MC68HC11F1, 54 pins are arranged into six 8-bit ports: A, B, C, E, F, and G, and one 6-bit port (D). Each of these seven ports serves a purpose other than I/O, depending on the operating mode or peripheral functions selected. Note that ports B, C, and F are available for I/O functions only in single-chip and bootstrap modes. The pins of ports A, C, D, and G are fully bidirectional. Ports B and F are output-only ports. Port E is an input-only port. Refer to **Table 2-1** for details about the 54 port signals' functions within different operating modes.

MC68HC11F1 TECHNICAL DATA

| Port/Bit | Single-Chip and<br>Bootstrap Mode | Expanded and<br>Special Test Mode |

|----------|-----------------------------------|-----------------------------------|

| PA0      | PA0/IC3                           |                                   |

| PA1      | PA1/IC2                           |                                   |

| PA2      | PA2/IC1                           |                                   |

| PA3      | PA3/OC5/IC4/0                     | DC1                               |

| PA4      | PA4/OC4/OC                        | 21                                |

| PA5      | PA5/OC3/OC                        | 21                                |

| PA6      | PA6/OC2/OC                        | 21                                |

| PA7      | PA7/PAI/OC                        | :1                                |

| PB[7:0]  | PB[7:0]                           | ADDR[15:8]                        |

| PC[7:0]  | PC[7:0]                           | DATA[7:0]                         |

| PD0      | PD0/RxD                           |                                   |

| PD1      | PD1/TxD                           |                                   |

| PD2      | PD2/MISO                          |                                   |

| PD3      | PD3/MOSI                          |                                   |

| PD4      | PD4/SCK                           |                                   |

| PD5      | PD5/SS                            |                                   |

| PE[7:0]  | PE[7:0]/AN[7                      | :0]                               |

| PF[7:0]  | PF[7:0]                           | ADDR[7:0]                         |

| PG0      | PG0                               |                                   |

| PG1      | PG1                               |                                   |

| PG2      | PG2                               |                                   |

| PG3      | PG3                               |                                   |

| PG4      | PG4                               | PG4/CSIO2                         |

| PG5      | PG5                               | PG5/CSIO1                         |

| PG6      | PG6                               | PG6/CSGEN                         |

| PG7      | PG7                               | PG7/CSPROG                        |

#### **Table 2-1 Port Signal Functions**

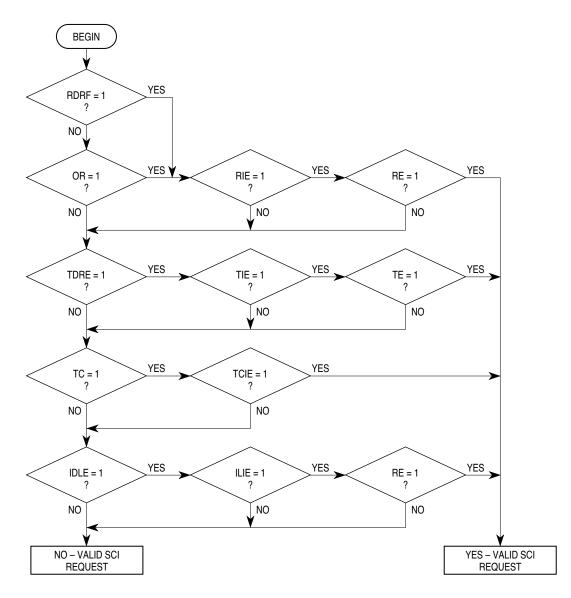

#### 2.11.1 Port A

Port A is an 8-bit general-purpose I/O port with a data register (PORTA) and a data direction register (DDRA). Port A pins share functions with the 16-bit timer system. PORTA can be read at any time. Inputs return the pin level; outputs return the pin driver input level. If written, PORTA stores the data in internal latches. It drives the pins only if they are configured as outputs. Writes to PORTA do not change the pin state when the pins are configured for timer output compares.

Out of reset, port A pins [7:0] are general-purpose high-impedance inputs. When the timer functions associated with these pins are disabled, the bits in DDRA govern the I/O state of the associated pin. For further information, refer to **SECTION 6 PARAL-LEL INPUT/OUTPUT**.

#### NOTE

When using the information about port functions, do not confuse pin function with the electrical state of the pin at reset. All general-purpose I/O pins configured as inputs at reset are in a high-impedance state. Port data registers reflect the logic state of the port at reset. The pin function is mode dependent.

#### **PIN DESCRIPTIONS**

TECHNICAL DATA

#### 2.11.2 Port B

Port B is an 8-bit output-only port. In single-chip modes, port B pins are general-purpose output pins (PB[7:0]). In expanded modes, port B pins act as the high-order address lines (ADDR[15:8]) of the address bus.

PORTB can be read at any time. Reads of PORTB return the pin driver input level. If PORTB is written, the data is stored in internal latches. It drives the pins only in singlechip or bootstrap mode. In expanded operating modes, port B pins are the high-order address outputs (ADDR[15:8]).

Refer to SECTION 6 PARALLEL INPUT/OUTPUT.

#### 2.11.3 Port C

Port C is an 8-bit general-purpose I/O port with a data register (PORTC) and a data direction register (DDRC). In single-chip modes, port C pins are general-purpose I/O pins (PC[7:0]). In expanded modes, port C pins are configured as data bus pins (DA-TA[7:0]).

PORTC can be read at any time. Inputs return the pin level; outputs return the pin driver input level. If PORTC is written, the data is stored in internal latches. It drives the pins only if they are configured as outputs in single-chip or bootstrap mode. Port C pins are general-purpose inputs out of reset in single-chip and bootstrap modes. In expanded and test modes, these pins are data bus lines out of reset.

The CWOM control bit in the OPT2 register disables port C's P-channel output drivers. Because the N-channel driver is not affected by CWOM, setting CWOM causes port C to become an open-drain-type output port suitable for wired-OR operation. In wired-OR mode, (PORTC bits are at logic level zero), pins are actively driven low by the Nchannel driver. When a port C bit is at logic level one, the associated pin is in a highimpedance state, as neither the N-channel nor the P-channel devices are active. It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. Port C can only be configured for wired-OR operation when the MCU is in single-chip or bootstrap modes.

Refer to SECTION 6 PARALLEL INPUT/OUTPUT.

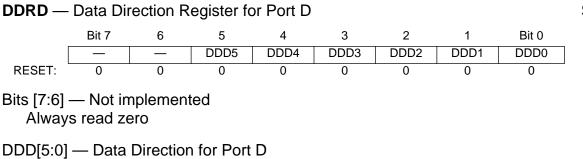

#### 2.11.4 Port D

Port D, a 6-bit general-purpose I/O port, has a data register (PORTD) and a data direction register (DDRD). The six port D lines (D[5:0]) can be used for general-purpose I/O, for the serial communications interface (SCI) and serial peripheral interface (SPI) subsystems.

PORTD can be read at any time. Inputs return the pin level; outputs return the pin driver input level. If PORTD is written, the data is stored in internal latches and can be driven only if port D is configured for general-purpose output.

The DWOM control bit in the SPCR register disables port D's P-channel output drivers. Because the N-channel driver is not affected by DWOM, setting DWOM causes port D to become an open-drain-type output port suitable for wired-OR operation. In wired-

```

PIN DESCRIPTIONS

```

MC68HC11F1 TECHNICAL DATA

OR mode, (PORTD bits are at logic level zero), pins are actively driven low by the Nchannel driver. When a port D bit is at logic level one, the associated pin is in a highimpedance state, as neither the N-channel nor the P-channel devices are active. It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. Port D can be configured for wired-OR operation in any operating mode.

#### Refer to SECTION 6 PARALLEL INPUT/OUTPUT, SECTION 7 SERIAL COMMUNI-CATIONS INTERFACE, and SECTION 8 SERIAL PERIPHERAL INTERFACE.

#### 2.11.5 Port E

Port E is an 8-bit input-only port that is also used as the analog input port for the analog-to-digital converter. Port E pins that are not used for the A/D system can be used as general-purpose inputs. However, PORTE should not be read during the sample portion of an A/D conversion sequence.

#### Refer to SECTION 10 ANALOG-TO-DIGITAL CONVERTER.

#### 2.11.6 Port F

Port F is an 8-bit output-only port. In single-chip mode, port F pins are general-purpose output pins (PF[7:0]). In expanded mode, port F pins act as the low-order address outputs (ADDR[7:0]).

PORTF can be read at any time. Reads of PORTF return the pin driver input level. If PORTF is written, the data is stored in internal latches. It drives the pins only in singlechip or bootstrap mode. In expanded operating modes, port F pins are the low-order address outputs (ADDR[7:0]).

Refer to SECTION 6 PARALLEL INPUT/OUTPUT.

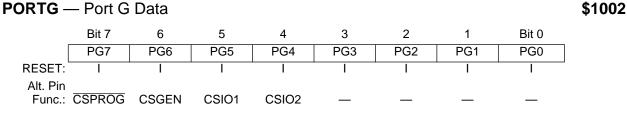

#### 2.11.7 Port G

Port G is an 8-bit general-purpose I/O port. When enabled, four chip select signals are alternate functions of port G bits [7:4].

PORTG can be read at any time. Inputs return the pin level; outputs return the pin driver input level. If PORTG is written, the data is stored in internal latches. It drives the pins only if they are configured as outputs.

The GWOM control bit in the OPT2 register disables port G's P-channel output drivers. Because the N-channel driver is not affected by GWOM, setting GWOM causes port G to become an open-drain-type output port suitable for wired-OR operation. In wired-OR mode, (PORTG bits are at logic level zero), pins are actively driven low by the Nchannel driver. When a port G bit is at logic level one, the associated pin is in a highimpedance state, as neither the N-channel nor the P-channel devices are active. It is customary to have an external pull-up resistor on lines that are driven by open-drain devices. Port G can be configured for wired-OR operation in any operating mode.

## Refer to SECTION 6 PARALLEL INPUT/OUTPUT and SECTION 4 OPERATING MODES AND ON-CHIP MEMORY.

**PIN DESCRIPTIONS**

TECHNICAL DATA

MC68HC11F1 TECHNICAL DATA

**PIN DESCRIPTIONS**

## **SECTION 3 CENTRAL PROCESSING UNIT**

This section presents information on M68HC11 central processing unit (CPU) architecture. Data types, addressing modes, the instruction set, and the extended addressing range required to support this MCU's memory expansion feature are also included, as are special operations such as subroutine calls and interrupts.

The CPU is designed to treat all peripheral, I/O, and memory locations identically as addresses in the 64 Kbyte memory map. This is referred to as memory-mapped I/O. There are no special instructions for I/O that are separate from those used for memory. This architecture also allows accessing an operand from an external memory location with no execution-time penalty.

#### 3.1 CPU Registers

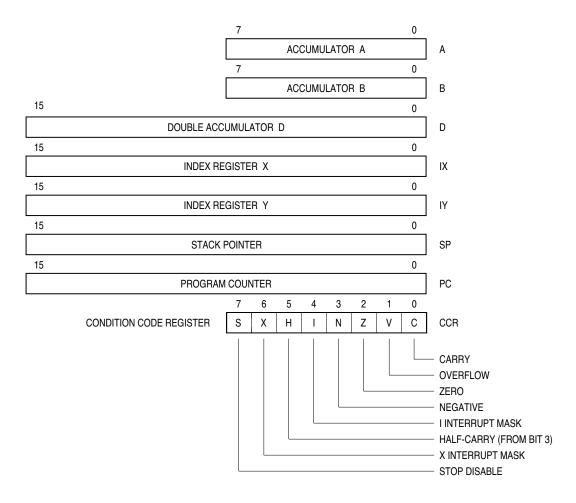

M68HC11 CPU registers are an integral part of the CPU and are not addressed as if they were memory locations. The seven registers, discussed in the following paragraphs, are shown in **Figure 3-1**.

Figure 3-1 Programming Model

#### 3.1.1 Accumulators A, B, and D

Accumulators A and B are general-purpose 8-bit registers that hold operands and results of arithmetic calculations or data manipulations. For some instructions, these two accumulators are treated as a single double-byte (16-bit) accumulator called accumulator D. Although most instructions can use accumulators A or B interchangeably, the following exceptions apply:

The ABX and ABY instructions add the contents of 8-bit accumulator B to the contents of 16-bit register X or Y, but there are no equivalent instructions that use A instead of B.

The TAP and TPA instructions transfer data from accumulator A to the condition code register, or from the condition code register to accumulator A, however, there are no equivalent instructions that use B rather than A.

The decimal adjust accumulator A (DAA) instruction is used after binary-coded decimal (BCD) arithmetic operations, but there is no equivalent BCD instruction to adjust accumulator B.

The add, subtract, and compare instructions associated with both A and B (ABA, SBA, and CBA) only operate in one direction, making it important to plan ahead to ensure that the correct operand is in the correct accumulator.

#### 3.1.2 Index Register X (IX)

The IX register provides a 16-bit indexing value that can be added to the 8-bit offset provided in an instruction to create an effective address. The IX register can also be used as a counter or as a temporary storage register.

#### 3.1.3 Index Register Y (IY)

The 16-bit IY register performs an indexed mode function similar to that of the IX register. However, most instructions using the IY register require an extra byte of machine code and an extra cycle of execution time because of the way the opcode map is implemented. Refer to **3.3 Opcodes and Operands** for further information.

#### 3.1.4 Stack Pointer (SP)

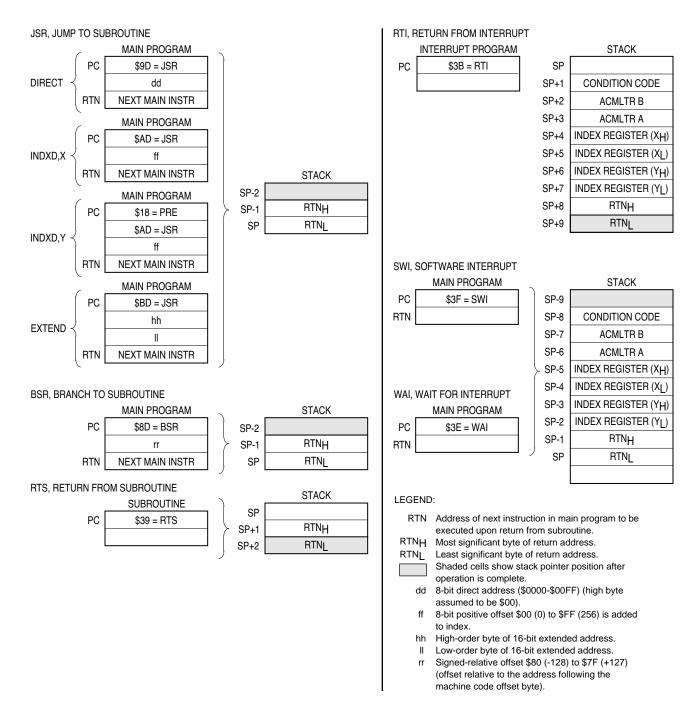

The M68HC11 CPU has an automatic program stack. This stack can be located anywhere in the address space and can be any size up to the amount of memory available in the system. Normally the SP is initialized by one of the first instructions in an application program. The stack is configured as a data structure that grows downward from high memory to low memory. Each time a new byte is pushed onto the stack, the SP is decremented. Each time a byte is pulled from the stack, the SP is incremented. At any given time, the SP holds the 16-bit address of the next free location in the stack. **Figure 3-2** is a summary of SP operations.

Figure 3-2 Stacking Operations

When a subroutine is called by a jump to subroutine (JSR) or branch to subroutine (BSR) instruction, the address of the instruction after the JSR or BSR is automatically pushed onto the stack, least significant byte first. When the subroutine is finished, a return from subroutine (RTS) instruction is executed. The RTS pulls the previously stacked return address from the stack, and loads it into the program counter. Execution then continues at this recovered return address.

MC68HC11F1 TECHNICAL DATA

When an interrupt is recognized, the current instruction finishes normally, the return address (the current value in the program counter) is pushed onto the stack, all of the CPU registers are pushed onto the stack, and execution continues at the address specified by the vector for the interrupt. At the end of the interrupt service routine, an RTI instruction is executed. The RTI instruction causes the saved registers to be pulled off the stack in reverse order. Program execution resumes at the return address.

There are instructions that push and pull the A and B accumulators and the X and Y index registers. These instructions are often used to preserve program context. For example, pushing accumulator A onto the stack when entering a subroutine that uses accumulator A, and then pulling accumulator A off the stack just before leaving the subroutine, ensures that the contents of a register will be the same after returning from the subroutine as it was before starting the subroutine.

#### 3.1.5 Program Counter (PC)

The program counter, a 16-bit register, contains the address of the next instruction to be executed. After reset, the program counter is initialized from one of six possible vectors, depending on operating mode and the cause of reset.

|              | POR or RESET Pin | Clock Monitor | COP Watchdog |

|--------------|------------------|---------------|--------------|

| Normal       | \$FFFE, F        | \$FFFC, D     | \$FFFA, B    |

| Test or Boot | \$BFFE, F        | \$BFFC, D     | \$BFFA, B    |

#### **Table 3-1 Reset Vector Comparison**

#### 3.1.6 Condition Code Register (CCR)

This 8-bit register contains five condition code indicators (C, V, Z, N, and H), two interrupt masking bits, (I and X) and a stop disable bit (S). In the M68HC11 CPU, condition codes are automatically updated by most instructions. For example, load accumulator A (LDAA) and store accumulator A (STAA) instructions automatically set or clear the N, Z, and V condition code flags. Pushes, pulls, add B to X (ABX), add B to Y (ABY), and transfer/exchange instructions do not affect the condition codes. Refer to **Table 3-2**, which shows what condition codes are affected by a particular instruction.

#### 3.1.6.1 Carry/Borrow (C)

The C bit is set if the arithmetic logic unit (ALU) performs a carry or borrow during an arithmetic operation. The C bit also acts as an error flag for multiply and divide operations. Shift and rotate instructions operate with and through the carry bit to facilitate multiple-word shift operations.

#### 3.1.6.2 Overflow (V)

The overflow bit is set if an operation causes an arithmetic overflow. Otherwise, the V bit is cleared.

#### 3.1.6.3 Zero (Z)

The Z bit is set if the result of an arithmetic, logic, or data manipulation operation is zero. Otherwise, the Z bit is cleared. Compare instructions do an internal implied subtraction and the condition codes, including Z, reflect the results of that subtraction. A few operations (INX, DEX, INY, and DEY) affect the Z bit and no other condition flags. For these operations, only = and - conditions can be determined.

#### 3.1.6.4 Negative (N)

The N bit is set if the result of an arithmetic, logic, or data manipulation operation is negative (MSB = 1). Otherwise, the N bit is cleared. A result is said to be negative if its most significant bit (MSB) is a one. A quick way to test whether the contents of a memory location has the MSB set is to load it into an accumulator and then check the status of the N bit.

#### 3.1.6.5 Interrupt Mask (I)

The interrupt request (IRQ) mask (I bit) is a global mask that disables all maskable interrupt sources. While the I bit is set, interrupts can become pending, but the operation of the CPU continues uninterrupted until the I bit is cleared. After any reset, the I bit is set by default and can only be cleared by a software instruction. When an interrupt is recognized, the I bit is set after the registers are stacked, but before the interrupt vector is fetched. After the interrupt has been serviced, a return from interrupt instruction is normally executed, restoring the registers to the values that were present before the interrupt occurred. Normally, the I bit is zero after a return from interrupt is executed. Although the I bit can be cleared within an interrupt service routine, "nesting" interrupts in this way should only be done when there is a clear understanding of latency and of the arbitration mechanism. Refer to **SECTION 5 RESETS AND INTERRUPTS**.

#### 3.1.6.6 Half Carry (H)

The H bit is set when a carry occurs between bits 3 and 4 of the arithmetic logic unit during an ADD, ABA, or ADC instruction. Otherwise, the H bit is cleared. Half carry is used during BCD operations.

#### 3.1.6.7 X Interrupt Mask (X)

The XIRQ mask (X) bit disables interrupts from the XIRQ pin. After any reset, X is set by default and must be cleared by a software instruction. When an XIRQ interrupt is recognized, the X and I bits are set after the registers are stacked, but before the interrupt vector is fetched. After the interrupt has been serviced, an RTI instruction is normally executed, causing the registers to be restored to the values that were present before the interrupt occurred. The X interrupt mask bit is set only by hardware (RESET or XIRQ acknowledge). X is cleared only by program instruction (TAP, where the associated bit of A is zero; or RTI, where bit 6 of the value loaded into the CCR from the stack has been cleared). There is no hardware action for clearing X.

#### 3.1.6.8 Stop Disable (S)

Setting the STOP disable (S) bit prevents the STOP instruction from putting the M68HC11 into a low-power stop condition. If the CPU encounters a STOP instruction while the S bit is set, it is treated as a no-operation (NOP) instruction, and processing continues to the next instruction. S is set by reset — STOP disabled by default.

#### 3.2 Data Types

The M68HC11 CPU supports the following data types:

- Bit data

- 8-bit and 16-bit signed and unsigned integers

- 16-bit unsigned fractions

- 16-bit addresses

A byte is eight bits wide and can be accessed at any byte location. A word is composed of two consecutive bytes with the most significant byte at the lower value address. Because the M68HC11 is an 8-bit CPU, there are no special requirements for alignment of instructions or operands.

#### 3.3 Opcodes and Operands

The M68HC11 family of microcontrollers uses 8-bit opcodes. Each opcode identifies a particular instruction and associated addressing mode to the CPU. Several opcodes are required to provide each instruction with a range of addressing capabilities. Only 256 opcodes would be available if the range of values were restricted to the number able to be expressed in 8-bit binary numbers.

A four-page opcode map has been implemented to expand the number of instructions. An additional byte, called a prebyte, directs the processor from page 0 of the opcode map to one of the other three pages. As its name implies, the additional byte precedes the opcode.

A complete instruction consists of a prebyte, if any, an opcode, and zero, one, two, or three operands. The operands contain information the CPU needs for executing the instruction. Complete instructions can be from one to five bytes long.

#### 3.4 Addressing Modes

Six addressing modes can be used to access memory: immediate, direct, extended, indexed, inherent, and relative. These modes are detailed in the following paragraphs. All modes except inherent mode use an effective address. The effective address is the memory address from which the argument is fetched or stored, or the address from which execution is to proceed. The effective address can be specified within an instruction, or it can be calculated.

#### 3.4.1 Immediate

In the immediate addressing mode an argument is contained in the byte(s) immediately following the opcode. The number of bytes following the opcode matches the size of the register or memory location being operated on. There are two-, three-, and four-

**CENTRAL PROCESSING UNIT**

(if prebyte is required) byte immediate instructions. The effective address is the address of the byte following the instruction.

#### 3.4.2 Direct

In the direct addressing mode, the low-order byte of the operand address is contained in a single byte following the opcode, and the high-order byte of the address is assumed to be \$00. Addresses \$00–\$FF are thus accessed directly, using two-byte instructions. Execution time is reduced by eliminating the additional memory access required for the high-order address byte. In most applications, this 256-byte area is reserved for frequently referenced data. In M68HC11 MCUs, the memory map can be configured for combinations of internal registers, RAM, or external memory to occupy these addresses.

#### 3.4.3 Extended

In the extended addressing mode, the effective address of the argument is contained in two bytes following the opcode byte. These are three-byte instructions (or four-byte instructions if a prebyte is required). One or two bytes are needed for the opcode and two for the effective address.

#### 3.4.4 Indexed

In the indexed addressing mode, an 8-bit unsigned offset contained in the instruction is added to the value contained in an index register (IX or IY). The sum is the effective address. This addressing mode allows referencing any memory location in the 64 Kbyte address space. These are two- to five-byte instructions, depending on whether or not a prebyte is required.

#### 3.4.5 Inherent

In the inherent addressing mode, all the information necessary to execute the instruction is contained in the opcode. Operations that use only the index registers or accumulators, as well as control instructions with no arguments, are included in this addressing mode. These are one- or two-byte instructions.

#### 3.4.6 Relative

The relative addressing mode is used only for branch instructions. If the branch condition is true, an 8-bit signed offset included in the instruction is added to the contents of the program counter to form the effective branch address. Otherwise, control proceeds to the next instruction. These are usually two-byte instructions.

#### 3.5 Instruction Set

Refer to **Table 3-2**, which shows all the M68HC11 instructions in all possible addressing modes. For each instruction, the table shows the operand construction, the number of machine code bytes, and execution time in CPU E clock cycles.

| Mnemonic   | Operation                  | Description                     |        | ressing        |    |          | struction      |        |   |   |          | onditio |   |          |          |   |

|------------|----------------------------|---------------------------------|--------|----------------|----|----------|----------------|--------|---|---|----------|---------|---|----------|----------|---|

|            |                            |                                 | N      | lode           | Ор | code     | Operand        | Cycles | S | Х | Н        | I       | Ν | Z        | V        | С |

| ABA        | Add<br>Accumulators        | $A + B \Rightarrow A$           |        | INH            |    | 1B       | -              | 2      | - | - | Δ        | _       | Δ | Δ        | Δ        | Δ |

| ABX        | Add B to X                 | $IX + (00 : B) \Rightarrow IX$  |        | INH            |    | ЗA       | —              | 3      | - | _ | _        | _       | - | _        | _        | — |

| ABY        | Add B to Y                 | $IY + (00 : B) \Rightarrow IY$  |        | INH            | 18 | ЗA       | —              | 4      | — | — | _        | —       | — | —        | —        | — |

| ADCA (opr) | Add with Carry             | $A + M + C \Rightarrow A$       | A      | IMM            |    | 89       | ii             | 2      | - | — | $\Delta$ | —       | Δ | $\Delta$ | $\Delta$ | Δ |

|            | to A                       |                                 | A      |                |    | 99<br>D0 | dd             | 3      |   |   |          |         |   |          |          |   |

|            |                            |                                 | A<br>A | EXT<br>IND,X   |    | B9<br>A9 | hh ll<br>ff    | 4      |   |   |          |         |   |          |          |   |

|            |                            |                                 | Â      | IND,Y          | 18 | A9       | ff             | 5      |   |   |          |         |   |          |          |   |

| ADCB (opr) | Add with Carry             | $B + M + C \Rightarrow B$       | В      | IMM            |    | C9       | ii             | 2      | _ | _ | Δ        | _       | Δ | Δ        | Δ        | Δ |

| (op)       | to B                       |                                 | В      | DIR            |    | D9       | dd             | 3      |   |   | -        |         | - | -        | -        | - |

|            |                            |                                 | В      | EXT            |    | F9       | hh ll          | 4      |   |   |          |         |   |          |          |   |

|            |                            |                                 | В      | IND,X          |    | E9       | ff             | 4      |   |   |          |         |   |          |          |   |

|            |                            |                                 | В      | IND,Y          | 18 | E9       | ff             | 5      |   |   |          |         |   |          |          |   |

| ADDA (opr) | Add Memory                 | $A + M \Rightarrow A$           | A      | IMM            |    | 8B       | ii<br>Jul      | 2      | - | — | Δ        | —       |   | Δ        | Δ        | Δ |

|            | to A                       |                                 | A      | DIR<br>EXT     |    | 9B<br>BB | dd<br>hh ll    | 3<br>4 |   |   |          |         |   |          |          |   |

|            |                            |                                 | A<br>A | IND,X          |    | AB       | ff             | 4      |   |   |          |         |   |          |          |   |

|            |                            |                                 | Â      | IND,Y          | 18 | AB       | ff             | 5      |   |   |          |         |   |          |          |   |

| ADDB (opr) | Add Memory                 | $B + M \Rightarrow B$           | В      | IMM            |    | CB       | ii             | 2      | _ | _ | Δ        | _       | Δ | Δ        | Δ        | Δ |

| (op)       | to B                       |                                 | В      | DIR            |    | DB       | dd             | 3      |   |   | -        |         | - | -        | -        | - |

|            |                            |                                 | В      | EXT            |    | FB       | hh ll          | 4      |   |   |          |         |   |          |          |   |

|            |                            |                                 | В      | IND,X          |    | EB       | ff             | 4      |   |   |          |         |   |          |          |   |

|            |                            |                                 | В      | IND,Y          | 18 | EB       | ff             | 5      |   |   |          |         |   |          |          |   |

| ADDD (opr) | Add 16-Bit to D            | $D + (M : M + 1) \Rightarrow D$ |        | IMM            |    | C3       | jj kk          | 4      | - | — | _        | _       | Δ | $\Delta$ | $\Delta$ | Δ |

|            |                            |                                 |        | DIR            |    | D3       | dd             | 5      |   |   |          |         |   |          |          |   |

|            |                            |                                 |        | EXT            |    | F3       | hh ll          | 6      |   |   |          |         |   |          |          |   |

|            |                            |                                 |        | IND,X<br>IND,Y | 18 | E3<br>E3 | ff<br>ff       | 6<br>7 |   |   |          |         |   |          |          |   |

|            | AND A with                 | $A \bullet M \Rightarrow A$     | ^      | IND, T         | 10 |          |                |        |   |   |          |         |   |          | 0        |   |

| ANDA (opr) | Memory                     | $A \bullet W \Rightarrow A$     | A<br>A | DIR            |    | 84<br>94 | ii<br>dd       | 2<br>3 | - | _ | _        | _       |   | $\Delta$ | 0        | _ |

|            | wentory                    |                                 | A      | EXT            |    | 94<br>B4 | hh II          | 4      |   |   |          |         |   |          |          |   |

|            |                            |                                 | A      | IND,X          |    | A4       | ff             | 4      |   |   |          |         |   |          |          |   |

|            |                            |                                 | A      | IND,Y          | 18 | A4       | ff             | 5      |   |   |          |         |   |          |          |   |

| ANDB (opr) | AND B with                 | $B \bullet M \Rightarrow B$     | В      | IMM            |    | C4       | ii             | 2      | _ | _ | _        | _       | Δ | Δ        | 0        | _ |

| ,          | Memory                     |                                 | В      | DIR            |    | D4       | dd             | 3      |   |   |          |         |   |          |          |   |

|            |                            |                                 | В      | EXT            |    | F4       | hh ll          | 4      |   |   |          |         |   |          |          |   |

|            |                            |                                 | В      | IND,X          | 10 | E4       | ff             | 4      |   |   |          |         |   |          |          |   |

|            | A 141 41                   |                                 | В      | IND,Y          | 18 | E4       | ff             | 5      |   |   |          |         |   |          |          |   |

| ASL (opr)  | Arithmetic                 | -                               |        | EXT            |    | 78       | hh II          | 6      | - | _ | _        | _       | Δ | Δ        | Δ        | Δ |

|            | Shift Left                 | <br>C b7 b0                     |        | IND,X<br>IND,Y | 18 | 68<br>68 | ff<br>ff       | 6<br>7 |   |   |          |         |   |          |          |   |

|            | A                          | <u>C D7 DU</u>                  | •      |                | 10 |          |                |        |   |   |          |         | - |          |          |   |

| ASLA       | Arithmetic<br>Shift Left A | -                               | A      | INH            |    | 48       | _              | 2      | - | _ | _        | _       |   | $\Delta$ | $\Delta$ | Δ |

|            | Shint Left A               | C b7 b0                         |        |                |    |          |                |        |   |   |          |         |   |          |          |   |

| ASLB       | Arithmetic                 | 0 07 00                         | В      | INH            |    | 58       |                | 2      |   |   |          |         | Δ | Δ        | Δ        | Δ |

| AGLD       | Shift Left B               |                                 | P      |                |    | 50       | _              | 2      | - |   | _        | _       |   | Δ        | Δ        | Δ |

|            | Onine Eone B               | C b7 b0                         |        |                |    |          |                |        |   |   |          |         |   |          |          |   |

| ASLD       | Arithmetic                 | 0 57 50                         |        | INH            |    | 05       | _              | 3      |   |   |          |         | Δ | Δ        | Δ        | Δ |

| AGED       | Shift Left D               | <del></del>                     |        |                |    | 05       |                | 5      |   |   |          |         |   | Δ        | Δ        | Δ |

|            | 0                          | C b7 A b0 b7 B b0               |        |                |    |          |                |        |   |   |          |         |   |          |          |   |

| ASR        | Arithmetic                 |                                 |        | EXT            |    | 77       | hh ll          | 6      | _ | _ | _        | _       | Δ | Δ        | Δ        | Δ |

|            | Shift Right                |                                 |        | IND,X          |    | 67       | ff             | 6      |   |   |          |         | - | -        | -        | - |

|            |                            | b7 b0 C                         |        | IND,Y          | 18 | 67       | ff             | 7      |   |   |          |         |   |          |          |   |

| ASRA       | Arithmetic                 |                                 | A      | INH            |    | 47       | _              | 2      | - | _ | _        | _       | Δ | Δ        | Δ        | Δ |

|            | Shift Right A              | ►►                              |        |                |    |          |                |        |   |   |          |         |   |          |          |   |