## for FIBRE CHANNEL Model: FXO-LC735RFC-212.5

LVDS 7 x 5mm 3.3V 50ppm XO Freq: 212.5MHz

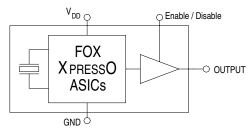

## **Features**

- Low Jitter

- Low Cost

- Tri-State Enable / Disable Feature

- Industry Standard Package

- Gold over Nickel Termination Finish

| Electrical Characteristics   |                                    |                            |                                        |

|------------------------------|------------------------------------|----------------------------|----------------------------------------|

| Parameters                   | Symbol                             | Condition                  | Maximum Value (unless otherwise noted) |

| Frequency                    | Fo                                 |                            | 212.5 MHz                              |

| Frequency Stability 1        |                                    |                            | 50 ppm                                 |

| Temperature Range            | T <sub>O</sub><br>T <sub>STG</sub> | Standard operating Storage | <i>-40℃ to</i> +85℃<br>-55°C to +125°C |

| Supply Voltage               | $V_{DD}$                           | Standard                   | 3.3V ± 5%                              |

| Input Current                | I <sub>DD</sub>                    | Standard Load              | 100 mA                                 |

| Output Load                  | Differential                       | Standard                   | 100 ohms Typ.                          |

| Start-Up Time                | Ts                                 |                            | 10 mS                                  |

| Output Enable / Disable Time |                                    |                            | 100 nS                                 |

| Moisture Sensitivity Level   | MSL                                |                            | 1                                      |

| Termination Finish           |                                    |                            | Au                                     |

Note 1 – Stability is inclusive of 25°C tolerance, operating temperature range, input voltage change, load change, aging, shock and vibration.

| Output Wave Characteristics     |                 |                  |                                        |

|---------------------------------|-----------------|------------------|----------------------------------------|

| Parameters                      | Symbol          | Condition        | Maximum Value (unless otherwise noted) |

| Differential Output Voltage     | $V_{OD}$        | Standard Load    | 0.6V Typ.                              |

| Output Offset Voltage           | V <sub>OS</sub> | Standard Load    | 1.3V Typ.                              |

| Output Symmetry                 |                 | @ 50% Vp-p Level | 45% ~ 55%                              |

| Output Enable (PIN # 1) Voltage | V <sub>IH</sub> |                  | ≥70% V <sub>DD</sub>                   |

| Output Disable (PIN#1) Voltage  | V <sub>IL</sub> |                  | ≤ 30% V <sub>DD</sub>                  |

| Cycle Rise Time                 | T <sub>R</sub>  | 20% ~ 80% Vp-p   | 400 pS                                 |

| Cycle Fall Time                 | $T_F$           | 80% ~ 20% Vp-p   | 400 pS                                 |

DWG-100748 Rev. 07/13/2010

## for FIBRE CHANNEL Model: FXO-LC735RFC-212.5

LVDS 7 x 5mm 3.3V 50ppm XO Freq: 212.5MHz

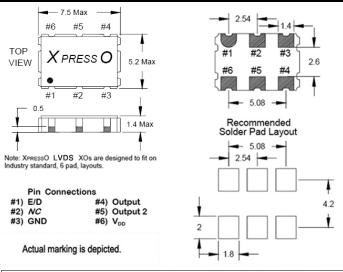

## **Dimensional Drawing & Pad Layout**

Drawing is for reference to critical specifications defined by size measurements. Certain non-critical visual attributes, such as side castellations, reference pin shape, etc. may vary

| Phase Jitter & Time Interval Error (TIE) (Typical Measurements) |              |                                              |        |

|-----------------------------------------------------------------|--------------|----------------------------------------------|--------|

| Frequency                                                       | Phase Jitter | <b>TIE</b><br>(Sigma of Jitter Distribution) | Units  |

| 212.5 MHz                                                       | 0.89         | 3.9                                          | pS RMS |

<u>Phase Jitter</u> is integrated from HP3048 Phase Noise Measurement System; measured directly into 50 ohm input;  $V_{DD} = 3.3V$ . <u>TIE</u> was measured on LeCroy LC684 Digital Storage Scope, directly into 50 ohm input, with Amherst M1 software;  $V_{DD} = 3.3V$ . Per **MJSQ** spec (Methodologies for Jitter and Signal Quality specifications)

| Random & Deterministic Jitter Composition (Typical Measurements) |             |                    |                                            |

|------------------------------------------------------------------|-------------|--------------------|--------------------------------------------|

| Frequency                                                        | Random (Rj) | Deterministic (Dj) | <b>Total Jitter (Tj)</b><br>(14 x Rj) + Dj |

| 212.5 MHz                                                        | 0.9         | 6.7                | 18.7 pS                                    |

**Rj and Dj**, measured on LeCroy LC684 Digital Storage Scope, directly into 50 ohm input, with Amherst M1 software. *Per MJSQ* spec (Methodologies for Jitter and Signal Quality specifications)

| Pin I | Pin Functional Description                                                                                                                        |        |                                                   |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------|--|

| Pin#  | Name                                                                                                                                              | Type   | Function                                          |  |

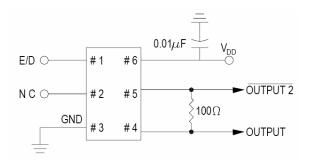

| 1     | E/D <sup>1</sup>                                                                                                                                  | Logic  | Enable / Disable Control of Output (0 = Disabled) |  |

| 2     | NC                                                                                                                                                |        | No Connection – Leave Open                        |  |

| 3     | GND                                                                                                                                               | Ground | Electrical Ground for V <sub>DD</sub>             |  |

| 4     | Output                                                                                                                                            | Output | LVDS Oscillator Output                            |  |

| 5     | Output 2                                                                                                                                          | Output | Complementary LVDS Output                         |  |

| 6     | V <sub>DD</sub> <sup>2</sup>                                                                                                                      | Power  | Power Supply Source Voltage                       |  |

| NOTES | NOTES: 1 Includes pull-up resistor to V <sub>DD</sub> to provide output when the pin (1) is No Connect.                                           |        |                                                   |  |

|       | Installation should include a 0.01μF bypass capacitor placed between V <sub>DD</sub> (Pin 6) and GND (Pin 3) to minimize power supply line noise. |        |                                                   |  |