For Ethernet over Coax Applications

#### **FEATURES**

- Based on Atheros' INT6400/INT1400 chipset

- Based on HomePlug® AV standard optimised for Ethernet over Coax (EoC) applications with raw data rates up to 200 MB/s

- Temperature rated for industrial applications

- MII (Host & PHY) interface

- Supports1024/256/64/16/8-QAM, QPSK, BPSK, and ROBO modulation schemes

- 128-bit AES Link Encryption with key management for secure power line communications

- Dynamic channel adaptation and channel estimation maximizes throughput in harsh channel conditions

- Advanced turbo code forward error correction

- ToS, CoS and IP port number packet classifiers

- Supports IGMP managed multicast sessions

- Green standard (ROHS) compliant

- GPIO second function as general data lines

- Horizontal mounting configuration using standard

1.27mm pin header

- Integrates all components necessary to add

Ethernet over Coax functionality to any embedded system at low cost

### **APPLICATIONS**

- Over-the-Top Video

- Telco / IPTV

- Ethernet over Coax (EoC) and

Multi-Dwelling Unit (MDU) applications

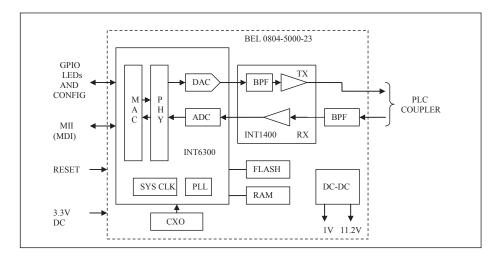

## **MODULE BLOCK DIAGRAM**

For Ethernet over Coax Applications

|     | TABLE OF CONTENTS                                  | Page |  |  |

|-----|----------------------------------------------------|------|--|--|

| 1.  | PRESENTATION                                       | 3    |  |  |

| 2.  | 2. MODULE INTERFACE                                |      |  |  |

| 2.1 | Pin I/O Table                                      | 3    |  |  |

| 2.2 | Media Independent Interface (MII)                  | 4    |  |  |

|     | 2.2.1 MII MAC                                      | 4    |  |  |

|     | 2.2.2 MII PHY                                      | 4    |  |  |

|     | 2.2.3 MII Signals                                  | 5    |  |  |

| 2.3 | MII Management Data Interface (MDI)                | 6    |  |  |

| 2.4 | General Purpose Input/Output (GPIO) Pins Interface | 6    |  |  |

| 2.5 | PHY Utility Interface                              | 7    |  |  |

| 2.6 | Coupling Interface                                 | 8    |  |  |

| 2.7 | 2.7 Reset Interface                                |      |  |  |

| 2.8 | 2.8 Power Interface                                |      |  |  |

| 2.9 | Reserved Pins                                      | 8    |  |  |

| 3.  | CONFIGURATION OPTIONS                              | 9    |  |  |

| 3.1 | MII Options                                        | 9    |  |  |

| 3.2 | Boot Options                                       | 9    |  |  |

| 4.  | FIRMWARE                                           | 9    |  |  |

| 5.  | ELECTRICAL CHARACTERISTICS                         | 10   |  |  |

| 6.  | MECHANICAL DRAWING                                 | 10   |  |  |

For Ethernet over Coax Applications

### 1. PRESENTATION

The Bel 0804-5000-23 single in line package (SIP) module is an industrial temperature rated MAC/PHY/AFE Powerline communications (PLC) transceiver. The module complements the existing range of Bel Powerline modules based on the Atheros INT6400/INT1400 and is optimised for communications over coax networks.

The Bel 0804-5000-23 module enables the development of HD grade communications bridges to and from the coax network. It also serves as a translator between the digital and analogue worlds. On the digital side host interfaces include Ethernet MII Host or PHY. The data received and transmitted is translated by the INT6400 to and from a complex analogue signal which is modulated on multiple carriers and transmitted over the coax network.

### 2. MODULE INTERFACE

#### 2.1 Pin I/O Table

| Pin Number | Pin Name       | Pin Number | Pin Name       |

|------------|----------------|------------|----------------|

| 1          | VDD            | 26         | MDC            |

| 2          | VSS            | 27         | Do not connect |

| 3          | VDD            | 28         | Do not connect |

| 4          | VSS            | 29         | VSS            |

| 5          | VDD            | 30         | MRX_D0         |

| 6          | TX+            | 31         | MRX_D1         |

| 7          | TX-            | 32         | MRX_D2         |

| 8          | VSS            | 33         | MRX_D3         |

| 9          | RX+            | 34         | COL            |

| 10         | RX-            | 35         | MRX_CLK        |

| 11         | RESET/         | 36         | vss            |

| 12         | GPIO0          | 37         | MRX_ERR        |

| 13         | GPIO1          | 38         | MRX_DV         |

| 14         | GPIO2          | 39         | MTX_D0         |

| 15         | GPIO3          | 40         | MTX_D1         |

| 16         | GPIO4          | 41         | MTX_D2         |

| 17         | GPIO5          | 42         | MTX_D3         |

| 18         | GPIO6          | 43         | CRS            |

| 19         | GPIO7          | 44         | MTX_CLK        |

| 20         | GPIO8          | 45         | MTX_EN         |

| 21         | GPIO9          | 46         | vss            |

| 22         | GPIO10         | 47         | PHY_RST/       |

| 23         | GPIO11         | 48         | VSS            |

| 24         | Do not connect | 49         | PHY_CLK        |

| 25         | MDIO           | 50         | VSS            |

For Ethernet over Coax Applications

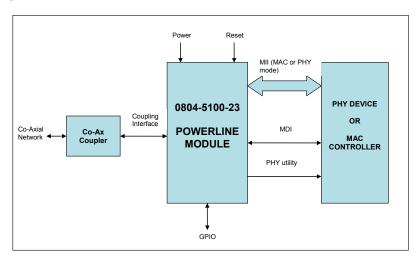

#### SYSTEM BLOCK DIAGRAM

The block diagram presents the 0804-5000-23 powerline module in a typical environment. Seven different types of interfaces are observed. These interfaces are described in details below.

## 2.2 Media Independent Interface (MII)

The MII interface is configured as either an Ethernet Medium Access Controller (MAC) or a Physical Medium Dependent (PMD or PHY) controller. Medium Independent Interface (MII) is an industry standard, multi-vendor interface between the MAC and PHY sub-layers. It provides a simple connection between Ethernet PHY controllers and IEEE802.3 Ethernet MACs from a variety of sources.

MII consists of separate 4-bit data paths for transmit and receive data along with carrier sense and collision detection. Further details of the MII are available from the IEEE 802.3u Standard.

Configuration straps described in Section 3 set the MII operation to a MAC or PHY controller. The MAC and PHY configurations support 10 Mbps or 100 Mbps in half-duplex or full-duplex modes and flow control for half-duplex and full-duplex connections. The Ethernet MAC module implements standard Ethernet MAC functionality. The Ethernet MAC is connected to an external Ethernet PHY function. The MAC configuration provides bridging between Ethernet and the powerline. The PHY configuration emulates Ethernet PHY functionality and provides HomePlug AV connectivity to devices designed to communicate over an Ethernet network.

The MII (Ethernet) interface has separate transmit and receive packet buffering. When operating as a MAC the MII transmit FIFO is 2 KB and the receive FIFO is 8 KB. When operating as a PHY controller, the MII transmit FIFO is 8 KB and the receive FIFO is 2 KB.

## 2.2.1 MII MAC

The MII MAC configuration operates as an IEEE 802.3 10/100-Mbps Ethernet MAC connected to an external 10/100-Mbps Ethernet PHY. The INT6400 MAC firmware configures the internal MII MAC based on firmware configuration and MMEs (message management entry). External devices do not have direct access to any MII MAC registers in the INT6400.

### 2.2.2 MII PHY

The MII PHY emulation hardware connects to an external 10/100-Mbps Ethernet MAC. The default PHY functionality is configured through standard management data interface communications (MDI interface) and may be overridden by the INT6400 MAC firmware access to the PHY emulation registers. The interface supports the standard control and status register.

- Link speed at 10 Mbps or 100 Mbps

- · Full-duplex or half-duplex operation

- Management data interface base address

- Isolate to disconnect the PHY from the MII port

For Ethernet over Coax Applications

# 2.2.3 MII Signals

| <u>.</u>             |                                      | I/          | 0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|----------------------|--------------------------------------|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin<br>Number        | Pin Name                             | MAC<br>Mode | PHY<br>Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 30<br>31<br>32<br>33 | MRX_D0<br>MRX_D1<br>MRX_D2<br>MRX_D3 | ı           | 0           | MII Receive Data. The PHY controller drives MRX_D[3:0] and the MAC core receives MRX_D[3:0]. MRX_D[3:0] transition synchronously with respect to MRX_CLK. For each MRX_CLK period in which MRX_DV is asserted, MRX_D[3:0] is valid. MRX_D0 is the least-significant bit. The PHY controller tri-states MRX_D[3:0] in isolate mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 34                   | COL                                  | I           | 0           | MII Collision Detected. The PHY controller asserts COL when it detects a collision on the medium. COL remains asserted while the collision condition persists. COL signal transitions are not synchronous to either the MTX_CLK or the MRX_CLK. The MAC core ignores the COL signal when operating in the full-duplex mode. The PHY controller tristates COL in isolate mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 35                   | MRX_CLK                              | I           | 0           | MII Receive Clock. MRX_CLK is a continuous clock that provides the timing reference for the transfer of the MRX_DV and MRX_D[3:0] signals from the PHY controller to the MAC core. The PHY controller sources MRX_CLK. MRX_CLK frequency is equal to 25% of the data rate of the received signal on the Ethernet cable. The PHY controller tri-states MRX_CLK in isolate mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 37                   | MRX_ERR                              | I           | 0           | MII Receive Error. The PHY controller asserts MRX_ERR high for one or more MRX_CLK periods to indicate to the MAC core that an error (a coding error or any error that the PHY is capable of detecting that is otherwise undetectable by the MAC) was detected somewhere in the current frame. MRX_ERR transitions ynchronously with respect to MRX_CLK. While MRX_DV is de-asserted, MRX_ERR has no effect on the MAC core. The PHY controller tri-states MRX_ERR in isolate mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 38                   | MRX_DV                               | ı           | 0           | MII Receive Data Valid. The PHY controller asserts MRX_DV to indicate to the MAC core that it is presenting the recovered and decoded data bits on MRX_D[3:0] and that the data on MRX_D[3:0] is synchronous to MRX_CLK. MRX_DV transitions synchronously with respect to MRX_CLK. MRX_DV remains asserted continuously from the first recovered nibble of the frame through the final recovered nibble, and is de-asserted prior to the first MRX_CLK that follows the final nibble. The PHY controller tri-states MRX_DV in isolate mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 39<br>40<br>41<br>42 | MTX_D0<br>MTX_D1<br>MTX_D2<br>MTX_D3 | 0           | I           | MII Transmit Data. The MAC core drives MTX_D[3:0] and the PHY controller receives MTX_D[3:0]. MTX_D[3:0] transitions synchronously with respect to MTX_CLK. For each MTX_CLK period in which MTX_EN is asserted, MTX_D[3:0] is valid. MTX_D0 is the least significant bit. The PHY controller ignores MTX_D[3:0] in isolate mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 43                   | CRS                                  | ı           | 0           | MII Carrier Sense. The PHY controller asserts CRS when either transmit or receive medium is non-idle. The PHY de-asserts CRS when both transmit and receive medium are idle. The PHY must ensure that CRS remains asserted throughout the duration of a collision condition. The transitions on the CRS signal are not synchronous to either the MTX_CLK or the MRX_CLK. The PHY controller tri-states CRS in isolate mode.  MII Transmit Clock. MTX_CLK is a continuous clock that provides a timing reference for the transfer of the MTX_EN and MTX_D[3:0] signals from the MAC core to the PHY controller. The PHY controller sources MTX_CLK. The operating frequency of MTX_CLK is 25 MHz when operating at 100 Mbps and 2.5 MHz when operating at 10 Mbps. The PHY controller tri-states MTX_CLK in isolate mode.  MII Transmit Enable. A high assertion on MTX_EN indicates that the MAC core is presenting nibbles to the PHY controller for transmission. The INT6400 MAC core asserts MTX_EN with the first nibble of the preamble and keeps MTX_EN asserted while all nibbles to be transmitted are presented to the MII. MTX_EN is de-asserted prior to the first MTX_CLK following the final nibble of the frame. MTX_EN transitions synchronously with respect to MTX_CLK. The PHY controller ignores MTX_EN in isolate mode. |  |

| 44                   | MTX_CLK                              | I           | 0           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 45                   | MTX_EN                               | 0           | I           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

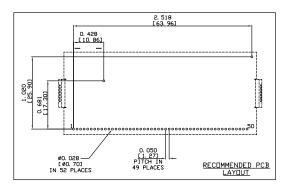

Special care must be taken during PCB layout of the MII bus. Keep MII signal traces as short as possible and preferably on inner PCB layers.

**For Ethernet over Coax Applications**

## 2.3 MII Management Data Interface (MDI)

The MII interface has a two-wires bi-directional serial Management Data Interface (MDI). This interface provides access to the status and control registers in the Ethernet PHY logic. The MII and MDI pins are shared between the MAC and PHY interfaces.

| · ·        | Pin Name | I/O      |          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|------------|----------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Number |          | MAC Mode | PHY Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 25         | MDIO     | I/O      | I/O      | MII Management Data In/Out. This is the data input signal from the PHY controller. The PHY drives the Read Data synchronously with respect to the MDC clock during the read cycles. This is also the data output signal from the MAC core that drives the control information during the Read/Write cycles to the PHY controller. The MAC core drives the MDO signal synchronously with respect to the MDC. An external pull-up resistor is needed on this pin. |  |

| 26         | MDC      | 0        | I        | MII Management Data Clock. The MAC core sources MDC as the timing reference for transfer of information on the MDIO signal. MDC signal has no maximum high or low times. MDC minimum high and low times are 160 ns each, and the minimum period for MDC is 400 ns.                                                                                                                                                                                              |  |

## 2.4 General Purpose Input/Output (GPIO) Pins Interface

General Purpose I/O pins are software programmable inputs or outputs, which can also be used as an external interrupt source. As indicated in the table below, some of these GPIO signals also have additional functionality as configuration straps. See section 3 for configuration options.

| Pin Number | Pin Name | Configuration Strap<br>Function | I/O* | Internal Pull Up/Down |

|------------|----------|---------------------------------|------|-----------------------|

| 12         | GPIO0    | N/A                             | S.C. | Up                    |

| 13         | GPIO1    | N/A                             | S.C. | Up                    |

| 14         | GPIO2    | N/A                             | S.C. | Up                    |

| 15         | GPIO3    | ISODEF                          | S.C. | Up                    |

| 16         | GPIO4    | SPEED                           | S.C. | Up                    |

| 17         | GPIO5    | MD_A3                           | S.C. | Up                    |

| 18         | GPIO6    | CFG_SEL                         | S.C. | Down                  |

| 19         | GPIO7    | MD_A4                           | S.C. | Down                  |

| 20         | GPIO8    | MP_SEL                          | S.C. | Up                    |

| 21         | GPIO9    | N/A                             | S.C. | Down                  |

| 22         | GPIO10   | BM_SEL                          | S.C. | Down                  |

| 23         | GPIO11   | N/A                             | S.C. | Down                  |

<sup>\*</sup> S. C. = software configurable.

For Ethernet over Coax Applications

In addition to their configuration strap function, the GPIOs can perform some software configurable functions after reset. The default configuration provided by Bel Fuse is as below:

| GPIO                               | I/O | Default Function After Reset                                                                                                                                                           |  |  |

|------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GPIO0                              | 0   | Not Used (HiZ)                                                                                                                                                                         |  |  |

| GPIO1                              | I   | Typically connected to a push-button. This GPIO is used to add a new device to, or remove an old device from, a HomePlug AC logical network. Contact BelFuse for further information.  |  |  |

| GPIO2                              | I   | Typically connected to a push-button. The factory default PIB can be restored by applying a low-level digital voltage on GPIO2 for greater than 0.5 seconds and less than 3.0 seconds. |  |  |

| GPIO [37]                          | 0   | Not Used (HiZ)                                                                                                                                                                         |  |  |

| GPIO8 On: Powerline link detected. |     | Flash: TX or RX powerline activity (if the INT6400 is serving as a Station).                                                                                                           |  |  |

| GPIO9                              | 0   | To be connected to an LED. The LED gives indications about Ethernet Link & activity.  On: Ethernet link detected.  Flash: Transmit or receive activity.  Off: No link detected.        |  |  |

| GPIO10                             | 0   | To be connected to an LED. The LED gives indications about Power line mode. On: N/A. Flash: HomePlug 1.0 traffic detected. Off: Silence.                                               |  |  |

| GPIO11                             | 0   | To be connected to an LED. The LED gives indication about Power. On: Power ready. Flash: Load firmware. Off: Power not ready.                                                          |  |  |

# 2.5 PHY Utility Interface

| Pin Number | Pin Name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47         | PHY_RST/ | 0   | PHY device Reset (active low). Connect to an external Ethernet PHY. This reset output is a stretched version of the RESET/ input.                                                                                                                                                                                                                                                                 |

| 49         | PHY_CLK  | 0   | 25MHz Clock Out. This output is a dedicated clock output that can be used to drive the clock input on an external Ethernet PHY. This clock output is only available when the INT6400 is configured in MAC mode, and not in PHY mode of operation. Note that if this output is used, it is strongly advised that the corresponding PHY_RST/ signal also be connected to the external Ethernet PHY. |

For Ethernet over Coax Applications

# 2.6 Coupling Interface

| Pin Number | Pin Name | I/O Description |                                                                      |

|------------|----------|-----------------|----------------------------------------------------------------------|

| 6          | TX+      | 0               | Differential TX Line Driver output, connects to coupling transformer |

| 7          | TX-      | 0               | Differential TX Line Driver output, connects to coupling transformer |

| 9          | RX+      | I               | Differential RX Line Filter input, connects to coupling transformer  |

| 10         | RX-      | I               | Differential RX Line Filter input, connects to coupling transformer  |

Special care must be taken during PCB layout of the coupling interface signals.

Route differential pairs close together and away from all other signals. Route each differential pair on the same PCB layer. Keep both traces of each differential pair as identical to each other as possible.

Wide copper is needed here to support current density of up to 30MHz. These high frequencies result in higher resistance due to skin effect. The wide traces also accommodate high transient currents caused by voltage spikes. Trace widths between the Module and the coupling transformer must be no less than 0.020" (0.5 mm) and should be no greater than 0.030" (0.75 mm). Use of the Bel Fuse 0557-7700-43 powerline coupler is recommended. Details can be found in its associated datasheet.

#### 2.7 Reset Interface

| Pin Number | Pin Name | I/O | Description                                                                                        |

|------------|----------|-----|----------------------------------------------------------------------------------------------------|

| 11         | RESET/   | I   | Resets all IC logic when low. Maintain this signal active for 100 ms after the VDD rail is stable. |

### 2.8 Power Interface

| Pin Number                     | Pin Name | I/O | Description               |

|--------------------------------|----------|-----|---------------------------|

| 1, 3, 5                        | VDD      | I   | +3.3V with respect to VSS |

| 2, 4, 8, 29, 36,<br>46, 48, 50 | VSS      | I   | Ground                    |

#### 2.9 Reserved Pins

| ĺ | Pin Number | Description                                                                  |

|---|------------|------------------------------------------------------------------------------|

| - | 24, 27, 28 | Internally connected and reserved for future use. Do not connect externally. |

### 3. CONFIGURATION OPTIONS

The INT6400 MII and boot options are selected by the initial condition of GPIO pins. If a GPIO pin is not used and its internal strapping resistor sets the booting option correctly, then the pin may be left unconnected. If a GPIO pin is not used but the internal strapping resistor sets the booting option incorrectly, then the pin must be pulled high or low to the correct booting option by an external resistor. This resistor can be 10 k-Ohms down to a few hundred Ohms. 3.3 k-Ohms is typical. Many GPIO pins are driven by firmware for LED output immediately after boot up so connecting these GPIO directly to ground or VDD is not permitted.

| Pin Number | Pin Name | Strap Function | Internal Pull Up/Down | Default Function                 |

|------------|----------|----------------|-----------------------|----------------------------------|

| 15         | GPIO3    | ISODEF         | Up                    | PHY MODE: Hi-Z MII interface     |

| 16         | GPIO4    | SPEED          | Up                    | PHY MODE: 100Mbps                |

| 17         | GPIO5    | MD_A3          | Up                    | PHY MODE: PHY Address 0x0100     |

| 18         | GPIO6    | CFG_SEL        | Down                  | BOOT: SDRAM parameters from Host |

| 19         | GPIO7    | MD_A4          | Down                  | PHY MODE: PHY address 0x0100     |

| 20         | GPIO8    | MP_SEL         | Up                    | HOST: MAC mode                   |

| 22         | GPIO10   | BM_SEL         | Down                  | BOOT:Firmware From Host          |

| 49         | PHY_CLK  | DUPLEX         | Up                    | PHY MODE: Full Duplex            |

For Ethernet over Coax Applications

### 3.1 MII Options

The MP\_SEL strap is used to specify whether the INT6400 chip is configured for MII MAC mode, or in MII PHY mode (i.e. reverse-MII mode). The encoding of this signal is table 11:

| MP_SEL | Mode            |  |

|--------|-----------------|--|

| 0      | MII in PHY mode |  |

| 1      | MII in MAC mode |  |

In MII PHY mode, there are 5 additional configuration straps that are unique to this mode of operation.

| SPEED | MII Speed |  |

|-------|-----------|--|

| 0     | 10 Mbps   |  |

| 1     | 100 Mbps  |  |

| ISODEF | Isolation        |  |

|--------|------------------|--|

| 0      | Normal Operation |  |

| 1      | Isolated         |  |

| DUPLEX | MII Duplex  |  |

|--------|-------------|--|

| 0      | Half Duplex |  |

| 1      | Full Duplex |  |

| MD_A [3,4] | MII Management Address |  |  |

|------------|------------------------|--|--|

| 00         | 0x00                   |  |  |

| 01         | 0x08                   |  |  |

| 10         | 0x10                   |  |  |

| 11         | 0x18                   |  |  |

### 3.2 Boot Options

The BM\_SEL strap is used to determine the source of the boot code for the embedded ARM processor. Similarly, the CFG\_ SEL strap is used to determine the source of the SDRAM configuration applet. The encodings for these two signals is shown in the following table.

| BM_SEL | CFG_SEL | Meaning                                                                                |  |  |

|--------|---------|----------------------------------------------------------------------------------------|--|--|

| 0      | 0       | Load SDRAM configuration and boot code from external host                              |  |  |

| 0      | 1       | Load SDRAM configuration applet from Flash, and then load boot code from external host |  |  |

| 1      | 0       | Not supported                                                                          |  |  |

| 1      | 1       | Load SDRAM configuration and boot code from Flash                                      |  |  |

### 4. FIRMWARE

The 0804-5000-23 powerline modules are supplied programmed with the most recent firmware versions and default Parameter Information Block (PIB) for EoC from Atheros. The PIB contains the parameters used to configure the operation of the INT6400 chipset, including:

- Network Management Key (NMK)

- MAC address

- Device Access Key (DAK)

- GPIO function after reset

This factory default PIB can be superseded by a customized User PIB using the Atheros' Avitar PC-based application. A non disclosure agreement is required with Atheros to access this tool.

**For Ethernet over Coax Applications**

### **ELECTRICAL CHARACTERISTICS**

| Symbol          | Parameter                     | Test Conditions                                | Min | Max | Units |

|-----------------|-------------------------------|------------------------------------------------|-----|-----|-------|

| VDD             | Supply voltage (1)            |                                                | 3.0 | 3.6 | V     |

| V <sub>IL</sub> | Low-level input voltage       |                                                |     | 0.8 | V     |

| V <sub>IH</sub> | High-level input voltage      |                                                | 2.0 |     | V     |

| V <sub>OL</sub> | Low-level output voltage      | I <sub>OL</sub> = 4 mA, 12 mA <sup>(2)</sup>   |     | 0.4 | V     |

| V <sub>OH</sub> | High-level output voltage     | I <sub>OH</sub> = -4 mA, -12 mA <sup>(3)</sup> | 2.4 |     | V     |

| I <sub>IL</sub> | Low-level input current       | V <sub>I</sub> = Gnd                           | -1  |     | μΑ    |

| I <sub>IH</sub> | High-level input current      | V <sub>I</sub> = 3.3 V                         |     | 1   | μΑ    |

| l <sub>OZ</sub> | High-impedance output current | Gnd < V <sub>I</sub> < 3.3 V                   | -1  | +1  | μΑ    |

| T <sub>op</sub> | Operating temperature range   |                                                | -40 | +85 | °C    |

- A typical supply current, assuming a nominal operation of 50% transmit and 50% receive duty cycle, is 580 mA.

- $I_{OL}$ =12 mA for all GPIOs.  $I_{OL}$  = 4 mA for all other digital interfaces.  $I_{OH}$  = -12 mA for all GPIOs.  $I_{OH}$  = -4 mA for all other digital interfaces.

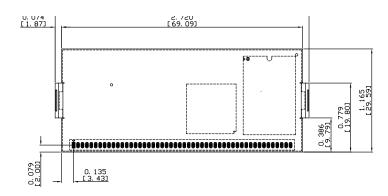

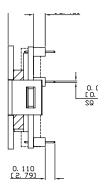

### **MECHANICAL**

## 0804-5000-23 **Horizontal Mount**

©2011 Bel Fuse Inc. Specifications subject to change without notice. 03.03.11 Atheros, PowerPacket, SIMPLE and SIMPLE PowerBus are registered trademarks of Atheros Corportation.

## **CORPORATE**

Bel Fuse Inc. 206 Van Vorst Street Jersey City, NJ 07302 Tel 201-432-0463 Fax 201-432-9542 www.belfuse.com

## **ASIA**

Bel Fuse Ltd. 8F / 8 Luk Hop Street San Po Kong Kowloon, Hong Kong Tel 852-2328-5515 Fax 852-2352-3706 www.belfuse.com

### **EUROPE**

**Bel Stewart Connector** 45/46 Riverside Medway City Estate Rochester, Kent ME2 4DP U.K. Tel 44-1634-722890 Fax 44-1634-716677 www.belfuse.com