### AS1504, AS1505

**Data Sheet**

# Octal 8-Bit Programmable Low-Power DACs with Shutdown and Mid-Scale Reset

### 1 General Description

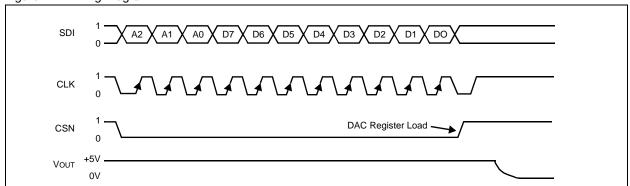

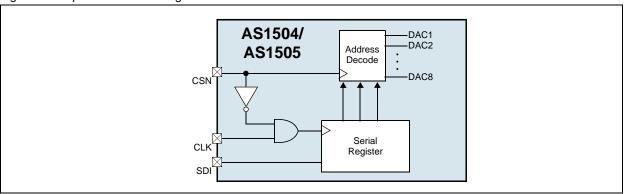

The AS1504/AS1505 are low-power ( $5\mu A @ 5V$ ) individually programmable 8-channel, 8-bit resolution digital-to-analog converters. All eight DACs share a common reference-voltage input making them ideal for applications where adjustments start at a nominal voltage.

Table 1. Standard Products

| Model  | Functionality                 |  |  |  |

|--------|-------------------------------|--|--|--|

| AS1504 | Mid-Scale Reset Pin           |  |  |  |

| AS1505 | Separate VREFL Range Settings |  |  |  |

The devices feature a low-power shutdown reference input current (5µA) that enables the devices to maintain individual DAC latch settings during shutdown until normal operation is resumed.

The devices are controlled via a standard 3-wire serial interface. Data is shifted into the DACs via the internal serial-to-parallel shift register.

The AS1504/AS1505 are available in a 16-pin SOIC-150 package.

### 2 Key Features

- 8 Individually-Controlled DACs

- Replaces 8 Potentiometers

- Standard 3-Wire Serial Interface

- Single-Supply Operation: +3 to +5V

- Mid-Scale Reset Pin (AS1504)

- Separate VREFL Range Setting (AS1505)

- Shutdown Mode: ≤25µW (IDD and IREF)

- Power-On Reset

- 16-pin SOIC-150 Package

### 3 Applications

The devices are ideal for video amplifier gain control, video equipment voltage-controlled frequencies and bandwidths, CRT display geometric corrections and automatic adjustments, or any other space-limited DAC application with low power-consumption requirements.

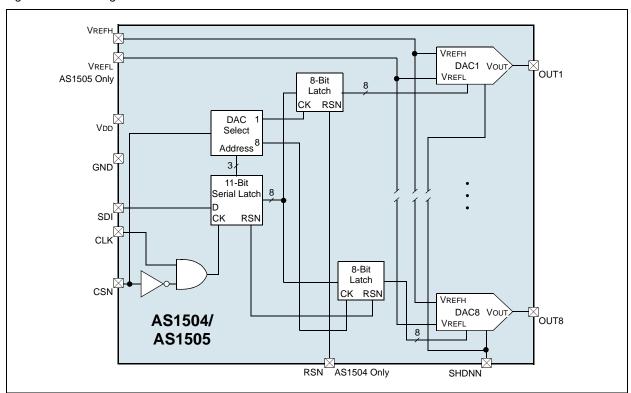

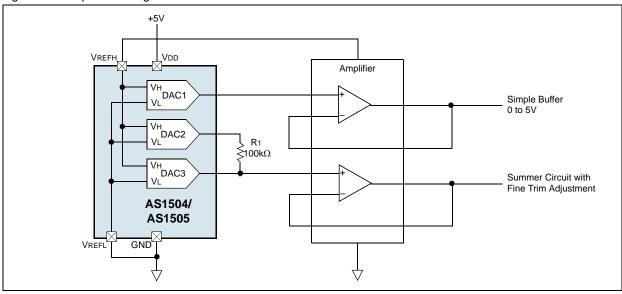

Figure 1. Block Diagram

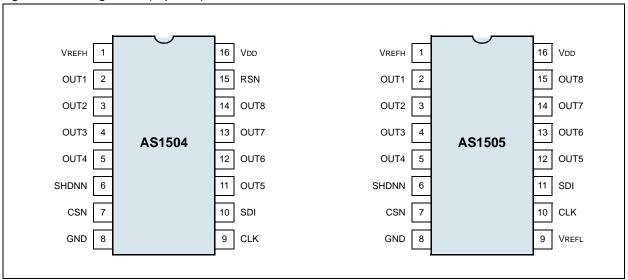

### 4 Pinout

### **Pin Assignments**

Figure 2. Pin Assignments (Top View)

### **Pin Descriptions**

Table 2. Pin Descriptions

| Pin Number     | Pin Name | Description                                                                                                                                                           |  |  |  |  |  |

|----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                | CLK      | Serial Clock Input. Positive-edge triggered.                                                                                                                          |  |  |  |  |  |

|                | CSN      | <b>Chip Select</b> . When this active-low pin goes high, the serial input register data is decoded based on the address bits and loaded into the target DAC register. |  |  |  |  |  |

|                | GND      | Ground                                                                                                                                                                |  |  |  |  |  |

|                | OUT1     | DAC 1 Output. DAC 1 address = 000 <sub>2</sub> .                                                                                                                      |  |  |  |  |  |

|                | OUT2     | DAC 2 Output. DAC 1 address = 001 <sub>2</sub> .                                                                                                                      |  |  |  |  |  |

|                | OUT3     | DAC 3 Output. DAC 1 address = 010 <sub>2</sub> .                                                                                                                      |  |  |  |  |  |

|                | OUT4     | DAC 4 Output. DAC 1 address = 011 <sub>2</sub> .                                                                                                                      |  |  |  |  |  |

|                | OUT5     | DAC 5 Output. DAC 1 address = 100 <sub>2</sub> .                                                                                                                      |  |  |  |  |  |

| (see Figure 2) | OUT6     | DAC 6 Output. DAC 1 address = 101 <sub>2</sub> .                                                                                                                      |  |  |  |  |  |

| (See Figure 2) | OUT7     | <b>DAC 7 Output</b> . DAC 1 address = 110 <sub>2</sub> .                                                                                                              |  |  |  |  |  |

|                | OUT8     | DAC 8 Output. DAC 1 address = 111 <sub>2</sub> .                                                                                                                      |  |  |  |  |  |

|                | RSN      | <b>Reset</b> (AS1504 Only). Active-low asynchronous reset to mid-scale output setting. Loads all DAC latches with 80 <sub>h</sub> .                                   |  |  |  |  |  |

|                | SDI      | Serial Data Input                                                                                                                                                     |  |  |  |  |  |

|                | SHDNN    | Shutdown. Active-low reference input open-circuit. All DAC outputs open-circuit.                                                                                      |  |  |  |  |  |

|                | OHDININ  | Note: DAC latch settings are maintained during shutdown.                                                                                                              |  |  |  |  |  |

|                | VDD      | Positive Supply Voltage. +3 to +5V.                                                                                                                                   |  |  |  |  |  |

|                | VREFH    | Common High-Side DAC Reference Input                                                                                                                                  |  |  |  |  |  |

|                | VREFL    | Common Low-Side DAC Reference Input (AS1505 Only).                                                                                                                    |  |  |  |  |  |

## **5 Absolute Maximum Ratings**

Stresses beyond those listed in Table 3 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 3. Absolute Maximum Ratings

| Parameter                             | Min  | Max  | Units | Comments                                                                                                                                                                                                        |

|---------------------------------------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD to GND                            | -0.3 | +7   | V     |                                                                                                                                                                                                                 |

| VREFH and VREFH to GND                | 0    | Vdd  | V     |                                                                                                                                                                                                                 |

| OUTx to GND                           | 0    | Vdd  | V     |                                                                                                                                                                                                                 |

| Digital Input Voltage to GND          | 0    | Vdd  | V     |                                                                                                                                                                                                                 |

| Package Power Dissipation             |      |      |       | Тј Мах - Тамв∕θја                                                                                                                                                                                               |

| Operating Temperature Range           | -40  | +85  | °C    |                                                                                                                                                                                                                 |

| Storage Temperature Range             | -65  | +150 | °C    |                                                                                                                                                                                                                 |

| Maximum Junction Temperature (TJ Max) |      | +150 | °C    |                                                                                                                                                                                                                 |

| Thermal Resistance (θJA)              |      | 60   | °C/W  |                                                                                                                                                                                                                 |

| Electro-Static Discharge              |      | <1   | kV    |                                                                                                                                                                                                                 |

| Package Body Temperature              |      | +260 | °C    | The reflow peak soldering temperature (body temperature) specified is in compliance with IPC/JEDEC J-STD-020C "Moisture/ Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices". |

### **6 Electrical Characteristics**

$VDD = +3.0V \pm 10\%$  or  $+5.0V \pm 10\%$ , VREFH = VDD, VREFL = 0V,  $-40^{\circ}\text{C} \le TAMB \le +85^{\circ}\text{C}$  (unless otherwise specified). Table 4. Electrical Characteristics

| Symbol       | Parameter                                             | Conditions                                                                       | Min   | Typ <sup>1</sup> | Max   | Unit |  |

|--------------|-------------------------------------------------------|----------------------------------------------------------------------------------|-------|------------------|-------|------|--|

| Static Accu  | <b>racy</b> (specifications apply to a                | all DACs)                                                                        |       |                  |       |      |  |

| N            | Resolution                                            |                                                                                  | 8     |                  |       | Bit  |  |

| INL          | Integral Non-Linearity Error                          |                                                                                  | -0.75 | ±0.15            | +0.75 | LSB  |  |

| DNL          | Differential Non-Linerarity                           | Guaranteed Monotonic                                                             | -0.5  | ±0.1             | +0.5  | LSB  |  |

| GFSE         | Full-Scale Error                                      |                                                                                  | -1    | ±0.2             | +1    | LSB  |  |

| Vzse         | Zero-Code Error                                       |                                                                                  | -0.5  | ±0.1             | +0.5  | LSB  |  |

| Rout         | DAC Output Resistance                                 |                                                                                  | 3     | 5                | 8     | kΩ   |  |

| ΔR/Rout      | Output Resistance Match                               |                                                                                  |       | 1                |       | %    |  |

| Reference    | Input                                                 |                                                                                  |       |                  |       |      |  |

| VREFH        | High Voltage<br>Input Range <sup>2</sup>              |                                                                                  | 0     |                  | VDD   | V    |  |

| VREFL        | Low Voltage Input Range<br>(AS1505 Only) <sup>3</sup> |                                                                                  | 0     |                  | VDD   | V    |  |

| Rın          | Input Resistance 4                                    | Digital Inputs = 55h, VREFH ≈ VDD                                                |       | 625              |       | Ω    |  |

| CREFH        | High Reference Input<br>Capacitance <sup>5</sup>      | nput District Language All Co                                                    |       | 60               |       | pF   |  |

| CREFL        | Low Reference Input<br>Capacitance <sup>5</sup>       | Digital Inputs = All 1s                                                          |       | 60               |       | pF   |  |

| Digital Inpu | ıts                                                   |                                                                                  |       |                  |       |      |  |

| \ /···       | Logic High                                            | VDD = +5V                                                                        | 2.4   |                  |       | V    |  |

| VIH          |                                                       | VDD = +3V                                                                        | 2.1   |                  |       | v    |  |

| VIL          | Logic Low                                             | VDD = +5V                                                                        |       |                  | 0.8   | V    |  |

| VIL          | Logic Low                                             | VDD = +3V                                                                        |       |                  | 0.6   | V    |  |

| lıL          | Input Current                                         | VIN = 0 or +5V                                                                   |       |                  | ±1    | μA   |  |

| CIL          | Input Capacitance 5                                   |                                                                                  |       | 5                |       | pF   |  |

| Power Sup    | plies <sup>6</sup>                                    |                                                                                  |       | •                |       |      |  |

| VDDRANGE     | Power Supply Range                                    |                                                                                  | 2.7   |                  | 5.5   | V    |  |

| <b>1</b>     | Supply Current<br>(CMOS)                              | VIH = VDD or VIL = 0V                                                            |       | 0.01             | 5     | μΑ   |  |

| IDD          | Supply Current<br>(TTL)                               | VIH = 2.4V or VIL = 0.8V, VDD = +5.5V                                            |       | 1                | 4     | mA   |  |

| IREFH        | Shutdown Current                                      | SHDNN = 0V                                                                       |       | 0.01             | 5     | μΑ   |  |

| Poiss        | Power Dissipation                                     | VIH = VDD  or  VIL = 0V, VDD = +5.5V                                             |       |                  | 27.5  | μW   |  |

| PSRR         | Power Supply Rejection<br>Ratio                       | $VDD = +5V \pm 10\%$ , $VREFH = +4.5V$<br>$VDD = +3V \pm 10\%$ , $VREFH = +2.7V$ |       | 0.001            | 0.002 | %/%  |  |

| Dynamic P    | erformance <sup>5</sup>                               |                                                                                  | 1     | 1                |       |      |  |

| ts           | Positive or Negative Vout<br>Settling Time            | ±0.5 LSB Error Band                                                              |       | 0.5              |       | μs   |  |

| СТ           | Crosstalk <sup>7</sup>                                |                                                                                  |       | 90               |       | dB   |  |

|              |                                                       |                                                                                  |       | 1                |       |      |  |

Table 4. Electrical Characteristics (Continued)

| Symbol    | Parameter Conditions                      |                  |    | Typ <sup>1</sup> | Max | Unit |  |  |

|-----------|-------------------------------------------|------------------|----|------------------|-----|------|--|--|

| Switching | Switching Characteristics <sup>5, 8</sup> |                  |    |                  |     |      |  |  |

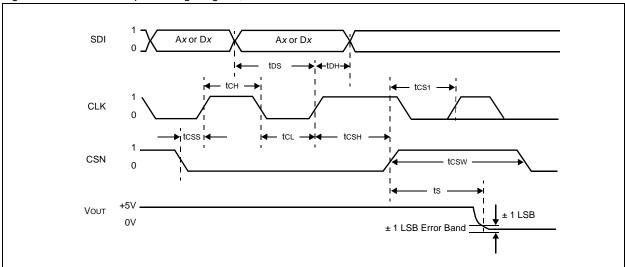

| tch       | Input Clock Pulse Width                   | High Clock Level | 15 |                  |     | ns   |  |  |

| tCL       | input Glock Fulse Width                   | Low Clock Level  | 15 |                  |     | ns   |  |  |

| tDS       | Data Setup Time                           |                  | 5  |                  |     | ns   |  |  |

| tDH       | Data Hold Time                            |                  | 5  |                  |     | ns   |  |  |

| tcss      | CSN Setup Time                            |                  | 10 |                  |     | ns   |  |  |

| tcsw      | CSN High Pulse Width                      |                  | 10 |                  |     | ns   |  |  |

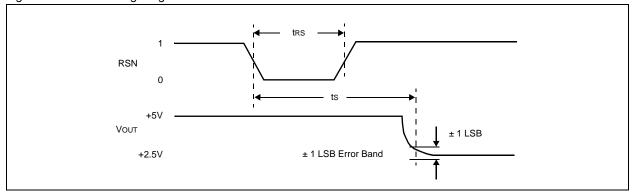

| trs       | Reset Pulse Width                         |                  | 60 |                  |     | ns   |  |  |

| tcsH      | CLK-Rise to CSN-Rise<br>Hold Time         |                  | 15 |                  |     | ns   |  |  |

| tCS1      | CSN-Rise to Next Rising<br>Clock Time     |                  | 10 |                  |     | ns   |  |  |

- 1. Typ values are average readings at +25°C.

- 2. VREFH can be any value between VDD and GND.

- 3. VREFL can be any value between VDD and GND.

- 4. With all DACs set to code 0x55h. Typical input resistance per DAC is 5kOhm with code 0x55h.

- 5. Guaranteed by design; not subject to production test.

- 6. VIN = 0V or VDD (CMOS); DAC outputs unloaded. PDISS is calculated as  $IDD \times VDD$ .

- 7. Measured at an OUTx pin where an adjacent OUTx pin is making a full-scale voltage change.

- 8. See Figure 13 on page 9 for location of measured values. All input control voltages are specified with tR = tF = 2ns.

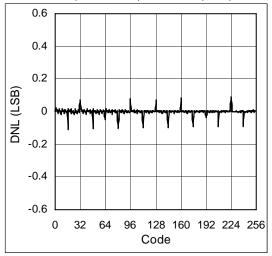

# 7 Typical Operating Characteristics

Figure 3. Differential Non-Linearity; VDD = 2.7V, VREFH = 2.7V, VREFL= 0V, TAMB = -40, +25, and +85°C

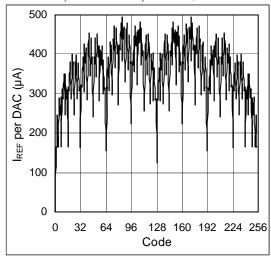

Figure 5. Reference Current vs. Code; VDD = 2.7V, VREFH = 2.7V, VREFL= 0V

Figure 7. DNL vs. Channel; VDD = 2.7V, T = 25°C

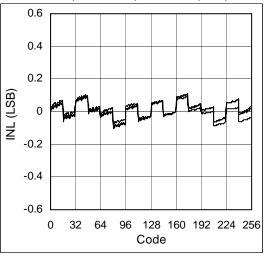

Figure 4. Integral Non-Linearity; VDD = 2.7V, VREFH = 2.7V, VREFL = 0V, TAMB = -40, +25, and  $+85^{\circ}C$

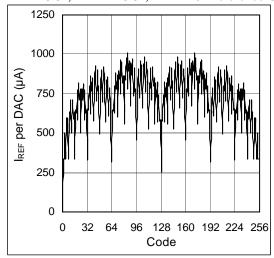

Figure 6. Reference Current vs. Code; VDD = 5.5V, VREFH = 5.5V, VREFL= 0VReference C.

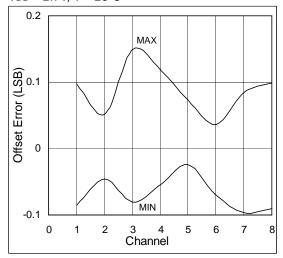

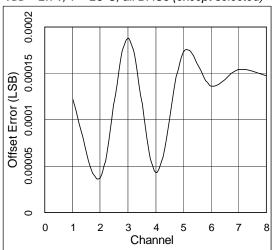

Figure 8. Offset Error vs. Channel; VDD = 2.7V, T = 25°C, all DACs (except selected) = 0x00h

Figure 9. Gain Error vs. Channel; VDD = 2.7V,  $T = 25^{\circ}C$ , all DACs (except selected) = 0x00h

0.3 (8S) 0.2 (2D) 0.1 (2D) 0 0 1 2 3 4 5 6 7 8 (2D) Channel

Figure 10. Output Resistance vs. Channel; VDD = 2.7V, T = 25°C, all DACs (except selected) = 0x00h

### 8 Detailed Description

The AS1504/AS1505 contain eight DAC channels of programmable voltage output adjustment capability. OUT*x* can be individually changed in random sequence. The fast serial-data loading (33MHz) allows all eight DACs to be quickly loaded (3ms typ; 12 x 8 x 30ns).

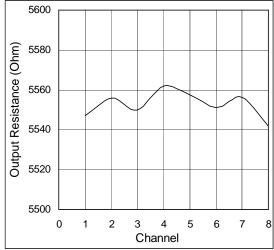

Figure 11. Detailed Block Diagram

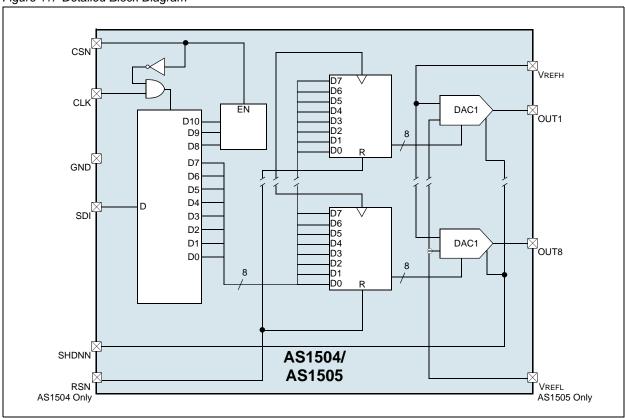

Each output voltage can be programmed by clocking an 11-bit serial data word into pin SDI (see Figure 12). The format of this data word is three address bits (MSB first, followed by eight data bits (see Table 5)).

To determine which of the DAC registers is to receive the serial register data (bits B7:B0) the DACx address is decoded as:

$$DACx = A2 \times 4 + A1 \times 2 + A0 + 1$$

(EQ 1)

Figure 12. Timing Diagram

Table 5. AS1504/AS1505 Serial Data Word Format

| Α               | ddress Bi      | ts             | Data Bits      |                |                |                |                |                |                |                |

|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| B10             | B9             | B8             | B7             | B6             | B5             | B4             | B3             | B2             | B1             | B0             |

| A2              | A1             | A0             | D7             | D6             | D5             | D4             | D3             | D2             | D1             | D0             |

| MSB             |                | LSB            | MSB            |                |                |                |                |                |                | LSB            |

| 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> |

The AS1504 provides a mid-scale reset activated by pin RSN which simplifies settings on initial power up. The AS1505 has a high- and low-side reference (pins VREFH and VREFL) to determine independent positive full-scale and zero-scale settings to optimize resolution. -

Both devices feature a power-on reset which resets them to mid-scale.

Both models feature a low-power shutdown mode which places the device into low power-consumption mode resulting in only leakage currents being consumed from the power supply, VREFx inputs, and all 8 outputs. In shutdown mode the DACx latch settings are maintained. When returning to normal operation from shutdown mode, the DACx outputs return to their previous voltage settings.

Figure 13. Serial Data Input Timing Diagram; RSN = 1

Figure 14. Reset Timing Diagram

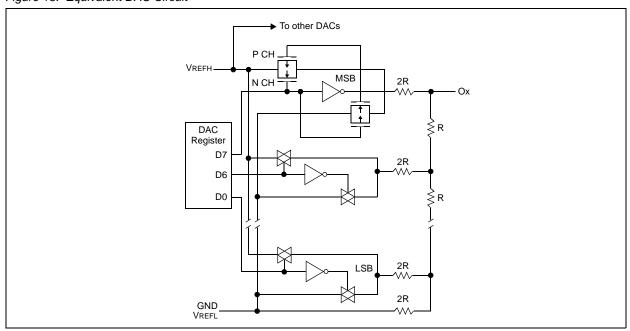

Figure 15. Equivalent DAC Circuit

### **Programming The Output Voltage**

The output voltage range is determined by the external reference connected to pins VREFH and VREFL (see Figure 15 on page 10 for a simplified diagram of the equivalent DAC circuit).

VREFL for the AS1504 is internally connected to GND and therefore cannot be offset. Pin VREFH can be tied to VDD and pin VREFL can be tied to GND establishing a basic rail-to-rail output voltage programming range. Other output ranges are established by the use of different external voltage references.

The programmed output voltage is determined as:

$$Vout (Dx) = (Dx)/256 x (VREFH - VREFL) + VREFL$$

(EQ 2)

#### Where:

Dx is the data contained in the 8-bit DACx latch.

For example, when VREFH = +5V and VREFL = 0V the output voltages will be generated per the codes listed in Table 6. Table 6. Output Voltages

| Data Bits | <b>V</b> OUT <i>x</i> | Output State (VREFH = +5V, VREFL = 0V) |  |  |

|-----------|-----------------------|----------------------------------------|--|--|

| 255       | 4.98V                 | Full-Scale                             |  |  |

| 128       | 2.50V                 | Half-Scale (Mid-Scale Reset Value)     |  |  |

| 1         | 0.02V                 | 1 LSB                                  |  |  |

| 0         | 0.00V                 | Zero-Scale                             |  |  |

### **Reference Inputs**

The reference input pins (VREFH and VREFL) set the output voltage range of all eight DACs. For the AS1504, only pin VREFH is available to establish a programmable full-scale output voltage.

Note: The external reference voltage can be any value between 0 and VDD but must not exceed VDD.

The AS1505 uses pin VREFL to establish the zero-scale output voltage. Any voltage can be applied between 0 and VDD. VREFL can be smaller or larger than VREFH since the DAC design uses fully bi-directional switches as shown in Figure 15. The input resistance to the DAC has a code dependent variation that has a nominal worst case measured at 55h, which is approximately  $2k\Omega$ . When VREFH is greater than VREFL, the REFL reference must be able to sink current out of the DAC ladder, while the REFH reference is sourcing current into the DAC ladder. The DAC design minimizes reference glitch current, thus maintaining minimum interference between DAC channels during code changes.

### **DAC Outputs**

The 8 DAC outputs (OUT1:OUT8) present a constant output resistance of approximately  $5k\Omega$  independent of code settings. The distribution of RouT from DAC to DAC typically matches within ±1%. Device-to-device matching is processlot dependent with a ±20% variation. The change in RouT with temperature has a 500 ppm/ $^{\circ}$ C temperature coefficient.

**Note:** During shutdown the OUT*x* outputs are open-circuited.

#### **Serial Interface**

The AS1504/AS1505 are controlled via a standard three-wire serial input. The three input pins are CLK, CSN and SDI.

The positive-edge sensitive CLK input requires a clean transition to avoid clocking spurious data into the serial input register (standard logic families are perfectly adequate). If mechanical switches are used for device evaluation, they should be de-bounced by a flip-flop or other suitable means.

Figure 11 on page 8 shows details of the internal digital circuitry. When CSN is pulled low, the clock can load data into the serial register on each positive clock edge (see Table 7).

Table 7. Function of Pins CSN and CLK

| CSN           | CLK           | Register Activity                                                                         |  |  |  |

|---------------|---------------|-------------------------------------------------------------------------------------------|--|--|--|

| 1             | X             | No effect.                                                                                |  |  |  |

| 0             | Positive Edge | Shifts serial register one bit loading the next bit in from the SDI pin.                  |  |  |  |

| Positive Edge | Х             | Data is transferred from the serial register to the decoded DAC register (see Figure 16). |  |  |  |

The data setup and data hold times in Table 4 on page 4 determine the valid data time requirements. The last 11 bits of the data word entered into the serial register are held when CSN goes high. When CSN goes high it gates the address decoder which enables one of the eight positive-edge triggered DAC registers (see Figure 16).

Figure 16. Equivalent Control Logic

The target DAC register is loaded with the last eight bits of the serial data word completing one DAC update. To change all eight output settings, eight separate 11-bit data words must be clocked in to the device.

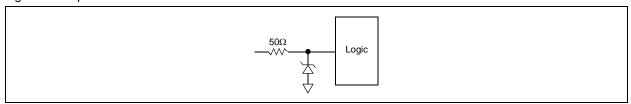

**Note:** All digital inputs (CSN, SDI, RSN, SHDNN, and CLK) are protected with the series input resistor and parallel zener diode ESD circuit illustrated in Figure 17.

Figure 17. Equivalent ESD Protection Circuit

**Note:** Digital inputs can be driven by voltages exceeding VDD thus providing logic level translation from 5V logic when the device is operated from a 3V supply.

### 9 Application Information

### **Supply Bypassing**

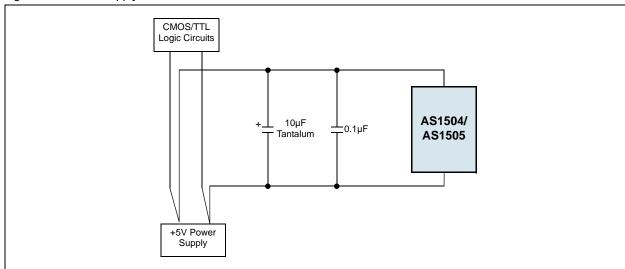

The AS1504/AS1505 require a well-filtered power source. In most applications, the AS1504/AS1505 should be powered directly from the system power supply (+3 to +5V). However, if the logic supply is a switch-mode design, it will probably generate noise in the 20kHz to 1MHz range. Additionally, fast logic gates can generate transients hundred of millivolts in amplitude from wiring resistance and inductance.

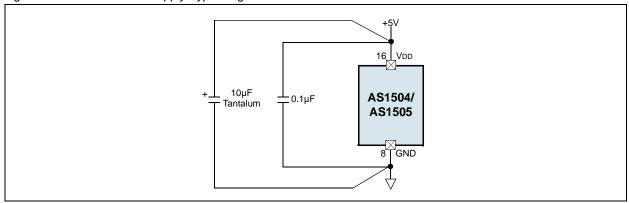

The circuit shown in Figure 18 isolates the analog section from any logic switching transients. Even if a separate power supply trace is not available, adequate supply bypassing will reduce supply-line induced errors. Local supply bypassing consisting of a 10µF tantalum electrolytic capacitor in parallel with a 0.1µF ceramic capacitor is recommended (see Figure 19).

Figure 18. Power Supply Traces

Figure 19. Recommended Supply Bypassing

#### **Output Buffering**

For most designs, the nominal  $5k\Omega$  output impedance of the AS1504/AS1505 is sufficient to drive succeeding circuitry. If a lower output impedance is required, an external amplifier can be added (see Figure 20 on page 13).

A single amplifier should be used as a simple buffer to reduce the output resistance of DAC1. An amplifier with low off-set voltage, low supply current, and operation at less than 3V is recommended due to its rail-to-rail input and output operation. DAC2 and DAC3 are configured in a summing arrangement where DAC3 provides the coarse output voltage setting and DAC2 is used for fine adjustments.

The use of R<sub>1</sub> in series with DAC2 (see Figure 20 on page 13)attenuates its contribution to the voltage sum node at the output of DAC3.

Figure 20. Output Buffering

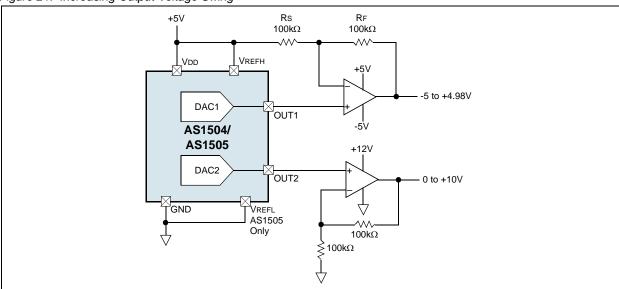

### **Increasing Output Voltage Swing**

An external amplifier can be used to extend the output voltage swing beyond the power supply rails of the AS1504/ AS1505. This design allows for a simple digital interface to the DAC, while expanding the output swing to take advantage of higher voltage external power supplies (e.g., DAC 1 of Figure 21 is configured to swing from -5 to +5V). The actual output voltage is given by:

$$VOUT = (1 + (RF/Rs))((D/256)5V) - 5V$$

(EQ 3)

#### Where:

D is the DAC input value (i.e., 0 to 255).

This design can be combined with the circuit in Figure 20 if very accurate adjustments around 0V are required.

Figure 21. Increasing Output Voltage Swing

DAC 2 (non-inverting Av = 2 configuration) of Figure 21 increases the available output swing to +10V. The feedback resistors can be adjusted to provide scaling of the output voltage, within the limits of the external operational amplifier power supplies.

#### **Microprocessor Interfaces**

The AS1504/AS1505 serial interface provides a simple connection to a wide range of microprocessors, most of which have built-in serial data capability that can be used for communicating with the device.

**Note:** In cases where a serial port is not available on the microprocessor, the AS1504/AS1505 can be addressed via software.

Eleven data bits are required to load data into the AS1504/AS1505 (3 bits for the DAC address and 8 bits for the DAC value). If more than eleven bits are transmitted before the microprocessor chip select input goes high, the most-significant bits are ignored. Because most microprocessors transmit data in 8-bit words, it will need to send 16 bits to the AS1504/AS1505; however, the AS1504/AS1505 only responds to the last 11 bits clocked into the SDI input, so the serial data interface is not affected.

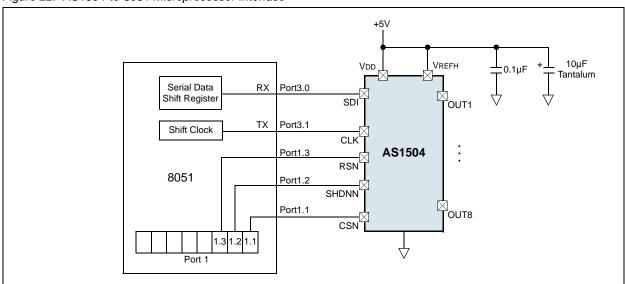

#### 8051 Microprocessor Interface

Figure 22 shows the AS1504/AS1505 interface to an 8051 microprocessor. This interface uses the 8051 internal serial port as a simple 8-bit shift register (Mode 0 operation). 8051 Port3.0 serves as the serial data output port and Port3.1 serves as the serial clock.

Figure 22. AS1504-to-8051 Microprocessor Interface

As data is written to the serial buffer register (SBUF, at Special Function Register location 99<sub>h</sub>), the data is automatically converted to serial format and clocked out via Port3.0 and Port3.1. Once 8 bits have been transmitted, the transmit interrupt flag (SCON.1) is set and the next 8 bits can be transmitted.

The AS1504/AS1505 requires that CSN goes low at the start of the serial data transfer. Additionally, pin CLK must be high when CSN goes high at the end of each data transfer. The 8051 serial clock meets these requirements, since Port3.1 begins and ends the serial data transfer in a high state.

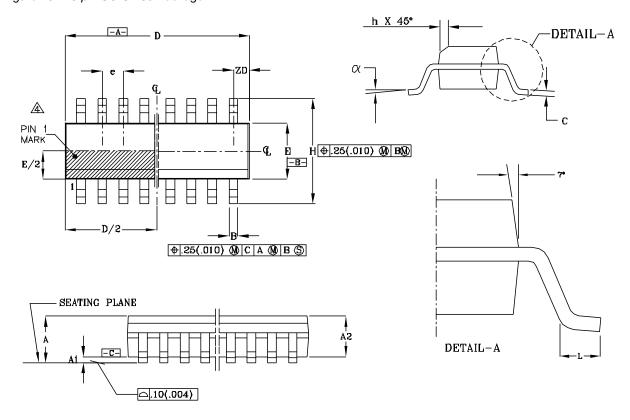

### 10 Package Drawings and Markings

The AS1504/AS1505 is available in a 16-pin SOIC-150 package.

Figure 23. 16-pin SOIC-150 Package

#### Notes:

- 1. Lead coplanarity should be 0 to 0.10mm (.004") max.

- 2. Package surface finishing:

- Top, matte (charmilles #18-30)

- All sides, matte (charmilles +18-30)

- Bottom, smooth or matte (charmilles +18-30)

- 3. All dimensions excluding mold flashes and end flash from the package body shall not exceed 0.25mm (.010") per side.

- 4. Details of pin #1 mark are optional but must be located within the area indicated.

| Symbol | Min      | Max  |  |  |

|--------|----------|------|--|--|

| Α      | 1.52     | 1.72 |  |  |

| A1     | 0.10     | 0.25 |  |  |

| A2     | 1.37     | 1.57 |  |  |

| В      | 0.36     | 0.46 |  |  |

| С      | 0.19     | 0.25 |  |  |

| D      | 9.80     | 9.98 |  |  |

| Е      | 3.81     | 3.99 |  |  |

| е      | 1.27     | BSC  |  |  |

| Н      | 5.80     | 6.20 |  |  |

| h      | 0.25     | 0.50 |  |  |

| L      | 0.41     | 1.27 |  |  |

| α      | 00       | 8º   |  |  |

| ZD     | 0.51 REF |      |  |  |

|        |          |      |  |  |

# 11 Ordering Information

The devices are available as the standard products shown in Table 8.

Table 8. Ordering Information

| Model    | Description                                    | Delivery Form | Package                |

|----------|------------------------------------------------|---------------|------------------------|

| AS1504-T | Octal 8-Bit DAC, Mid-Scale Reset               | Tape and Reel | 16-pin SOIC-150 Narrow |

| AS1505-T | Octal 8-Bit DAC, Separate VREFL Range Settings | Tape and Reel | 16-pin SOIC-150 Narrow |

#### Copyrights

Copyright © 1997-2007, austriamicrosystems AG, Schloss Premstaetten, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### **Disclaimer**

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### **Contact Information**

#### **Headquarters**

austriamicrosystems AG A-8141 Schloss Premstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact