# CMX683 Call Progress and "Voice" Detector

D/683/2 May 2006 Provisional Issue

#### **Features**

- Detects Single and Dual Call Progress Tones

- Worldwide Call Progress Tone Compatibility

- "Voice" Detect Outputs (Fast and Slow)

- Wide Dynamic Range with Low Falsing

- Low Power Operation: 600µA at 3.0V typ.

- 3.58MHz Xtal/Clock Oscillator

## **Applications**

- Worldwide Payphone Systems

- Telephone Redialling Systems

- Dialling Modems

- Banking and Billing Systems

- Telecom Test Equipment

- Telecom Security Systems

#### 1. Brief Description

The CMX683 is a general purpose Call Progress tone detector for use in monitoring the progress of calls in Public Switched Telephone System (PSTN) applications. Dial Tone, Ringing, Busy and Not Available states can be distinguished by using the host  $\mu$ C to qualify the cadence of the CP DETECT output. The CMX683 uses advanced digital techniques to characterise valid Call Progress tones, unwanted tones, line noise and voice or music signals. In contrast to Call Progress detection devices based on simple filtering techniques, the CMX683 offers excellent sensitivity coupled with low false detection rates.

The response time of the CMX683 allows it to operate with almost any Call Progress system. In particular the 'stuttered dial tone' of voice mail messaging systems is supported. The use of statistical processing techniques, which analyse signal frequency, duration and amplitude, enable the CMX683 to distinguish voice or music activity from DTMF or Call Progress signals. Separate outputs integrate the "voice" activity over both shorter and longer periods, enabling payphone and other billing systems to commence charging when a line connection has been established. A single 3.58MHz crystal ensures accurate and repeatable performance. With supply requirements between 2.7V and 5.5V and a low current consumption, the CMX683 can be easily integrated into a wide range of telecom equipments. The CMX683 has a similar pinout to all commonly used Call Progress detectors and is available in DIP, TSSOP or SOIC packages.

## **CONTENTS**

| <u>Section</u> |                                                                  | <u>Page</u> |

|----------------|------------------------------------------------------------------|-------------|

| 1.             | Brief Description                                                | 1           |

| 2.             | Block Diagram                                                    | 3           |

| 3.             | Signal List                                                      | 4           |

| 4.             | External Components                                              | 5           |

| 5.             | General Description                                              | 6<br>6      |

| 6.             | Application Notes                                                | 9           |

| 7.             | Performance Specification7.1 Electrical Performance7.2 Packaging | 11          |

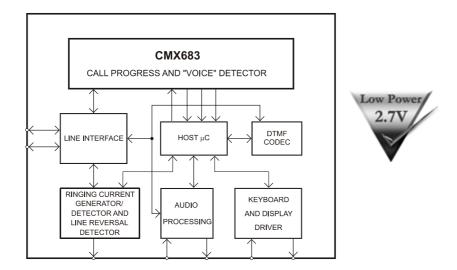

# 2. Block Diagram

Figure 1 Block Diagram

3

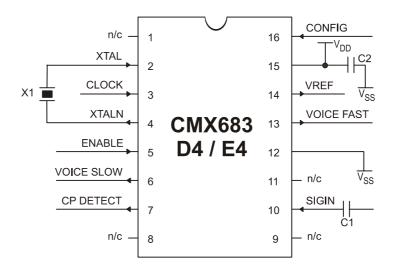

# 3. Signal List

| SOIC<br>Package | TSSOP<br>Package | DIP<br>Package |                |       |                                                                                                                                                                                                                                                        |

|-----------------|------------------|----------------|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D4<br>Pin No.   | E4<br>Pin No.    | P1<br>Pin No.  | Signal<br>Name | Туре  | Description                                                                                                                                                                                                                                            |

| 1               | 1                | _              |                | NC    | Reserved for future use. Do not make any connection to this pin.                                                                                                                                                                                       |

| 2               | 2                | 1              | XTAL           | I/P   | The input to the on-chip oscillator, to be used in conjunction with the XTALN output. An external crystal only is required. All other components are on-chip. If the on-chip oscillator is not used, this pin should be connected to V <sub>SS</sub> . |

| 3               | 3                | _              | CLOCK IN       | I/P   | The external clock input. Connect the CONFIG pin to V <sub>DD</sub> to enable this input.                                                                                                                                                              |

| 4               | 4                | 2              | XTALN          | O/P   | The inverted output of the on-chip oscillator. Leave unconnected if not used.                                                                                                                                                                          |

| 5               | 5                | 3              | ENABLE         | I/P   | A logic 1 applied to this input enables all detector outputs. A logic 0 will force all detector outputs to a logic 0.                                                                                                                                  |

| 6               | 6                | _              | VOICE<br>SLOW  | O/P   | When a Non Call Progress signal is detected this output goes to a logic 1. (See Table 1).                                                                                                                                                              |

| 7               | 7                | 4              | CP<br>DETECT   | O/P   | When a Call Progress signal is detected this output goes to a logic 1. (See Table 1).                                                                                                                                                                  |

| 8               | 8                | _              |                | NC    | Reserved for future use. Do not make any connection to this pin.                                                                                                                                                                                       |

| 9               | 9                | _              |                | NC    | Reserved for future use. Do not make any connection to this pin.                                                                                                                                                                                       |

| 10              | 10               | 5              | SIGIN          | I/P   | Signal input (which should be ac coupled as the dc bias on this pin is set internally).                                                                                                                                                                |

| 11              | 11               | -              |                | NC    | Reserved for future use. Do not make any connection to this pin.                                                                                                                                                                                       |

| 12              | 12               | 6              | $V_{SS}$       | Power | The negative supply rail (ground).                                                                                                                                                                                                                     |

| 13              | 13               | 7              | VOICE<br>FAST  | O/P   | When a Non Call Progress signal is detected this output goes to a logic 1. (See Table 1).                                                                                                                                                              |

| 14              | 14               | _              | VREF           | O/P   | Internally generated reference voltage held at ½V <sub>DD</sub> and available to power external circuits.                                                                                                                                              |

| 15              | 15               | 8              | $V_{DD}$       | Power | The positive supply rail. This pin should be decoupled to $V_{SS}$ by a capacitor.                                                                                                                                                                     |

| 16              | 16               | _              | CONFIG         | I/P   | Oscillator configuration. Leave unconnected when using an external crystal. This pin has an internal pulldown to the V <sub>SS</sub> pin.                                                                                                              |

**Notes:** I/P = Input O/P = Output NC = No Connection

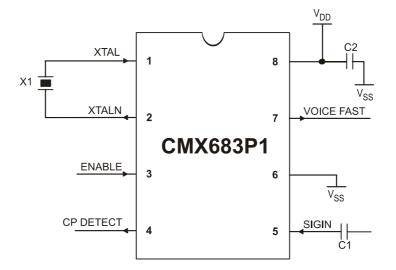

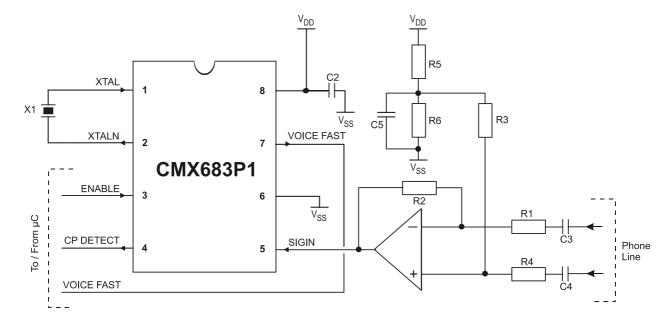

## 4. External Components

## **Typical Values:**

C1  $0.1\mu F \pm 20\%$ C2  $0.1\mu F \pm 20\%$

X1 3.579545MHz (refer to Section 7.1)

Note: C1 is not required if the input is referenced to VREF.

#### Figure 2 Recommended External Components

To achieve good noise performance,  $V_{DD}$  decoupling and protection of the receive path from extraneous in-band signals are very important. It is recommended that the printed circuit board is laid out with a ground plane in the CMX683 area to provide a low impedance connection between the  $V_{SS}$  pin and the  $V_{DD}$  decoupling capacitor.

## 5. General Description

## 5.1 Overall Function Description

The CMX683 Call Progress Tone Detector uses different tone detection methods from those commonly found with other products.

Many traditional devices from other suppliers use a bandpass filter followed by an energy detector. The filter is usually designed to pass input signals with a frequency between about 300 and 700 Hz, and the amplitudes of signals in this range are then checked against a level threshold. Any signal of acceptable level in this frequency band is classed as a Call Progress tone, including signals due to speech, music, DTMF and noise. False outputs are a common feature with these products. To avoid background noise causing a stuck "detect" output, the sensitivity of such devices is often poor.

The CMX683, by contrast, uses a stochastic signal processing technique based on analysis in both the frequency and time domains, with signal amplitude forming part of the decision process. This analysis includes checks on whether the signal has a profile which matches international standards for Call Progress tones, or whether the profile is more likely to match that of DTMF, speech, music, noise or no signal. The frequency response of the CMX683 is confined to the Call Progress band, plus a small extension above and below this band. This ensures that the CMX683 will not respond to FAX, Modem or other out-of-band signals.

The following Glossary and the Decode Truth Table in section 5.4 provide a simple explanation of the decoding functions and features offered by the CMX683.

#### 5.2 Glossary

**Call Progress Tones:** The single and dual frequency tones in the range 350 to 620 Hz which are specified widely for call progress signalling.

**Call Progress Band:** The nominal range 315 to 650 Hz within which the CMX683 will detect Call Progress tones. The detection algorithm requires that these tones have the characteristics typical of Call Progress Tones.

**No Signal:** The absence of an input signal (below the detection threshold) or

A signal below 190Hz or

A signal between 900Hz and 10kHz.

#### Non Call Progress ("Voice") Signal:

A signal falling within the nominal range of 190 to 895 Hz,

but NOT within the Call Progress band or

A signal falling within the nominal range of 190 to 895 Hz,

but NOT meeting the Call Progress detection requirements for that part of the signal which falls within the Call Progress band. Subject to the duration and other characteristics of such signals, the CMX683 will usually interpret these as a Non Call Progress signal (ie "Voice" activity).

Note that signals above 10kHz should not exceed -38dB (relative to 775mVrms), to avoid aliasing.

**Nominal:** Subject to dynamic tolerances within the signal analysis process. Absolute values are not material or adverse to performance.

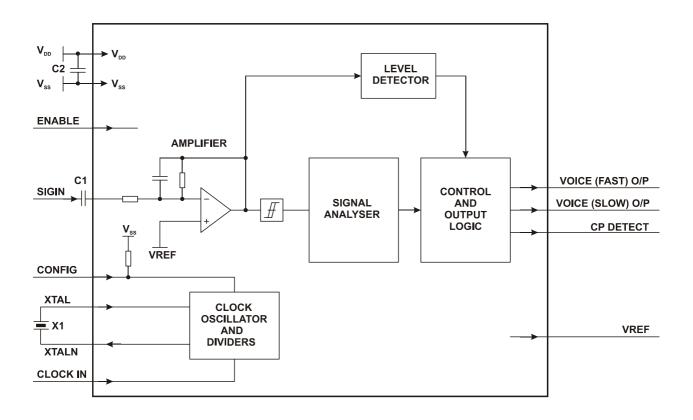

#### 5.3 Block Diagram Description

#### **Amplifier**

The input signal is amplified by a self-biased inverting amplifier. The dc bias of this input is internally set at  $\frac{1}{2}V_{DD}$

#### Signal Analyser

The frequency range, quality and consistency of the input signal is analysed by this functional block. To be classified as a Call Progress signal the input signal frequencies must lie between 315 and 650 Hz, and the signal to noise ratio must be 16dB or greater. The signal must have a minimum rms amplitude of about -60dB (relative to 775mVrms) and the signal must be consistent over a period of about 80ms. These decode criteria are continuously monitored and the assessment is updated every 6ms. To be classified as a Non Call Progress ("Voice") signal the input signal frequencies must lie between 190 and 895 Hz and the frequencies must not match the predefined profiles for DTMF or Call Progress signals. The signal must have a minimum rms amplitude of about -60dB (relative to 775mVrms) and the signal must show activity over a period of about 145ms (fast response) or 500ms (slow response).

## **Control and Output Logic**

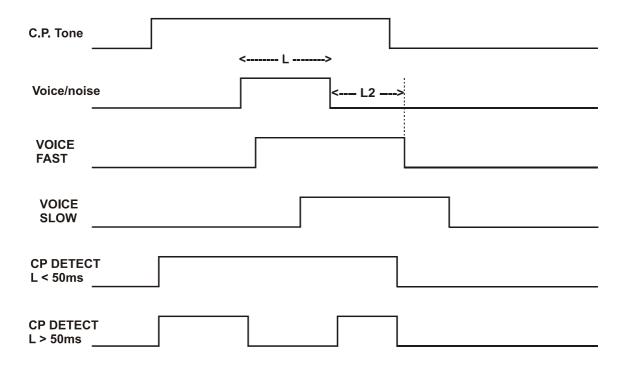

This block categorises the nature of the signal into Call Progress and Non Call Progress output states. A Non Call Progress output is further checked for activity over a longer detection period, resulting in a VOICE FAST output responding to speech/music in around 90ms and a VOICE SLOW output (with a more consistent detection) responding in around 370ms. If the VOICE FAST output is at logic 1 for more than 51% of the previous 728ms then the VOICE SLOW output will change to a logic 1. If the VOICE FAST output is at logic 1 for less than 10% of the previous 728ms then the VOICE SLOW output will change to a logic 0. The Decode Output Truth Table on the following page gives further details. Also refer to the timing diagram in Figure 5.

#### **Level Detector**

The Level Detector operates by measuring the level of the amplified input signal and comparing it with a preset threshold, which has a nominal value of -42dB (relative to 775mVrms). The Level Detector output goes to the Control and Output Logic block, where the Call Progress signal and Voice detector outputs are gated with the Level Detector output. The CP DETECT, VOICE FAST and VOICE SLOW outputs are valid only if the input signal level is above this preset threshold.

#### **Xtal Oscillator**

If the on-chip Xtal oscillator is to be used, an external 3.58MHz crystal (X1) only is required and the CONFIG pin should be left unconnected. If an external clock source is to be used, the clock should be connected to the CLOCK IN input pin and the XTAL pin should be connected to  $V_{SS}$ . The XTALN pin should be left unconnected and the CONFIG pin must be connected to  $V_{DD}$ . Note that this external clock option is not available with the P1 package.

#### **Enable Input**

A logic 1 applied to this input enables the whole device, including the outputs and the xtal oscillator circuit. About 15ms should be allowed for the oscillator to start up, once enabled.

A logic 0 applied to this input resets the device, then powersaves the xtal oscillator, the signal analyser, level detector and control and output logic. In addition the CPDETECT, VOICE FAST and VOICE SLOW outputs will be cleared to a logic 0. The  $V_{REF}$  supply is maintained at  $\frac{1}{2}V_{DD}$ , so will continue to draw a small amount of current.

## 5.4 Decode Output Truth Table

In the following Truth Table it should be noted that it is possible to get both CP DETECT and VOICE FAST or VOICE SLOW outputs simultaneously at logic 1. If the activity is initially

consistent with and meets the Call Progress signal profile, the CP DETECT output will go to logic 1. If the activity subsequently meets the Non Call Progress signal profile, the VOICE FAST output (and, eventually, the VOICE SLOW output) will go to a logic 1 without changing the CP DETECT output. The host  $\mu$ C must then use cadence information to decide what signal is present. See section 6.

Note that CP DETECT responds to the whole range of Call Progress tones from 315 to 650 Hz.

| CONDITIONS                                                                                                    | CP DETECT | "VOICE"<br>FAST/SLOW |

|---------------------------------------------------------------------------------------------------------------|-----------|----------------------|

| No Signal                                                                                                     | 0         | 0                    |

| Call Progress Signal: Will detect 350+440, 400+450, 440+480, 400, 425, 440, 450, 480+620, 600 and 620Hz tones | 1         | 0                    |

| DTMF Signal                                                                                                   | 0         | 0                    |

| Non Call Progress Signal (eg voice)                                                                           | 0         | 1                    |

| FAX/Modem or other out-of-band signals                                                                        | 0         | 0                    |

**Table 1 Decode Output Truth Table**

## 6. Application Notes

On power-up, it will take no more than 15ms to initialise the internal state. This delay should be accounted for before the CP DETECT, VOICE SLOW and VOICE FAST outputs are valid.

Figure 3 A typical Telephone Line Circuit Application

| R1 | 470k $Ω$ | R4 | 470k $Ω$ | C2 | 0.1µF       |

|----|----------|----|----------|----|-------------|

| R2 | 470k $Ω$ | R5 | 100k $Ω$ | C3 | 0.01µF 250V |

| R3 | 470k $Ω$ | R6 | 100k $Ω$ | C4 | 0.01µF 250V |

|    |          |    |          | C5 | 0.1µF       |

Note:

- 1. Resistors  $\pm 1\%$ , Capacitors  $\pm 20\%$ , unless otherwise stated.

- 2. A low offset opamp is needed. The decoupling capacitor C1 (see Figure 2) is not required if the quiescent dc level at the opamp output is the same as VREF.

All outputs should be examined for cadence information. Sometimes a call progress signal will not cause the CPDETECT output to go to a 1 because the signal has a high harmonic content, or is amplitude or frequency modulated by another tone. Often this will result in a "voice" detection instead, so it is good practice to examine the VOICE FAST output for a regular call progress cadence. A typical detection strategy might be:

#### To detect Call Progress tones

Examine CPDETECT cadence first, then examine VOICE FAST cadence. Ignore any output which has an unexpected cadence. A more accurate result will be obtained by checking the cadence over a long period of time.

#### To detect "Voice" activity

Examine the VOICE FAST cadence first. If this is irregular, it probably signifies "voice" activity. This can be confirmed by examining the VOICE SLOW output, which integrates the "voice" detection over a much longer period. If this output goes to a 1 and stays at a 1 for a long period of time, it has almost certainly detected "voice" activity.

The detection process for both "voice" and call progress tones depends on stochastic signal processing techniques and requires the customer to examine the cadence (timing) information before a final decision can be made. Frequently the call progress tone will contain noise, which may cause the CMX683 to respond with a VOICE FAST output instead. An example of this is shown in Figure 4, where the VOICE FAST output is maintained until the call progress tone has ceased, as illustrated by time L2.

Figure 4: CMX 683 Voice / Tone Response

# 7. Performance Specification

## 7.1 Electrical Performance

## 7.1.1 Absolute Maximum Ratings

Exceeding these maximum ratings can result in damage to the device.

| Min. | Max.                | Units                                             |

|------|---------------------|---------------------------------------------------|

| -0.3 | 7.0                 | V                                                 |

| -0.3 | $V_{DD} + 0.3$      | V                                                 |

| -30  | +30                 | mA                                                |

| -20  | +20                 | mA                                                |

|      | -0.3<br>-0.3<br>-30 | -0.3 7.0<br>-0.3 V <sub>DD</sub> + 0.3<br>-30 +30 |

| P1 Package                                       | Min. | Max. | Units |

|--------------------------------------------------|------|------|-------|

| Total Allowable Power Dissipation at Tamb = 25°C |      | 800  | mW    |

| Derating                                         |      | 13.0 | mW/°C |

| Storage Temperature                              | -55  | +125 | °C    |

| Operating Temperature                            | -40  | +85  | °C    |

| E4 Package                                       | Min. | Max. | Units |

|--------------------------------------------------|------|------|-------|

| Total Allowable Power Dissipation at Tamb = 25°C |      | 300  | mW    |

| Derating                                         |      | 5.0  | mW/°C |

| Storage Temperature                              | -55  | +125 | °C    |

| Operating Temperature                            | -40  | +85  | °C    |

| D4 Package                                       | Min. | Max. | Units |

|--------------------------------------------------|------|------|-------|

| Total Allowable Power Dissipation at Tamb = 25°C |      | 800  | mW    |

| Derating                                         |      | 13.0 | mW/°C |

| Storage Temperature                              | -55  | +125 | °C    |

| Operating Temperature                            | -40  | +85  | °C    |

## **Operating Limits**

Correct operation of the device outside these limits is not implied.

|                                             | Notes | Min. | Max. | Units |

|---------------------------------------------|-------|------|------|-------|

| Supply (V <sub>DD</sub> - V <sub>SS</sub> ) |       | 2.7  | 5.5  | V     |

| Xtal Frequency                              |       | 3.57 | 3.59 | MHz   |

## 7.1.3 Operating Characteristics

Xtal Frequency = 3.579545MHz, S/N = 16dB, Noise Bandwidth = 5kHz,  $V_{DD}$  = 3.0V to 5.0V, Tamb = -40°C to +85°C. 0dB = 775mVrms.

| DC Parameters   IDD (ENABLE = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                           |                          | Notes | Min.  | Тур.     | Max.  | Units     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------|-------|-------|----------|-------|-----------|

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                           |                          |       |       |          |       |           |

| Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                          |       | _     |          | _     | •         |

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                          |       | _     |          |       |           |

| AC Parameters           SIGIN pin           Input Impedance         2         -         0.1         -         MΩ           Minimum Input Signal Level         -         -38.0         -         dB           Input Signal Dynamic Range         40.0         -         -         dB           Signal to Noise Ratio         16.0         -         -         dB           Clock Input           'High' Pulse Width         3         100         -         -         ns           'Low' Pulse Width         3         100         -         -         ns           Gain (I/P = 1mVrms at 100Hz)         20.0         -         -         dB           Level Detector         Wust Detect Signal Level         4         -38.0         -         -         dB           Must Detect Signal Level         4         -38.0         -         -         dB           Must Detect Signal Level         4         -38.0         -         -         dB           Must Detect Range         315         -         650         Hz           Must Not Detect Range         750         -         250         Hz                                                                                                  |                                           | $(V_{DD} = 3.0V)$        |       | _     |          |       |           |

| SIGIN pin         Input Impedance         2         -         0.1         -         MΩ           Minimum Input Signal Level         -         -38.0         -         dB           Input Signal Dynamic Range         40.0         -         -         dB           Signal to Noise Ratio         16.0         -         -         dB           Signal to Noise Ratio         3         100         -         -         ns           'Low' Pulse Width         3         100         -         -         ns           'Low' Pulse Width         3         100         -         -         ns           Gain (I/P = 1mVrms at 100Hz)         20.0         -         -         dB           Level Detector         Must Detect Signal Level         4         -38.0         -         -         -         dB           Must Not Detect Signal Level         4         -         -         -         -         dB           Must Not Detect Range         315         -         650         Hz           Must Not Detect Range         750         -         250         Hz           Logic Interface         1         -         -         -         VDD                                                  | V <sub>REF</sub> Output                   |                          | 8     | 45%   | 50%      | 55%   | $V_{DD}$  |

| Minimum Input Signal Level         -         -38.0         -         dB           Input Signal Dynamic Range         40.0         -         -         dB           Signal to Noise Ratio         16.0         -         -         -           Clock Input           'High' Pulse Width         3         100         -         -         ns           'Low' Pulse Width         3         100         -         -         ns           Gain (I/P = 1mVrms at 100Hz)         20.0         -         -         dB           Level Detector           Must Detect Signal Level         4         -38.0         -         -         dB           Must Not Detect Signal Level         4         -38.0         -         -         dB           Call Progress Band         7         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                       |                                           |                          |       |       |          |       |           |

| Input Signal Dynamic Range Signal to Noise Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Input Impedance                           |                          | 2     | _     | 0.1      | _     | $M\Omega$ |

| Input Signal Dynamic Range Signal to Noise Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Minimum Input Signal Leve                 | el                       |       | _     | -38.0    | _     | dB        |

| Clock Input           'High' Pulse Width         3         100         -         -         ns           'Low' Pulse Width         3         100         -         -         ns           Gain (I/P = 1mVrms at 100Hz)         20.0         -         -         dB           Level Detector           Must Detect Signal Level         4         -38.0         -         -         dB           Must Not Detect Signal Level         4         -         -         -50.0         dB           Call Progress Band         7           Must Detect Range         315         -         650         Hz           Must Not Detect Range         750         -         250         Hz           Logic Interface           Input Logic 1 Level         5         80%         -         -         -         V <sub>DD</sub> Input logic 0 level         5         -         -         20%         V <sub>DD</sub> Input Capacitance         5         -         7.5         -         pF           Output logic 1 level (I <sub>OH</sub> = 120µA)         6         90%         -         -         -         V <sub>DD</sub>                                                                                   |                                           |                          |       | 40.0  | _        | _     | dB        |

| 'High' Pulse Width       3       100       -       -       ns         'Low' Pulse Width       3       100       -       -       ns         Gain (I/P = 1mVrms at 100Hz)       20.0       -       -       dB         Level Detector       20.0       -       -       -       dB         Must Detect Signal Level       4       -38.0       -       -       -       dB         Must Not Detect Signal Level       4       -       -       -50.0       dB         Call Progress Band       7         Must Detect Range       315       -       650       Hz         Must Not Detect Range       750       -       250       Hz         Logic Interface         Input Logic 1 Level       5       80%       -       -       -       V <sub>DD</sub> Input leakage current (Vin = 0 to V <sub>DD</sub> )       5       -5.0       -       +5.0       μA         Input Capacitance       5       -       7.5       -       pF         Output logic 1 level (I <sub>OH</sub> = 120μA)       6       90%       -       -       V <sub>DD</sub>                                                                                                                                                                  | Signal to Noise Ratio                     |                          |       | 16.0  | _        | _     |           |

| 'High' Pulse Width       3       100       -       -       ns         'Low' Pulse Width       3       100       -       -       ns         Gain (I/P = 1mVrms at 100Hz)       20.0       -       -       dB         Level Detector       20.0       -       -       -       dB         Must Detect Signal Level       4       -38.0       -       -       -       dB         Must Not Detect Signal Level       4       -       -       -50.0       dB         Call Progress Band       7         Must Detect Range       315       -       650       Hz         Must Not Detect Range       750       -       250       Hz         Logic Interface         Input Logic 1 Level       5       80%       -       -       -       V <sub>DD</sub> Input leakage current (Vin = 0 to V <sub>DD</sub> )       5       -5.0       -       +5.0       μA         Input Capacitance       5       -       7.5       -       pF         Output logic 1 level (I <sub>OH</sub> = 120μA)       6       90%       -       -       V <sub>DD</sub>                                                                                                                                                                  | Clock Input                               |                          |       |       |          |       |           |

| 'Low' Pulse Width Gain (I/P = 1mVrms at 100Hz)       3       100       -       -       ns dB         Level Detector       Value       Value |                                           |                          | 3     | 100   | _        | _     | ns        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                          |       |       | _        | _     | _         |

| Must Detect Signal Level 4 -38.0 dB Must Not Detect Signal Level 4 -3 -50.0 dB    Call Progress Band 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           | Hz)                      |       |       | _        | _     | _         |

| Must Detect Signal Level 4 -38.0 dB Must Not Detect Signal Level 4 -38.050.0 dB    Call Progress Band 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | l evel Detector                           |                          |       |       |          |       |           |

| Must Not Detect Signal Level4 $  -50.0$ dBCall Progress Band<br>Must Detect Range7Must Detect Range315 $-$ 650HzMust Not Detect Range750 $-$ 250HzLogic Interface<br>Input Logic 1 Level580% $   V_{DD}$ Input logic 0 level5 $  -$ 20% $V_{DD}$ Input leakage current (Vin = 0 to $V_{DD}$ )5 $-5.0$ $ +5.0$ $\mu$ AInput Capacitance5 $ 7.5$ $ p$ FOutput logic 1 level ( $I_{OH}$ = 120 $\mu$ A)690% $  V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           |                          | 4     | -38 0 | _        | _     | dB        |

| Must Detect Range 315 - 650 Hz Must Not Detect Range 750 - 250 Hz  Logic Interface Input Logic 1 Level 5 80% V <sub>DD</sub> Input logic 0 level 5 20% V <sub>DD</sub> Input leakage current (Vin = 0 to V <sub>DD</sub> ) 5 -5.0 - +5.0 μA Input Capacitance 5 - 7.5 - pF Output logic 1 level ( $I_{OH}$ = 120μA) 6 90% V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           | el                       |       | _     | _        | -50.0 | -         |

| Must Detect Range 315 - 650 Hz Must Not Detect Range 750 - 250 Hz  Logic Interface Input Logic 1 Level 5 80% V <sub>DD</sub> Input logic 0 level 5 20% V <sub>DD</sub> Input leakage current (Vin = 0 to V <sub>DD</sub> ) 5 -5.0 - +5.0 μA Input Capacitance 5 - 7.5 - pF Output logic 1 level ( $I_{OH}$ = 120μA) 6 90% V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Call Progress Band                        |                          | 7     |       |          |       |           |

| Must Not Detect Range 750 - 250 Hz <b>Logic Interface</b> Input Logic 1 Level 5 80% V <sub>DD</sub> Input logic 0 level 5 20% V <sub>DD</sub> Input leakage current (Vin = 0 to V <sub>DD</sub> ) 5 -5.0 - +5.0 $\mu$ A Input Capacitance 5 - 7.5 - $\mu$ C Output logic 1 level (I <sub>OH</sub> = 120 $\mu$ A) 6 90% V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                          | ,     | 315   | _        | 650   | Hz        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                           |                          |       |       | _        |       |           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Wast Not Detest Range                     |                          |       | 700   |          | 200   | 1 12      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                           |                          | _     | 000/  |          |       | .,        |

| Input leakage current (Vin = 0 to $V_{DD}$ ) 5 -5.0 - +5.0 $\mu A$ Input Capacitance 5 - 7.5 - $\mu A$ Output logic 1 level ( $I_{OH}$ = 120 $\mu A$ ) 6 90% - $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                           |                          |       |       | _        | _     |           |

| Input Capacitance 5 - 7.5 - pF Output logic 1 level ( $I_{OH}$ = 120µA) 6 90% - $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                           | - 0 to 1/                |       |       | _        |       |           |

| Output logic 1 level ( $I_{OH}$ = 120 $\mu$ A) 6 90% $\dot{V}_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                           | = 0 to V <sub>DD</sub> ) |       |       | -<br>7.5 |       | •         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                           | 1004\                    |       |       | 7.5      | _     | •         |

| Output logic 0 level ( $I_{OL} = 360\mu A$ ) 6 – 10% $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output logic 1 level (I <sub>OH</sub> = 1 | ιΖυμΑ)                   | ь     | 90%   | _        | _     | $v_{DD}$  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Output logic 0 level (I <sub>OL</sub> = 3 | 860μA)                   | 6     | _     | _        | 10%   | $V_{DD}$  |

Notes:

- 1. Not including any current drawn from the CMX683 pins by external circuitry.

- 2. Small signal impedance over the frequency range 100Hz to 2000Hz and at  $V_{DD}$  = 5.0V.

- 3. Timing for an external input to the CLOCK IN pin.

- 4. Input signal level at  $V_{DD}$  = 5.0V, scale signal for different  $V_{DD}$ .

- 5. ENABLE and CONFIG pins.

- 6. CP DETECT, VOICE FAST and VOICE SLOW pins.

- 7. Nominal values which are subject to dynamic tolerances within the signal analysis process, as a result of using stochastic signal processing techniques.

- 8. Load impedance on this output must exceed 330k $\Omega$ .

## **Electrical Performance** (continued)

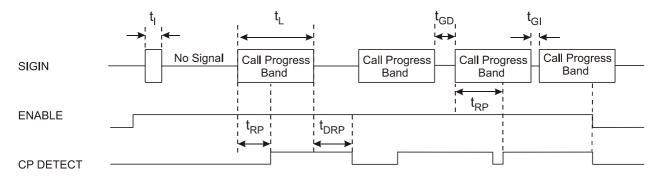

Figure 5 µC Parallel Interface Timings

For the following conditions unless otherwise specified:

Xtal Frequency = 3.579545MHz,  $V_{DD}$  = 3.0V to 5.0V, Tamb = -40°C to +85°C, S/N = 20dB.

|                  |                                           | Notes | Min. | Тур. | Max. | Units |  |

|------------------|-------------------------------------------|-------|------|------|------|-------|--|

| Signal T         | Signal Timings (ref. Figure 5)            |       |      |      |      |       |  |

| t <sub>l</sub>   | Burst Length Ignored                      |       | -    | -    | 40.0 | ms    |  |

| $t_{L}$          | Burst Length Detected                     |       | 80.0 | -    | -    | ms    |  |

| $t_{GI}$         | Call Progress Tone Gap Length Ignored     | 9     | -    | -    | 20.0 | ms    |  |

| $t_{GD}$         | Call Progress Tone Gap Length<br>Detected | 9     | 40.0 | -    | -    | ms    |  |

| $t_{RP}$         | Call Progress Tone Response Time          | 10    | -    | 46   | 80.0 | ms    |  |

| t <sub>DRP</sub> | Call Progress Tone De-Response Time       | 10    | -    | 46   | 80.0 | ms    |  |

Notes:

- 9. Only applies to bursts of the same frequency.

- 10. Measured with 350 + 440 Hz tone pair.

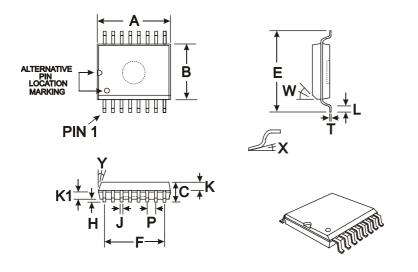

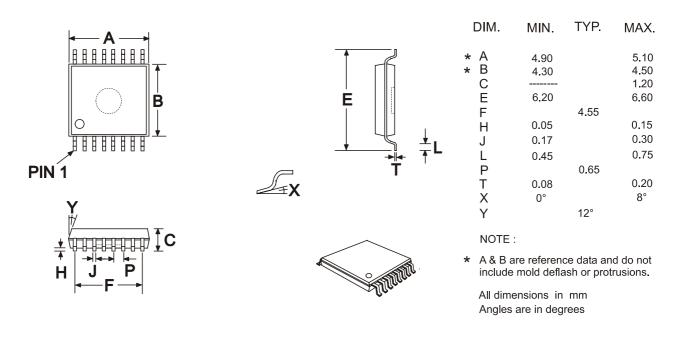

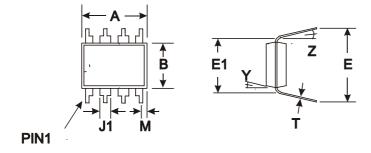

## 7.2 Packaging

\* A & B are reference datum's and do not include mold deflash or protrusions.

All dimensions in inches (mm.)

Angles are in degrees

Co-Planarity of leads within 0.004" (0.1mm)

Figure 6 SOIC Mechanical Outline: Order as part no. CMX683D4

Figure 7 TSSOP Mechanical Outline: Order as part no. CMX683E4

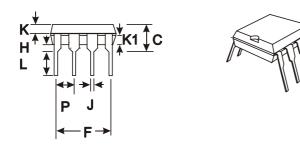

| DIM. | MIN.         | TYP.     | MAX.          |

|------|--------------|----------|---------------|

| * A  | 0.346 (8.790 | )        | 0.400 (10.16) |

| * B  | 0.240 (6.10) |          | 0.260 (6.60)  |

| С    | 0.145 (3.68) |          | 0.200 (5.08)  |

| Е    | 0.300 (7.62) |          | 0.390 (9.91). |

| E1   | 0.290 (7.37) |          | 0.325 (8.25)  |

| F    | 0.           | 30 (7.6  | 62)           |

| Н    | 0.           | 030 (0.7 | 76)           |

| J    | 0.015 (0.38) |          | 0.023 (0.58)  |

| J1   | 0.045 (1.14) |          | 0.065 (1.65)  |

| K    | 0.           | 062 (1.  | 58)           |

| K1   | 0.           | 062 (1.  | 58)           |

| L    | 0.121 (3.07) |          | 0.150 (3.81)  |

| M    | 0.           | 029 (0.7 | 74)           |

| Р    | 0.           | 100 (2.5 | 54)           |

| Τ    | 0.008 (0.20) |          | 0.015 (0.38)  |

| Υ    |              | 7°       |               |

| Z    |              | 5°       |               |

## NOTE:

\* A & B are reference datum's and do not include mold deflash or protrusions.

All dimensions in inches (mm.) Angles are in degrees

Figure 8 DIP Mechanical Outline: Order as part no. CMX683P1

Handling precautions: This product includes input protection, however, precautions should be taken to prevent device damage from electro-static discharge. CML does not assume any responsibility for the use of any circuitry described. No IPR or circuit patent licences are implied. CML reserves the right at any time without notice to change the said circuitry and this product specification. CML has a policy of testing every product shipped using calibrated test equipment to ensure compliance with this product specification. Specific testing of all circuit parameters is not necessarily performed.

## www.cmlmicro.com

For FAQs see: www.cmlmicro.com/products/faqs/

For a full data sheet listing see: www.cmlmicro.com/products/datasheets/download.htm

For detailed application notes: www.cmlmicro.com/products/applications/

| CML Microcircuits (UK) Ltd COMMUNICATION SEMICONDUCTORS      | CML Microcircuits (USA) Inc. COMMUNICATION SEMICONDUCTORS        | CML Microcircuits (Singapore)Pte Ltd COMMUNICATION SEMICONDUCTORS                             |                                                                                                                                |

|--------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Oval Park, Langford,<br>Maldon, Essex,<br>CM9 6WG - England. | 4800 Bethania Station Road,<br>Winston-Salem,<br>NC 27105 - USA. | No 2 Kallang Pudding<br>Road, #09 - 05/06 Mactech<br>Industrial Building,<br>Singapore 349307 | No. 218, Tian Mu Road<br>West, Tower 1, Unit 1008,<br>Shanghai Kerry Everbright<br>City, Zhabei,<br>Shanghai 200070,<br>China. |

| Tel: +44 (0)1621 875500<br>Fax: +44 (0)1621 875600           | Tel: +1 336 744 5050,<br>800 638 5577<br>Fax: +1 336 744 5054    | Tel: +65 6745 0426<br>Fax: +65 6745 2917                                                      | Tel: +86 21 6317 4107<br>+86 21 6317 8916<br>Fax: +86 21 6317 0243                                                             |

| Sales:<br>sales@cmlmicro.com                                 | Sales:<br>us.sales@cmlmicro.com                                  | Sales:<br>sg.sales@cmlmicro.com                                                               | Sales:<br>cn.sales@cmlmicro.com.cn                                                                                             |

| Technical Support: techsupport@cmlmicro.com                  | Technical Support:<br>us.techsupport@cmlmicro.com                | Technical Support: sg.techsupport@cmlmicro.com                                                | Technical Support:<br>sg.techsupport@cmlmicro.com                                                                              |