# CMX7032 AIS Rx Data Processor NMEA 0183-HS Output

D/7032\_FI2.0/8 July 2011

## **DATASHEET**

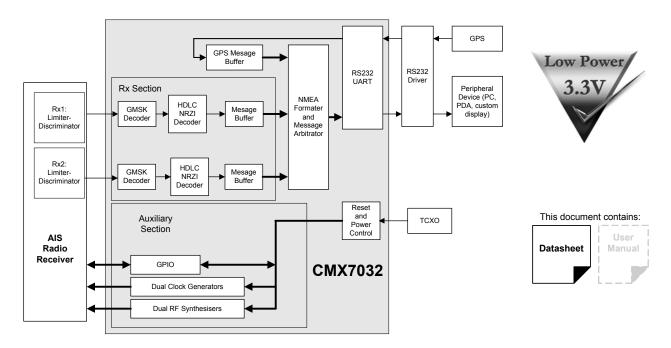

CMX7032FI-2.x: Marine AIS Rx-only data processor designed for Limiter-Discriminator based RF systems

#### Features:

- Dual GMSK Demodulators

- AIS Data Output in RS232 NMEA 0183 Format

- Optimum Rx Co-channel Performance

- Low Profile 64 Pin Leadless VQFN and LQFP Packages

- Configurable by Function Image™ (FI)

- Two RF Synthesisers

- Two Auxiliary System Clock Generators

- Low-Power (3.0V to 3.6V) Operation

- Limiter-Discriminator Rx Interface

- Automatic FI Loading from EEPROM for Host-less Operation

- Automatic Identification System (AIS) for Marine Safety

- Compatible with PE0201 Kit

- Compatible with DE70321 Kit

- For AIS Rx-only Modules

Brief description, see next page...

D/7032\_FI2.0/8

#### 1 Brief Description

A highly integrated Baseband Signalling Processor IC, the CMX7032 used with 7032FI-2.x fulfils the requirements of the Rx-only Marine Automatic Identification System (AIS) receiver market.

The AIS system allows ships and base stations to communicate their position and other data to each other without the need for a centralised controller. This allows vessels to "see" each other and take appropriate action to avoid collision and so improve marine safety. The system uses a GMSK 9600 baud data link in the Marine VHF radio band. The system requirements are defined in ITU-M 1371-1.

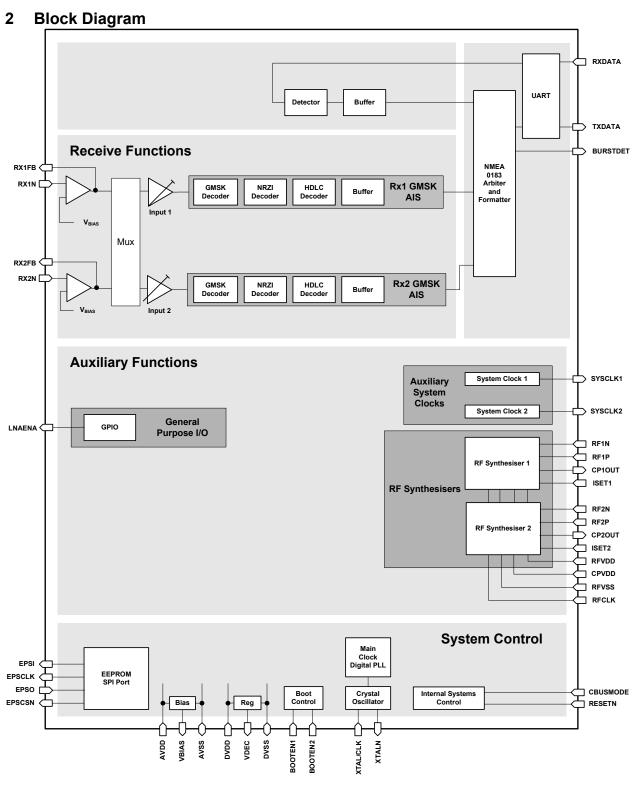

When used with the 7032FI-2.x the device operates in a Rx-only mode and comprises two parallel Limiter-Discriminator Rx paths and an RS232 style/NMEA 0183-HS compatible output (38400 baud). The device performs signal demodulation with associated AIS functions, such as training sequence detection, NRZI conversion and HDLC processing (flags, bit de-stuffing, CRC check). Integrated Rx data buffers are also provided which removes the need for a host  $\mu$ C. Provision of a number of user-programmable areas in the FI allows the RF synthesisers of the CMX7032 to be programmed directly, which simplifies the system hardware design, reducing the overall equipment cost and size. Allowance is made in the RS232 interface for an external GPS device to be connected to reduce the proliferation of interface connections in the final product design.7032FI-2.0 is compatible with CMX7032 devices with batch code 67228 or later. Devices from earlier batch codes may be used with care, but are not recommended for production.

The CMX7032 device utilises CML's proprietary  $FirmASIC^{\circledR}$  component technology. On-chip subsystems are configured by a Function Image<sup>TM</sup>: this is a data file that is uploaded during device initialisation and defines the device's function and feature set. The Function Image<sup>TM</sup> can be loaded automatically from an external EEPROM or from a host  $\mu$ Controller over the built-in RS232 serial interface. The device's functions and features can be enhanced by subsequent Function Image<sup>TM</sup> releases, facilitating in-the-field upgrades.

This Datasheet is the first part of a two-part document comprising Datasheet and User Manual: the User Manual can be obtained by registering your interest in this product with your local CML representative. These documents refer specifically to the features provided by Function Image™ 2.x.

## **CONTENTS**

| 1    | Brief Description                                      | 2  |

|------|--------------------------------------------------------|----|

|      | 1.1 History                                            | 4  |

| 2    | Block Diagram                                          | 6  |

| 3    | Signal List                                            | o  |

| 3    | 3.1 Signal Definitions                                 |    |

| 4    | Recommended External Components                        | 11 |

| 5    | PCB Layout Guidelines and Power Supply Decoupling      | 13 |

| 6    | General Description                                    | 14 |

|      | 6.1 Overview 14                                        |    |

|      | 6.2 AIS System Formats                                 | 14 |

| 7    | Detailed Descriptions                                  | 16 |

| •    | 7.1 Clock Source                                       |    |

|      | 7.2 Power Supply                                       |    |

|      | 7.3 Peripheral Interface                               |    |

|      | 7.3.1 Interface Hardware                               |    |

|      | 7.3.2 Interface Format                                 |    |

|      | 7.3.3 Operational Mode                                 |    |

|      | 7.3.4 GPS Pass Through                                 |    |

|      | 7.4 Function Image™ Load                               |    |

|      | 7.4.1 FI Loading from EEPROM                           |    |

|      | 7.4.2 FI Loading from Host Controller                  |    |

| 8    | System Description and Tasks                           | 24 |

| 0    | 8.1.1 Signal Routing                                   |    |

|      | 8.1.2 Operating Modes                                  |    |

|      | 8.1.3 Modem and Data Units                             |    |

|      | 8.1.4 Rx Operation                                     |    |

|      | 8.2 Configuration Options                              |    |

|      | 8.3 RF Synthesiser                                     |    |

|      | 8.4 System Clock Synthesisers                          |    |

|      | 0.4 System Clock Synthesisers                          | 20 |

| 9    | Performance Specification                              |    |

|      | 9.1 Electrical Performance                             |    |

|      | 9.1.1 Absolute Maximum Ratings                         |    |

|      | 9.1.2 Operating Limits                                 | 28 |

|      | 9.1.3 Operating Characteristics                        |    |

|      | 9.1.4 Parametric Performance                           | 32 |

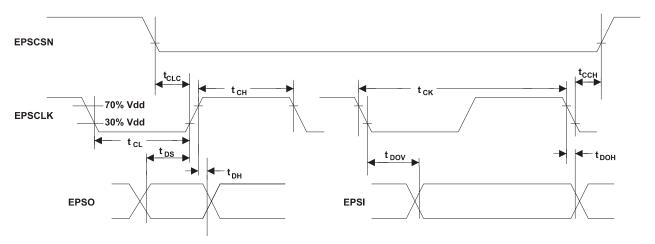

|      | 9.2 SPI Timing 33                                      |    |

|      | TABLES                                                 |    |

| Tabl | le 1 Definition of Power Supply and Reference Voltages | 10 |

| Tabl | le 2 Component Values                                  | 12 |

|      | le 3 Message Structure                                 |    |

|      | -                                                      |    |

| ıabı | lle 4 BOOTEN Pin States                                | 19 |

## **FIGURES**

| Figure 1  | CMX7032 FI-2.x Block Diagram                               | 6  |

|-----------|------------------------------------------------------------|----|

| Figure 2  | Typical System Block Diagram                               | 7  |

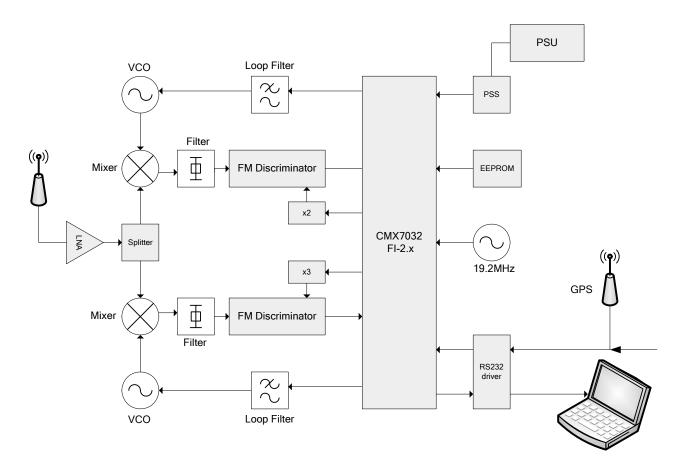

| Figure 3  | CMX7032 FI-2 Recommended External Components               | 11 |

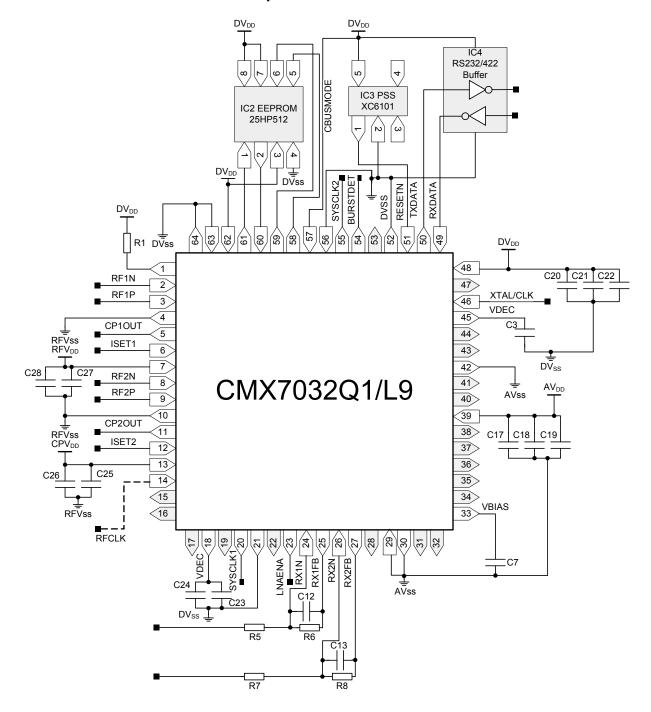

| Figure 4  | CMX7032 Power Supply Connections and De-coupling           | 13 |

| Figure 5  | FI Loading from EEPROM                                     | 20 |

| Figure 6  | Rx Task Operation                                          | 22 |

| Figure 7  | Example RF Synthesiser Components                          | 23 |

| Figure 8  | Single RF Synthesiser Block Diagram                        | 24 |

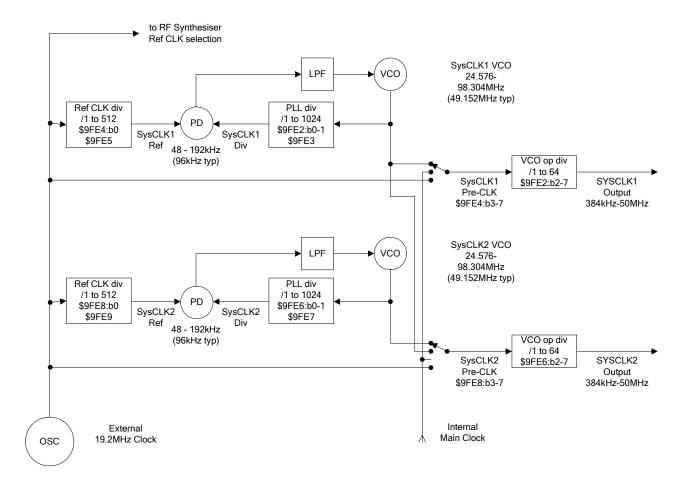

| Figure 9  | System Clock Generation                                    | 26 |

| Figure 10 | SPI Interface Timing                                       | 33 |

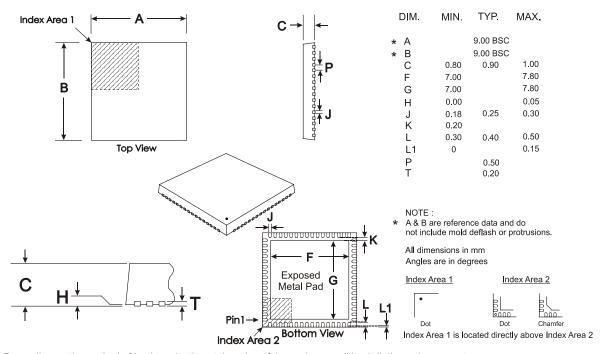

| Figure 1  | 1 Mechanical outline for 64-pad VQFN package (Q1)          | 34 |

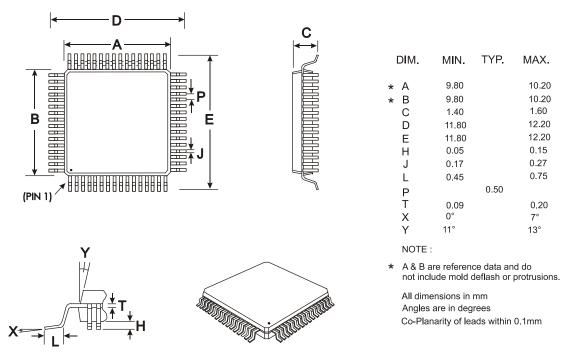

| Figure 12 | 2 Mechanical outline for 64-pin LQFP (leaded) package (L9) | 34 |

# 1.1 History

| Version | Changes                                                                                                                 | Date    |

|---------|-------------------------------------------------------------------------------------------------------------------------|---------|

| 8       | Update to RF Synthesiser paramaters, following evaluation.                                                              | 29/7/11 |

| 7       | <ul> <li>Addition of operating voltage range clarification (3.0V to 3.6V) into History files</li> </ul>                 | 18/9/09 |

|         | <ul> <li>Reference to "thickstub" tools being removed from section 7.4.2 added into</li> </ul>                          |         |

|         | History files. Contact CML for further help on EEPROM in-circuit programming.                                           |         |

|         | <ul> <li>Corrected typographical errors in section 9 (V<sub>DD</sub>, etc).</li> </ul>                                  |         |

|         | <ul> <li>Function Image™ flowchart (Fig 5) revised to show "\$PCML CMX7032-</li> </ul>                                  |         |

|         | 20nn <cr><lf>" as the data string output after successfully loading the FI.</lf></cr>                                   |         |

| 6       | <ul> <li>Corrections to BOOTEN pin states, Table 4</li> </ul>                                                           | 9/9/09  |

|         | Other minor typographical and stylistic updates                                                                         |         |

|         | GPS pass-through sentences updated                                                                                      |         |

|         | Power-on reset response updated to include version identification                                                       |         |

| 5       | Correction of FI reference to 2.0                                                                                       | 6/10/08 |

|         | <ul> <li>Correction to signal flow direction on SPI bus and addition of C-BUS Mode</li> </ul>                           |         |

|         | connection to Block Diagram (Figure 1)                                                                                  |         |

|         | • Emphasis of unused pins which need to be connected to Vss or Vdd, section 3                                           |         |

|         | <ul> <li>Correction to signal flow of Burst_Det and RFVss signals in Figure 3</li> </ul>                                |         |

|         | <ul> <li>Reference to potential FI upgrades and version number reporting added to<br/>sections 7.3.3 and 7.4</li> </ul> |         |

|         | <ul> <li>Clarification of required clock frequency for operation of CMX7032 with FI-2.0</li> </ul>                      |         |

|         | in section 9.1.2                                                                                                        |         |

|         | <ul> <li>Correction of Rx input impedance in parametric specification, section 9.1.3</li> </ul>                         |         |

|         | <ul> <li>Correction of N and R division ratio limits in section 9.1.3</li> </ul>                                        |         |

|         | <ul> <li>Clarification of typical and maximum current consumption in section 9.1.3</li> </ul>                           |         |

|         | <ul> <li>Addition/correction of notes 23, 24 and 34 to section 9.1.3</li> </ul>                                         |         |

|         | <ul> <li>Clarification of operation of b13 in System CLK 1 and 2 registers, section</li> </ul>                          |         |

|         | 11.1.3                                                                                                                  |         |

|         | <ul> <li>Change status of FI-2.0.0.2 to full release in section 13</li> </ul>                                           |         |

|         | minor editorial changes and clarifications                                                                              |         |

| 4       | Text references to SYSCLK1 and 2 corrected in section 11.                                                               | 22/9/08 |

| 2 |                                                                                | EEDDOM as a sister of the DE DIT N/D as most of in Table 4                               | 2/0/00  |  |  |  |  |  |

|---|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

| 3 | • =                                                                            | EEPROM registers for RF PLL N/R corrected in Table 4                                     | 3/9/08  |  |  |  |  |  |

|   | • F                                                                            | References to CMX7042 removed                                                            |         |  |  |  |  |  |

|   | • 8                                                                            | <ul> <li>Section 11.1.3, default SYSCLK states and operation of b13 corrected</li> </ul> |         |  |  |  |  |  |

|   | • E                                                                            | EEPROM (not C_BUS) locations - Figure 9 corrected                                        |         |  |  |  |  |  |

|   | • T                                                                            | Text regarding HEX files added in section 11                                             |         |  |  |  |  |  |

| 2 | • F                                                                            | Pin 57 now connected to DVdd. This is required to guarantee reliable operation           | 31/1/08 |  |  |  |  |  |

|   | • F                                                                            | Pin 29 now connected to AVss. This is required to guarantee reliable operation           |         |  |  |  |  |  |

|   | Pin 56 now connected to DVss. This is required to guarantee reliable operation |                                                                                          |         |  |  |  |  |  |

|   | Information on the Q1 package exposed metal pad added                          |                                                                                          |         |  |  |  |  |  |

|   | AIS Channel Number added to Table 2                                            |                                                                                          |         |  |  |  |  |  |

|   | Notes 6 and 7 added to Table 1                                                 |                                                                                          |         |  |  |  |  |  |

|   | • L                                                                            | Loop filter example changed to coincide with that on DE70321                             |         |  |  |  |  |  |

|   | • (                                                                            | CLK, RxIN, PLL, Charge Pump parameters updated                                           |         |  |  |  |  |  |

|   | • T                                                                            | Cch parameter updated                                                                    |         |  |  |  |  |  |

|   | • n                                                                            | minor editorial changes and clarifications                                               |         |  |  |  |  |  |

| 1 | • (                                                                            | Original document                                                                        | 23/7/07 |  |  |  |  |  |

Figure 1 CMX7032 FI-2.x Block Diagram

Figure 2 Typical System Block Diagram

## 3 Signal List

| 3 Signal List              |             |      |                                                                                                                                                                                                                                               |

|----------------------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMX7032<br>64-pin<br>Q1/L9 | Pin<br>Name | Туре | Description                                                                                                                                                                                                                                   |

| 1                          | -           | OP   | reserved: connect to DVDD with a 100k $\Omega$ resistor                                                                                                                                                                                       |

| 2                          | RF1N        | IP   | RF Synthesiser #1 Negative Input                                                                                                                                                                                                              |

| 3                          | RF1P        | IP   | RF Synthesiser #1 Positive Input                                                                                                                                                                                                              |

| 4                          | RFVSS       | PWR  | The negative supply rail (ground) for the RF synthesisers                                                                                                                                                                                     |

| 5                          | CP1OUT      | OP   | 1st Charge Pump output                                                                                                                                                                                                                        |

| 6                          | ISET1       | IP   | 1st Charge Pump Current Set input                                                                                                                                                                                                             |

| 7                          | RFVDD       | PWR  | The 2.5V positive supply rail for the RF synthesisers. This should be decoupled to ${\sf RFV}_{\sf SS}$ by a capacitor mounted close to the device pins.                                                                                      |

| 8                          | RF2N        | IP   | RF Synthesiser #2 Negative Input                                                                                                                                                                                                              |

| 9                          | RF2P        | IP   | RF Synthesiser #2 Positive Input                                                                                                                                                                                                              |

| 10                         | RFVSS       | PWR  | The negative supply rail (ground) for the 2nd RF synthesiser                                                                                                                                                                                  |

| 11                         | CP2OUT      | OP   | 2nd Charge Pump output                                                                                                                                                                                                                        |

| 12                         | ISET2       | IP   | 2nd Charge Pump Current Set input                                                                                                                                                                                                             |

| 13                         | CPVDD       | PWR  | The 3.3V positive supply rail for the RF charge pumps. This should be decoupled to ${\sf RFV}_{\sf SS}$ by a capacitor mounted close to the device pins                                                                                       |

| 14                         | RFCLK       | IP   | RF Clock Input (common to both synthesisers) <sup>1</sup>                                                                                                                                                                                     |

| 15                         | -           | NC   | reserved – do not connect this pin                                                                                                                                                                                                            |

| 16                         | -           | NC   | reserved – do not connect this pin                                                                                                                                                                                                            |

| 17                         | -           | NC   | reserved – do not connect this pin                                                                                                                                                                                                            |

| 18                         | VDEC        | PWR  | Internally generated 2.5V digital supply voltage. Must be decoupled to $\mathrm{DV}_\mathrm{SS}$ by capacitors mounted close to the device pins. No other connections allowed, except for optional connection to $\mathrm{RFV}_\mathrm{DD}$ . |

| 19                         | -           | NC   | reserved – do not connect this pin                                                                                                                                                                                                            |

| 20                         | SYSCLK1     | OP   | Synthesized Digital System Clock Output 1                                                                                                                                                                                                     |

| 21                         | DVSS        | PWR  | Digital Ground                                                                                                                                                                                                                                |

| 22                         | -           | NC   | reserved – do not connect this pin                                                                                                                                                                                                            |

| 23                         | LNAENA      | OP   | LNA_enable: active lo when demodulator is running                                                                                                                                                                                             |

| 24                         | RX1N        | IP   | Rx1 inverting input                                                                                                                                                                                                                           |

| 25                         | RX1FB       | OP   | Rx1 input amplifier feedback                                                                                                                                                                                                                  |

| 26                         | RX2N        | IP   | Rx2 inverting input                                                                                                                                                                                                                           |

| 27                         | RX2FB       | OP   | Rx2 input amplifier feedback                                                                                                                                                                                                                  |

| 28                         | -           | NC   | reserved – do not connect this pin                                                                                                                                                                                                            |

<sup>&</sup>lt;sup>1</sup> To minimise crosstalk, this signal should be connected to the same clock source as XTAL/CLK input. By default, this is connected internally at power-on, alternatively, this may be achieved by connecting the pin to the XTALN output when a 19.2MHz source is in use.

\_

| CMX7032<br>64-pin<br>Q1/L9 | Pin<br>Name | Туре  | Description                                                                                                                                                                                                                                                        |  |

|----------------------------|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 29                         | -           | IP    | reserved: connect to AV <sub>SS</sub>                                                                                                                                                                                                                              |  |

| 30                         | AVSS        | PWR   | Analogue Ground                                                                                                                                                                                                                                                    |  |

| 31                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 32                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 33                         | VBIAS       | OP    | Internally generated bias voltage of about $AV_{DD}/2$ , except when the device is in 'Powersave' mode when $V_{BIAS}$ will discharge to $AV_{SS}$ . Must be decoupled to $AV_{SS}$ by a capacitor mounted close to the device pins. No other connections allowed. |  |

| 34                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 35                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 36                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 37                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 38                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 39                         | AVDD        | PWR   | Analogue +3.3V supply rail. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to $AV_{SS}$ by capacitors mounted close to the device pins.                                                                    |  |

| 40                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 41                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 42                         | AVSS        | PWR   | Analogue Ground                                                                                                                                                                                                                                                    |  |

| 43                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 44                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 45                         | VDEC        | PWR   | Internally generated 2.5V supply voltage. Must be decoupled to $DV_{SS}$ by capacitors mounted close to the device pins. No other connections allowed, except for the optional connection to $RFV_{DD}$ .                                                          |  |

| 46                         | XTAL/CLK    | IP    | 19.2MHz input from the external clock source                                                                                                                                                                                                                       |  |

| 47                         | XTALN       | OP    | The output of the on-chip Xtal oscillator inverter. NC as a 19.2MHz Clock source is used                                                                                                                                                                           |  |

| 48                         | DVDD        | PWR   | Digital +3.3V supply rail. This pin should be decoupled to DV <sub>SS</sub> by capacitors mounted close to the device pins                                                                                                                                         |  |

| 49                         | RXDATA      | IP    | RS232: Serial data input from the μC/GPS                                                                                                                                                                                                                           |  |

| 50                         | TXDATA      | TS OP | RS232: Serial data output in NMEA 0183-HS format                                                                                                                                                                                                                   |  |

| 51                         | RESETN      | IP+PU | Reset Input                                                                                                                                                                                                                                                        |  |

| 52                         | DVSS        | PWR   | Digital Ground                                                                                                                                                                                                                                                     |  |

| 53                         | -           | NC    | reserved – do not connect this pin                                                                                                                                                                                                                                 |  |

| 54                         | BURSTDET    | OP    | AIS Burst detected – active lo                                                                                                                                                                                                                                     |  |

| 55                         | SYSCLK2     | OP    | Synthesised Digital System Clock Output 2                                                                                                                                                                                                                          |  |

| 56                         | -           | IP    | reserved: connect to DV <sub>SS</sub>                                                                                                                                                                                                                              |  |

| 57                         | CBUSMODE    | IP+PD | Connect to DV <sub>DD</sub>                                                                                                                                                                                                                                        |  |

| 58                         | EPSI        | OP    | EEPROM Serial Interface: SPI bus Output                                                                                                                                                                                                                            |  |

| CMX7032<br>64-pin<br>Q1/L9 | Pin<br>Name | Туре  | Description                                                                                                                                                            |

|----------------------------|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 59                         | EPSCLK      | OP    | EEPROM Serial Interface: SPI bus Clock                                                                                                                                 |

| 60                         | EPSO        | IP+PD | EEPROM Serial Interface: SPI bus Input                                                                                                                                 |

| 61                         | EPSCSN      | OP    | EEPROM Serial Interface: SPI bus Chip Select                                                                                                                           |

| 62                         | BOOTEN1     | IP+PD | Used in conjunction with BOOTEN2 to determine the operation of the bootstrap program                                                                                   |

| 63                         | BOOTEN2     | IP+PD | Used in conjunction with BOOTEN1 to determine the operation of the bootstrap program                                                                                   |

| 64                         | DVSS        | PWR   | Digital Ground                                                                                                                                                         |

| EXPOSED<br>METAL<br>PAD    | SUB         | ~     | On Q1 packages only : the central metal pad may be connected to Analogue Ground (AV <sub>SS</sub> ) or left unconnected.  No other electrical connection is permitted. |

## Notes:

ΙP Input (+PU/PD = internal pullup/pulldown resistor)

OP Output

= = = TS OP 3-state Output

Power Supply Connection PWR

NC No Connection

# 3.1 Signal Definitions

Table 1 Definition of Power Supply and Reference Voltages

| Signal<br>Name    | Pins  | Usage                                                                           |

|-------------------|-------|---------------------------------------------------------------------------------|

| $AV_{DD}$         | AVDD  | Power supply for analogue circuits                                              |

| $DV_DD$           | DVDD  | Power supply for digital circuits                                               |

| RFV <sub>DD</sub> | RFVDD | Power supply for RF synthesiser circuits                                        |

| CPV <sub>DD</sub> | CPVDD | Power supply for RF charge pump                                                 |

| $V_{DEC}$         | VDEC  | Power supply for core logic, derived from DV <sub>DD</sub> by on-chip regulator |

| $V_{BIAS}$        | VBIAS | Internal analogue reference level, derived from AV <sub>DD</sub>                |

| AV <sub>SS</sub>  | AVSS  | Ground for all analogue circuits                                                |

| DV <sub>SS</sub>  | DVSS  | Ground for all digital circuits                                                 |

| RFV <sub>SS</sub> | RFVSS | Ground for all RF circuits                                                      |

## 4 Recommended External Components

Figure 3 CMX7032 FI-2 Recommended External Components

#### **Table 2 Component Values**

| R1 | 100kΩ                     | C3  | 10nF       | C21 | 10nF | IC2      | 25HP512    |

|----|---------------------------|-----|------------|-----|------|----------|------------|

| R5 | $100$ k $\Omega$ - note 2 | C4  | not fitted | C22 | 10nF | IC3      | XC6101     |

| R6 | 100k $\Omega$             | C7  | 100nF      | C23 | 10nF | IC4      | ADM1385    |

| R7 | $100$ k $\Omega$ - note 3 | C12 | 47pF       | C24 | 10µF |          |            |

| R8 | 100k $\Omega$             | C13 | 47pF       | C25 | 10nF |          |            |

|    |                           | C17 | 10μF       | C26 | 10µF |          |            |

|    |                           | C18 | 10nF       | C27 | 10nF | XTAL/CLK | 19.2MHz    |

|    |                           | C19 | 10nF       | C28 | 10µF |          | See note 1 |

|    |                           | C20 | 10uF       |     | •    |          |            |

Resistors  $\pm 5\%$ , capacitors and inductors  $\pm 20\%$  unless otherwise stated.

#### Notes:

- 1. CLK is a 19.2MHz external clock generator.

- 2. R5 should be selected to provide the desired dc gain of the input, as follows:

$$|GAIN_{RX1N}| = 100k\Omega / R5$$

The gain should be such that the resultant output at the RX1FB pin is within the input signal range specified in 9.1.3.

3. R7 should be selected to provide the desired dc gain of the input as follows:

$$|GAIN_{RX2N}| = 100k\Omega / R7$$

The gain should be such that the resultant output at the RX2FB pin is within the input signal range specified in 9.1.3.

- 4. Care should be taken in connecting the output of the Limiter-Discriminator device to the Rx input pins of the CMX7032. The format of the GMSK signal requires that the frequency response of the input circuits extends to below 10Hz, however the variations in the incoming AIS signals from many different stations require that the input must rapidly follow the changes in dc and signal levels without de-grading the signal seen at the Rx input pins.

- 5. C12 and C13 should be chosen to minimise the phase distortion of the input signal and provide a flat amplitude response up to at least 4800Hz.

- 6. A single 10μF electrolytic capacitor (C24, fitted as shown) may be used for smoothing the power supply to both V<sub>DEC</sub> pins, providing they are connected together on the pcb with an adequate width power supply trace. Alternatively, separate smoothing capacitors should be connected to each V<sub>DEC</sub> pin. High frequency decoupling capacitors (C3 and C23) must always be fitted as close as possible to both V<sub>DEC</sub> pins.

- 7. The BOOTEN pins (pins 62 and 63) are configured in this diagram for loading from EEPROM, other loading modes are available see section 7.4.

## DV<sub>SS</sub> DVSS DVSS 64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 DVDD 47 46 44 43 REVDD AVSS 42 41 40 AVDD 39 38 -V<sub>SS</sub> 37 12 36 35 34 28 29 30 31 32 RFV<sub>SS</sub> Ground Plane AV<sub>SS</sub> Ground Plane $AV_{SS}$ DVSS DVSS DVSS

## 5 PCB Layout Guidelines and Power Supply Decoupling

Figure 4 CMX7032 Power Supply Connections and De-coupling

Component Values as per Table 2.

#### Notes:

- 1. It is important to protect the analogue pins from extraneous inband noise and to minimise the impedance between the CMX7032 and the supply and bias de-coupling capacitors. The supply decoupling capacitors should be as close as possible to the CMX7032. It is therefore recommended that the printed circuit board is laid out with separate ground planes for the AV<sub>SS</sub>, RFV<sub>SS</sub> and DV<sub>SS</sub> supplies in the area of the CMX7032, with provision to make links between them close to the CMX7032. Use of a multi-layer printed circuit board will facilitate the provision of ground planes on separate layers.

- The central metal pad (which is exposed on Q1 package only) may be electrically unconnected or, alternatively, may be connected to Analogue Ground (AV<sub>SS</sub>). No other electrical connection is permitted.

- 3. V<sub>BIAS</sub> is used as an internal reference for detecting and generating the various analogue signals. It must be carefully decoupled to ensure its integrity so, apart from the decoupling capacitor shown, no other loads should be connected. If V<sub>BIAS</sub> needs to be used to set the discriminator mid-point reference, it must be buffered with an external high input impedance buffer.

- 4. The 2.5V  $V_{DEC}$  output can be used to supply the 2.5V RFV $_{DD}$ , to remove the need for an external 2.5V regulated supply. VDEC can be directly connected to RFVDD.

## 6 General Description

#### 6.1 Overview

#### **Rx Modem Functions**

- Fixed modulation format:

- o AIS 25kHz channel (GMSK, 9600bps, 2.4kHz deviation, BT=0.4)

- Simultaneous reception of two AIS channels

- AIS Burst mode with full AIS frame formatting (HDLC-type)

- Frame sync recognition

- Bit de-stuffing

- NRZI decoding

- Training sequence and start/stop flag detection

- CRC checking

- Four 160 byte Rx data buffers can automatically store up to four 5-slot AIS bursts (2 per Rx channel)

- Rx signal input gain

#### 100 - 600 MHz RF Synthesisers

- Two Integer-N synthesisers

- Flexible design minimizes reference spurs for low phase noise results

- Charge pump

- High/low soft selectable current setting to speed large frequency channel changes

- Nominal current user defined by external resistor value

#### I/O Functions

- Output port to enable external LNA circuit

- Output port to indicate valid AIS burst received

#### **System Functions**

- All internal subsystems are controlled from the Function Image<sup>™</sup> so removing the need for a host µC

- Internal system clocks derived from RF synthesiser reference oscillator eliminate the need for additional clock oscillator(s)

- User clock synthesisers generate two clocks for external use

- Function Image<sup>™</sup> loads and executes directly from low-cost EEPROM

- Integrated 2.5V regulator can develop 2.5V from required 3.3V supply

- RS232 interface allows external GPS input to be connected and the data passed-through to the peripheral device

## 6.2 AIS System Formats

The AIS system uses two basic channel access mechanisms – Self Organising Time Division Multiple Access (SOTDMA) and Carrier-Sensing Time Division Multiple Access (CSTDMA). The 7032FI-2.0 is compatible with both systems. The SOTDMA system is detailed in ITU-R M.1371-1 and IEC 61993-2 while the CSTDMA is detailed in IEC 62287.

The CSTDMA system is used in the implementation of the Class B-CS AIS. This requires the Receiver to monitor the first part of a slot for an existing AIS transmission from another station before deciding to use the slot for its own transmission or aborting and selecting a different slot.

The SOTDMA system is used in the Class A and Base Station AIS as well as the Class B-SOTDMA AIS standard.

14

The device will transfer all currently known AIS messages and formats, it is the peripheral device that must convert them into the relevant format for the user.

The relevant International standards are:

| [0] | 11U-R M.137 | 1-1                |

|-----|-------------|--------------------|

| [1] | IEC 61993-2 | Class A            |

| [2] | IEC 62287-1 | Class B CSTDMA     |

| [3] | IEC 62287-2 | Class B SOTDMA     |

| [4] | IEC 62320-1 | Base Station       |

| [5] | IEC 62320-2 | Aids to Navigation |

| [6] | IEC 61162   | NMEA data format   |

## 7 Detailed Descriptions

#### 7.1 Clock Source

The 7032FI-2.x must be used with a 19.2MHz oscillator. The RFCLK on the CMX7032 should also be derived from this source to avoid the generation of unwanted spurious signals. The default settings route the RFCLK directly from the XTAL/CLK pin internally, so no external connection is required in this configuration.

## 7.2 Power Supply

The CMX7032 is designed to function using the  $V_{DD}$  values shown in section 9.1.2. To achieve the published performance figures it is necessary to ensure that all power supplies are adequately de-coupled to remove spurious signals or noise. The CMX7032 stores the Function Image<sup>™</sup> internally in static RAM, therefore it is imperative that  $DV_{DD}$  is maintained at all times to ensure the correct operation of the device. It is recommended that an external power supply supervisor is connected to the RESETN pin so that the device can be reset to its default state in the event of the power supply voltage being outside the specified levels (brown-out protection).

Care should be taken in the design of the power supply circuits to ensure that  $DV_{DD}$  power-on rise time characteristic allows the BOOTEN pins to achieve their correct state before the device becomes active.

#### 7.3 Peripheral Interface

This section provides a general description of the RS232 serial interface protocol used to transfer data between the CMX7032, used with 7032FI-2.x, and the peripheral device.

#### 7.3.1 Interface Hardware

The 7032FI-2.x receives AIS data bursts and after extracting the information from them, re-formats them into the NMEA 0183 format as defined in IEC 62287, IEC 61993 and IEC 61162 and outputs them on the TXDATA pin of the RS232 UART at 38400 baud, 8 bits, no parity. No hardware or software handshaking is implemented. A suitable level shifter/inverter/buffer should be used to interface this signal to the peripheral device for true RS232 or RS422 compatibility.

#### 7.3.2 Interface Format

The 7032FI-2.x will only output data if the AIS burst has been correctly decoded with a valid CRC field. All bursts that have detected errors will be discarded. All error-free bursts will be presented at the TXDATA pin, irrespective of their data content, up to the maximal length of the data buffer, therefore it is the responsibility of the peripheral device to decode the NMEA 0183 data message as appropriate. This ensures that any changes or additions to the AIS messages or structures will not adversely affect the operation of the 7032FI-2.x. The 7032FI-2.x has been successfully tested with a number of commercial PC-based and PDA software packages<sup>2</sup>.

The NMEA message structure is defined in IEC 61162 for AIS applications using the "encapsulated message" format, as shown in Table 3.

<sup>&</sup>lt;sup>2</sup> See www.shipplotter.com for a suitable PC-based software package. Others are available.

#### **Table 3 Message Structure**

!AIVDM,x1,x2,x3,a,c--c,x4\*hh<CR><LF>

| ASCII | HEX | Description                                                                                                                                                                                                                                                                                                                                 |

|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| !     | 21  | Start of Sentence: starting delimiter.                                                                                                                                                                                                                                                                                                      |

| AIVDM |     | Address Field: identifying type of talker and sentence format.                                                                                                                                                                                                                                                                              |

| ,     | 2C  | Field Delimiter: starts each field except address and checksum fields.                                                                                                                                                                                                                                                                      |

| x1    |     | Total Number of Sentences field: encapsulated information often requires more than one sentence.                                                                                                                                                                                                                                            |

| x2    |     | Sentence Number Field: identifies which sentence of the total number of sentences this is.                                                                                                                                                                                                                                                  |

| x3    |     | Sequential Message Identifier Field: field is incremented each time an encapsulated message is generated with the same formatter as a previously encapsulated message.                                                                                                                                                                      |

| а     |     | AIS Channel (A or B)                                                                                                                                                                                                                                                                                                                        |

| CC    |     | Data Sentence Block: AIS data coded as 6-bit fields.                                                                                                                                                                                                                                                                                        |

| x4    |     | Fill Bits Field: represents the number of fill bits added to complete the last six-bit coded character.                                                                                                                                                                                                                                     |

| *     | 2A  | Checksum Delimiter: indicates that the following two alphanumeric characters show the HEX value of the checksum.                                                                                                                                                                                                                            |

| hh    |     | Checksum Field: calculated by exclusive-OR'ing the 8 data bits (no start bits or stop bits) of each character in the sentence, between, but excluding "!" and "*". The hexadecimal value of the most significant and least significant 4 bits of the result are converted to two ASCII characters (0-9, A-F (upper case)) for transmission. |

| cr    | 0D  | Carriage return.                                                                                                                                                                                                                                                                                                                            |

| If    | 0A  | Line feed.                                                                                                                                                                                                                                                                                                                                  |

The message has a maximum length of 80 characters, which can be easily exceeded by an AIS message, so the multi-sentence feature is used in most cases. Some peripheral equipment is available which can handle messages in excess of the standard limit, in which case a bit in the User Configuration register can be used to instruct the CMX7032 to ignore the limit and produce a single sentence. This feature can increase the efficiency of the RS232 interface but should be used with caution.

#### 7.3.3 Operational Mode

The 7032FI-2.x has no user selectable modes of operation. It is entirely autonomous in its operation and if the device is configured to load the FI from EEPROM, then there is no host or µcontroller interaction required.

Once the device has powered up, it will check the BOOTEN pins for their status, and if set for EEPROM mode, will load the FI automatically. Once successfully loaded, it will output the proprietary NMEA 0183 data string:

#### \$PCML CMX7032-2010<cr><lf>

to indicate that it is now operating. The User Configuration registers will then be read and the SYSCLKs and RF PLLs set up accordingly. (Note: FI version 2.0.0.2 does not report the version number in the data string).

The device will then begin to attempt to decode any signal appearing at the RX1N and RX2N inputs, and once a valid preamble and start flag has been detected, place the received data into its internal buffer. On reception of a stop flag it will then decode the data and check the received checksum field. If the checksum indicates that the message has been received with no errors, it will then be passed to the NMEA formatter and placed in the output buffer. The device will automatically return to decoding signals at its input. Note that should a stop flag not be detected within the maximum allowed AIS message length, then the decode process will be reset and restarted automatically. The conditions that result in a message being discarded are:

#### Message too long or missing end flag

This indicates that the received message, after bit de-stuffing, is too long to fit into the internal message buffer. This condition could be caused by a missing or corrupted end flag.

#### CRC mismatch

This indicates that the received frame checksum does not match that calculated by the CMX7032, most probably as the result of one or more message bits being corrupted.

## New frame header found when message buffer full

This happens if the internal message buffers are still in use when another message arrives.

#### · End flag not on byte boundary

This indicates that the received message, after bit de-stuffing, is not a multiple of 8 bits. Assuming that the message was transmitted correctly, probably caused by an end flag being missed due to noise, and a subsequent message's start flag being mis-identified as the expected end flag or a bit error causing the bit de-stuffer to fail.

This process is performed on both Rx channels in parallel, but the NMEA data formatter will present the first decoded message to the RS232 UART while holding the second message in its internal buffer so that no data is lost. As there is no provision for handshaking on the UART, the peripheral device must be capable of reading the data back at the full 38400 baud rate, otherwise some data may be lost or the message corrupted. An active low pulse will be output on the BURSTDET pin when an AIS message is being transmitted over the RS232 port.

#### 7.3.4 GPS Pass Through

Many applications (eg: chart plotter) also require an input from a positioning device. This is usually accomplished using a GPS unit. If the peripheral device has a limited number of communications ports, it is possible to attach the GPS sensor to the CMX7032 RS232 input, where it is turned round, so as to present both GPS and AIS data to the peripheral device on the IC's RS232 output.

Whenever the device is not actively outputting received AIS data, it will monitor the RXDATA pin for a valid GPS NMEA sentence at 4800 baud. If a message with a valid GPS identifier is found, it will be placed in the buffer and be output on the TXDATA pin at 38400 baud. Note that while the 7032FI-2.x is receiving data on the RXDATA pin it cannot output AIS data on the TXDATA pin at the same time due to the difference in baud rates. For this reason, the GPS sentences are checked for a valid header so that the 7032FI-2.x can return to AIS output mode as soon as possible, so as to avoid buffer over-runs and potential loss of AIS data on a busy channel.

The valid GPS identifiers that are checked for are:

- \$--GGA

- \$--GLL

- \$--GSA

- \$--GSV

- \$--RMC

- \$--VTG

- o \$--DSC

- o \$--DSE

## All other messages are discarded

Once a message from the GPS has been received by the device, it will check the AIS buffers for data. This means that if the GPS sends multiple messages in quick succession, some may be ignored in preference to the AIS data.

D/7032\_FI2.0/8

## 7.4 Function Image™ Load

The Function Image™ (FI) file, which defines the operational capabilities of the device, may be obtained from the CML Technical Portal, following registration. This is in the form of a 'C' header file which can be included into the host controller software or an Intel HEX file which can be programmed into an external EEPROM. The maximum possible size of Function Image™ is 46kbytes, although a typical FI will be less than this. Note that the BOOTEN pins are only read at power-on or after the RESETN pin returns high and must remain stable throughout the FI loading process. Once the FI load has completed, the BOOTEN pins are ignored by the CMX7032 until the next power-up.

Each time the device is powered up its Function Image<sup>TM</sup> must first be loaded. This assigns internal device resources and determines all device features. The device does not operate until the Function Image<sup>TM</sup> is loaded.

The BOOTEN pins are both fitted with internal 100k (approx.) pull down resistors.

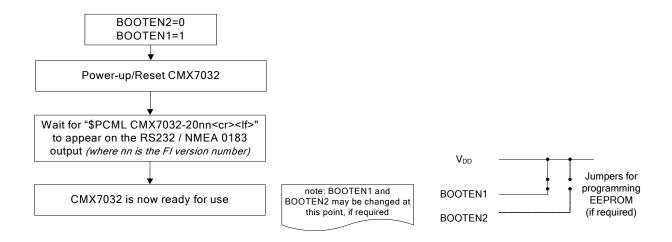

For EEPROM load, only BOOTEN1 needs to be pulled high, however, if it is required to program the EEPROM in-situ from the host, either jumpers to  $V_{DD}$  or links to host I/O pins should be provided (see Table 4). Note that the BOOTEN pins MUST be in a valid state at power-up.

Once the FI has been loaded, the CMX7032 performs these actions:

- (1) the product identification code and FI version number is reported e.g \$PCML CMX7032-2010. (The 2.0.0.2 release does not include the version number).

- (2) LNAENA output pin is cleared to 0.

If an invalid device is detected, the device will become unresponsive and a power-on reset is required to recover from this state.

RS232 Host load

1

1

reserved

1

0

EEPROM load

0

1

No FI load

0

0

**Table 4 BOOTEN Pin States**

Note:

$DV_{DD}$  MUST be maintained at all times to preserve the Function Image<sup>TM</sup> data. If  $DV_{DD}$  is suspected of exceeding the specification limits, then a full power-on reset and an FI re-load should be performed to maintain the integrity of the device.

## 7.4.1 FI Loading from EEPROM

If the 'C' header file is used then the FI must be converted into a format suitable for the EEPROM programmer (normally Intel Hex) and loaded into the EEPROM either by a host or an external programmer. Alternatively, the CML Technical Portal also holds an Intel HEX file of the same FI. Any changes to the User Configuration registers must be completed before programming the EEPROM, either by changing the 'C' header file or the data in the EEPROM programmer's buffer. The CMX7032 needs to have the BOOTEN pins set to EEPROM load, and then on power-on, the CMX7032 will automatically load the data from the EEPROM.

Figure 5 FI Loading from EEPROM

The CMX7032 has been designed to function with Atmel AT25HP512 serial EEPROM and the ATF512 flash EEPROM devices<sup>3</sup>, however other manufacturers' parts may also be suitable. The time taken to load the FI is dependant on the XTAL/CLK source frequency, but should be less than 500ms.

#### 7.4.2 FI Loading from Host Controller

The FI can be included into a host controller software build and downloaded into the CMX7032 at power-up over the RS232 interface. The BOOTEN pins must be set to the RS232 load configuration, the XTAL/CLK source set to 6.144MHz and the CMX7032 powered up. The data can then be sent directly over the RS232 to the CMX7032 at 115200baud. Following a successful FI load, the XTAL/CLK source should be returned to 19.2MHz to ensure correct operation. Further details of the data format and process are available through the CML Technical Portal.

<sup>&</sup>lt;sup>3</sup> Note that these two memory devices have slightly different addressing schemes. FI-2.x is compatible with both schemes.

## 8 System Description and Tasks

This section describes the operation of main sections of the 7032FI-2.x and the interface provided to the external device(s).

#### 8.1.1 Signal Routing

The 7032FI-2.x provides processing capability for two simultaneous AIS receive channels which are allocated to the RX1N and RX2N pins of the device. Both of these inputs are configured around an inverting op-amp stage to facilitate gain and filtering adjustments.

#### 8.1.2 Operating Modes

The 7032FI-2.x automatically enters into its Operating mode when the Function Image<sup>™</sup> has been successfully loaded. If the 7032FI-2.x does not load correctly the device will not operate.

#### 8.1.3 Modem and Data Units

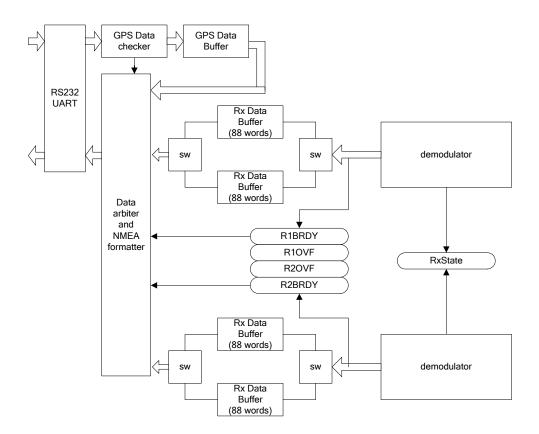

The 7032FI-2.x is logically divided into two main units, each of which can accept and perform tasks separately:

- Modem Unit

- Data Unit

The Modem Unit is primarily responsible for processing the Rx input signals to recover the Rx data they represent and storing that data in the internal Rx data buffers.

The Data Unit is primarily responsible for transferring and arbitrating data from the internal data buffers (including the external GPS input) to the RS232 interface and converting the data into NMEA 0183 format.

#### 8.1.4 Rx Operation

Typical stages of Rx task operation are depicted in Figure 6 and occur as follows:

- 1. A Modem task is automatically started on power up and continues to run indefinitely. This instructs the IC to transfer any received data from the Rx1/2 Modems to the Rx1/2 Data Buffers.

- 2. The RxBRDY flags indicate to the Data Arbiter that data is ready and outputs it to the RS232 UART in NMEA 0183 format.

- 3. After the data has been sent, the Data Arbiter will re-check the Rx1/2 Data Buffers for valid data and output it as in Step 2.

- 4. If there is no data in Rx1/2 data buffers, the Data Arbiter will re-set the RS232 UART to 4800 baud and check for valid GPS data. If valid GPS data is detected, it will be loaded into the GPS data buffer and when complete, will be re-output at 38400baud.

Figure 6 Rx Task Operation

## 8.2 Configuration Options

The device allows some of its parameters to be configured to a particular target application by changing the values of the User Configuration register locations of the FI (see User Manual section 10).

- o RF PLL 1

- o RF PLL 2

- o SysCLK1

- o SysCLK2

- NMEA 0183 sentence mode

## 8.3 RF Synthesiser

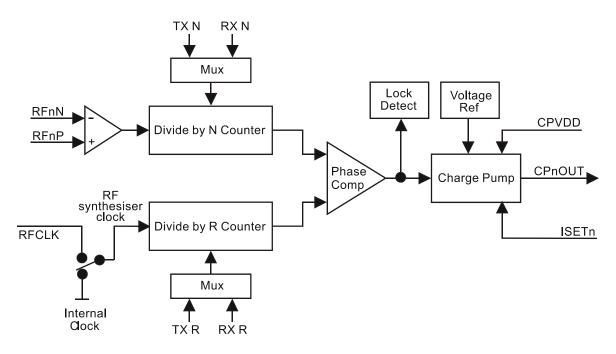

The CMX7032 includes two Integer-N RF synthesisers, each comprising a divider, phase comparator and charge pump. The divider has two sets of N and R registers: one set can be used for transmit and the other for receive. The division ratios can be set up by means of the User Configuration registers in the FI.

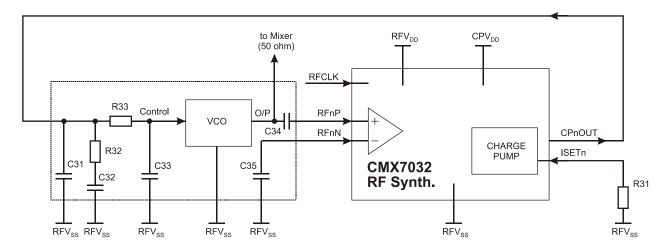

External RF components are needed to complete the synthesiser circuit. A typical schematic for one synthesiser, with external components, is shown in Figure 7.

Figure 7 Example RF Synthesiser Components

| R31 | $\Omega$ | C31 | 68nF       |

|-----|----------|-----|------------|

| R32 | 820R     | C32 | 470nF      |

| R33 | $\Omega$ | C33 | Not Fitted |

|     |          | C34 | 1nF        |

|     |          | C35 | 1nF        |

Resistors  $\pm 5\%$ , capacitors and inductors  $\pm 20\%$  unless otherwise stated.

Note: R31 is chosen within the range  $0\Omega$  to  $30k\Omega$  and selects the nominal charge pump current.

It is recommended that C34 and C35 are kept close to the VCO and that the stub from the VCO to the CMX7032 is kept as short as possible. The loop filter components should be placed close to the VCO.

Figure 8 Single RF Synthesiser Block Diagram

The two RF synthesisers are programmable to any frequency in the range 100MHz to 600MHz. Figure 8 is a block diagram of one synthesiser channel. The RF synthesiser clock is the same 19.2MHz clock as is used by the baseband circuitry. The RF synthesiser clock is common to both channels. The charge pump supply (  $\text{CPV}_{DD}$ ) is also common to both channels. The RF input pins (RFnN and RFnP), CPnOUT, ISETn and RFV $_{SS}$  pins are channel specific and designated as either RF1P, RF1N, CP1OUT, ISET1, RFV $_{SS}$  or RF2P, RF2N, CP2OUT, ISET2, RFV $_{SS}$  on the Signal List in section 3. The N and R values for Tx and Rx modes are channel specific. The divide by N counter is 20 bits; the R counter is 13 bits. Typical external components are shown in Figure 7.

Both synthesisers are phase locked loops (PLLs) of the same design, utilising external VCOs and loop filters. The VCOs need to have good phase noise performance although it is likely that the high division ratios used will result in the dominant noise source being the reference oscillator. The phase detectors are of the phase-frequency type with a high impedance charge pump output requiring just passive components in the loop filter.

Two levels of charge pump gain are available to the user, to facilitate the possibility of locking at different rates under program control. A current setting resistor (R31) is connected between the ISETn pin (one for each PLL system) and the respective RFV<sub>SS</sub>. This resistor will have an internally generated band gap voltage expressed across it and may have a value of  $0\Omega$  to  $30k\Omega$ , which (in conjunction with the on-chip series resistor of  $9.6k\Omega$ ) will give charge pump current settings over a range of 2.5mA down to  $230\mu A$  (including the control bit variation of 4 to 1). The value of the current setting resistor (R31) is determined in accordance with the following formulae:

gain bit set to 1: R31 (in  $\Omega$ ) = (24/lcp) – 9600 gain bit cleared to 0: R31 (in  $\Omega$ ) = (6/lcp) – 9600 where lcp is the charge pump current (in mA).

Note that the charge pump current should always be set to at least  $230\mu A$ . The 'gain bit' refers to either bit 3 or bit 11 in the RF Synthesiser Control register.

The step size (comparison frequency) is programmable; to minimise the effects of phase noise this should be kept as high as possible. This can be set as low as 2.5kHz (for a reference input of 20MHz or less), or up to 200kHz – limited only by the performance of the phase comparator.

The frequency for each synthesiser is set by using two registers: an 'R' register that sets the division value of the input reference frequency to the comparison frequency (step size), and an 'N' register that sets the division of the required synthesized frequency from the external VCO to the comparison frequency. This yields the required synthesized frequency (Fs), such that:

$$Fs = (N/R) \times F_{REF}$$

where  $F_{REF}$  is the selected reference frequency

Other parameters for the synthesisers are the charge pump setting (high or low)

• Since the set-up for the PLLs takes 4 x "RF Synthesiser Data register" writes it follows that, while updating the PLL settings, the registers may contain unwanted or intermediate values of bits. These will persist until the last register is written. The names "Tx" and "Rx" are arbitrary and may be assigned to other functions as required. They are independent sets of registers, one of which is selected to command each PLL by changing the settings in the RF Synthesiser Control register.

For optimum performance, a common master clock should be used for the RF synthesisers (RFCLK) and the baseband sections (Main and Auxiliary System Clocks). Using unsynchronised clocks can result in spurious products being generated in the synthesiser output and in some cases difficulty may be experienced with obtaining lock in the RF synthesisers. The 7032FI-2.x is configured to use the internal clock for both RF synthesisers by default.

#### **Lock Status**

The lock status is not available on this FI.

#### **RF Inputs**

The RF inputs are differential and self-biased (when not powersaved). They are intended to be capacitively coupled to the RF signal. The signal should be in the range 0dBm to -20dBm (not necessarily balanced). To ensure an accurate input signal the RF should be terminated with  $50\Omega$  as close to the chip as possible and with the "P" and "N" inputs capacitively coupled to the input and ground, keeping these connections as short as possible. The RF input impedance is almost purely capacitive and is dominated by package and printed circuit board parasitics.

## Guidelines for using the RF Synthesisers

- RF input slew rate (dv/dt) should be 14 V/µs minimum.

- The RF Synthesiser 2.5V digital supply (RFVDD) can be powered from the VDEC output pin.

- RF clock sources and other, different clock sources <u>must not</u> share common IC components, as this may introduce coupling into the RF. Unused ac-coupled clock buffer circuits should be tied to a dc supply, to prevent them oscillating. By default the RF clock source is routed to the XTAL/CLK input internally.

- It is recommended that the RF Synthesisers are operated with maximum gain lset (ie. ISETn tied to RFV<sub>SS</sub>).

- The loop components should be optimised for each VCO.

## 8.4 System Clock Synthesisers

Two System Clock outputs, SYSCLK1 and SYSCLK2, are available to drive additional circuits, as required. These are phase locked loop (PLL) clocks that can be programmed via the System Clock registers in the User Configuration block of the FI. The System Clock PLL Configuration registers control the values of the VCO Output divider and Main Divide registers, while the System Clock Ref. Configuration registers control the values of the Reference Divider and signal routing configurations. The PLLs are designed for a comparison frequency of 96kHz.

The System Clock output divider stages are designed so that they have a 1:1 Mark-to-Space ratio when an even divide number is selected.

Figure 9 System Clock Generation

The 7032FI-2.x XTAL/CLK input should be driven by an externally generated 19.2MHz clock, in which case the default settings following FI load will provide 9.6MHz and 19.2MHz clock sources.

26

# 9 Performance Specification

## 9.1 Electrical Performance

## 9.1.1 Absolute Maximum Ratings

Exceeding these maximum ratings can result in damage to the device.

|                                                                                                                                                                                                                                              | Min.       | Max.                    | Unit  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------|-------|

| Supply: DV <sub>DD</sub> - DV <sub>SS</sub>                                                                                                                                                                                                  | -0.3       | 4.5                     | V     |

| AV <sub>DD</sub> - AV <sub>SS</sub>                                                                                                                                                                                                          | -0.3       | 4.5                     | V     |

| RFV <sub>DD</sub> - RFV <sub>SS</sub>                                                                                                                                                                                                        | -0.3       | 4.5                     | V     |

| CPV <sub>DD</sub> - RFV <sub>SS</sub>                                                                                                                                                                                                        | -0.3       | 4.5                     | V     |

| Voltage on any pin to DV <sub>SS</sub>                                                                                                                                                                                                       | -0.3       | $DV_{DD} + 0.3$         | V     |

| Voltage on any pin to AV <sub>SS</sub>                                                                                                                                                                                                       | -0.3       | $AV_{DD} + 0.3$         | V     |

| Voltage on any pin to RFV <sub>SS</sub> (excluding CPV <sub>DD</sub> )                                                                                                                                                                       | -0.3       | RFV <sub>DD</sub> + 0.3 | V     |

| Current into or out of any power supply pin (excluding V <sub>BIAS</sub> ) (i.e. V <sub>DEC</sub> , AV <sub>DD</sub> , AV <sub>SS</sub> , DV <sub>DD</sub> , DV <sub>SS</sub> , CPV <sub>DD</sub> , RFV <sub>DD</sub> or RFV <sub>SS</sub> ) | -30        | +30                     | mA    |

| Current into or out of any other pin Voltage differential between power supplies:                                                                                                                                                            | -20        | +20                     | mA    |

| DV <sub>DD</sub> and AV <sub>DD</sub> or CPV <sub>DD</sub>                                                                                                                                                                                   | 0          | 0.3                     | V     |

| $AV_DD$ and $CPV_DD$                                                                                                                                                                                                                         | 0          | 0.3                     | V     |

| DV <sub>SS</sub> and AV <sub>SS</sub> or RFV <sub>SS</sub>                                                                                                                                                                                   | 0          | 50                      | mV    |