D/990/6 April 2008

Features

- Single Chip RF Transceiver and GMSK Modem

- IF, RF, Control and Synthesizer Stages

- Selectable B<sub>t</sub> = 0.27, 0.3 or 0.5

- Receiver Sensitivity -116dBm at 8kbps

- Full Mobitex Compatibility

- Versatile Data Rates: 4kbps to 16kbps

- Packet and Freeformat (Raw) Data

- Low-Power, Low Profile, Low-Cost BOM

# **CMX990** GMSK Packet Data Modem and RF Transceiver

**Provisional Issue**

- 400MHz 1GHz Radio Data Systems

- Simple Parallel Interfacing

- AGC Algorithm

- RSSI Measurement

- Flexible System Clocks

- Suitable for EN 300 113, EN 300 220 and FCC CFR 47 Part 90

### **1** Brief Description

A single-chip GMSK packet-data modem and RF transceiver, the CMX990 provides the majority of circuits and functions to implement a full-feature 'wireless modem' subsystem. The CMX990 can operate in RF ranges of 400MHz to 1GHz at data rates of 4 to 16 kbps and is fully Mobitex compatible.

With a minimum of external components and circuits, this half-duplex device provides on-chip: a flexible, formattable GMSK packet and free-format modem, a dual synthesiser, IF and RF stages for both Rx and Tx modes, and auxiliary ADCs and DACs for system control and monitoring.

This versatile GMSK modem is programmable to both packet and free-format data operations via an efficient task-oriented Rx and Tx format and command structure, which is combined with data scrambling, interleaving and FEC and CRC capabilities. Rx data acquisition, extraction and tracking abilities, allied with Rx data quality feedback, allow the CMX990 to operate seamlessly in varying signal environments.

Tx includes an internal vector modulator to accurately generate the modulation. This is then translated to the final frequency using an offset-phased locked loop. In the Rx path an image-reject mixer is provided to minimise external RF filtering requirements. The output of the mixer goes off-chip to allow the circuit designer flexibility in the choice of IF filter. The CMX990 then provides AGC functions and I/Q mix down to generate baseband signals for the modem. Significant Rx selectivity is provided using internal I/Q baseband filters.

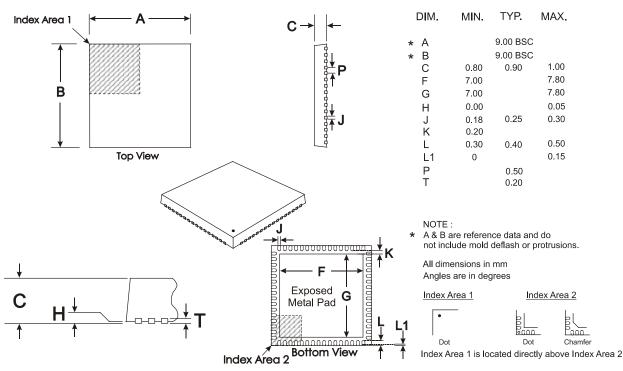

Comprehensive internal and external system control and monitoring is provided by the 8-bit host interface registers and the on-chip ADCs and DACs. Requiring a power supply input in the range 3.0 to 3.6 Volts, the CMX990 can be used in wireless products designed to comply with such standards as EN 300 113 and FCC CFR 47 Part 90. Operating over a temperature range of -40°C to +85°C, the CMX990 consolidates the core radio modem functions to enable a new generation of small, narrow-band wireless data modems. The CMX990 comes in a 64-pin low profile VQFN package.

### CONTENTS

| Section |                |                | <u>P</u>                                                    | age  |  |  |

|---------|----------------|----------------|-------------------------------------------------------------|------|--|--|

| 1       | Brief D        | escripti       | on                                                          | 1    |  |  |

| 2       | Block Diagram5 |                |                                                             |      |  |  |

| 3       | Signal List6   |                |                                                             |      |  |  |

| 4       | Extern         | al Comp        | ponents                                                     | 9    |  |  |

|         | 4.1            |                | Recommendations                                             |      |  |  |

|         | 4.2            | Proces         | sor Interface                                               | . 10 |  |  |

|         | 4.3            | Synthe         | siser and TCXO                                              | . 11 |  |  |

|         | 4.4            |                | hitter                                                      |      |  |  |

|         | 4.5            |                | er                                                          |      |  |  |

|         | 4.6            | Power          | Supply Decoupling and Layout                                | . 17 |  |  |

| 5       | Genera         | al Descr       | iption                                                      | . 19 |  |  |

|         | 5.1            |                | and Modem                                                   |      |  |  |

|         |                | 5.1.1          | Description of Blocks                                       |      |  |  |

|         |                | 5.1.2          | Modem - µC Interaction                                      |      |  |  |

|         |                | 5.1.3          | Data Formats                                                |      |  |  |

|         |                | 5.1.4          | Modem Interface                                             |      |  |  |

|         | 5.2            |                | IIF                                                         |      |  |  |

|         |                | 5.2.1<br>5.2.2 | Transmitter Section                                         |      |  |  |

|         | 5.3            |                | Receiver Section<br>y Map, Interface and Register Functions |      |  |  |

|         | 5.5            | 5.3.1          | Data Bus Buffers                                            |      |  |  |

|         |                | 5.3.2          | Address and R/W Decode                                      |      |  |  |

|         |                | 5.3.3          | Power-on and Reset                                          |      |  |  |

|         |                | 5.3.4          | Modem Interface                                             |      |  |  |

|         |                | 5.3.5          | Power control                                               |      |  |  |

|         |                | 5.3.6          | Auxiliary DAC and ADC                                       |      |  |  |

|         |                | 5.3.7          | Analogue Setup                                              |      |  |  |

|         |                | 5.3.8          | Special Command Functions                                   |      |  |  |

|         |                | 5.3.9          | Local Oscillator Synthesisers                               | . 53 |  |  |

|         |                | 5.3.10         | Clock Control                                               |      |  |  |

|         |                | 5.3.11         | Transmitter Control Bits                                    |      |  |  |

|         |                | 5.3.12         | Other Transceiver Functions                                 | . 58 |  |  |

| 6       | Applic         | ation No       | otes                                                        | . 60 |  |  |

|         | 6.1            |                | al                                                          |      |  |  |

|         | 6.2            |                | EC, Interleaving and Scrambling Information:                | . 60 |  |  |

|         |                | 6.2.1          | CRC 60                                                      |      |  |  |

|         |                | 6.2.2          | FEC 60                                                      |      |  |  |

|         |                | 6.2.3          | Interleaving                                                |      |  |  |

|         | <u> </u>       | 6.2.4          | Scrambling                                                  |      |  |  |

|         | 6.3            | 6.3.1          | Application Examples                                        |      |  |  |

|         |                | 6.3.1          | Transmit Frame Example<br>Receive Frame Example             |      |  |  |

|         | 6.4            |                | nitter                                                      |      |  |  |

|         | 0.7            | 6.4.1          | Transmitter O-PLL Frequency Tuning Range Considerations.    |      |  |  |

|         |                | 6.4.2          | Start Up                                                    |      |  |  |

|         |                | 6.4.3          | Spurious Emissions                                          |      |  |  |

|         |                | 6.4.4          | Variable BT                                                 |      |  |  |

|         |                |                |                                                             |      |  |  |

|   |       | 6.4.5   | Transmitter Performance     | 75 |

|---|-------|---------|-----------------------------|----|

|   | 6.5   | Receiv  | /er                         |    |

|   |       | 6.5.1   | Architecture Overview       | 78 |

|   |       | 6.5.2   | DC Calibration              |    |

|   |       | 6.5.3   | Matching                    |    |

|   |       | 6.5.4   | Rx Mixer Options            |    |

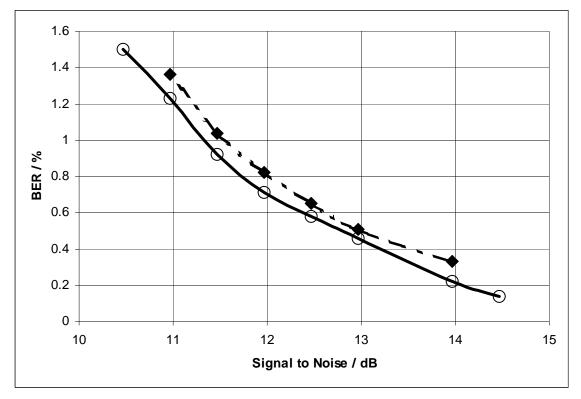

|   |       | 6.5.5   | Signal to Noise             |    |

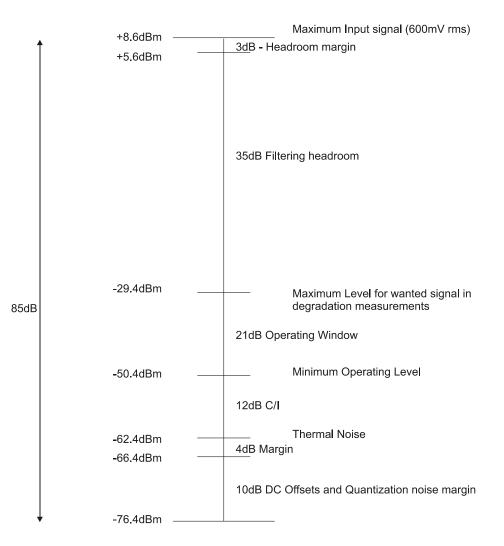

|   |       | 6.5.6   | Dynamic Range, RSSI and AGC |    |

|   |       | 6.5.7   | Signal Processing           |    |

| 7 | Perfo | rmance  | Specification               |    |

|   | 7.1   | Electri | cal Performance             |    |

|   |       | 7.1.1   |                             |    |

|   |       | 7.1.2   | Operating Limits            |    |

|   |       | 7.1.3   | Operating Characteristics   |    |

|   | 7.2   | Packa   | ging                        |    |

It is always recommended that you check for the latest product datasheet version from the Datasheets page of the CML website: [www.cmlmicro.com].

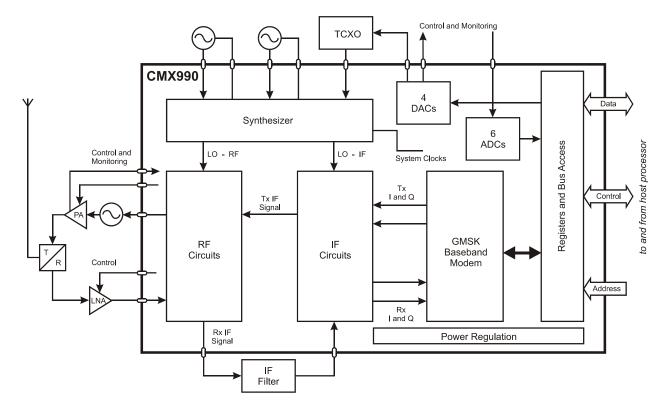

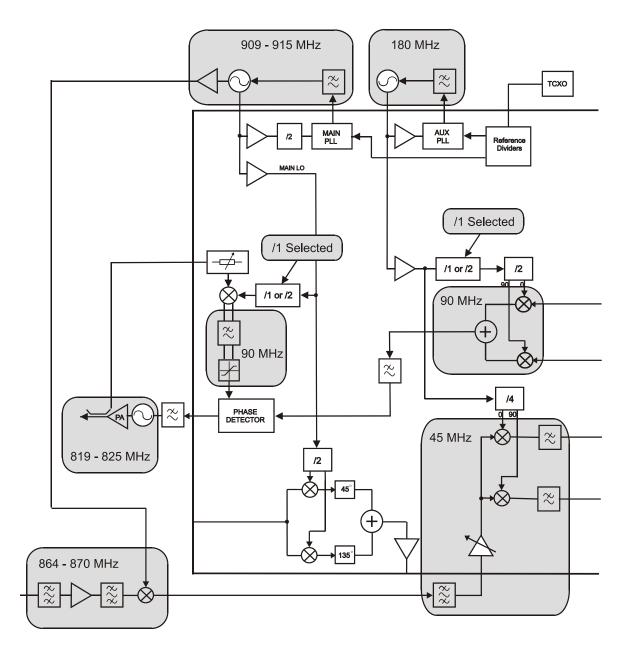

# 2 Block Diagram

Figure 1 Block Diagram

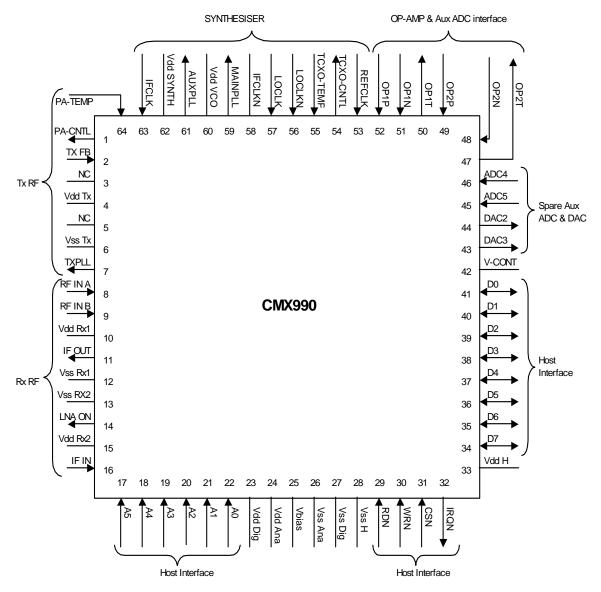

# 3 Signal List

| Package<br>Q1 | Signal              |       | Description                                                                                                            |

|---------------|---------------------|-------|------------------------------------------------------------------------------------------------------------------------|

| Pin No.       | Name                | Туре  |                                                                                                                        |

| 1             | PA-CNTL             | O/P   | DAC0 output to control PA power.                                                                                       |

| 2             | TX FB               | I/P   | Tx feedback input signal.                                                                                              |

| 3             | -                   | NC    | do not make any connection to this pin                                                                                 |

| 4             | V <sub>DD</sub> Tx  | Power | Power supply to Tx IF and RF circuits.                                                                                 |

| 5             | -                   | NC    | do not make any connection to this pin                                                                                 |

| 6             | $V_{SS} Tx$         | Power | Return for $V_{DD}$ Tx, good decoupling required.                                                                      |

| 7             | TXPLL               | O/P   | Tx Phase Detector output.                                                                                              |

| 8             | RF IN A             | I/P   | RF input A for received signal.                                                                                        |

| 9             | RF IN B             | I/P   | RF input B for received signal.                                                                                        |

|               |                     |       | (RF IN A and RF IN B are a differential input)                                                                         |

| 10            | V <sub>DD</sub> Rx1 | Power | Power supply to Rx RF circuits.                                                                                        |

| 11            | IF OUT              | O/P   | Output to the external IF filter.                                                                                      |

| 12            | V <sub>ss</sub> Rx1 | Power | Return for $V_{DD}$ Rx1, good decoupling required.                                                                     |

| 13            | V <sub>SS</sub> Rx2 | Power | Return for $V_{DD}$ Rx2, good decoupling required.                                                                     |

| 14            | LNA ON              | O/P   | Digital output to turn on external LNA block.                                                                          |

| 15            | V <sub>DD</sub> Rx2 | Power | Power supply to Rx IF circuits.                                                                                        |

| 16            | IF IN               | I/P   | Input from the external IF filter.                                                                                     |

| 17            | A5                  | I/P   | Register address select logic inputs.                                                                                  |

| 18            | A4                  | I/P   | n                                                                                                                      |

| 19            | A3                  | I/P   | n                                                                                                                      |

| 20            | A2                  | I/P   | n                                                                                                                      |

| 21            | A1                  | I/P   | n                                                                                                                      |

| 22            | A0                  | I/P   | n                                                                                                                      |

| 23            | $V_{\text{DD}}$ Dig | Power | Power supply to base band digital circuits.                                                                            |

| 24            | $V_{DD}$ Ana        | Power | Power supply to aux ADC, DAC, OP1/2 circuits.                                                                          |

| 25            | V <sub>BIAS</sub>   | O/P   | Output of internal bias generator, decouple to $V_{\rm SS}$ Ana.                                                       |

| 26            | V <sub>SS</sub> Ana | Power | Return for $V_{DD}$ Ana, good decoupling required.                                                                     |

| 27            | V <sub>ss</sub> Dig | Power | Return for $V_{DD}$ Dig, good decoupling required.                                                                     |

| 28            | V <sub>SS</sub> H   | Power | Return for $V_{DD}$ H, good decoupling required.                                                                       |

| 29            | RDN                 | I/P   | Read. An active low logic level input used to control the reading of data from the modem into the controlling $\mu$ C. |

| Package<br>Q1 | Signa      | I     | Description                                                                                                                                                                                                                       |

|---------------|------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30            | WRN        | I/P   | Write. An active low logic level input used to control the writing of data into the modem from the controlling $\mu$ C.                                                                                                           |

| 31            | CSN        | I/P   | Chip Select. An active low logic level input used to enable a data read or write operation.                                                                                                                                       |

| 32            | IRQN       | O/P   | A 'wire-ORable' output for connection to the host<br>Interrupt Request input. This output has a low<br>impedance pull down to Vss when active and is<br>high impedance when inactive. An external<br>pullup resistor is required. |

| 33            | $V_{DD}$ H | Power | Power supply to host interface and 2.5V regulator circuit.                                                                                                                                                                        |

| 34            | D7         | BI    | Tri-state µC interface data line.                                                                                                                                                                                                 |

| 35            | D6         | BI    | н                                                                                                                                                                                                                                 |

| 36            | D5         | BI    | и                                                                                                                                                                                                                                 |

| 37            | D4         | BI    | и                                                                                                                                                                                                                                 |

| 38            | D3         | BI    | и                                                                                                                                                                                                                                 |

| 39            | D2         | BI    | п                                                                                                                                                                                                                                 |

| 40            | D1         | BI    | п                                                                                                                                                                                                                                 |

| 41            | D0         | BI    | п                                                                                                                                                                                                                                 |

| 42            | V-CONT     | O/P   | Control signal for external regulating transistor.                                                                                                                                                                                |

| 43            | DAC3       | O/P   | Aux. D/A 3 output.                                                                                                                                                                                                                |

| 44            | DAC2       | O/P   | Aux. D/A 2 output.                                                                                                                                                                                                                |

| 45            | ADC5       | I/P   | Aux. A/D 5 input.                                                                                                                                                                                                                 |

| 46            | ADC4       | I/P   | Aux. A/D 4 input.                                                                                                                                                                                                                 |

| 47            | OP2T       | O/P   | Uncommitted op-amp 2 output, internally connected to ADC3.                                                                                                                                                                        |

| 48            | OP2N       | I/P   | Uncommitted op-amp 2 negative input.                                                                                                                                                                                              |

| 49            | OP2P       | I/P   | Uncommitted op-amp 2 positive input.                                                                                                                                                                                              |

| 50            | OP1T       | O/P   | Uncommitted op-amp 1 output, internally connected to ADC2.                                                                                                                                                                        |

| 51            | OP1N       | I/P   | Uncommitted op-amp 1 negative input.                                                                                                                                                                                              |

| 52            | OP1P       | I/P   | Uncommitted op-amp 1 positive input.                                                                                                                                                                                              |

| 53            | REFCLK     | I/P   | Master clock input from external TCXO.                                                                                                                                                                                            |

| 54            | TCXO-CNTL  | O/P   | DAC1 output to control TCXO.                                                                                                                                                                                                      |

| 55            | TCXO-TEMP  | I/P   | A/D input to measure TCXO temperature, internally connected to ADC1.                                                                                                                                                              |

| 56            | LOCLKN     | I/P   | Inverted input from the RF Oscillator circuit.                                                                                                                                                                                    |

| 57            | LOCLK      | I/P   | Input from the RF Oscillator circuit.                                                                                                                                                                                             |

| Package<br>Q1           | Signal              |       | Description                                                                                                                                                                                |

|-------------------------|---------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 58                      | IFCLKN I/P          |       | Inverting Input from IF Oscillator (if balanced<br>input is used). If IFCLK is used as a single<br>ended input this pin should be connected to the<br>VCO ground. The pin is a.c. coupled. |

| 59                      | MAINPLL             | O/P   | Main PLL output, connect to external filter.                                                                                                                                               |

| 60                      | V <sub>DD</sub> VCO | Power | Power supply to the VCO charge pump.                                                                                                                                                       |

| 61                      | AUXPLL              | O/P   | Aux PLL output, connect to external filter.                                                                                                                                                |

| 62                      | $V_{DD}$ Synth      | Power | Power supply to synthesiser circuits.                                                                                                                                                      |

| 63                      | IFCLK               | I/P   | Input from the IF Oscillator circuit.                                                                                                                                                      |

| 64                      | PA-TEMP             | I/P   | A/D input to measure PA temperature, internally connected to ADC0.                                                                                                                         |

| Exposed<br>Metal<br>Pad | SUB                 | Power | The Exposed Metal Pad must be electrically connected to Analogue Ground (V <sub>SS</sub> Ana).                                                                                             |

Total = 65 Pins (64 pins and central metal ground pad)

Notes:

$$I/P = Input$$

$O/P = Output$

$BI = Bidirectional$

$T/S = 3$ -state Output

$NC = No Connection$

# 4 External Components

Note: In the following sections specified, component tolerances indicate a minimum requirement, components with better tolerances may be substituted.

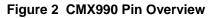

# 4.1 Layout Recommendations

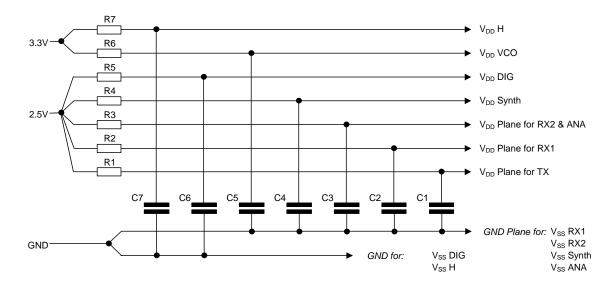

To achieve good noise performance, decoupling of V<sub>BIAS</sub> and all supplies is very important as is protection of the receive path from extraneous in-band signals. It is recommended that the printed circuit board is laid out with a ground plane in the CMX990 area to provide a low impedance connection between the V<sub>SS</sub> pins and all V<sub>DD</sub> and V<sub>BIAS</sub> decoupling capacitors. As shown in Figure 12 the ground for V<sub>SS</sub> digital signals should be kept separate from that used for analogue / RF signals. The digital ground should be routed back to a suitable star point.

The CMX990 package has a metal area connected to ground under the main body of the IC. This pad should be connected to analogue ground. It will be noted that caution should be exercised over placing any tracks underneath the CMX990. Furthermore, any vias other than ground should be avoided under the device unless manufacturers can guarantee that the exposed ground pad on the CMX990 will not cause short circuits while a good electrical contact is maintained between the device and ground.

Apart from these recommendations normal RF layout practices should apply, such as keeping tracks as short as possible, equal track lengths on differential inputs, care with coupling between tracks etc.

### 4.2 **Processor Interface**

$\mu C$  Address Bus

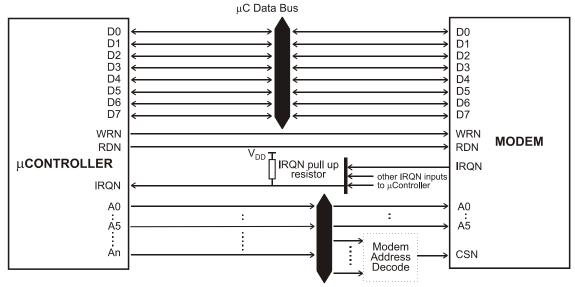

Figure 3 Recommended External Configuration - Processor Interface

The receiver circuits can be affected by digital noise from the host interface. Screening of RF circuits is recommended along with filtering of the digital lines.  $100\Omega$  series resistors with 56pF to ground on the CMX990 side of the resistor is suggested however designers are likely to find requirements will vary in individual designs depending on layout, screening arrangements and host. Care should be taken to ensure digital control lines A0-A5 are kept away from the IF input on pin 16 as these address lines are adjacent on pins 17-22.

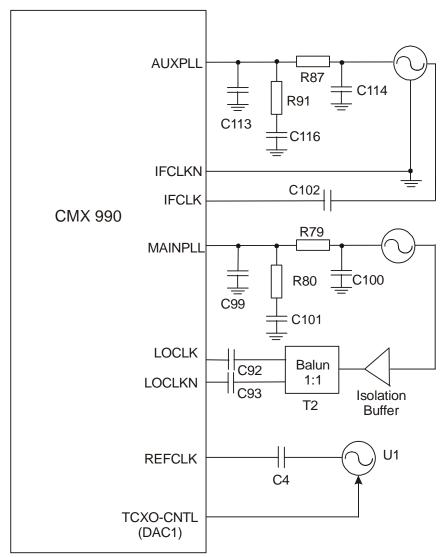

# 4.3 Synthesiser and TCXO

The CMX990 synthesiser section provides two independent synthesisers. The PLLs implement a Type II loop with a phase / frequency phase detector providing an output of a charge pump current. Various types of loop filter can be used and should be optimised for VCO gain of a particular design. Figure 4 gives typical configuration and values.

| C4<br>C92 | 1 nF<br>1 nF | T | 2  | TC1-1-13M+     |

|-----------|--------------|---|----|----------------|

| C93       | 1 nF         | R | 79 | 470 Ω          |

| C99       | 100 nF       | R | 80 | 1.0 k $\Omega$ |

| C100      | 27 nF        | R | 87 | 12 kΩ          |

| C101      | 680 nF       | R | 91 | 1.5 kΩ         |

| C102      | 1 nF         |   |    |                |

| C113      | 22 nF        |   |    |                |

| C114      | 1 nF         | U | 1  | See notes      |

| C116      | 150 nF       |   |    |                |

|           |              |   |    |                |

Notes:

- 1 Resistors  $\pm$ 1%, capacitors  $\pm$ 5% unless otherwise stated.

- 2 For optimum lock time / phase noise it is recommended C113 and C116 use a low piezo type such as PPS film; optimum performance is not guaranteed with X7R or Y5V types.

- 3 U1 Should be a VCTCXO or TCXO depending on application requirements. A typical device is the Golledge GTXO-83. The CMX990 has a high impedance input suitable for use with oscillators with clipped sine wave output. An external DC blocking capacitor (as shown, C4) is required.

- 4 Ground currents on the board can result in contamination of the IFCLK signal, so for the best possible results use a balun to connect the differential inputs IFCLK and IFCLKN to the VCO. However, adequate elimination of ground noise may be achieved by connection of the IFCLKN to the ground of the VCO.

- 5 The IFCLK pin needs to be ac coupled. In the case of differential drive it is recommended that external dcblocking capacitors for both IFCLK and IFCLKN be used so as to provide equal paths for both complementary signals.

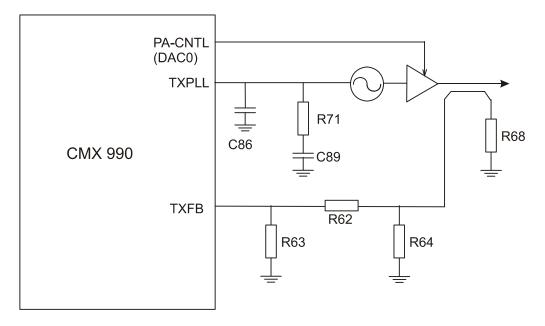

# 4.4 Transmitter

The CMX990 transmitter uses an offset phase-locked loop to accurately modulate RF signals. Details are contained in subsequent sections of this document. The components used around the CMX990 will depend on application requirements however a typical configuration is shown in Figure 5.

#### Figure 5 Recommended External Components - Transmit

| C86<br>C89 | 15 nF<br>68 nF |  | R63 | 18 Ω<br>270 Ω<br>270 Ω<br>47 Ω<br>36 Ω |

|------------|----------------|--|-----|----------------------------------------|

|------------|----------------|--|-----|----------------------------------------|

Notes:

1 Resistors  $\pm$ 1%, capacitors  $\pm$ 5% unless otherwise stated.

- 2 The coupler may be a packaged type (e.g. 0869CP14A090 for 800MHz operation), a lumped element type or printed on the PCB; alternatively a sample of the output can be obtained with a resistive or capacitive tap.

- 3 Tx loop filter components need to be optimised for the selected VCO.

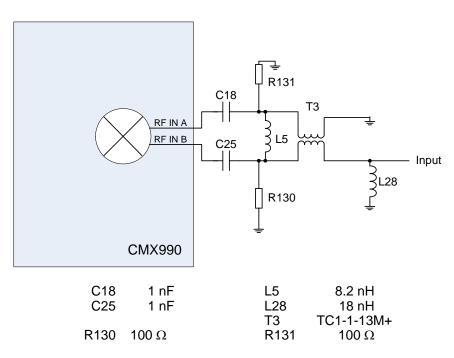

### 4.5 Receiver

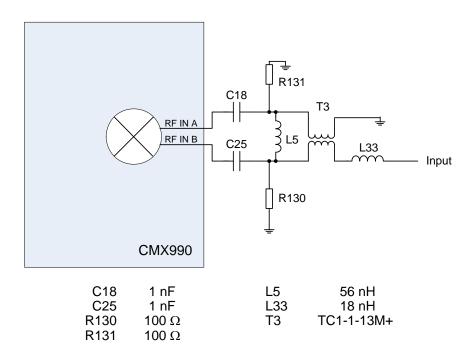

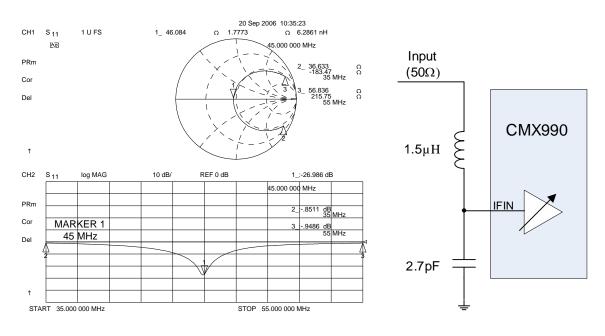

The receiver relies on external LNA, filtering and T/R switch; details can be found in the following sections. The 1<sup>st</sup> mixer in the CMX990 has a differential input. To ensure optimum performance a balun is required when driving from typical single un-balanced LNAs or filters. The balun may be a transformer type or implemented using LC networks.

The input impedance to the CMX990 mixer is relatively high so suitable matching components around the balun should be selected for the desired operating frequency to provide a match to the desired impedance e.g.  $50\Omega$ . Figure 6 shows a typical configuration for 800 - 840MHz operation and Figure 8 for 360-490MHz operation.

Two matching configurations can be used for either best noise figure or best inter-modulation performance. In configuration 1 two 100ohm resistors are fitted (R131 and R130). These define the matching impedance but result in a small loss of signal although as the input is essentially a voltage swing the loss is not as much as might be expected. This configuration gives optimum inter-modulation performance. The alternative arrangement is to omit the resistors and match the impedance directly. This results in a small degradation in inter-modulation but provides an improved noise figure. Typical results for 800MHz operation are:

|                                   | Configuration 1 | Configuration 2 |

|-----------------------------------|-----------------|-----------------|

| Noise Figure (See Note 17         | 15dB            | 13dB            |

| Section 7.1.3, page 91)           |                 |                 |

| Input Third Order Intercept Point | +9.5dBm         | +6.5dBm         |

| 1dB Compression point             | -7dBm           | -9.5dBm         |

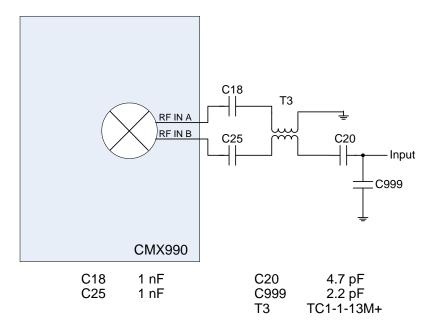

Figure 6 Recommended External Components (800MHz) – Receive Mixer Configuration 1

Notes:

1 Resistors  $\pm$ 1%, capacitors and inductors  $\pm$ 5% unless otherwise stated.

2 Values for L5, L28 are typical matching values for 800MHz operation.

<sup>© 2008</sup> CML Microsystems Plc

# Figure 7 Recommended External Components (800MHz) – Receive Mixer Configuration 2

Notes:

- 1 Resistors  $\pm$ 1%, capacitors and inductors  $\pm$ 5% unless otherwise stated.

- 2 C20, C999 values are typical values for 800MHz operation.

# Figure 8 Recommended External Components (400MHz) – Receive Mixer Configuration 1

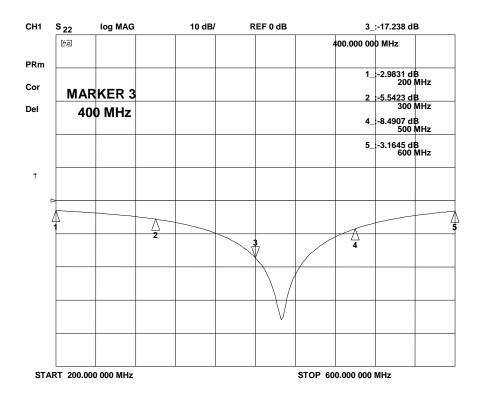

### Figure 9 400MHz input match return loss with matching as Figure 8.

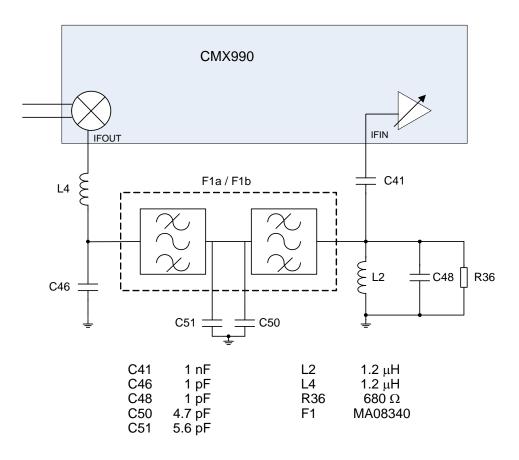

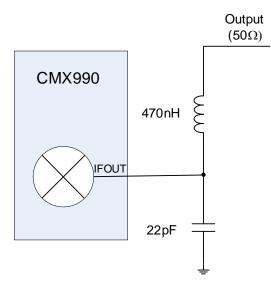

The output of the CMX990 first receive mixer should be at an IF in the range 44 to 46MHz. Only IF's in this range will benefit from the image reject functionality of the mixer. Between the mixer and IF amplifier stages a crystal filter is recommended. This filter is to protect the IF amplifier and subsequent stages from off-channel signals. Matching arrangements will vary, being dependant on the filter used, however an example of a typical configuration for a 45MHz IF is given in Figure 10.

#### Figure 10 Recommended External Components – Receive IF Section

#### Notes:

- 1 Resistors  $\pm$ 1%, capacitors and inductors  $\pm$ 5% or better unless otherwise stated.

- F1 is a SMT 4 pole crystal filter implemented as a matched pair with a ±6kHz pass-band, load 500R//4pF, Cc = 13pF. The part is available from Golledge Electronics (www.golledge.com). Other parts may be equally suitable although matching arrangements will vary and different filters are recommended for different channel bandwidths and performance requirements. When selecting and matching a crystal filter care should be taken to ensure a flat pass-band and the performance should always be checked with a specific PCB layout. For further information on filter selection see section 6.5.1 and Table 3.

# 4.6 Power Supply Decoupling and Layout

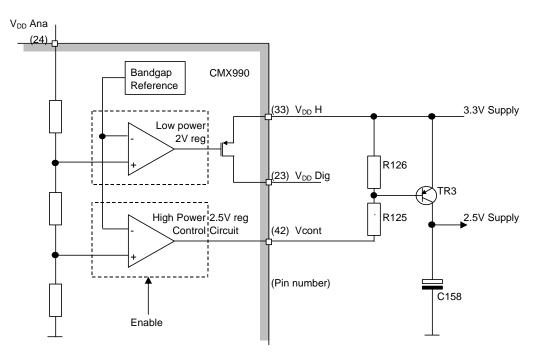

The CMX990 has dual supply voltages: a 3.3V supply is required for the PLLs and charge pump circuits and for the digital I/O pads, and a 2.5V supply (with separate decoupling) is required for the RF sections (Rx1, Rx2, Tx) as well as the baseband analogue and digital circuits.

The 3.3V supply must be provided by an external regulator circuit. The 2.5V supply may be provided by an external regulator, or alternatively may be derived from the 3.3V supply using an off-chip low saturation voltage transistor in conjunction with the on-chip control circuit (enabled by register PowerUp1 bit 5) - an example of this arrangement is shown in Figure 11. Whichever method is used to generate the 2.5V it is essential that all the circuits relying on this supply are powered down before this 2.5V source is turned off. The CMX990 will then allow the supply to drop to 2.0V, at which point it will be clamped by a separate on-chip micropower regulator. This is done so that the data in the on-chip registers and memories is not lost. The main 2.5V regulator circuit must be powered up again and allowed to settle before any RF or analogue circuitry, or the clock to the internal logic, is enabled. In other words, PowerUp1 (\$04 - bits 7-6 and 4-0) and PowerUp2 (\$05 - bits 7-4 and 0) must be set low whenever the 2.5V supply is unavailable.

The circuit shown in Figure 11 is an example, and will require that the 3.3V supply is regulated to within +/- 5%. This is necessary to ensure that the PNP transistor shown (TR3) does not enter saturation, taking worst case ambient conditions and bandgap / component tolerances into account.

#### Figure 11 Voltage Regulator Connections

| C158 | 100 µF   | R125 | 330 Ω |

|------|----------|------|-------|

| TR3  | PMBT4403 | R126 | 47 kΩ |

Resistors  $\pm$ 5%, capacitors  $\pm$ 20% or better.

| C1 | 10 nF | R1 | 2.2 Ω |

|----|-------|----|-------|

| C2 | 10 nF | R2 | 2.2 Ω |

| C3 | 10 nF | R3 | 3.3 Ω |

| C4 | 10 nF | R4 | 10 Ω  |

| C5 | 10 nF | R5 | 10 Ω  |

| C6 | 10 nF | R6 | 10 Ω  |

| C7 | 10 nF | R7 | 10 Ω  |

|    |       |    |       |

Resistors  $\pm$ 5%, capacitors  $\pm$ 20% unless otherwise stated.

#### Note:

It is expected that low frequency interference on the 3.3 Volt supply will be removed by active regulation; although a large capacitor is an alternative it may require more board space and so may not be preferred by the user. It is particularly important, however, to ensure that there is no interference from the  $V_{DD}$  H (which supplies the digital I/O) or from any other circuit that may use the 3.3V supply (such as a microprocessor) to sensitive analogue supplies like  $V_{DD}$  VCO or, importantly, the external RF VCO supplies.

The supply decoupling shown is intended for RF noise suppression only. It is necessary to have a small series impedance prior to the decoupling capacitor for the decoupling to work efficiently with physically small capacitors; this may be cost effectively done with the resistor and capacitor values shown. The use of resistors results in a small DC voltage drops (up to approx 0.1V). Choosing resistor values approximately inversely proportional to the DC current requirements of each supply, ensures the DC voltage drop on each supply are reasonably matched. The internal regulator uses  $V_{DD}$  ANA as its feedback, so this will compensate to reduce this voltage drop. In any case the DC voltage change that results is well within the design tolerance of the device. If higher impedance resistors are used (not recommended) then greater care will be needed to ensure the supply voltages are maintained within tolerance, even when individual parts of the device are enabled or disabled.

# 5 General Description

The CMX990 comprises a baseband modem and an associated RF section to provide a GMSK data modem including the ability to support the Mobitex air-interface. Device control and status is transferred via a set of memory mapped registers. An overview of the operation of the Modem is provided in section 5.1 and the RF / IF functions in section 5.2. These are followed by detailed description of the Host  $\mu$ C interface in section 5.3. Further application information is contained in section 6.

# 5.1 Baseband Modem

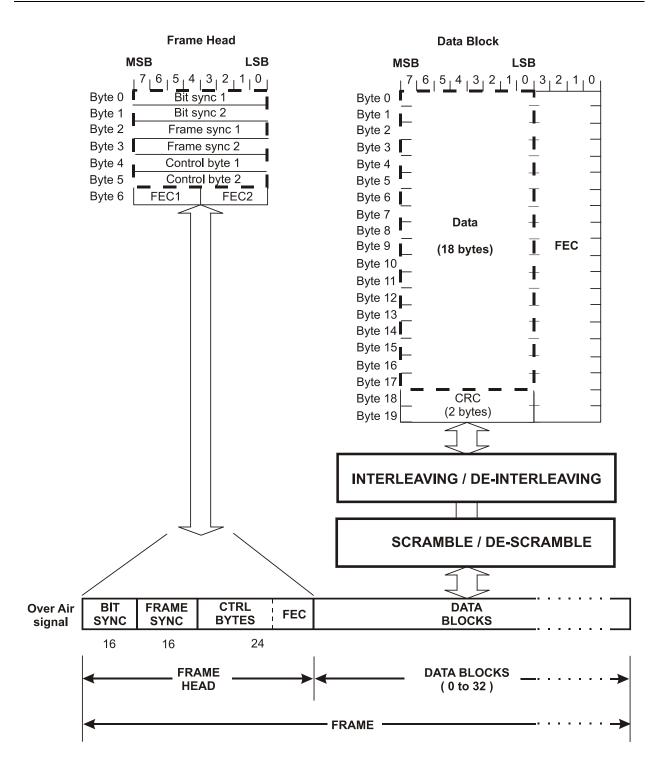

This section has been designed to be compliant with the appropriate sections of the "Mobitex Interface Specification" including Short Block Frame formatting for the extended battery saving protocol. References to 'data blocks' in this section apply to both the normal (18 byte) Data Block and the smaller (4 byte) Short Data Block.

The function of this section is further divided into Receive and Transmit sections that operate in half duplex.

In transmit mode the data may be encoded according to the Mobitex standard. This includes the calculation and appending of a Cyclic Redundancy Checksum (CRC) and Forward Error Correction (FEC), and Interleaving to reduce the effects of noise (note these functions can be bypassed if required). The subsequent NRZ data stream is then filtered digitally and the resulting digital data processed to produce an I and Q signal as the baseband form of the required FM signal. These are converted to analogue signals via D-A converters and passed to the RF section for subsequent transmission.

In receive mode, the analogue I and Q representations, at baseband, of the FM signal from the RF section are converted to digital signals via A-D converters. These signals are digitally filtered to suppress the adjacent channels and demodulated digitally. The resulting signal is then filtered, to optimise the signal to noise performance, before slicing to resolve into a digital bit stream. Mobitex specified error correction and de-interleaving can be applied and the resulting data is presented for transfer to an external processor.

### 5.1.1 Description of Blocks

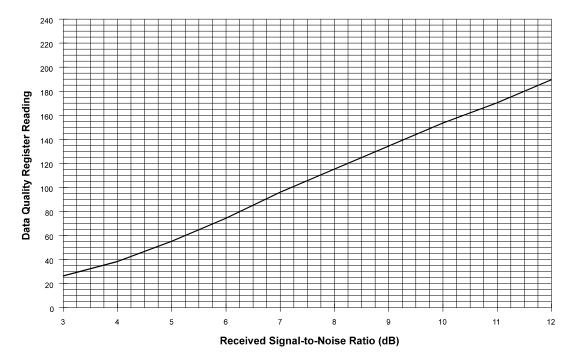

#### **Status and Data Quality Registers**

8-bit registers which the  $\mu$ C can read to determine the status of the modem and the received data quality.

#### Command, Mode and Control Registers

The values written by the  $\mu$ C to these 8-bit registers control the operation of the modem.

#### Data Buffer

An 18-byte buffer used to hold receive or transmit data to or from the  $\mu$ C.

#### Frame Assembly / Disassembly

Each of these blocks consists of 4 circuits which generate (in transmit mode) or check (in receive mode) the bits of both short and normal Mobitex data blocks.

#### CRC Generator/Checker

A circuit which generates (in transmit) or checks (in receive) the CRC bits, which are included in transmitted Mobitex data blocks so that the receive modem can detect transmission errors.

#### FEC Generator/Checker

In transmit mode this circuit calculates and adds the FEC (4 bits) to each byte presented to it. In receive mode the FEC information is used to correct most transmission errors that have occurred in Mobitex data blocks or in the Frame Head control bytes.

#### Interleave/De-interleave Buffer

This circuit interleaves data bits within a data block before transmission and de-interleaves the received data block so that the FEC system is best able to handle short noise bursts or signal fades.

#### Scramble/De-scramble

This block may be optionally used to scramble/de-scramble the transmitted and received data blocks. It does this by modulating the data with a 511-bit pseudorandom sequence, as described in section 6.2.4. Scrambling improves the transmitted spectrum, especially when repetitive sequences are to be transmitted.

### Frame Sync Detect

This circuit, which is only active in receive mode, is used to look for the user specified 16-bit Frame Synchronisation pattern which is transmitted to mark the start of every frame.

#### **Tx Modulator and Low Pass Filter**

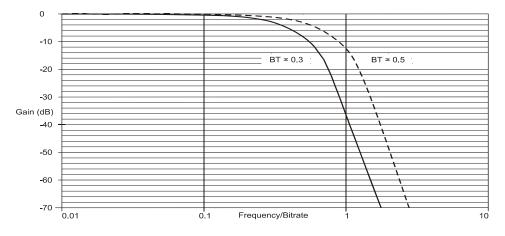

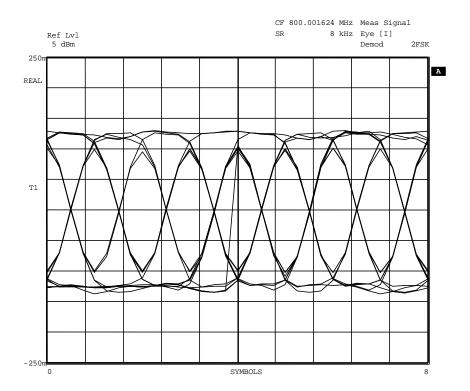

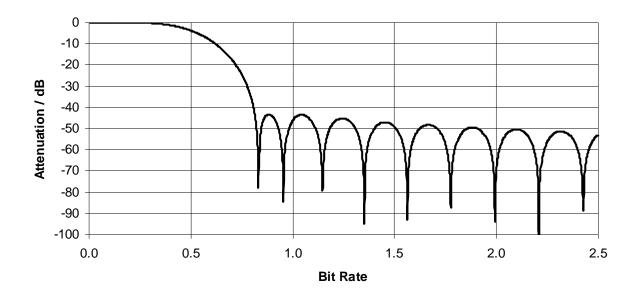

The filter is used in transmit mode and is a low pass transitional Gaussian filter having a 3dB loss at 0.27, 0.3 or 0.5 times the bit rate (BT=0.27, 0.3 or 0.5). See Figure 13. This filter eliminates the high frequency components which would otherwise cause interference into adjacent radio channels. The BT=0.27 option is added as means of meeting the more stringent regulatory requirements for Adjacent Channel Power (for example EN 300 113).

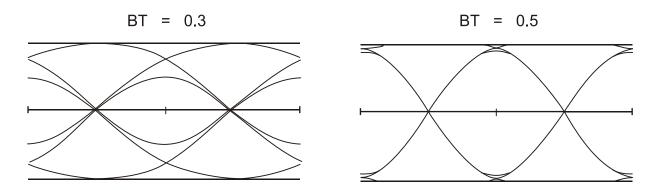

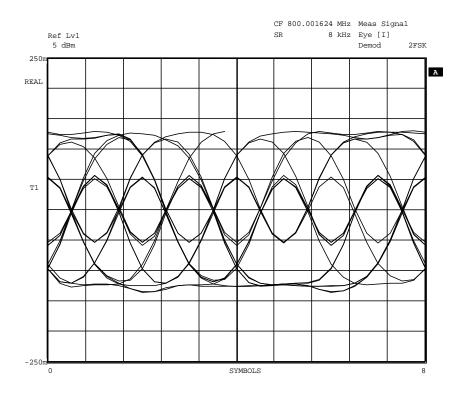

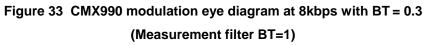

The unmodulated baseband 'eye' diagrams of the transmitted signal is shown in Figure 14.

The Tx Modulator converts the baseband signal into an I and Q form which is passed to the Tx IF stage.

Figure 13 Typical Tx Baseband Filter Response

<sup>© 2008</sup> CML Microsystems Plc

Figure 14 Baseband Transmitter Signal Eye Diagrams

### **Rx Low Pass Filter**

This filter is a low pass transitional Gaussian filter having a 3dB loss at 0.56 times the bit rate (BT=0.56). It is used to reject HF noise to improve the BER.

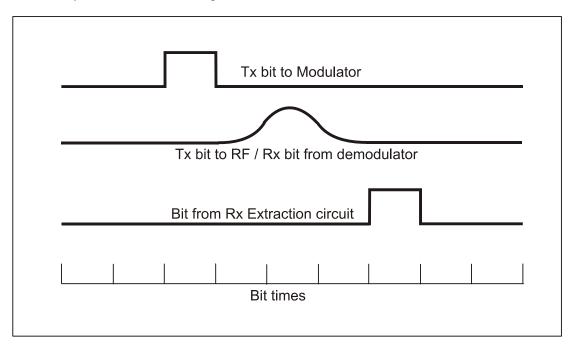

#### Level Track and DPLL

These circuits, which operate only in receive mode, extract a bit rate clock from the received signal and measure the received signal amplitude and dc offset. This information is then used to extract the received bits and also to provide an input to the received Data Quality measuring circuit.

#### 5.1.2 Modem - µC Interaction

In general, data is transmitted over air in the form of messages, or 'Frames', consisting of a 'Frame Head' optionally followed by one or more formatted data blocks. The Frame Head includes a Frame Synchronisation pattern designed to allow the receiving modem to identify the start of a frame. The following data blocks are constructed from the 'raw' data using a combination of CRC (Cyclic Redundancy Checksum) generation, Forward Error Correction coding, Interleaving and Scrambling. Details of the message formats handled by this modem are given in section 5.1.3 and further information is given in sections 6.2, 6.2.3, 6.2.4 and 6.3.

To reduce the processing load on the host  $\mu$ C, this modem has been designed to perform as much as possible of the computationally intensive work involved in Frame formatting and de-formatting and (when in receive mode) in searching for and synchronising onto the Frame Head. In normal operation the modem will only require servicing by the  $\mu$ C once per received or transmitted data block.

Thus, to transmit a block, the host  $\mu$ C has only to load the unformatted (raw) binary data into the modem's data buffer then instruct the modem to format and transmit that data. The modem will then calculate and add the CRC bits as required, encode the result with Forward Error Correction coding, interleave then scramble the bits before transmission.

In receive mode, the modem can be instructed to assemble a block's worth of received bits, de-scramble and de-interleave the bits, check and correct them (using the FEC coding) and check the resulting CRC before placing the received binary data into the Data Buffer for the  $\mu$ C to read.

The modem can also handle the transmission and reception of unformatted data, to allow the transmission of special Bit and Frame Synchronisation sequences, test patterns or custom data formats.

#### 5.1.3 Data Formats

#### Raw data

If required the user may transmit and receive raw data. This is transferred between the host and device a byte (8 bits) at a time.

Note that it is important to have established frame synchronisation before receiving data to enable the receiving device to decode synchronously. The user may add error detection and correction by way of algorithms performed on the host device.

#### **General Purpose Formats**

In a proprietary system the user may employ the data elements provided by this device to construct a custom, over-air data structure.

For example, 16 bits of bit sync + 2 bytes of frame sync + 4 bytes of receiver and sender address + n data blocks would be sent as:

TQB (bit and frame sync) + TQB (addresses) + (n x TDB) + TSB

And received as:

SFS + RSB + RSB + RSB + RSB + (n x RDB)

#### **Mobitex Frame Structure**

The Mobitex format for transmitted data is in the form of a Frame Head immediately followed by either 1 Short Data Block or a number of Data Blocks (0 to 32).

The Frame Head consists of 7 bytes:

2 bytes of bit sync: 1100110011001100 from base, 0011001100110011 from mobile bits are transmitted from left to right

2 bytes of frame sync: System specific.

2 bytes of control data.

1 byte of FEC code, 4 bits for each of the control bytes: bits 7-4 (leftmost) operate on the first control byte. bits 3-0 (rightmost) operate on the second control byte.

Each byte in the Frame Head is transmitted bit 7 (MSB) first to bit 0 (LSB) last.

The normal and short data blocks consist of:

18 bytes of data (Data Block) **OR** 4 bytes of data (Short Data Block).

2 bytes of CRC calculated from the data bytes.

4 bits of FEC code for each of the data and CRC bytes

The resulting data block bits are interleaved and scrambled before transmission.

Figure 15 shows how the over air signal is built up from Frame Sync and Bit Sync patterns, Control bytes and Data Blocks. The binary data transferred between the modem and the host  $\mu$ C is that shown enclosed by the thick dashed rectangles near the top of the diagram.

<sup>© 2008</sup> CML Microsystems Plc

#### 5.1.4 Modem Interface

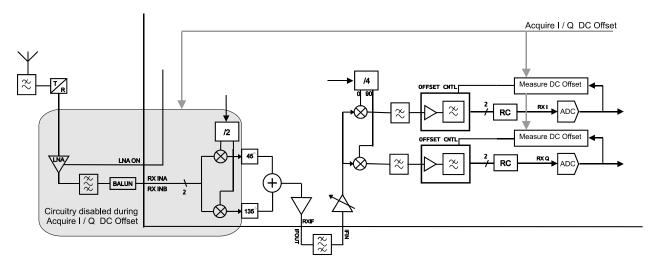

The data modem interfaces to the RF circuits using I and Q format for both transmit and receiver. Operation can be seen in Figure 1. On the transmitter the frame assembly block feeds data to the modulator which creates I and Q data streams for internal digital to analogue converters (DAC). The

output of the DAC is differential and is filtered to remove spurious responses before being passed to the analogue RF stages.

The input to the receiver section of the modem comes from the analogue receiver stages as a differential signal in I/Q format. Anti-alias filters are used prior to analogue to digital conversion (ADC). The analogue circuits include the ability to minimise DC offset errors, thus optimising the dynamic range of the signal. Further DC offset correction is applied in the signal processing after the ADC (for further details see section 6.5.2). Following the ADC FIR channel filters (see section 6.5.1) are applied prior to demodulation and associated timing recovery and synchronisation.

# 5.2 RF and IF

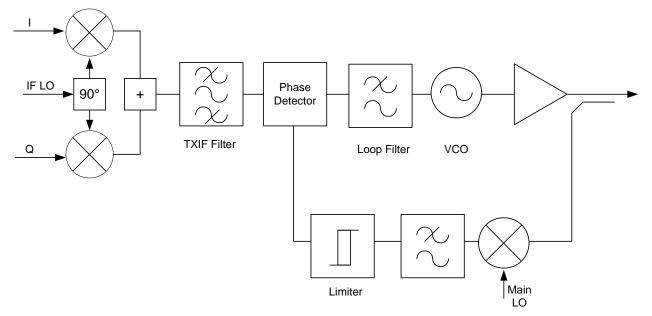

The CMX990 is a broadband RF modem system. The RF section can support transmission and reception between 400MHz and 1GHz.

The transmitter and receiver parts are designed for half duplex operation so should be operated mutually exclusively - normally the non-utilised part being powered down when not in use. For single antenna operation an external transmit/receive (T/R) switch is required.

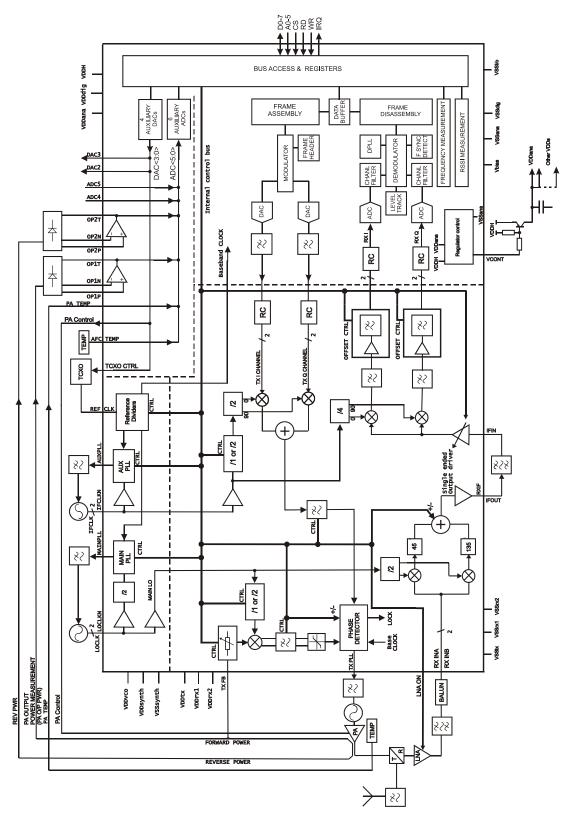

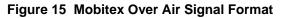

The transmitter takes the baseband I and Q signals from the modem (See section 5.1 and Figure 1) and up-converts them via a quadrature modulator to a suitable Intermediate Frequency (IF). An offset PLL is then used to control an external VCO which translates the IF to the desired transmission frequency. The output of the VCO is sampled, usually after amplification, and mixed down to the IF; this mixed down signal is then phase/frequency compared with the IF signal from the quadrature modulator. The output of the phase comparator is fed to an external loop filter, which controls the VCO thereby closing the loop. The VCO output then will be an FM signal at the required RF frequency having a low out-of-band spurious response typical of VCO driven transmitters whilst guaranteeing a modulation index of exactly 0.5. The output of the VCO requires amplifying with an external PA (Power Amplifier).

The receiver requires use of an external LNA with some pre-filtering and an external balun. The differential output from the balun is down converted by an image reject mixer to a suitable IF (typically 45 MHz). The single ended IF signal is filtered with an external filter to remove spurious signals and this goes into an AGC stage with a gain control range of 45dB. The output of the AGC is mixed down to I and Q signals at baseband via quadrature mixers. The I and Q signals are amplified and filtered to remove any signals that may alias with the subsequent A-D sampling. The amplifier also has a coarse offset removal system to allow the approximate nulling of DC offsets developed in the circuits that may restrict the dynamic range in the subsequent processing.

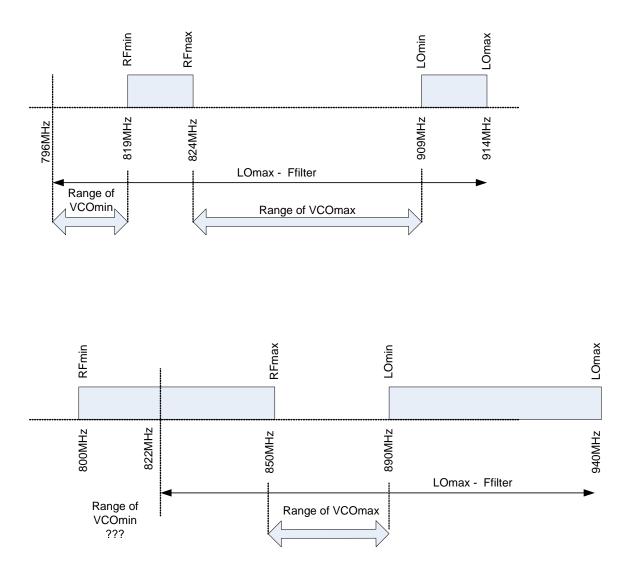

As with any RF system care is required with frequency planning to minimise component count, avoid spurious responses etc. A examples of typical frequency planning is shown in Figure 17 and further discussion is given in section 6.5.1.

### 5.2.1 Transmitter Section

I and Q signals from the Modem block are base-band representations of the required modulated RF signal. These are up-converted by a quadrature modulator stage to a suitable IF. The summed output from this stage has the required modulation index but at a lower frequency (TXIF, typically 45MHz or 90MHz) than that required for transmission. The CMX990 provides either divide by 2 or divide by 4 from the programmed auxiliary local oscillator frequency to aid IF selection.

An Offset Phase Locked Loop (O-PLL) is used to translate this modulated TXIF signal to the appropriate carrier frequency. The O-PLL architecture is shown in Figure 16. The O-PLL works as a feedback loop with the TXIF signal as it's reference input. Considering the forward path the final frequency modulation is generated by a VCO which then drives a power amplifier to generate the required output level. The full power signal is sampled and then attenuated externally and / or on chip. For the signal sampling a directional coupler is recommended although a simple sample of the PA output can be used. The

attenuated signal is then down-mixed with the main LO signal to a frequency nominally the same as the TXIF value. The resulting signal is low-pass filtered to remove unwanted mixer products. This filter can be set to two values depending on the TXIF in use (section 5.3.11). A high gain limiting amplifier is then used to enable the loop to have a high dynamic range and to lock-in even when the transmitted signal is very small, e.g. when just starting to ramp up. The output of the limiting amplifier is then phase/frequency compared with the TXIF reference signal from the modulator, the charge pump output being passed off chip into a suitable loop filter. The filtered output controls the VCO with its nominal frequency set to the middle of the required transmission band. When the loop is locked, the VCO follows the frequency modulations of the reference signal so as to give an exact modulation index of 0.5 whilst having the low spurii in transmission typical of a VCO based system.

#### Figure 16 Block Diagram of Offset Phase Locked Loop Transmitter

As noted above, the output of the VCO is generally amplified with a Power Amplifier. A special feature of one of the Auxiliary D-A converters may be used to control the ramping of the power amplifier optimally should this be required. This feature is explained in section 5.3.6. The Auxiliary A-D section can also be used for sensing the forward and reverse power values, and the PA temperature should these features be required.

Further information on the transmitter operation can be found in section 6.4.

Figure 17 Simplified Block Diagram of CMX990 Showing Example Frequency Plan for 864-870MHz (Rx) / 819-825MHz (Tx) band

#### 5.2.2 Receiver Section

It is expected that the signal from the T/R switch will be amplified via an external LNA. The use and positioning of an image reject filtering is up to the radio designer. As a guide, the Mobitex specification requires a minimum of 45dB of first image rejection of which at least 30dB will be provided by the on-chip image reject mixer stage. The design is optimised with an LNA gain of about 15dB. It has been assumed that there is some insertion loss prior to the LNA; but an overall noise figure of 4dB and gain of 10dB (approx.) is achieved by the circuits preceding the CMX990. A digital control signal is available from the chip which should be used to enable/disable the LNA. A balun must be used to produce a differential signal to the first mixer on the chip.

The Image Reject Mixer down-converts the signal to 45 MHz, although this frequency may be changed slightly if necessary, for example when used in regions where there may be conflicts with local broadcast transmissions. The resulting IF is then output from the chip as a single ended signal for filtering. A relatively low cost crystal filter can be used to remove signals outside the channel bandwidth. The specification of this filter will vary with the intented application. For detailed filter requirements see Table 3 (section 6.5.1).

The IF-signal from the filter is then taken back on chip to an amplifier stage which includes gain control, thus allowing Automatic Gain Control (AGC) to be implemented. The AGC is adjustable in steps of 15dB from -5dB to +40dB and can be adjusted automatically by the chip or may be controlled by instruction from the host processor.

The output from the AGC is then mixed down to baseband, by a quadrature mixer stage, to produce I and Q signals. These are then filtered, to remove unwanted mixer products, spurii and remaining blocking signals and at the same time amplified to a suitable level for subsequent A-D conversion. The filters also precondition the signal to prevent aliasing with the A-D sample frequency. Channel filtering is provided digitally in the baseband processing section (see section 6.5.1).

# 5.3 Memory Map, Interface and Register Functions

| The following is a summary of the internal registers as seen by the host, details of operation may be found |

|-------------------------------------------------------------------------------------------------------------|

| in the relevant section.                                                                                    |

|                                                                                                             |

| Address | Read              | Write                             |

|---------|-------------------|-----------------------------------|

| \$00    | Data Buffer (Rx)  | Data Buffer (Tx)                  |

| \$01    | Status 1          | Command                           |

| \$02    | Data Quality      | Control                           |

| \$03    | Status 2          | Mode                              |

| \$04    | Freq Offset       | Power Up 1                        |

| \$05    | RSSI              | Power Up 2                        |

| \$08    | Aux ADC 0 LSB     | Aux DAC 0 LSB                     |

| \$09    | Aux ADC 0 MSB     | Aux DAC 0 MSB                     |

| \$0A    | Aux ADC 1 LSB     | Aux DAC 1 LSB                     |

| \$0B    | Aux ADC 1 MSB     | Aux DAC 1 MSB                     |

| \$0C    | Aux ADC 2 LSB     | Aux DAC 2 LSB                     |

| \$0D    | Aux ADC 2 MSB     | Aux DAC 2 MSB                     |

| \$0E    | Aux ADC 3 LSB     | Aux DAC 3 LSB                     |

| \$0F    | Aux ADC 3 MSB     | Aux DAC 3 MSB                     |

| \$10    | Aux ADC 4 LSB     | RAM DAC control                   |

| \$11    | Aux ADC 4 MSB     | Aux ADC control 1                 |

| \$12    | Aux ADC 5 LSB     | Aux ADC control 2                 |

| \$13    | Aux ADC 5 MSB     | -                                 |

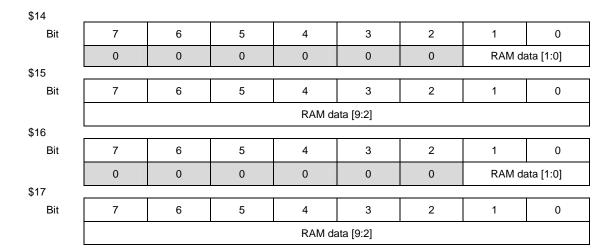

| \$14    | -                 | Aux Ram Data1 LSB                 |

| \$15    | -                 | Aux Ram Data1 MSB                 |

| \$16    | -                 | Aux Ram Data2 LSB                 |

| \$17    | -                 | Aux Ram Data2 MSB                 |

| \$18    | Analogue Setup 1  | Analogue Setup 1                  |

| \$19    | Analogue Setup 2  | Analogue Setup 2                  |

| \$1A    | -                 | Special Command                   |

| \$1B    | Special Data0 LSB | Special Data0 LSB                 |

| \$1C    | Special Data0 MSB | Special Data0 MSB                 |

| \$1D    | Special Data1 LSB | Special Data1 LSB                 |

| \$1E    | Special Data1 MSB | Special Data1 MSB                 |

| \$20    | -                 | Main PLL M div LSB                |

| \$21    | -                 | Main PLL M div MSB                |

| \$22    | -                 | Main PLL N div LSB                |

| \$23    | -                 | Main PLL N div NSB                |

| \$24    | -                 | Main PLL N div MSB                |

| \$25    | -                 | Aux PLL M div LSB                 |

| \$26    | -                 | Aux PLL M div MSB                 |

| \$27    | -                 | Aux PLL N div LSB                 |

| \$28    | -                 | Aux PLL N div MSB                 |

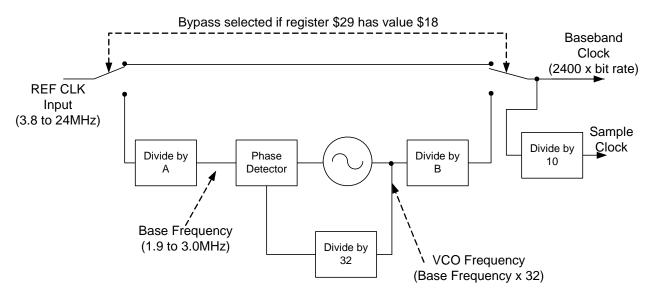

| \$29    | -                 | Clock Control                     |

| \$3F    | -                 | Test Output (see section 5.3.8.4) |

Note: All unused addresses from \$00 to \$3F are reserved for future use.

#### 5.3.1 Data Bus Buffers

The circuitry driving the D0-7 pins consists of 8 internal bidirectional 3-state logic level buffers between the internal registers and the external data bus lines.

#### 5.3.2 Address and R/W Decode

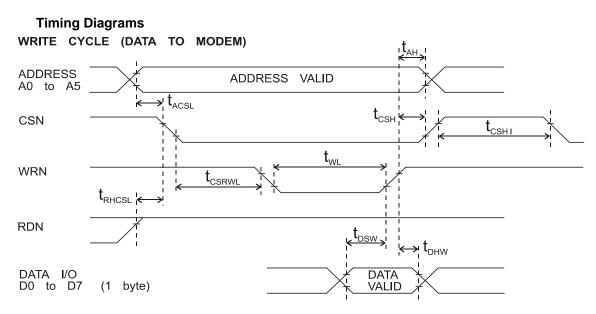

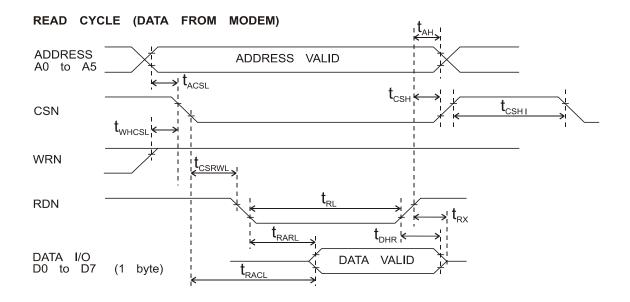

Transfer of data bytes between the  $\mu$ C and the internal registers is controlled according to the state of the Write and Read Enable inputs (WRN and RDN), the Chip Select input (CSN) and the Register Address inputs A0 to A5.

The Data Bus Buffers, Address and R/W Decode blocks provide a byte-wide parallel  $\mu$ C interface, which can be memory-mapped, as shown in Figure 3.

#### 5.3.3 Power-on and Reset

When the power is first applied to the device an internal circuit will reset internal registers to a known state and put all circuit blocks in an inactive and power saved state with the exception of the 'Enable Clock bit' in 'Power Up 1' register (section 5.3.5). This bit is set to '1' so that the device may respond to the TCXO clock which the reset task needs to complete its cycle.

The small current that this Clock enable circuit uses may be saved by writing all '0's to the 'Power Up 1' register through the micro interface. Read bits will be reset to '0' - the inactive state. Counters / states will be reset to an inactive and known condition after a reset event - which can occur asynchronously.

Setting the RESET bit (Register \$05, see section 5.3.5) to '1' is similar except the RESET bit does not control the 'V Reg", 'Preserve registers' and 'Vbias' bits (shown in bold in the following register diagrams) and the 'Clock Control Register' (\$29, see section 5.3.10), they will remain at the last programmed state. If minimum power is required and the 'Clock Control register' is using a value other than its default value of \$18, it must be re-programmed with \$18.

#### 5.3.4 Modem Interface

The modem appears to the programmer as a series of 8-bit read and write registers, individual registers being selected by the A0 to A5 address pins. Most of the baseband control for formatting or decoding the data is controlled by the following registers:

| Address | Write to Modem   | Read from Modem       |  |  |

|---------|------------------|-----------------------|--|--|

| \$00    | Data Buffer      | Data Buffer           |  |  |

| \$01    | Command Register | Status 1 Register     |  |  |

| \$02    | Control Register | Data Quality Register |  |  |

| \$03    | Mode Register    | Status 2 Register     |  |  |

#### 5.3.4.1 Data Buffer

| Data Buffer \$00 Write |         |      |      |   |   |   |   |   |

|------------------------|---------|------|------|---|---|---|---|---|

| Bit:                   | 7       | 6    | 5    | 4 | 3 | 2 | 1 | 0 |

|                        | Tx Data |      |      |   |   |   |   |   |

| Data B                 | uffer   | \$00 | Read |   |   |   |   |   |

| Bit:                   | 7       | 6    | 5    | 4 | 3 | 2 | 1 | 0 |

|                        | Rx Data |      |      |   |   |   |   |   |

This is an 18-byte read/write buffer which is used to transfer data (as opposed to command, status, mode, data quality and control information) between the modem and the host  $\mu$ C.

It appears to the  $\mu$ C as a single 8-bit register; the modem ensuring that sequential  $\mu$ C reads or writes to the buffer are routed to the correct locations within the buffer.

The µC should only access this buffer 2 µs after the Status Register BFREE (Buffer Free) bit is set to '1'.

The buffer should only be written to while in Tx mode and read from while in Rx mode (except when loading Frame Sync detection bytes while in Rx mode).

#### 5.3.4.2 Command Register

Writing to this register tells the modem to perform a specific action or actions, depending on the setting of the TASK and acquire bits. The enable packet detect bit is used to indicate the presence of data signals in the receive path.

#### Command Register \$01 Write

| Bit: | 7                    | 6                     | 5              | 4                          | 3            | 2 | 1 | 0 |

|------|----------------------|-----------------------|----------------|----------------------------|--------------|---|---|---|

|      | Acquire<br>Bit Clock | Acquire<br>I Q Offset | Acquire<br>AFC | Enable<br>packet<br>detect | Task Control |   |   |   |

When it has no action to perform (but is not 'powersaved'), the modem will be in an 'idle' state. If the modem is in transmit mode the input to the Tx filter will be connected to a mid level. In receive mode the modem will continue to measure the received data quality and extract bits from the received signal, supplying them to the de-interleave buffer, but will otherwise ignore the received data.

#### Command Register B7: Acquire Bit Clock

This bit has no effect in transmit mode.

In receive mode, whenever a byte with the Acquire Bit Clock set to '1' is written to the Command Register, and TASK is not set to RESET, it initiates an automatic sequence designed to achieve bit timing synchronisation with the received signal as quickly as possible. This involves setting the Phase Locked Loop of the received bit timing extraction circuits to its widest bandwidth, then gradually reducing the bandwidth as timing synchronisation is achieved, until it reaches the 'normal' value set by the PLL Control bits of the Control Register.

Setting this bit to '0' (or changing it from '1' to '0') has no effect, however note that the acquisition sequence will be re-started every time that a byte written to the Command Register has the Acquire Bit Clock bit set to '1'. Details of the acquisition sequence are in section 5.3.4.3.

The Acquire Bit Clock will normally be set to '1' up to 12 bits before an SFS (Search for Frame Sync) or SFH (Search for Frame Head) task, however it may also be used independently to re-establish clock synchronisation quickly after a long fade. Alternatively, a SFS or SFH task may be written to the Command Register with the Acquire Bit Clock bit set to '0' if it is known that clock synchronisation does not need to be re-established. Details of the acquisition sequence are in section 5.3.4.3.

#### Command Register B6: Acquire I Q Offset

This bit has no effect in transmit mode.

In receive mode, when this bit is changed from a '0' to a '1' it initiates an automatic sequence designed to compensate the dc offset of the received I and Q signal. This sequence involves temporarily disabling the RF input and measuring dc offset and applying an appropriate correction. Once this has been completed the RF input will be reasserted and operation will then depending on the setting of bits 4 and 5 of the Control Register (\$02). Details of the acquisition sequence are in section 5.3.4.3.

<sup>© 2008</sup> CML Microsystems Plc

Changing this bit from '1' to '0' will terminate acquisition and the 'normal' value set by bits 4 and 5 of the Control Register (\$02) will be carried out.

The Acquire I Q Offset bit will normally be set after changing or reacquiring a channel (e.g. after powering up from a sleep condition). This would normally be done so the acquisition sequence was completed before an SFS or SFH task is initiated. Alternatively, a SFS or SFH task may be written to the Command Register without previously setting the Acquire I Q Offset bit to '1' if it is known that there is no need to reestablish the received signal offsets, e.g. when receiving another message on the same channel in quick succession.

Note: SFH or SFS task should be set when the Acquire I Q Offset has completed and 12 bits after setting the Acquire Bit Clock sequence. For further discussion on I/Q offset correction see section 6.5.2.

#### Command Register B5: Acquire AFC

This bit has no effect in transmit mode.

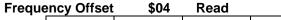

In receive mode, when this bit is changed from a '0' to a '1' it initiates an automatic sequence designed to measure and compensate for small differences in the carrier frequencies of the transmitter and receiver. If the TCXO frequency is too far out the dc offset in the demodulated signal will become excessive and limit the decode performance of the device. In these cases the host must adjust the TCXO frequency via the on chip DAC based on the value read from the Frequency Offset register (\$04).

In Mobitex systems the carrier frequencies of basestations are very accurate compared to the permitted tolerances of mobile units. Therefore once a mobile unit has set up it's local TCXO frequency it should be suitable for transmitting or receiving with any basestation. The Slow tracking mode should be sufficient to track any variations caused by environmental changes. Details of the acquisition sequence are in section 5.3.4.3.

#### Command Register B4: Enable packet detect

This bit has no effect in transmit mode.

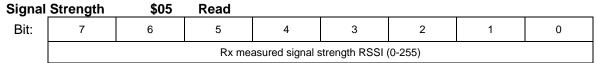

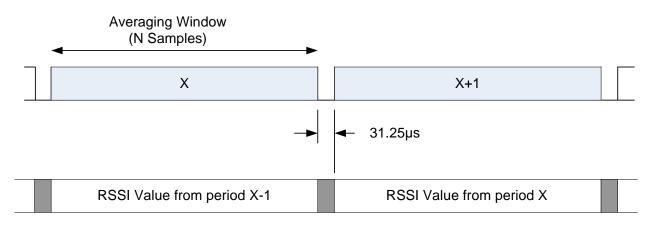

In receive mode if this bit is set to '1' the device will monitor the demodulated waveform for signals likely to be valid data. The likely presence of valid data will be reported via bit 0 of Status Register 1. This information can assist in the timing of setting a SFS or SFH task. Note that some noise signals may appear in the baseband as valid data, the RSSI signal should be used to confirm that the received signal is suitable before relying on this signal, bearing in mind the RSSI averaging time, see section 5.3.8.6.

It is recommended that this bit is only set to '1' when searching for the start of a packet. Once a frame sync has been detected this bit should be set to '0' until the start of a new packet needs to be found.

#### Command Register B3, B2, B1, B0: Task

Operations such as transmitting a data block are treated by the modem as 'tasks' and are initiated when the  $\mu$ C writes a byte to the Command Register with the TASK bits set to one of the data handling commands (marked BOLD in the table below).

| <b>B</b> 3 | B2 | B1 | <b>B0</b> |       | Receive Mode              |                                 | Transmit Mode             |  |  |  |

|------------|----|----|-----------|-------|---------------------------|---------------------------------|---------------------------|--|--|--|

| 0          | 0  | 0  | 0         | NULL  |                           | NULL                            |                           |  |  |  |

| 0          | 0  | 0  | 1         | SFH   | Search for Frame Head     | T7H Transmit 7 byte Frame H     |                           |  |  |  |

| 0          | 0  | 1  | 0         | R3H   | Read 3 byte Frame Head    | Reserved                        |                           |  |  |  |

| 0          | 0  | 1  | 1         | RDB   | Read Data Block           | TDB                             | Transmit Data Block       |  |  |  |

| 0          | 1  | 0  | 0         | SFS   | Search for Frame Sync     | TQB Transmit 4 Bytes            |                           |  |  |  |

| 0          | 1  | 0  | 1         | RSB   | Read Single Byte          | TSB                             | Transmit Single Byte      |  |  |  |

| 0          | 1  | 1  | 0         | LFSB  | Load Frame Sync Bytes     | TSO Transmit Scrambler Output   |                           |  |  |  |

| 0          | 1  | 1  | 1         | RESET | Cancel any current action | RESET Cancel any current action |                           |  |  |  |

| 1          | 0  | 0  | 1         | SFHZ  | SFH with zero errors      |                                 | Reserved                  |  |  |  |

| 1          | 0  | 1  | 1         | RSD   | Read Short Data Block     | TSD                             | Transmit Short Data Block |  |  |  |

| 1          | 1  | 0  | 0         | SFSZ  | SFS with zero errors      |                                 | Reserved                  |  |  |  |

#### Mobitex modem tasks:

Note: All other bit patterns are reserved. Bold text indicates a 'data handling command'

The  $\mu$ C should not write a data handling command to the Command Register or write to or read from the Data Buffer when the BFREE (Buffer Free) bit of the Status 1 Register is '0'.

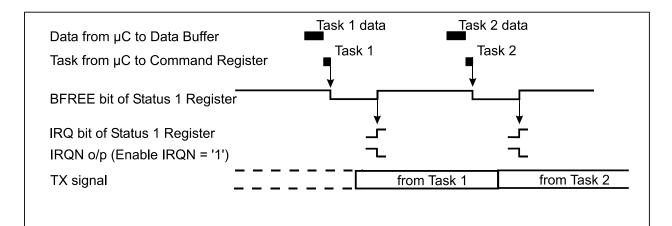

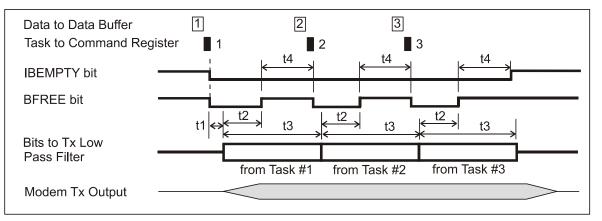

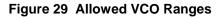

Different tasks apply in receive and transmit modes. Detailed timings for the various tasks are given in Figure 20 and Figure 21.

### 5.3.4.2.1 Transmit Operation

When the modem is in transmit mode, all data handling commands other than TSO instruct the modem to transmit data from the Data Buffer, formatting it as required. For these tasks the  $\mu$ C should wait until the BFREE (Buffer Free) bit of the Status 1 Register is '1', before writing the data to the Data Buffer. If more than 1 byte needs to be written to the Data Buffer, byte number 0 of the block should be written first. The host should then write the desired task to the Command Register.

Once the byte containing the desired task has been written to the Command Register, the modem will:

Set the BFREE (Buffer Free) bit of the Status 1 Register to '0'.

Take the data from the Data Buffer as quickly as it can - transferring it to the Interleave Buffer for eventual transmission. This operation will start immediately if the modem is 'idle' (i.e. not transmitting data from a previous task), otherwise it will be delayed until there is sufficient room in the Interleave Buffer.

Once all of the data has been transferred from the Data Buffer the modem will set the BFREE and IRQ bits of the Status 1 Register to '1', (causing the chip IRQN output to go low if the IRQ Enable bit of the Mode Register has been set to '1') to tell the  $\mu$ C that it may write new data and the next task to the modem.

In this way the  $\mu$ C can write a task and the associated data to the modem while the modem is still transmitting the data from the previous task. See Figure 18.

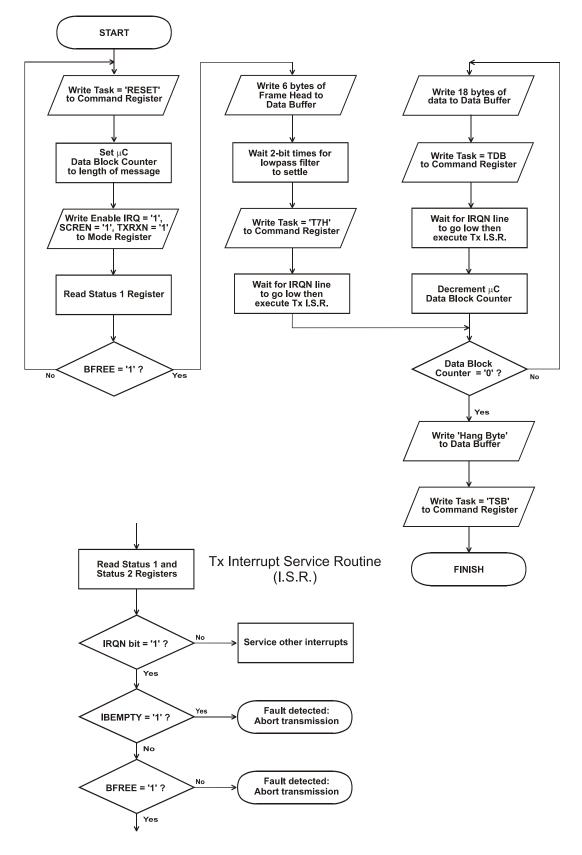

Figure 18 The Transmit Process

### 5.3.4.2.2 Receive Operation

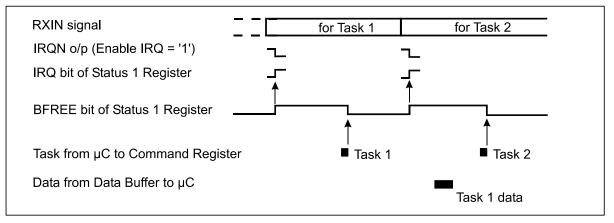

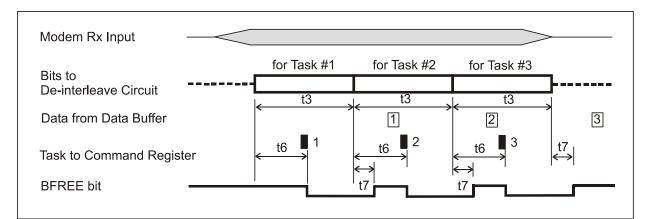

When the modem is in receive mode, the  $\mu$ C should wait until the BFREE bit of the Status 1 Register is '1', then write the desired task to the Command Register.

Once the byte containing the desired task has been written to the Command Register, the modem will:

Set the BFREE bit of the Status Register to '0'.

Wait until enough received bits are in the De-interleave Buffer.

Decode them as needed, and transfer any resulting data to the Data Buffer.

Then the modem will set the BFREE and IRQ bits of Status 1 Register to '1', (causing the IRQN output to go low if the IRQ Enable bit of the Mode Register has been set to '1') to tell the  $\mu$ C that it may read from the Data Buffer and write the next task to the modem. If more than 1 byte is contained in the Data Buffer, byte number '0' of the data will be read first.

In this way the  $\mu$ C can read data and write a new task to the modem while the received bits needed for this new task are being stored in the De-interleave Buffer. See Figure 19.

The above is not true for loading the Frame Sync detection bytes (LFSB): the bytes to be compared with the incoming data must be loaded prior to the task bits being written.

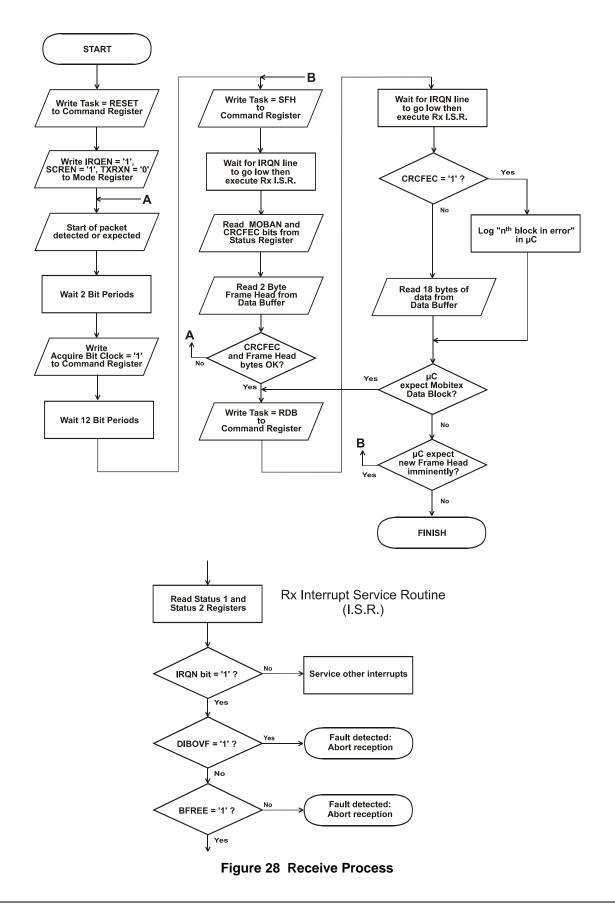

Figure 19 The Receive Process

#### **Task Descriptions:**

#### NULL - No effect

This task is provided so the acquisition commands can be issued without loading a new task.

#### SFH - Search for Frame Head

Causes the modem to search the received signal for a Frame Head. The Frame Head will consist of a 16-bit Frame Sync followed by control data (see Figure 15- Mobitex Over Air Signal). The search will continue until a Frame Head has been found, or until the RESET task is loaded.

The search is carried out by first attempting to match the incoming bits against the previously programmed (task LFSB) 16-bit Frame Sync pattern (allowing up to any one bit (of 16) in error). When a match has been found, the modem will read the next 3 received bytes as Frame Head bytes, these bytes will be checked, and corrected if necessary, using the FEC bits. The two Frame Head Data bytes are then placed into the Data Buffer.

The BFREE and IRQ bits of the Status 1 Register will then be set to a logic '1' to indicate that the  $\mu$ C may read the 2 Frame Head Data bytes from the Data Buffer and write the next task to the Command

Register. If the FEC indicates uncorrectable errors the modem will set the CRCFEC bit in the Status 1 Register to a logic '1'. The MOBAN bit (Mobile or Base) in the Status 1 Register will be set according to the polarity of the 3 bits preceding the Frame Sync pattern.

### R3H - Read 3-byte Frame Head

This task, which would normally follow an SFS task, will place the next 3 bytes directly into the Data Buffer. It also causes the modem to check the 3 bytes as Frame Head control data bytes and will set the CRCFEC bit to a logic '1' (high) only if the FEC bits indicate uncorrectable errors. Note: This task will not correct any errors and, due to the Mobitex FEC specification, will not detect all possible uncorrectable error patterns. The BFREE and IRQ bits of the Status 1 Register will be set to '1' when the task is complete to indicate that the  $\mu$ C may read the data from the Data Buffer and write the next task to the modem's Command Register.

The CRCFEC bit in the Status 1 Register will be set according to the validity of the received FEC bits.

### RDB - Read Data Block

This task causes the modem to read the next 240 bits as a Mobitex Data Block.