# Ultra Low Power CODEC for Portable Multimedia Applications Featuring Class G Ground Referenced Headphone Driver

### DESCRIPTION

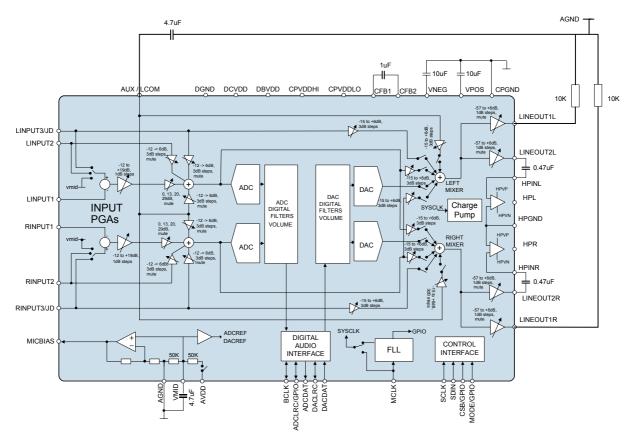

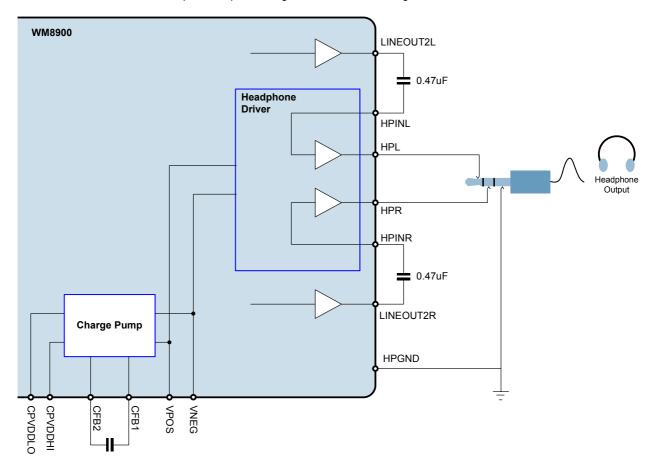

The WM8900 is designed for portable multimedia applications requiring low power consumption, high performance audio and a compact form factor. Pop and click optimised ground referenced headphone amplifiers provide high quality audio performance and improved bass response whilst also eliminating bulky headphone capacitors. Headphone amplifier playback power consumption is minimised by implementing an efficient class G amplifier powered by adaptive charge pump technology. Flexible analogue signal routing and digital signal processing capabilities enable advanced audio signal manipulation for fully featured multimedia applications whilst minimising power consumption.

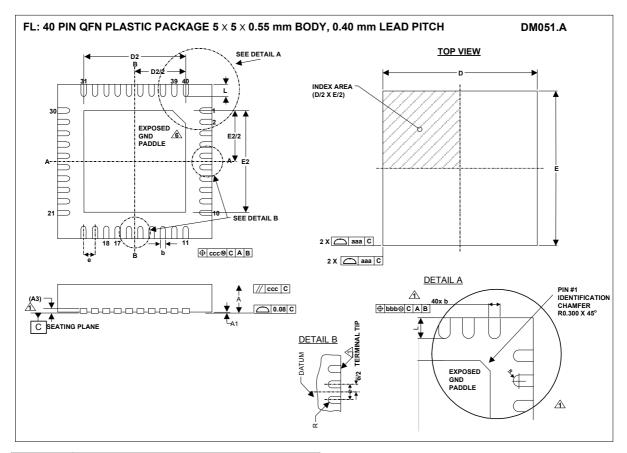

Stereo 24bit multi-bit sigma-delta ADCs and DACs are used with over-sampling digital interpolation and decimation filters. The master clock can be input directly or generated internally by an integrated low power FLL. WM8900 operates at analogue supply voltages down to 2.4v. The digital core can operate at voltages down to 1.8v to save power. Different sections of the chip can also be powered down under software control. The WM8900 is supplied in a very small and thin 5x5x0.55mm QFN package, ideal for use in hand-held and portable systems

Low power, high performance audio features can be realized with a minimal set of small form factor external components, reducing BOM costs and PCB dimensions

### **FEATURES**

- DAC to HP SNR 97dB ('A' weighted, 2.4V)

- DAC to HP THD -82dB at 48kHz Fs, 2.4V

- ADC SNR 95dB ('A' weighted, 3.3V)

- ADC THD -84dB at 48kHz Fs, 2.4V

### • Highly Flexible Input and Output Configuration

- 2 single ended or pseudo differential mic inputs

- 2 stereo line inputs (eg. Line In / FM tuner)

- Up to +48dB microphone/line input gain

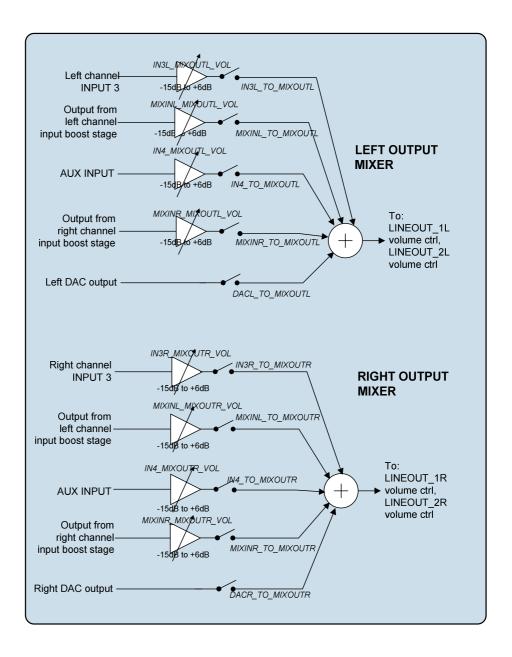

- Stereo output mixers with -15dB to +6dB gain range; mixing DAC outputs, line, auxiliary and mic inputs

# Class-G Ultra-low Power Headphone Driver

- Up to 12.4mW per channel output power into  $32\Omega$  at 3.3V

- Up to 6.6mW per channel output power into 32Ω at 2.4V

- Ground referenced outputs

- Pop and click suppression circuitry

### Soft Mute Control

### Low Power Consumption with User Selectable Modes

- 9 mW stereo headphone playback (32Ω)

(AVDD = 2.4V, DCVDD = 1.8V, 48k fs)

- 6 mW stereo headphone playback (32Ω)

(AVDD = 2.4V, DCVDD = 1.8V, 8k fs, quiescent)

- 5 mW bypass mode. Line in to stereo headphone playback (32Ω) (AVDD = 2.4V, DCVDD = 1.8V)

### Low Supply Voltages

- Analogue: 2.4V to 3.3VDigital core: 1.8V to 3.3V

- Digital I/O: 1.8V to 3.3V

- Charge Pump High: 2.4V to 3.3V

- Charge Pump Low: 1.6V to 3.3V

### Low Power FLL

- Supports MCLK input up to 19.2MHz or DACLRC input down to 8kHz

- TDM Mode dual data time slots for ADC and DAC

- Audio Sample Rates (kHz): 8, 11.025, 16, 22.05, 24, 32, 44.1, 48 generated internally from master clock

- 5 x 5 x 0.55mm 40 lead QFN package

- -25 °C +85°C temperature range

### **APPLICATIONS**

- MP3 players

- Portable Multimedia Applications

- Multimedia Handsets

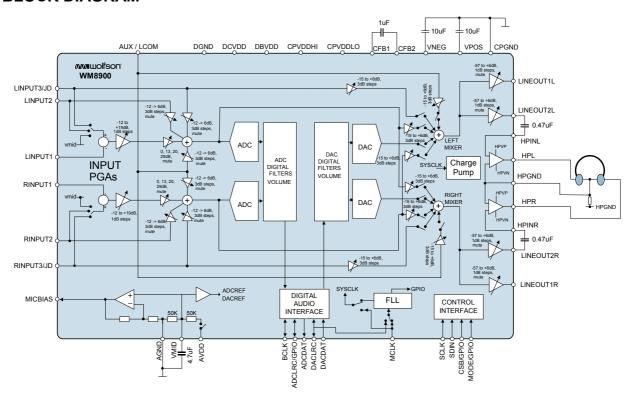

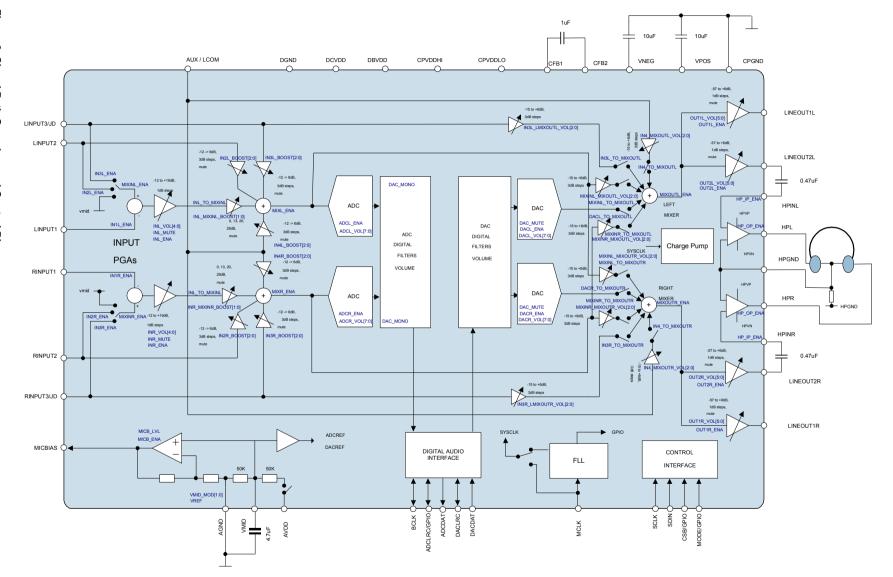

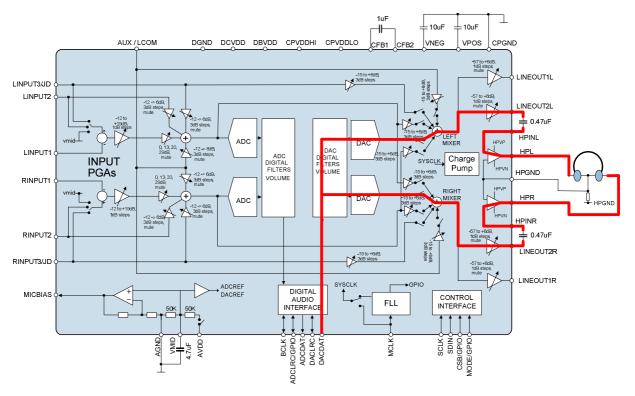

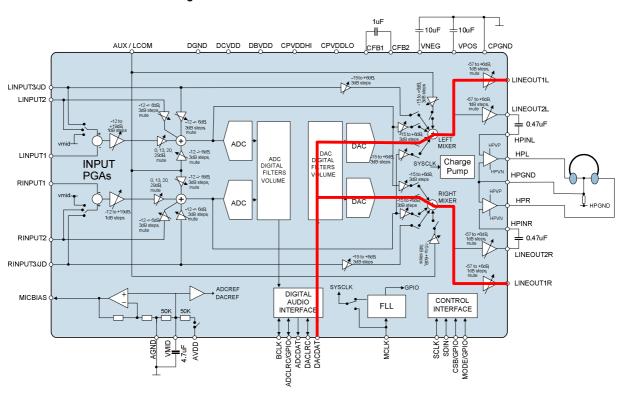

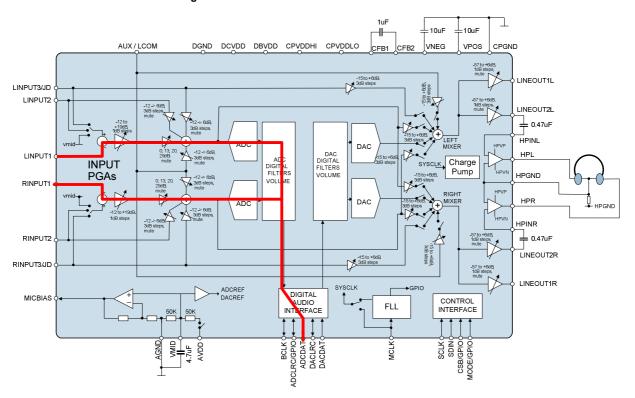

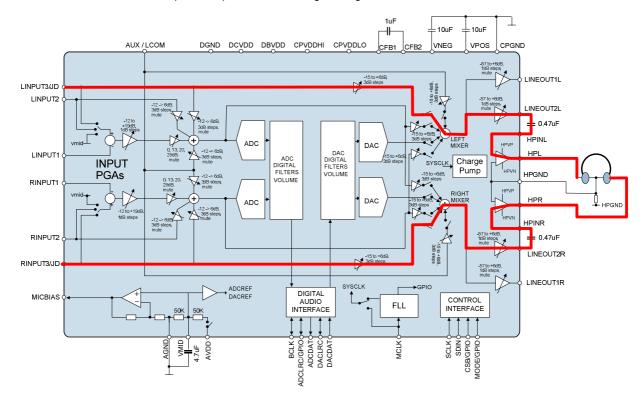

# **BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                        |

| APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                                        |

| BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |

| PIN CONFIGURATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |

| ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                          |

| PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                                                        |

| RECOMMENDED OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |

| ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |

| POWER CONSUMPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |

| DAC TO HEADPHONE POWER CONSUMPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |

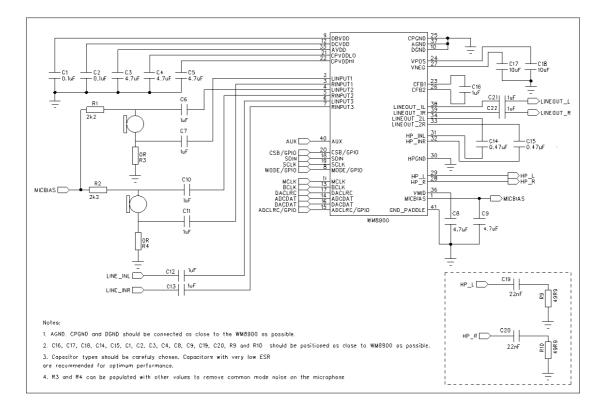

| EXTERNAL COMPONENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18                                                                                                       |

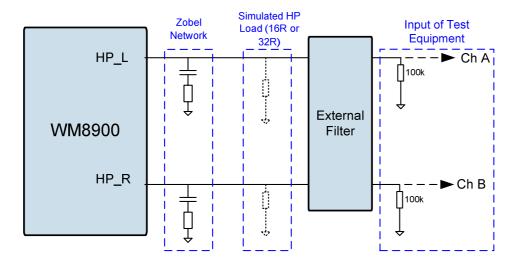

| RECOMMENDED TEST METHOD FOR TESTING AUDIO OUTPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |

| AUDIO PATHS OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                          |

| SYSTEM CLOCK TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                          |

| AUDIO INTERFACE TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          |

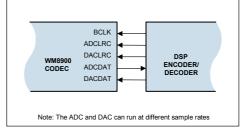

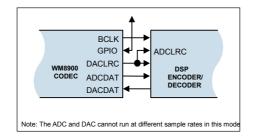

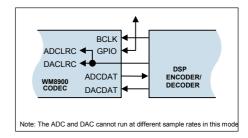

| MASTER MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                          |

| SLAVE MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

| CONTROL INTERFACE TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                          |

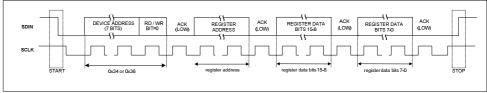

| 2-WIRE MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                          |

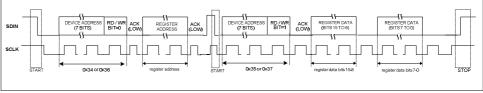

| 3-WIRE MODE  INTERNAL POWER ON RESET CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                          |

| INTEDNAT DAMED AN DECETABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7/                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |

| POP-CLICK MINIMISATION CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29                                                                                                       |

| POP-CLICK MINIMISATION CONTROL REGISTERS DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                               | 29<br>30                                                                                                 |

| POP-CLICK MINIMISATION CONTROL REGISTERS  DEVICE DESCRIPTION  INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                | <b>29</b><br><b>30</b><br>30                                                                             |

| POP-CLICK MINIMISATION CONTROL REGISTERS  DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>29</b><br><b>30</b><br>30                                                                             |

| POP-CLICK MINIMISATION CONTROL REGISTERS  DEVICE DESCRIPTION  INTRODUCTION  INPUT SIGNAL PATH  ANALOGUE TO DIGITAL CONVERTER (ADC)                                                                                                                                                                                                                                                                                                                                                        | <b>29</b><br><b>30</b><br>30<br>38                                                                       |

| POP-CLICK MINIMISATION CONTROL REGISTERS  DEVICE DESCRIPTION  INTRODUCTION  INPUT SIGNAL PATH  ANALOGUE TO DIGITAL CONVERTER (ADC)  DIGITAL MIXING                                                                                                                                                                                                                                                                                                                                        | <b>29 30</b> 30 38 41                                                                                    |

| POP-CLICK MINIMISATION CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>29 30</b> 30 38 41 44                                                                                 |

| POP-CLICK MINIMISATION CONTROL REGISTERS.  DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                             | 29<br>30<br>30<br>38<br>41<br>44                                                                         |

| POP-CLICK MINIMISATION CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>29 30</b> 30 38 41 44 48 56                                                                           |

| POP-CLICK MINIMISATION CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29<br>30<br>30<br>38<br>41<br>44<br>48<br>56                                                             |

| POP-CLICK MINIMISATION CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29<br>30<br>30<br>38<br>41<br>44<br>48<br>56<br>57                                                       |

| POP-CLICK MINIMISATION CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29<br>30<br>30<br>38<br>41<br>44<br>48<br>56<br>57                                                       |

| POP-CLICK MINIMISATION CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29<br>30<br>30<br>38<br>41<br>44<br>56<br>57<br>58<br>59                                                 |

| POP-CLICK MINIMISATION CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29<br>30<br>30<br>38<br>41<br>44<br>48<br>56<br>57<br>59<br>61                                           |

| POP-CLICK MINIMISATION CONTROL REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29<br>30<br>30<br>38<br>41<br>44<br>56<br>57<br>58<br>59<br>61<br>62                                     |

| POP-CLICK MINIMISATION CONTROL REGISTERS.  DEVICE DESCRIPTION.  INTRODUCTION.  INPUT SIGNAL PATH                                                                                                                                                                                                                                                                                                                                                                                          | 29<br>30<br>30<br>38<br>41<br>44<br>56<br>57<br>58<br>61<br>62<br>63<br>64                               |

| POP-CLICK MINIMISATION CONTROL REGISTERS.  DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                             | 29<br>30<br>30<br>38<br>41<br>44<br>56<br>57<br>58<br>61<br>62<br>63<br>64                               |

| POP-CLICK MINIMISATION CONTROL REGISTERS  DEVICE DESCRIPTION  INTRODUCTION  INPUT SIGNAL PATH  ANALOGUE TO DIGITAL CONVERTER (ADC)  DIGITAL MIXING  DIGITAL TO ANALOGUE CONVERTER (DAC)  OUTPUT SIGNAL PATH  ULTRA-LOW POWER GROUND-REFERENCED HEADPHONE OUTPUT  MASTER BIAS  OPTIMAL PLAYBACK POWER CONSUMPTION  VOLUME UPDATES  HEADPHONE JACK DETECT  THERMAL SHUTDOWN  GENERAL PURPOSE INPUT/OUTPUT  DIGITAL AUDIO INTERFACE  AUDIO INTERFACE CONTROL  CLOCKING AND SAMPLE RATES  FLL | 29<br>30<br>30<br>38<br>41<br>48<br>56<br>57<br>59<br>61<br>62<br>63<br>64<br>71                         |

| POP-CLICK MINIMISATION CONTROL REGISTERS.  DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                             | 29<br>30<br>30<br>38<br>41<br>44<br>56<br>57<br>59<br>61<br>62<br>63<br>64<br>71<br>75<br>81             |

| POP-CLICK MINIMISATION CONTROL REGISTERS.  DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                             | 29<br>30<br>30<br>38<br>41<br>44<br>56<br>57<br>62<br>63<br>64<br>71<br>81<br>84                         |

| POP-CLICK MINIMISATION CONTROL REGISTERS.  DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                             | 29<br>30<br>30<br>38<br>41<br>44<br>56<br>57<br>58<br>61<br>62<br>63<br>64<br>71<br>75<br>84<br>86       |

| POP-CLICK MINIMISATION CONTROL REGISTERS.  DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                             | 29<br>30<br>30<br>38<br>41<br>44<br>48<br>56<br>57<br>61<br>62<br>63<br>64<br>71<br>75<br>81<br>86<br>87 |

| POP-CLICK MINIMISATION CONTROL REGISTERS.  DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                             | 29<br>30<br>30<br>38<br>41<br>44<br>48<br>56<br>57<br>61<br>62<br>63<br>64<br>71<br>75<br>81<br>86<br>87 |

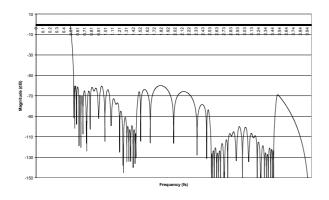

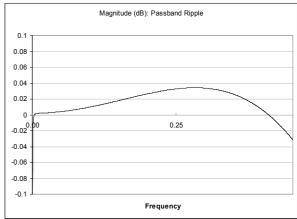

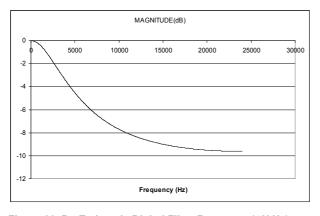

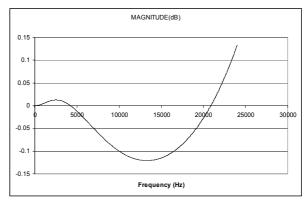

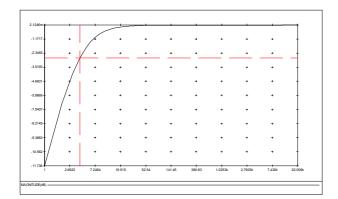

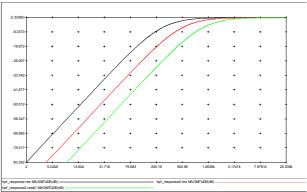

| DIGITAL FILTER CHARACTERISTICS  | 106 |

|---------------------------------|-----|

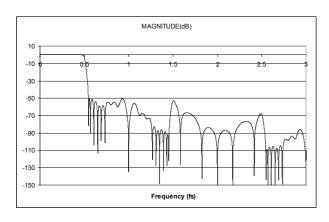

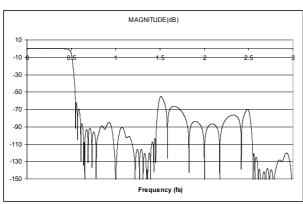

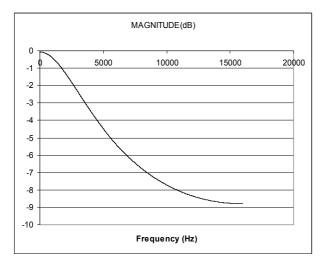

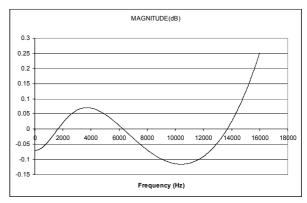

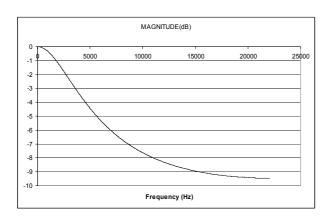

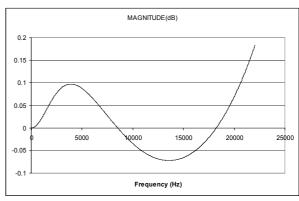

| ADC FILTER RESPONSES            | 107 |

| ADC FILTER RESPONSES            | 107 |

| DAC FILTER RESPONSES            | 107 |

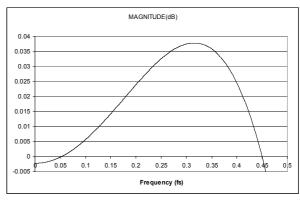

| DE-EMPHASIS FILTER RESPONSES    | 108 |

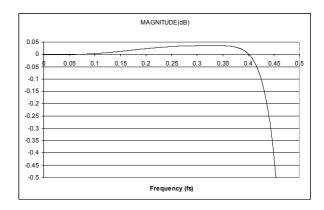

| ADC HIGH PASS FILTER RESPONSES  | 109 |

| APPLICATIONS INFORMATION        | 110 |

| RECOMMENDED PATHS               | 110 |

| RECOMMENDED POWER DOWN SEQUENCE | 115 |

| IMPORTANT NOTICE                | 117 |

| ADDRESS:                        |     |

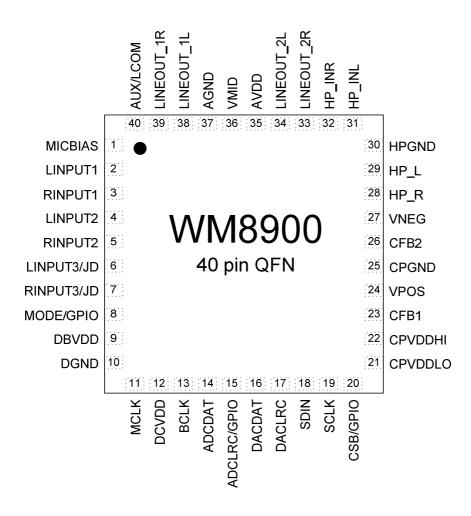

# **PIN CONFIGURATION**

# ORDERING INFORMATION

| ORDER CODE     | TEMPERATURE<br>RANGE | PACKAGE                                              | MOISTURE SENSITIVITY<br>LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|----------------|----------------------|------------------------------------------------------|-------------------------------|-------------------------------|

| WM8900LGEFK/V  | -25°C to +85°C       | 40-lead QFN (5x5x0.55mm)<br>(Pb-free)                | MSL3                          | 260°C                         |

| WM8900LGEFK/RV | -25°C to +85°C       | 40-lead QFN (5x5x0.55mm)<br>(Pb-free, tape and reel) | MSL3                          | 260°C                         |

### Note:

Reel quantity = 3500 Tube quantity = 95

# **PIN DESCRIPTION**

| PIN NO | NAME          | TYPE                   | DESCRIPTION                                                            |

|--------|---------------|------------------------|------------------------------------------------------------------------|

| 1      | MICBIAS       | Analogue Output        | Microphone Bias                                                        |

| 2      | LINPUT1       | Analogue Input         | Left Channel Input 1 (inverting)                                       |

| 3      | RINPUT1       | Analogue Input         | Right Channel Input 1 (inverting)                                      |

| 4      | LINPUT2       | Analogue Input         | Left Channel Input 2 (non-inverting)                                   |

| 5      | RINPUT2       | Analogue Input         | Right Channel Input 2 (non-inverting)                                  |

| 6      | LINPUT3 / JD  | Analogue Input         | Left Channel Input 3 or Jack Detect (non-inverting)                    |

| 7      | RINPUT3 / JD  | Analogue Input         | Right Channel Input 3 or Jack Detect (non-inverting)                   |

| 8      | MODE / GPIO   | Digital Input / Output | 2-wire / 3-wire control interface mode select or GPIO                  |

| 9      | DBVDD         | Supply                 | Digital Buffer (I/O) Supply                                            |

| 10     | DGND          | Supply                 | Digital Ground (return path for both DCVDD and DBVDD)                  |

| 11     | MCLK          | Digital Input          | Master Clock                                                           |

| 12     | DCVDD         | Supply                 | Digital Supply (Digital Core and FLL Digital)                          |

| 13     | BCLK          | Digital Input / Output | Audio Interface Bit Clock                                              |

| 14     | ADCDAT        | Digital Output         | ADC Digital Audio Data                                                 |

| 15     | ADCLRC / GPIO | Digital Input / Output | Audio Interface ADC Left/Right Clock or GPIO pin                       |

| 16     | DACDAT        | Digital Input          | DAC Digital Audio Data                                                 |

| 17     | DACLRC        | Digital Input / Output | Audio Interface DAC Left / Right Clock                                 |

| 18     | SDIN          | Digital Input/Output   | Control Interface Data Input / 2-wire Acknowledge output               |

| 19     | SCLK          | Digital Input          | Control Interface Clock Input                                          |

| 20     | CSB / GPIO    | Digital Input / Output | Chip select or GPIO                                                    |

| 21     | CPVDDLO       | Supply                 | Lower Supply for charge pump typically 1.8v                            |

| 22     | CPVDDHI       | Supply                 | Supply for charge pump 2.4 to 3.3v                                     |

| 23     | CFB1          | Analogue Output        | Flyback capacitor connection 1                                         |

| 24     | VPOS          | Analogue Output        | Headphone positive supply decoupling capacitor                         |

| 25     | CPGND         | Supply                 | Ground for Headphone Charge Pump                                       |

| 26     | CFB2          | Analogue Output        | Flyback capacitor connection 2                                         |

| 27     | VNEG          | Analogue Output        | Headphone negative supply decoupling capacitor                         |

| 28     | HP_R          | Analogue Output        | Right headphone output                                                 |

| 29     | HP_L          | Analogue Output        | Left headphone output                                                  |

| 30     | HPGND         | Analogue Input         | Headphone ground reference                                             |

| 31     | HP_INL        | Analogue Input         | Left channel input to headphone driver                                 |

| 32     | HP_INR        | Analogue Input         | Right channel input to headphone driver                                |

| 33     | LINEOUT_2R    | Analogue Output        | Right channel line output 2                                            |

| 34     | LINEOUT_2L    | Analogue Output        | Left channel line output 2                                             |

| 35     | AVDD          | Supply                 | Analogue Supply (DAC, ADC, Input Amps, Lineout, Mixers & FLL Analogue) |

| 36     | VMID          | Analogue Output        | Midrail Voltage Decoupling Capacitor                                   |

| 37     | AGND          | Supply                 | Analogue Ground                                                        |

| 38     | LINEOUT_1L    | Analogue Output        | Left channel line output 1                                             |

| 39     | LINEOUT_1R    | Analogue Output        | Right channel line output 1                                            |

| 40     | AUX / LCOM    | Analogue Input         | Aux Mono Input / Low noise Line input ground connection                |

# Note:

It is recommended that the PCB is laid out with a single ground plane. The QFN ground paddle should be tracked directly to AGND on the application PCB.

### **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                   | MIN        | MAX         |

|---------------------------------------------|------------|-------------|

| Supply voltages                             | -0.3V      | +3.63V      |

| Voltage range digital inputs                | DGND -0.3V | DBVDD +0.3V |

| Voltage range analogue inputs               | AGND -0.3V | AVDD +0.3V  |

| Operating temperature range, T <sub>A</sub> | -25°C      | +85°C       |

| Storage temperature after soldering         | -65°C      | +150°C      |

### **Notes**

- 1. Analogue and digital grounds must always be within 0.3V of each other.

- 2. All digital and analogue supplies are completely independent from each other (i.e. not internally connected).

- 3. DCVDD must be <= DBVDD.

- 4. DBVDD and DCVDD must be <= AVDD.

- 5. CPVDDLO must be <= CPVDDHI

# RECOMMENDED OPERATING CONDITIONS

| PARAMETER                     | SYMBOL            | MIN  | TYP | MAX | UNIT |

|-------------------------------|-------------------|------|-----|-----|------|

| Digital supply range (Core)   | DCVDD             | 1.7  |     | 3.6 | V    |

| Digital supply range (Buffer) | DBVDD             | 1.7  |     | 3.6 | V    |

| Analogue supply AVDD          | AVDD              | 2.28 |     | 3.6 | V    |

| Charge Pump Analog Supply     | CPVDDLO           | 1.6  |     | 3.6 | V    |

| Charge Pump Analog Supply     | CPVDDHI           | 2.28 |     | 3.6 | V    |

| Ground                        | DGND, AGND, CPGND |      | 0   |     | V    |

# **ELECTRICAL CHARACTERISTICS**

### **Test Conditions**

DCVDD=1.8V, DBVDD=1.8V, DGND=AGND=CPGND=HPGND=0V, AVDD=CPVDDHI=2.4V, CPVDDLO=1.8V;  $T_A$  = +25°C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                              | SYMBOL            | TEST CONDITIONS      | MIN | TYP    | MAX | UNIT |  |  |  |  |

|------------------------------------------------------------------------|-------------------|----------------------|-----|--------|-----|------|--|--|--|--|

| Analogue Inputs (LINPUT1, RINPUT1, LINPUT2, LINPUT3, RINPUT2, RINPUT3) |                   |                      |     |        |     |      |  |  |  |  |

| Full-scale Input Signal Level –                                        | $V_{INFS}$        | L/RINPUT1            |     | 1.0    |     | Vrms |  |  |  |  |

|                                                                        |                   | Single-ended         |     | 0      |     | dBV  |  |  |  |  |

| AVDD = 3.3v                                                            |                   | L/RINPUT2/3          |     | 0.5    |     | Vrms |  |  |  |  |

|                                                                        |                   | Differential MIC     |     | -6     |     | dBV  |  |  |  |  |

| $V_{INFS}$ is proportional to $AVDD$ -                                 |                   | L/RINPUT2/3          |     | 1.0    |     | Vrms |  |  |  |  |

| $V_{INFS}$ = (AVDD/3.3) x 1Vrms                                        |                   | Boost or bypass path |     | 0      |     | dBV  |  |  |  |  |

|                                                                        |                   | L/RINPUT3            |     | 1.0    |     | Vrms |  |  |  |  |

|                                                                        |                   | Boost + bypass path  |     | 0      |     | dBV  |  |  |  |  |

| Full-scale Input Signal Level –                                        | V <sub>INFS</sub> | L/RINPUT1            |     | 0.9091 |     | Vrms |  |  |  |  |

|                                                                        |                   | Single-ended         |     | -0.828 |     | dBV  |  |  |  |  |

| AVDD = 3.0v                                                            |                   | L/RINPUT2/3          |     | 0.455  |     | Vrms |  |  |  |  |

|                                                                        |                   | Differential MIC     |     | -6.84  |     | dBV  |  |  |  |  |

|                                                                        |                   | L/RINPUT2/3          |     | 0.9091 |     | Vrms |  |  |  |  |

|                                                                        |                   | Boost or bypass path |     | -0.828 |     | dBV  |  |  |  |  |

|                                                                        |                   | L/RINPUT3            |     | 0.9091 |     | Vrms |  |  |  |  |

|                                                                        |                   | Boost + bypass path  |     | -0.828 |     | dBV  |  |  |  |  |

| Full-scale Input Signal Level –                                        | V <sub>INFS</sub> | L/RINPUT1            |     | 0.727  |     | Vrms |  |  |  |  |

|                                                                        |                   | Single-ended         |     | -2.77  |     | dBV  |  |  |  |  |

| AVDD = 2.4v                                                            |                   | L/RINPUT2/3          |     | 0.364  |     | Vrms |  |  |  |  |

|                                                                        |                   | Differential MIC     |     | -8.79  |     | dBV  |  |  |  |  |

|                                                                        |                   | L/RINPUT2/3          |     | 0.727  |     | Vrms |  |  |  |  |

|                                                                        |                   | Boost or bypass path |     | -2.77  |     | dBV  |  |  |  |  |

|                                                                        |                   | L/RINPUT3            |     | 0.727  |     | Vrms |  |  |  |  |

|                                                                        |                   | Boost + bypass path  |     | -2.77  |     | dBV  |  |  |  |  |

| Mic PGA equivalent input noise                                         |                   | 0 to 20kHz,          |     | 150    |     | uV   |  |  |  |  |

|                                                                        |                   | +19dB gain           |     |        |     |      |  |  |  |  |

WM8900

### **Test Conditions**

DCVDD=1.8V, DBVDD=1.8V, DGND=AGND=CPGND=HPGND=0V, AVDD=CPVDDHI=2.4V, CPVDDLO=1.8V;  $T_A$  = +25°C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                   | SYMBOL               | TEST CONDITIONS                | MIN | TYP            | MAX | UNIT             |

|-------------------------------------------------------------|----------------------|--------------------------------|-----|----------------|-----|------------------|

| Input resistance                                            | R <sub>INPUT1</sub>  | +19dB PGA gain                 |     | 2              |     | kΩ               |

| (Note that input boost and                                  |                      | Differential or single-        |     |                |     |                  |

| bypass path resistances will be                             |                      | ended MIC configuration        |     |                |     |                  |

| seen in parallel with PGA input resistance when these paths | R <sub>INPUT1</sub>  | 0dB PGA gain                   |     | 10             |     | kΩ               |

| are enabled)                                                |                      | Differential or single-        |     |                |     |                  |

| and entance,                                                | _                    | ended MIC configuration        |     |                |     |                  |

|                                                             | R <sub>INPUT1</sub>  | -12dB PGA gain                 |     | 16             |     | kΩ               |

|                                                             |                      | Differential or single-        |     |                |     |                  |

|                                                             |                      | ended MIC configuration        |     | 00             |     | l-O              |

|                                                             | R <sub>INPUT2,</sub> | (Constant for all gains)       |     | 20             |     | kΩ               |

|                                                             | R <sub>INPUT3</sub>  | Differential MIC configuration |     |                |     |                  |

|                                                             | R <sub>INPUT2,</sub> | Max boost gain                 |     | 7.5            |     | kΩ               |

|                                                             | R <sub>INPUT3</sub>  | L/RINPUT2/3 to boost           |     | 7.5            |     | N22              |

|                                                             | R <sub>INPUT2,</sub> | 0dB boost gain                 |     | 15             |     | kΩ               |

|                                                             |                      | L/RINPUT2/3 to boost           |     | 15             |     | K22              |

|                                                             | R <sub>INPUT3</sub>  | †                              |     | 00             |     | l <sub>1</sub> O |

|                                                             | R <sub>INPUT2,</sub> | Min boost gain                 |     | 60             |     | kΩ               |

|                                                             | R <sub>INPUT3</sub>  | L/RINPUT2/3 to boost           |     | 40             |     | L-O              |

|                                                             | R <sub>INPUT3</sub>  | Max bypass gain                |     | 10             |     | kΩ               |

|                                                             |                      | L/RINPUT2/3 to bypass          |     | 110            |     |                  |

|                                                             | R <sub>INPUT3</sub>  | Min bypass gain                |     | 112            |     | kΩ               |

|                                                             |                      | L/RINPUT2/3 to bypass          |     |                |     |                  |

|                                                             | R <sub>AUX</sub>     | Max boost gain                 |     | 4.4            |     | kΩ               |

|                                                             |                      | AUX to boost                   |     |                |     |                  |

|                                                             | R <sub>AUX</sub>     | 0dB boost gain                 |     | 8.61           |     | kΩ               |

|                                                             |                      | AUX to boost                   |     |                |     |                  |

|                                                             | R <sub>AUX</sub>     | Min boost gain                 |     | 34.3           |     | kΩ               |

|                                                             |                      | AUX to boost                   |     |                |     |                  |

|                                                             | R <sub>AUX</sub>     | Max boost gain                 |     | 5.75           |     | $k\Omega$        |

|                                                             |                      | AUX to bypass                  |     |                |     |                  |

|                                                             | R <sub>AUX</sub>     | 0dB boost gain                 |     | 11.41          |     | kΩ               |

|                                                             |                      | AUX to bypass                  |     |                |     |                  |

|                                                             | R <sub>AUX</sub>     | Min boost gain                 |     | 63.65          |     | kΩ               |

|                                                             |                      | AUX to bypass                  |     |                |     |                  |

| Input capacitance                                           |                      |                                |     | 10             |     | pF               |

| MIC Programmable Gain Ampli                                 | fier (PGA)           |                                |     |                |     |                  |

| Programmable Gain                                           |                      |                                | -12 |                | +19 | dB               |

| Programmable Gain Step Size                                 |                      | Guaranteed monotonic           |     | 1              |     | dB               |

| Mute Attenuation                                            |                      |                                | _   | 100            | _   | dB               |

| Selectable Input Gain Boost                                 |                      |                                |     | '              |     |                  |

| Gain Boost Steps                                            |                      | Input from PGA                 |     | 0, 13, 20,     |     | dB               |

|                                                             |                      |                                |     | 29, MUTE       |     |                  |

|                                                             |                      | Input from L/RINPUT2 or        |     | -12, -6, 0, 6, |     | dB               |

|                                                             |                      | L/RINPUT3                      |     | MUTE           |     |                  |

# **Test Conditions**

DCVDD=1.8V, DBVDD=1.8V, DGND=AGND=CPGND=HPGND=0V, AVDD=CPVDDHI=2.4V, CPVDDLO=1.8V; TA =  $+25^{\circ}$ C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                      | SYMBOL        | TEST CONDITIONS              | MIN                                   | TYP         | MAX   | UNIT |

|------------------------------------------------|---------------|------------------------------|---------------------------------------|-------------|-------|------|

| Analogue Inputs (LINPUT1, RIN                  | PUT1, LINPU   | T2, RINPUT2, LINPUT3, R      | RINPUT3) to A                         | ADC Out     | '     |      |

| Signal to Noise Ratio                          | SNR           | AVDD=3.3V                    | · · · · · · · · · · · · · · · · · · · | 95          |       | dB   |

| (A-weighted)                                   |               | AVDD = 2.4V                  | 83                                    | 91          |       |      |

| Signal to Noise Ratio                          | SNR           | AVDD=3.3V                    |                                       | 93          |       | dB   |

| (Unweighted)                                   | Ont           | AVDD = 2.4V                  |                                       | 90          |       |      |

|                                                | TUD           |                              |                                       |             |       |      |

| Total Harmonic Distortion                      | THD           | -1dBFs input,<br>AVDD = 3.3V |                                       | -84         |       | dB   |

|                                                |               | -1dBFs input,                |                                       | -84         | -76   |      |

|                                                |               | AVDD = 2.4V                  |                                       | -04         | -70   |      |

| Total Harmonic Distortion +                    | THD+N         | -1dBFs input,                |                                       | -82         |       | dB   |

| Noise                                          |               | AVDD = 3.3V                  |                                       |             |       |      |

|                                                |               | -1dBFs input,                |                                       | -82         | -73   |      |

|                                                |               | AVDD = 2.4V                  |                                       |             |       |      |

| ADC Channel Separation                         |               | 1kHz full scale signal into  |                                       | 90          |       | dB   |

|                                                |               | ADC via L/RINPUT1, MIC       |                                       |             |       |      |

|                                                |               | amp (single-ended) and boost |                                       |             |       |      |

|                                                |               | 1kHz full scale signal into  |                                       | 90          |       | dB   |

|                                                |               | ADC via L/RINPUT1/2,         |                                       | 90          |       | uБ   |

|                                                |               | MIC amp (differential)       |                                       |             |       |      |

|                                                |               | and boost                    |                                       |             |       |      |

|                                                |               | 1kHz full scale signal into  |                                       | 90          |       | dB   |

|                                                |               | ADC via L/RINPUT2 and boost  |                                       |             |       |      |

|                                                |               | 1kHz full scale signal into  |                                       | 90          |       | dB   |

|                                                |               | ADC via L/RINPUT3 and        |                                       |             |       | QD.  |

|                                                |               | boost                        |                                       |             |       |      |

| Line Input / MIC Separation                    |               | Single-ended MIC input       |                                       | 90          |       | dB   |

| (Quiescent input to ADC via                    |               | on L/RINPUT1                 |                                       |             |       |      |

| boost; Output on ADC;                          |               | Differential MIC input       |                                       | 90          |       | dB   |

| 1kHz on L/RINPUT3 to HP out via bypass path)   |               | using L/RINPUT2              |                                       |             |       |      |

| Boost / Bypass Separation                      |               | 1kHz on LINPUT2 to           |                                       | 90          |       | dB   |

| (Quiescent L/RINPUT3 to HP                     |               | ADC via boost only           |                                       |             |       |      |

| outputs via bypass)                            |               | 1kHz on LINPUT1 to           |                                       | 90          |       | dB   |

|                                                |               | ADC via single-ended         |                                       |             |       |      |

| Channel Matching                               |               | MIC PGA & boost              |                                       | 0.0         |       | 4D   |

| Channel Matching  DAC to Line-Out (LINEOUT_1L) | LINEOUT 1     | 1kHz signal                  | NIT 2D with                           | 0.2         | load) | dB   |

| Signal to Noise Ratio                          | SNR           | AVDD=2.4V                    | 90<br>90                              | 97          | loau) | dB   |

| (A-weighted)                                   | ONIX          | AVDD-2.4V                    | 30                                    | 31          |       | uБ   |

| Total Harmonic Distortion                      | THD           | AVDD=2.4V                    |                                       | -89         | -80   | dB   |

| Total Harmonic Distortion +                    | THD+N         | AVDD=2.4V                    |                                       | -88         | -79   | dB   |

| Noise                                          |               |                              |                                       |             |       |      |

| DAC to Line-Out (LINEOUT_1L                    | /LINEOUT_1    | R or LINEOUT_2L / LINEO      | OUT_2R with                           | 10kΩ / 50pF | load) |      |

| - Reduced Power Mode (DAC_E                    | BIAS = 01 = H | lalf Bias)                   |                                       |             |       |      |

| Signal to Noise Ratio                          | SNR           | AVDD = 2.4V                  |                                       | 92          |       | dB   |

| (A-weighted)                                   |               |                              |                                       |             |       |      |

| Signal to Noise Ratio                          | SNR           | AVDD = 2.4V                  |                                       | 89          |       | dB   |

| (Unweighted)                                   |               |                              |                                       |             |       |      |

| Total Harmonic Distortion                      | THD           | AVDD = 2.4V                  |                                       | -83         |       | dB   |

| Total Harmonic Distortion +                    | THD+N         | AVDD = 2.4V                  |                                       | -81         |       | dB   |

| Noise                                          |               |                              |                                       |             |       |      |

WM8900

#### **Test Conditions** DCVDD=1.8V, DBVDD=1.8V, DGND=AGND=CPGND=HPGND=0V, AVDD=CPVDDHI=2.4V, CPVDDLO=1.8V; TA = +25°C, 1kHz signal, fs = 48kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated. SYMBOL **TEST CONDITIONS** MIN TYP MAX UNIT **PARAMETER** 100 dΒ **Channel Separation** 1kHz signal L/RINPUT3 to HP\_L / HP\_R via bypass path **Channel Separation** dΒ 85 DAC to LINEOUT\_2L / LINEOUT\_2R to HP\_L / HP\_R Signal to Noise Ratio SNR AVDD = 2.4V90 97 dΒ (A-weighted) THD **Total Harmonic Distortion** AVDD = 2.4V-92 -82 dB Total Harmonic Distortion + THD+N AVDD = 2.4V-90 -80 dB Noise DAC to LINEOUT 2L / LINEOUT 2R to HP L / HP R - Reduced Power Mode (DAC\_BIAS = 01 = Half Bias) 0dB Full scale output voltage AVDD/3.3 Vrms Mute attenuation 1kHz, full scale signal 90 dΒ SNR Signal to Noise Ratio AVDD = 2.4V92 dB (A-weighted) AVDD = 2.4V Signal to Noise Ratio SNR 90 dB (Unweighted) **Total Harmonic Distortion** THD AVDD=2.4V, $R_L$ =32 $\Omega$ , -86 dΒ $P_0$ = 5mW AVDD=2.4V, $R_1$ =16 $\Omega$ , -82 dΒ Po= 5mW Total Harmonic Distortion + THD+N AVDD=2.4V, $R_1$ =32 $\Omega$ , -84 dB Noise Po=5mW AVDD=2.4V, $R_1$ =16 $\Omega$ , -80 dB Po= 5mW PGA for LINEOUT\_2L and LINEOUT\_2R (can be used to control HP\_L and HP\_R amplitude or as a separate LINE OUT) Minimum Gain -57 dΒ Maximum Gain +6 dB Programmable Gain Step Size Guaranteed monotonic 1 dΒ PGA for LINEOUT 1L and LINEOUT\_1R Minimum Gain -57 dB Maximum Gain +6 dΒ dΒ Programmable Gain Step Size Guaranteed monotonic 1 **Analogue Reference Levels** Midrail Reference Voltage **VMID** -3% AVDD/2 +3% V **VREF Buffered Reference Voltage** -3% AVDD/2 +3% V **Microphone Bias** Bias Voltage 3mA load current -5% 0.9×AVDD + 5% V $V_{\text{MICBIAS}}$ MBSEL = 0 3mA load current -5% 0.65×AVDD + 5% V MBSEL = 1 Bias Current Source 3 mΑ $\mathbf{I}_{\text{MICBIAS}}$ Output Noise Voltage Vn nV/√Hz 1kHz to 20kHz 25 $MICB_LVL = 0$ 17 nV/√Hz 1K to 20kHz $MICB_LVL = 1$ **Digital Input / Output** Input HIGH Level $V_{\text{IH}}$ 0.7×DBVDD V Input LOW Level $V_{\text{IL}}$ 0.3×DBVDD V Output HIGH Level 0.9×DBVDD V $V_{OH}$ $I_{OL}$ =1mA

$V_{\text{OL}}$

I<sub>OH</sub>-1mA

Output LOW Level

**Production Data**

0.1×DBVDD

٧

### **Test Conditions**

DCVDD=1.8V, DBVDD=1.8V, DGND=AGND=CPGND=HPGND=0V, AVDD=CPVDDHI=2.4V, CPVDDLO=1.8V; TA =  $\pm 25^{\circ}$ C, 1kHz signal, fs =  $\pm 48$ kHz, PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                      | SYMBOL            | TEST CONDITIONS                             | MIN        | TYP        | MAX     | UNIT               |

|------------------------------------------------|-------------------|---------------------------------------------|------------|------------|---------|--------------------|

| Input capacitance                              |                   |                                             |            | 10         |         | pF                 |

| Input leakage                                  |                   |                                             |            | 1          |         | uA                 |

| FLL                                            |                   |                                             |            |            |         |                    |

| Lock Time See note 3                           | Lock              | FLL_SLOW_LOCK_REF<br>= 0                    |            |            | 509     | Reference<br>Clock |

|                                                |                   | FLL_SLOW_LOCK_REF<br>= 1                    |            |            | 49      | Periods            |

| Reference Clock Frequency                      | $F_REF$           | LRCLK_REF_ENA = 0                           | 48kHz      |            | 19.2MHz |                    |

|                                                |                   | LRCLK_REF_ENA = 1                           | 8          |            | 48      | kHz                |

| Output Clock Frequency                         | F <sub>out</sub>  |                                             | 10         |            | 20      | MHz                |

| Charge Pump                                    |                   |                                             |            |            |         |                    |

| Efficiency                                     | CP <sub>EFF</sub> |                                             | 90         |            |         | %                  |

| Startup Time                                   | CP <sub>ST</sub>  |                                             |            |            | 500     | us                 |

| High Input                                     | CPVDDHI           |                                             | 2.4        |            | 3.3     | V                  |

| Low Input                                      | CPVDDLO           |                                             | 1.6        |            | 3.3     | V                  |

| VPOS                                           | VPOS              | Using CPVDDHI                               |            | CPVDDHI/2  |         | V                  |

|                                                |                   | Using CPVDDLO                               |            | CPVDDLO/2  |         |                    |

| VNEG                                           | VNEG              | Using CPVDDHI                               |            | -CPVDDHI/2 |         | V                  |

|                                                |                   | Using CPVDDLO                               |            | -CPVDDLO/2 |         |                    |

| Charge Pump output switching frequency         | CPFREQ            |                                             |            |            | 1.536   | MHz                |

| Internal clock (SYSCLK) when using charge pump | SYSCLK            | Using analog bypass e.g.<br>LRIN1 to HP out | See note 2 | 12         |         | MHz                |

| Standby mode (All modules po                   | wered down,       | clocks stopped)                             |            | •          |         |                    |

| Current consumption                            | Idd (standby)     |                                             |            | 75         | 150     | uA                 |

Table 1 Electrical characteristics (see Note 1)

### Notes:

- 1. The bias conditions are explained in Table 45 on page 12.

- 2. For a given headphone load, it is expected that the HP\_L/HP\_R output will begin to clip at 6dB lower amplitude for every 50% reduction in charge pump SYSCLK.

The FLL lock time is the time from last CSB edge of serial interface write to first clock edge of f<sub>OUT</sub> from FLL (see Figure 46).

# **POWER CONSUMPTION**

| MODE                       | Α   | VDD    | D   | CVDD   | D   | BVDD   | CPVDDI |        | СР  | VDDHI  | TOTAL   |  |

|----------------------------|-----|--------|-----|--------|-----|--------|--------|--------|-----|--------|---------|--|

|                            | ٧   | mA     | V   | mA     | ٧   | mA     | ٧      | mA     | ٧   | mA     | mW      |  |

| Headphone Playback         |     |        |     |        |     |        |        |        |     |        |         |  |

| DAC to HP playback         | 3.3 | 2.2640 | 1.8 | 0.3600 | 1.8 | 0.0016 | 1.8    | 0.0000 | 3.3 | 0.8680 | 10.9865 |  |

| 32ohm load, quiescent      | 3.0 | 2.0490 | 1.8 | 0.3600 | 1.8 | 0.0016 | 1.8    | 0.0000 | 3.0 | 0.7560 | 9.0659  |  |

| 8kHz sample rate           | 2.4 | 1.6240 | 1.8 | 0.3600 | 1.8 | 0.0007 | 1.8    | 0.0000 | 2.4 | 0.5560 | 5.8812  |  |

| DAC to HP playback         | 3.3 | 2.3720 | 1.8 | 0.4160 | 1.8 | 0.0024 | 1.8    | 1.6570 | 3.3 | 0.0233 | 11.6401 |  |

| 32ohm load, 0.1mW/channel  | 3.0 | 2.1480 | 1.8 | 0.4140 | 1.8 | 0.0021 | 1.8    | 1.6620 | 3.0 | 0.0207 | 10.2466 |  |

| 8kHz sample rate           | 2.4 | 1.7050 | 1.8 | 0.4150 | 1.8 | 0.0012 | 1.8    | 1.6270 | 2.4 | 0.0156 | 7.8073  |  |

| DAC to HP playback         | 3.3 | 2.3860 | 1.8 | 0.4140 | 1.8 | 0.0023 | 1.8    | 6.7160 | 3.3 | 0.0762 | 20.9633 |  |

| 32ohm load, 2.0mW/channel  | 3.0 | 2.1620 | 1.8 | 0.4140 | 1.8 | 0.0020 | 1.8    | 6.8210 | 3.0 | 0.0683 | 19.7174 |  |

| 8kHz sample rate           | 2.4 | 1.7200 | 1.8 | 0.4150 | 1.8 | 0.0009 | 1.8    | 6.8700 | 2.4 | 0.0534 | 17.3835 |  |

| LINE OUT 1 Playback        |     |        |     |        |     |        |        |        |     |        |         |  |

| DAC to Line Out 1 playback | 3.3 | 2.4530 | 1.8 | 2.5350 | 1.8 | 0.0112 | 1.8    | 0.0000 | 3.3 | 0.0042 | 12.6918 |  |

| 10k load, quiescent        | 3.0 | 2.2090 | 1.8 | 2.5350 | 1.8 | 0.0096 | 1.8    | 0.0000 | 3.0 | 0.0033 | 11.2171 |  |

| 48kHz sample rate          | 2.4 | 1.7340 | 1.8 | 2.5350 | 1.8 | 0.0046 | 1.8    | 0.0000 | 2.4 | 0.0019 | 8.7374  |  |

| DAC to Line Out 1 playback | 3.3 | 2.2950 | 1.8 | 0.3590 | 1.8 | 0.0020 | 1.8    | 0.0000 | 3.3 | 0.0140 | 8.2372  |  |

| 10k load, quiescent        | 3.0 | 2.0680 | 1.8 | 0.3590 | 1.8 | 0.0014 | 1.8    | 0.0000 | 3.0 | 0.0033 | 6.8626  |  |

| 8kHz sample rate           | 2.4 | 1.6240 | 1.8 | 0.3590 | 1.8 | 0.0007 | 1.8    | 0.0000 | 2.4 | 0.0019 | 4.5496  |  |

| MIC/LINE Record            |     |        |     |        |     |        |        |        |     |        |         |  |

| Mic to ADC record,         | 3.3 | 4.5250 | 1.8 | 2.4310 | 1.8 | 0.0451 | 1.8    | 0.0000 | 3.3 | 0.0041 | 19.4031 |  |

| quiescent                  | 3.0 | 4.3220 | 1.8 | 2.4380 | 1.8 | 0.0377 | 1.8    | 0.0001 | 3.0 | 0.0033 | 17.4323 |  |

| 48kHz sample rate          | 2.4 | 3.9280 | 1.8 | 2.4440 | 1.8 | 0.0225 | 1.8    | 0.0000 | 2.4 | 0.0019 | 13.8714 |  |

| Mic to ADC record,         | 3.3 | 4.2830 | 1.8 | 0.4090 | 1.8 | 0.0077 | 1.8    | 0.0000 | 3.3 | 0.0042 | 14.8978 |  |

| quiescent                  | 3.0 | 4.1050 | 1.8 | 0.4100 | 1.8 | 0.0069 | 1.8    | 0.0000 | 3.0 | 0.0033 | 13.0753 |  |

| 8kHz sample rate           | 2.4 | 3.7540 | 1.8 | 0.4100 | 1.8 | 0.0037 | 1.8    | 0.0000 | 2.4 | 0.0018 | 9.7587  |  |

| Line In to ADC record,     | 3.3 | 4.5030 | 1.8 | 2.4310 | 1.8 | 0.0467 | 1.8    | 0.0000 | 3.3 | 0.0042 | 19.3336 |  |

| quiescent                  | 3.0 | 4.3020 | 1.8 | 2.4370 | 1.8 | 0.0409 | 1.8    | 0.0000 | 3.0 | 0.0033 | 17.3761 |  |

| 48kHz sample rate          | 2.4 | 3.9100 | 1.8 | 2.4410 | 1.8 | 0.0222 | 1.8    | 0.0000 | 2.4 | 0.0019 | 13.8222 |  |

| Line In to ADC record,     | 3.3 | 4.2590 | 1.8 | 0.4090 | 1.8 | 0.0074 | 1.8    | 0.0001 | 3.3 | 0.0042 | 14.8181 |  |

| quiescent                  | 3.0 | 4.0820 | 1.8 | 0.4100 | 1.8 | 0.0074 | 1.8    | 0.0000 | 3.0 | 0.0033 | 13.0070 |  |

| 8kHz sample rate           | 2.4 | 3.7360 | 1.8 | 0.4110 | 1.8 | 0.0038 | 1.8    | 0.0000 | 2.4 | 0.0018 | 9.7176  |  |

| Bypass Path to Headphone   |     |        |     |        |     |        |        |        |     |        |         |  |

| Line In to HP bypass path  | 3.3 | 0.7900 | 1.8 | 0.5410 | 1.8 | 0.0086 | 1.8    | 0.0000 | 3.3 | 1.6490 | 9.0380  |  |

| 32ohm load, quiescent      | 3.0 | 0.7220 | 1.8 | 0.5400 | 1.8 | 0.0071 | 1.8    | 0.0000 | 3.0 | 1.4570 | 7.5219  |  |

|                            | 2.4 | 0.5870 | 1.8 | 0.5410 | 1.8 | 0.0035 | 1.8    | 0.0000 | 2.4 | 1.1010 | 5.0312  |  |

| Line In to HP bypass path  | 3.3 | 0.8680 | 1.8 | 0.5350 | 1.8 | 0.0086 | 1.8    | 1.5490 | 3.3 | 0.1130 | 7.0040  |  |

| 32ohm load, 0.1mW/channel  | 3.0 | 0.7950 | 1.8 | 0.5350 | 1.8 | 0.0071 | 1.8    | 1.5540 | 3.0 | 0.1020 | 6.4639  |  |

|                            | 2.4 | 0.6540 | 1.8 | 0.5350 | 1.8 | 0.0034 | 1.8    | 1.6410 | 2.4 | 0.0801 | 5.6849  |  |

| Line In to HP bypass path  | 3.3 | 0.8920 | 1.8 | 0.5410 | 1.8 | 0.0087 | 1.8    | 6.1740 | 3.3 | 0.4310 | 16.4685 |  |

| 32ohm load, 2.0mW/channel  | 3.0 | 0.8200 | 1.8 | 0.5410 | 1.8 | 0.0070 | 1.8    | 6.2770 | 3.0 | 0.3890 | 15.9121 |  |

|                            | 2.4 | 0.6840 | 1.8 | 0.5410 | 1.8 | 0.0036 | 1.8    | 6.8540 | 2.4 | 0.3070 | 15.6958 |  |

Table 2 Power Consumption

Note: All parameters in this table were measured at default bias conditions, and at 48kHz sample rate unless otherwise stated.

WM8900

# DAC TO HEADPHONE POWER CONSUMPTION

The following tables detail the DAC to Headphone power consumption differences and SNR differences (where applicable) between 4 different playback conditions and 3 different biasing modes. The biasing modes are detailed in Table 45 on page 12.

| SUPPLIES        | AV   | DD   | DC   | VDD  | DB   | DBVDD |      | DBVDD |          | DBVDD |       | CPVDDLO |  | CPVDDLO CI |  | /DDHI | TOTAL |

|-----------------|------|------|------|------|------|-------|------|-------|----------|-------|-------|---------|--|------------|--|-------|-------|

| MODE            | V    | mA   | V    | mA   | V    | mA    | V    | mA    | <b>V</b> | mA    | mW    |         |  |            |  |       |       |

|                 | 3.30 | 4.11 | 1.80 | 2.27 | 1.80 | 0.01  | 1.80 | 0.00  | 3.30     | 1.70  | 23.26 |         |  |            |  |       |       |

| Default mode    | 3.00 | 3.71 | 1.80 | 2.27 | 1.80 | 0.01  | 1.80 | 0.00  | 3.00     | 1.49  | 19.72 |         |  |            |  |       |       |

|                 | 2.40 | 2.93 | 1.80 | 2.27 | 1.80 | 0.00  | 1.80 | 0.00  | 2.40     | 1.12  | 13.82 |         |  |            |  |       |       |

|                 |      |      |      |      |      |       |      |       |          |       |       |         |  |            |  |       |       |

| Reduced power   | 3.30 | 2.57 | 1.80 | 2.27 | 1.80 | 0.01  | 1.80 | 0.00  | 3.30     | 1.70  | 18.20 |         |  |            |  |       |       |

| mode            | 3.00 | 2.33 | 1.80 | 2.27 | 1.80 | 0.01  | 1.80 | 0.00  | 3.00     | 1.49  | 15.57 |         |  |            |  |       |       |

|                 | 2.40 | 1.85 | 1.80 | 2.27 | 1.80 | 0.01  | 1.80 | 0.00  | 2.40     | 1.12  | 11.22 |         |  |            |  |       |       |

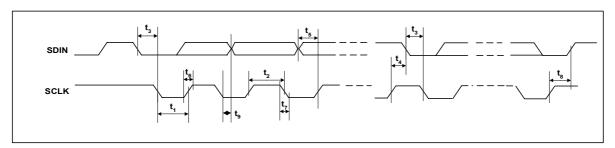

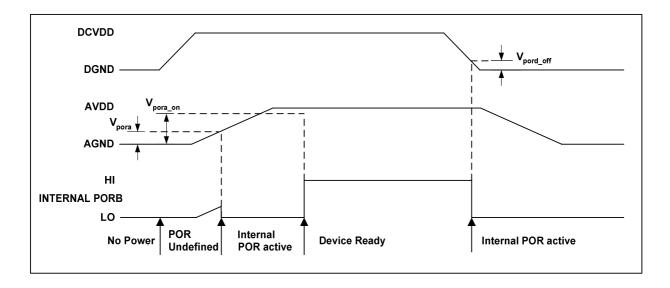

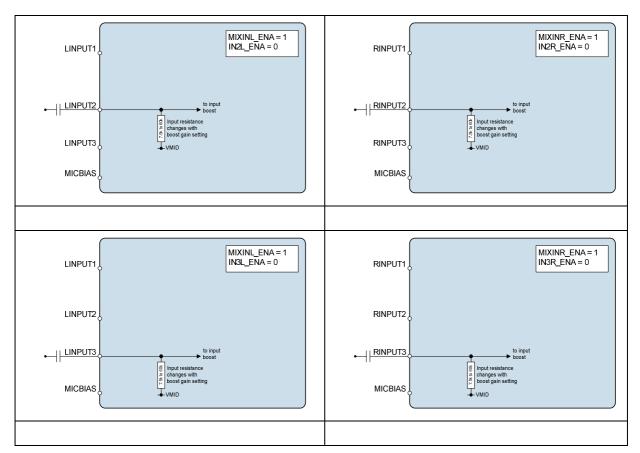

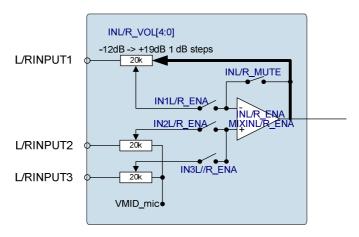

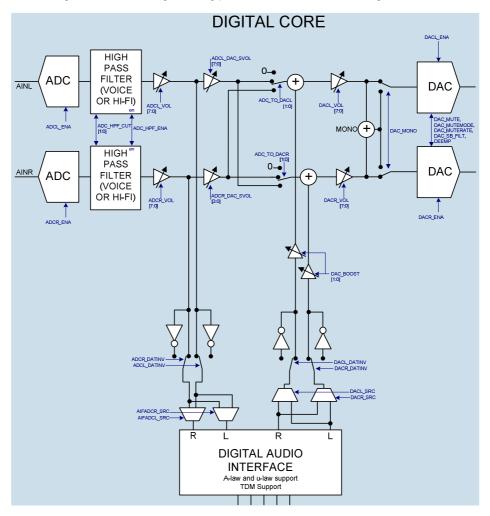

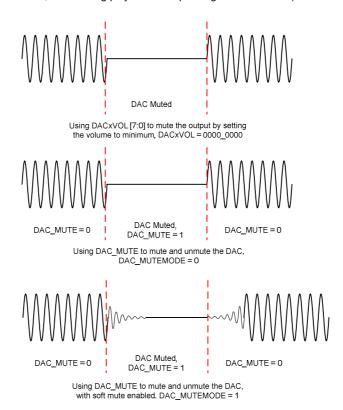

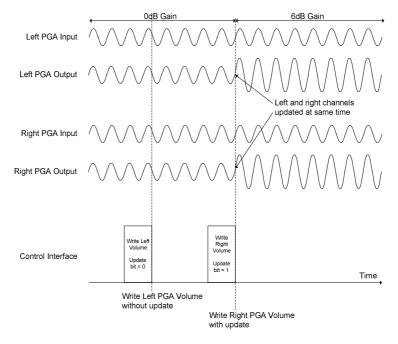

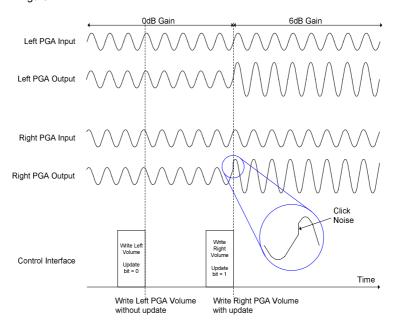

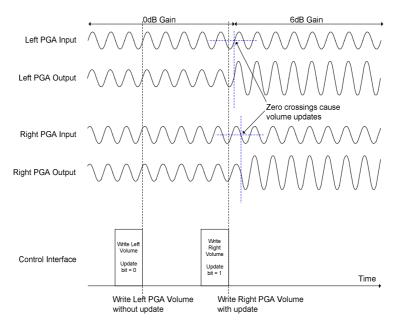

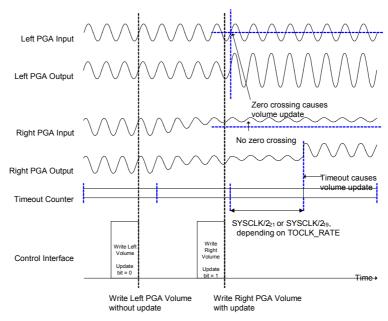

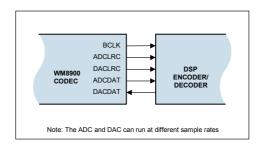

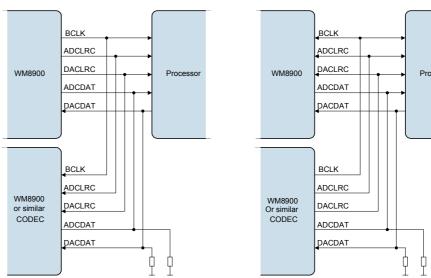

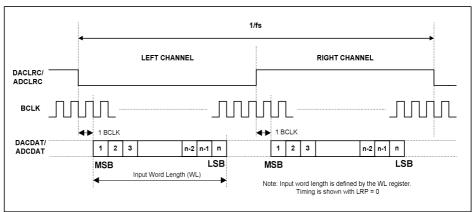

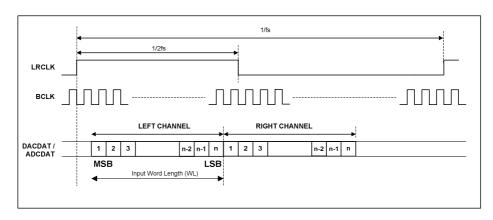

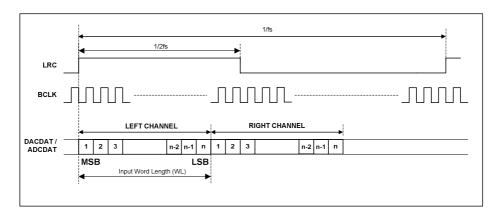

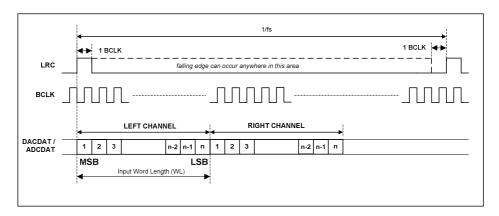

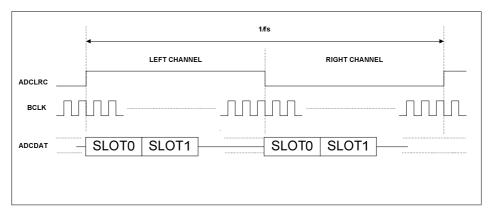

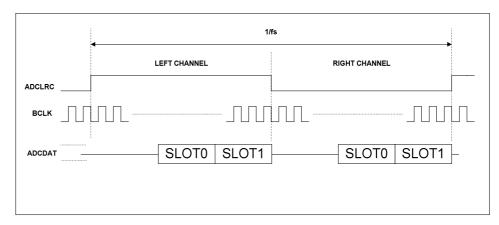

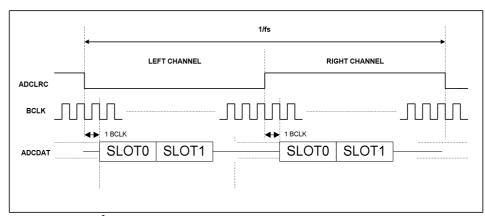

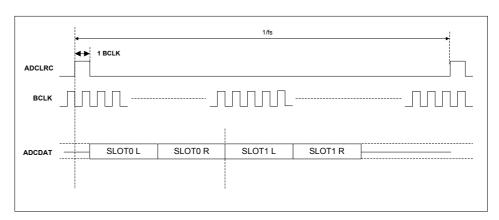

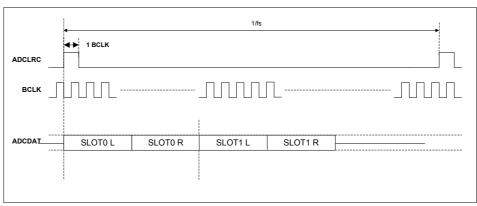

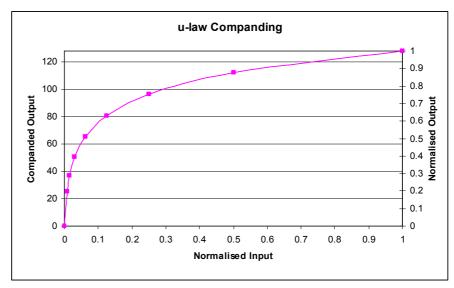

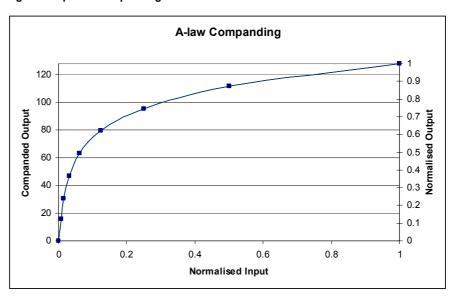

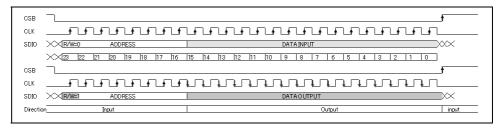

|                 |      |      |      |      |      |       |      |       |          |       |       |         |  |            |  |       |       |