May 2008

# FAN5099 — Wide Frequency Synchronous Buck PWM & LDO Controller

#### **Features**

- General Purpose PWM Regulator and LDO Controller

- Input Voltage Range: 3V to 24V

- Output Voltage Range: 0.8V to 15V

- V<sub>CC</sub>

- 5V

- Shunt Regulator for 12V Operation

- Support for Ceramic Cap on PWM Output

- Programmable Current Limit for PWM Output

- Wide Programmable Switching Frequency Range (50kHz to 600kHz)

- R<sub>DS(ON)</sub> Current Sensing

- Internal Synchronous Boot Diode

- Soft-Start for both PWM and LDO

- Multi-Fault Protection with Optional Auto-restart

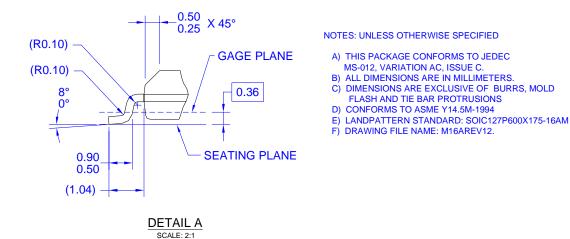

- 16-Pin TSSOP Package

## **Applications**

- High-Efficiency (80+) Computer Power Supples

- PC/Server Motherboard Peripherals

- V<sub>CC</sub>\_MCH (1.5V), V<sub>DDQ</sub> (1.5V) at V<sub>TT GTL</sub> (1.25V)

- Power Supply for

- FPGA, DSP, Embedded controllers, Graphic Card Processor, and Communication Processors

- High-Power DC-to-P Cc verte

# Related Application Involes

- AN-6020 F √5099 Com, Jnent Calcuing and Simulation Simulation

- AN-COS Syncial prous Buck MOSFET Los Coculations with Excel Mod

## **Description**

The FAN5099 combines a high-efficient puls, vidth modulated (PWM) controller and an LPO ( v droi out) linear regulator controller. The vVM controller are is designed to operate over a wide from each yrange (50kHz to 600kHz) to accommodate various of applications. Synchronous rectification revides ighter iciency over wide range of load currents. It iciency is from enhanced by using the way of JSFET's Revious sense current. In a circum, a capability to operate at low switching freedoms, by reducing switching sees and gain cost sales are using low-cost materials. The spowdered corumn output industor.

P the lin. or and PWM regul for cart are control of single extern capacity to limit in rush curant from the supply the capacity regulators are first on leo. Current lin. for PWM is also programmable.

FAN5099's billy to handle wide input voltage ranges make this entre or suitable for power solutions in a wide large lappeations involving conversion input voltages and Silver box, battery, and adapters. The PW M regular in inploys a summing-current-mode control with external compensation to achieve fast load transit asponse and provide system design optimization.

Nbc 9 is offered in both industrial temperature grade  $^{\circ}$ C to +85°C) as well as commercial temperature grade (-10°C to +85°C).

# L'de...ig Informa 'on

| Number      | Perat | g Temperature Range | Package       | Packing Method | Qty/Reel |

|-------------|-------|---------------------|---------------|----------------|----------|

| FAN5099MT X |       | -10℃ to +85℃        | 16-Lead TSSOP | Tape and Reel  | 2500     |

| FAN5099EMT  |       | -40℃ to +85℃        | 16-Lead TSSOP | Tape and Reel  | 2500     |

| FAN5099MX   |       | -10℃ to +85℃        | 16-Lead SOIC  | Tape and Reel  | 2500     |

| FAN5099EMX  |       | -40℃ to +85℃        | 16-Lead SOIC  | Tape and Reel  | 2500     |

All standard Fairchild Semiconductor products are RoHS compliant and many are also "GREEN" or going green. For Fairchild's definition of "green" please visit: http://www.fairchildsemi.com/company/green/rohs\_green.html.

Contact Fairchild sales for availability of other package options.

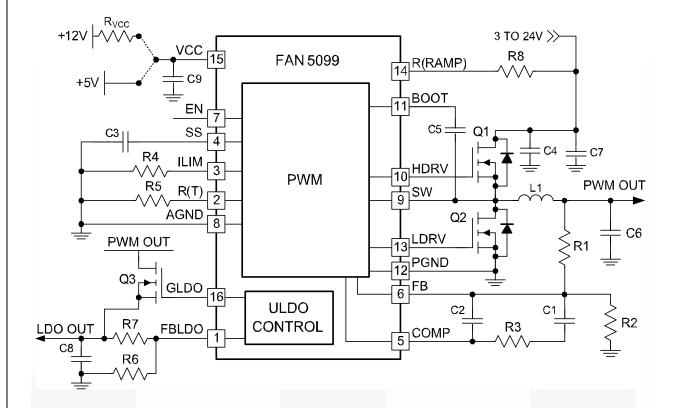

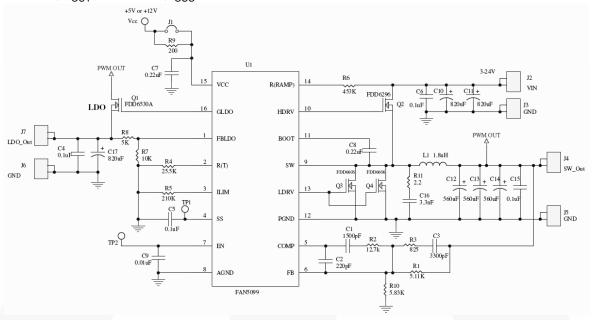

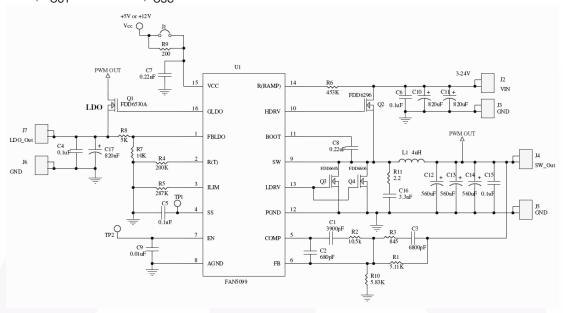

# **Typical Application**

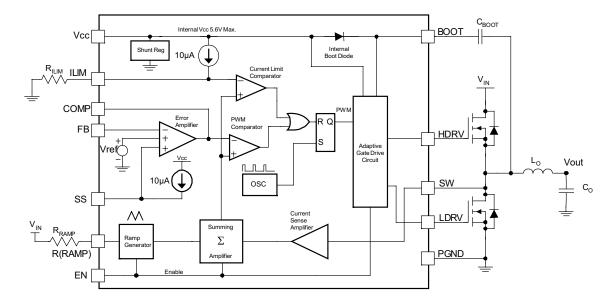

**Figure 1. Typical Application Diagram**

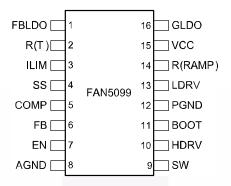

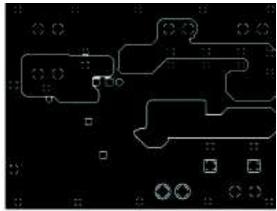

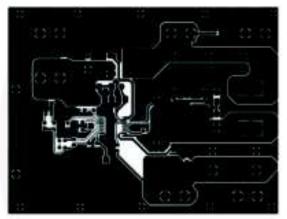

# **Pin Configuration**

Figure 2. Pin Assignment

# **Pin Description**

| 1 FBLDO LDO Feedback. This node is regulated to V <sub>REF</sub> .  2 R(T) Oscillator Set Resistor. This pin provides oscillator switchin ing a resistor (RT) from this pin to GND, the nominal 50kHz strong a resistor (RT) from this pin to GND sets the current Limit. A resistor from this pin to GND programs the strong soft-Start. A capacitor from this pin to GND programs the strong strong initialization. It also sets the time by which the after a fault occurs. SS has to reach 1.2V before fault shutch is enabled when SS reaches 2.2V.  5 COMP COMP. The output of the error amplifier drives this pin.  Feedback. This pin is the inverting input of the internal error nation with the COMP pin, to compensate the feedback loop latched fault condition. This is a CMOS input whose state needs to be properly biased at all times.  8 AGND Analog Ground. The signal ground for the IC. All internal compin. Tie this pin to the ground island/plane through the lowest to source of high-side MOSFET and drain of low-side MOSFET and drain of low-side MOSFET and bigh-side MOSFET is turned off. |                                                                                                              |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ing a resistor (RT) from this pin to GND, the nominal 50kHz s  ILIM Current Limit. A resistor from this pin to GND sets the curred Soft-Start. A capacitor from this pin to GND programs the sLDO during initialization. It also sets the time by which the after a fault occurs. SS has to reach 1.2V before fault shutder is enabled when SS reaches 2.2V.  COMP. The output of the error amplifier drives this pin.  Feedback. This pin is the inverting input of the internal error nation with the COMP pin, to compensate the feedback loop latched fault condition. This is a CMOS input whose state needs to be properly biased at all times.  AGND Analog Ground. The signal ground for the IC. All internal compin. Tie this pin to the ground island/plane through the lowest to source of high-side MOSFET and drain of low-side MOSFET driver are to source of high-side MOSFET and drain of low-side MOSFET and drain of low-side MOSFET and pin is also monitored by the adaptive shoot-through protection.                                                                                                | Feedback. This node is regulated to V <sub>REF</sub> .                                                       |  |  |  |  |  |

| Soft-Start. A capacitor from this pin to GND programs the set LDO during initialization. It also sets the time by which the after a fault occurs. SS has to reach 1.2V before fault shutder is enabled when SS reaches 2.2V.  5 COMP COMP. The output of the error amplifier drives this pin.  Feedback. This pin is the inverting input of the internal error nation with the COMP pin, to compensate the feedback loop latched fault condition. This is a CMOS input whose state needs to be properly biased at all times.  AGND Analog Ground. The signal ground for the IC. All internal copin. Tie this pin to the ground island/plane through the lowest to source of high-side MOSFET and drain of low-side MOSF High-Side Gate Drive Output. Connect to the gate of the pin is also monitored by the adaptive shoot-through protection.                                                                                                                                                                                                                                                                           |                                                                                                              |  |  |  |  |  |

| LDO during initialization. It also sets the time by which the after a fault occurs. SS has to reach 1.2V before fault shutch is enabled when SS reaches 2.2V.  COMP COMP. The output of the error amplifier drives this pin.  Feedback. This pin is the inverting input of the internal error nation with the COMP pin, to compensate the feedback loop latched fault condition. This is a CMOS input whose state needs to be properly biased at all times.  AGND Analog Ground. The signal ground for the IC. All internal copin. Tie this pin to the ground island/plane through the lowest to source of high-side MOSFET and drain of low-side MOSFET to source of high-side MOSFET and drain of low-side MOSFET to pin is also monitored by the adaptive shoot-through protection.                                                                                                                                                                                                                                                                                                                                    | nt limit.                                                                                                    |  |  |  |  |  |

| FB Feedback. This pin is the inverting input of the internal error nation with the COMP pin, to compensate the feedback loop  Enable. Enables operation when pulled to logic high. Togglin latched fault condition. This is a CMOS input whose state needs to be properly biased at all times.  AGND Analog Ground. The signal ground for the IC. All internal copin. Tie this pin to the ground island/plane through the lowest to source of high-side MOSFET and drain of low-side MOSFET driver are to source of high-side MOSFET and drain of low-side MOSFET the pin is also monitored by the adaptive shoot-through protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | converter delays when restarting                                                                             |  |  |  |  |  |

| nation with the COMP pin, to compensate the feedback loop  Enable. Enables operation when pulled to logic high. Togglin latched fault condition. This is a CMOS input whose state needs to be properly biased at all times.  Analog Ground. The signal ground for the IC. All internal copin. Tie this pin to the ground island/plane through the lowest to source of high-side MOSFET and drain of low-side MOSFET driver are to source of high-side MOSFET and drain of low-side MOSFET and the pin is also monitored by the adaptive shoot-through protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |  |  |  |  |  |

| 7 EN latched fault condition. This is a CMOS input whose state needs to be properly biased at all times.  8 AGND Analog Ground. The signal ground for the IC. All internal compiners pin. Tie this pin to the ground island/plane through the lowest to source of high-side MOSFET and drain of low-side MOSFET and drain of low-side MOSFET and the pin is also monitored by the adaptive shoot-through protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |  |  |  |  |  |

| 9 SW Switching Node. Return for the high-side MOSFET driver are to source of high-side MOSFET and drain of low-side MOSFET and the gate of the pin is also monitored by the adaptive shoot-through protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |  |  |  |  |  |

| to source of high-side MOSFET and drain of low-side MOSF  High-Side Gate Drive Output. Connect to the gate of the pin is also monitored by the adaptive shoot-through protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                              |  |  |  |  |  |

| 10 HDRV pin is also monitored by the adaptive shoot-through protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                              |  |  |  |  |  |

| BOOT Bootstrap Supply Input. Provides a boosted voltage to the Connect to bootstrap capacitor as shown in Figure 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | high-side MOSFET driver.                                                                                     |  |  |  |  |  |

| PGND Power Ground. The return for the low-side MOSFET drive MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | r. Connect to source of low-side                                                                             |  |  |  |  |  |

| Low-Side Gate Drive Output. Connect to the gate of the low is also monitored by the adaptive shoot-through protection lower MOSFET is turned off.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |  |  |  |  |  |

| 14 R(RAMP) Ramp Resistor. A resistor from this pin to VIN sets the ram feed-forward.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>amp Resistor</b> . A resistor from this pin to VIN sets the ramp amplitude and provides volta ed-forward. |  |  |  |  |  |

| V <sub>CC</sub> . Provides bias power to the IC and the drive voltage f capacitor as close to this pin as possible. This pin has a shu when the input voltage is above 5.6V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                              |  |  |  |  |  |

| 16 GLDO Gate Drive for the LDO. Turned off (low) until SS is greater                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                              |  |  |  |  |  |

## **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only. Absolute maximum ratings apply individually only, not in combination. Unless otherwise specified, all other voltages are referenced to AGND.

| Parameter                                      |                                                    | Min. | Max.                  | Unit |  |

|------------------------------------------------|----------------------------------------------------|------|-----------------------|------|--|

| VCC to GND                                     | Continuous                                         |      | 6.0                   | V    |  |

| POOT to CND                                    | Continuous                                         | -0.3 | 33                    | V    |  |

| BOOT to GND                                    | Transient (t < 100ns, f < 500kHz)                  | -0.5 | 35                    | V    |  |

| BOOT to SW                                     | Continuous                                         | -0.5 | 6.0                   | V    |  |

| BOOT to SW                                     | Transient (t < 50ns, f < 500kHz)                   | -2.5 |                       | V    |  |

| SW to GND                                      | Continuous                                         | -0.5 | 33.0                  | V    |  |

| SW to GND                                      | Transient (t < 50ns, f < 500kHz)                   | -3.0 | 35.0                  | V    |  |

| HDRV to SW                                     | Continuous                                         | -0.5 | 6.0                   | V    |  |

| INDRV 10 SW                                    | Transient (t < 40ns, f < 500kHz)                   | -2.5 |                       | V    |  |

| LDRV to PGND                                   | Continuous                                         | -0.5 | 6.0                   | V    |  |

| LDRV to PGND                                   | Transient (t < 40ns, f < 500kHz)                   | -2.5 |                       | V    |  |

| All Other Pins                                 | Continuous                                         | -0.3 | V <sub>CC</sub> + 0.3 | V    |  |

| Maximum Shunt Current                          |                                                    |      | 150                   | mA   |  |

| Electrostatic Discharge (ESD) Protection Level | Human Body Model<br>(Mil Std. 883E, Method 3015.7) | 3.5  |                       | kV   |  |

| Electrostatic Discharge (ESD) Protection Level | Charged Device Model<br>(EIA/JESD22C101-A)         | 1.8  |                       | KV   |  |

## **Thermal Information**

| Symbols          | Parameter                                               | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------------------------------|------|------|------|------|

| T <sub>STG</sub> | Storage Temperature                                     | -65  |      | +150 | C    |

| $T_L$            | Lead Soldering Temperature, 10 Seconds                  |      |      | +300 | C    |

|                  | Vapor Phase, 60 Seconds                                 |      |      | +215 | C    |

|                  | Infrared, 15 Seconds                                    |      |      | +220 | S    |

| P <sub>D</sub>   | Power Dissipation, T <sub>A</sub> = 25℃                 |      |      | 715  | mW   |

| $\theta_{JC}$    | Thermal Resistance – Junction-to-Case                   |      | 37   |      | €/M  |

| $\theta_{JA}$    | Thermal Resistance – Junction-to-Ambient <sup>(1)</sup> |      | 100  |      | €/M  |

#### Notes:

Junction-to-ambient thermal resistance, θ<sub>JA</sub>, is a strong function of PCB material, board thickness, thickness and number of copper planes, number of vias used, diameter of vias used, available copper surface, and attached heat sink characteristics.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbols         | Parameter            | Conditions             | Min. | Тур. | Max. | Unit |

|-----------------|----------------------|------------------------|------|------|------|------|

| V <sub>CC</sub> | Supply Voltage       | V <sub>CC</sub> to GND | 4.5  | 5.0  | 5.5  | V    |

| T <sub>A</sub>  | Ambient Temperature  | Commercial             | -10  |      | +85  | C    |

| 'A              | Ambient Temperature  | Industrial             | -40  |      | +85  | C    |

| T <sub>J</sub>  | Junction Temperature |                        |      |      | +125 | S    |

## **Electrical Characteristics**

Unless otherwise noted,  $V_{CC}$  = 5V,  $T_A$  = 25°C, using the circuit in Figure 1. The '•' denotes that the specifications apply to the full ambient operating temperature range. (2,3)

| Symbol                | Parameter                                    | Conditions                                                     |   | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------------------------------|----------------------------------------------------------------|---|------|------|------|------|

| Supply Cu             | urrent                                       |                                                                |   |      |      |      |      |

| I <sub>VCC</sub>      | V <sub>CC</sub> Current (Quiescent)          | HDRV, LDRV Open                                                | • | 2.6  | 3.2  | 3.8  | mA   |

| I <sub>VCC(SD)</sub>  | V <sub>CC</sub> Current (Shutdown)           | $EN = 0V, V_{CC} = 5.5V$                                       | • |      | 200  | 400  | μА   |

| I <sub>VCC(OP)</sub>  | V <sub>CC</sub> Current (Operating)          | $EN = 5V, V_{CC} = 5.0V,$<br>$Q_{FET} = 20nC, f_{SW} = 200kHz$ |   |      | 10   | 15   | mA   |

| V <sub>SHUNT</sub>    | V <sub>CC</sub> Voltage <sup>(4)</sup>       | Sinking 1mA to 100mA at V <sub>CC</sub> Pin                    |   | 5.4  |      | 5.9  | V    |

| Under-Vol             | tage Lockout (UVLO)                          |                                                                |   |      |      |      |      |

| UVLO(H)               | Rising V <sub>CC</sub> UVLO Threshold        |                                                                | • | 4.00 | 4.25 | 4.50 | V    |

| UVLO(L)               | Falling V <sub>CC</sub> UVLO Threshold       |                                                                | • | 3.60 | 3.75 | 4.00 | V    |

|                       | V <sub>CC</sub> UVLO Threshold<br>Hysteresis |                                                                |   |      | 0.5  |      | V    |

| Soft-Start            |                                              |                                                                |   |      |      |      |      |

| I <sub>SS</sub>       | Current                                      |                                                                |   |      | 10   |      | μА   |

| V <sub>LDOSTART</sub> | LDO Start Threshold                          |                                                                |   |      | 2.2  |      | V    |

| V <sub>SSOK</sub>     | PWM Protection Enable<br>Threshold           |                                                                |   |      | 1.2  | y    | V    |

| Oscillator            |                                              |                                                                |   |      |      |      | •    |

|                       |                                              | $R(T) = 25.5K\Omega \pm 1\%$                                   |   | 240  | 300  | 360  | kHz  |

| fosc                  | Frequency                                    | $R(T) = 199K\Omega \pm 1\%$                                    |   | 60   | 80   | 100  | kHz  |

|                       |                                              | R(T) = Open                                                    |   |      | 50   |      | kHz  |

|                       | Operating Frequency Range                    |                                                                |   | 40   |      | 600  | kHz  |

| $\Delta V_{RAMP}$     | Ramp Amplitude<br>(Peak-to-Peak)             | R(RAMP) = 330KΩ                                                |   |      | 0.4  |      | V    |

|                       | Minimum On Time                              | f = 200kHz                                                     |   |      | 200  |      | ns   |

| Reference             |                                              |                                                                |   |      |      |      |      |

| \/                    | Reference Voltage                            | $T_A = 0$ °C to $70$ °C                                        | • | 790  | 800  | 810  | mV   |

| $V_{REF}$             | (Measured at FB Pin)                         | T <sub>A</sub> = -40℃ to 85℃                                   | • | 788  | 800  | 812  | mV   |

|                       | Current Amplifier Reference (at SW node)     |                                                                |   |      | 160  |      | mV   |

|                       |                                              | •                                                              |   |      |      |      |      |

Continued on the following page...

## **Electrical Characteristics** (Continued)

Unless otherwise noted,  $V_{CC}$  = 5V,  $T_A$  = 25°C, using the circuit in Figure 1. The ' •' denotes that the specifications apply to the full ambient operating temperature range. (2, 3)

| Symbol              | Parameter                  | Conditions                                                                                             |   | Min. | Тур. | Max.     | Unit |

|---------------------|----------------------------|--------------------------------------------------------------------------------------------------------|---|------|------|----------|------|

| Error Am            | olifier                    |                                                                                                        |   |      | •    | •        |      |

|                     | DC Gain                    |                                                                                                        |   |      | 80   |          | dB   |

| GBWP                | Gain-BW Product            |                                                                                                        |   |      | 25   |          | MHz  |

| S/R                 | Slew Rate                  | 10pF across COMP to GND                                                                                |   |      | 8    |          | V/µS |

|                     | Output Voltage Swing       | No Load                                                                                                | • | 0.5  |      | 4.0      | V    |

| I <sub>FB</sub>     | FB Pin Source Current      |                                                                                                        |   |      |      |          | μА   |

| Gate Drive          | e                          |                                                                                                        |   |      | •    | •        |      |

| R <sub>HUP</sub>    | HDRV Pull-up Resistor      | Sourcing                                                                                               | • |      | 1.8  | 3.0      | Ω    |

| R <sub>HDN</sub>    | HDRV Pull-down Resistor    | Sinking                                                                                                | • |      | 1.8  | 3.0      | Ω    |

| R <sub>LUP</sub>    | LDRV Pull-up Resistor      | Sourcing                                                                                               | • |      | 1.8  | 3.0      | Ω    |

| R <sub>LDN</sub>    | LDRV Pull-down Resistor    | Sinking                                                                                                | • |      | 1.2  | 2.0      | Ω    |

| Protection          | n/Disable                  |                                                                                                        |   |      | •    |          |      |

| I <sub>LIM</sub>    | ILIMIT Source Current      |                                                                                                        |   | 9    | 10   | 11       | μА   |

| I <sub>SWPD</sub>   | SW Pull-down Current       | SW = 1V, EN = 0V                                                                                       |   |      | V    |          | mA   |

| V <sub>UV</sub>     | Under-Voltage Threshold    | As % of set point;<br>2µS noise filter                                                                 |   | 65   | 75   | 80       | %    |

| V <sub>OV</sub>     | Over-Voltage Threshold     | As % of set point;<br>2μS noise filter                                                                 | • | 110  | 115  | 120      | %    |

| Supply C            | urrent                     |                                                                                                        |   |      |      | •        |      |

| TSD                 | Thermal Shutdown           |                                                                                                        |   |      | 160  |          | C    |

|                     | 5 II TI I III I            | Enable Condition                                                                                       | • | 2.0  |      |          | V    |

| V <sub>EN</sub>     | Enable Threshold Voltage   | Disable Condition                                                                                      | • |      |      | 0.8      | V    |

|                     | Enable Source Current      | $V_{CC} = 5V$                                                                                          |   |      | 50   |          | μА   |

|                     | Enable Sink Current        | V <sub>CC</sub> = 5V and fault conditions<br>(overload, short-circuit,<br>over-voltage, under-voltage) |   |      | 10   |          | μА   |

| Low Dro             | p-Out (LDO) <sup>(5)</sup> |                                                                                                        |   |      | •    | <u>'</u> |      |

| M                   | Reference Voltage          | $T_A = 0$ °C to $70$ °C                                                                                | • | 775  | 800  | 825      | mV   |

| V <sub>LDOREF</sub> | (measured at FBLDO pin)    | T <sub>A</sub> = -40℃ to 85℃                                                                           | • | 770  | 800  | 830      | mV   |

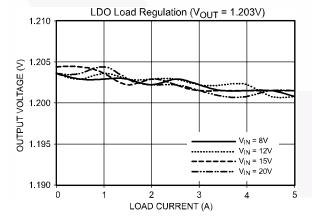

|                     | Regulation                 | $0A \le I_{LOAD} \le 5A$                                                                               | • | 1.17 | 1.20 | 1.23     | V    |

| $V_{LDO\_DO}$       | Drop-out Voltage           | $I_{LOAD} \le 5A$ and $R_{DS-ON} < 50m\Omega$                                                          |   |      |      | 0.3      | V    |

|                     | External Cata Drive        | V <sub>CC</sub> = 4.75V                                                                                | • |      |      | 4.5      | V    |

|                     | External Gate Drive        | V <sub>CC</sub> = 5.6V                                                                                 | • |      |      | 5.3      | V    |

|                     | Gate Drive Source Current  |                                                                                                        |   |      | 1.2  |          | mA   |

|                     | Gate Drive Sink Current    |                                                                                                        |   |      | 400  |          | μΑ   |

#### Notes:

- 2. All limits at operating temperature extremes are guaranteed by design, characterization, and statistical quality control.

- 3. AC specifications guaranteed by design/characterization (not production tested).

- 4. For a case when  $V_{CC}$  is higher than the typical 5V  $V_{CC}$ , voltage observed at  $V_{CC}$  pin when the internal shunt regulator is sinking current to keep voltage on  $V_{CC}$  pin constant.

- 5. Test Conditions:  $V_{LDO\ IN} = 1.5V$  and  $V_{LDO\ OUT} = 1.2V$ .

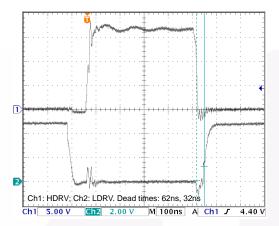

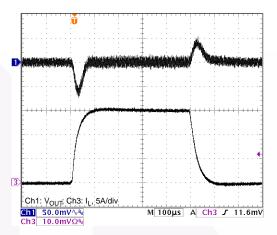

## **Typical Performance Characteristics**

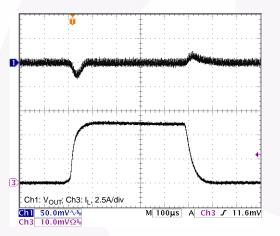

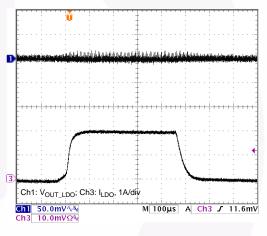

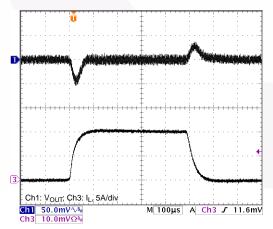

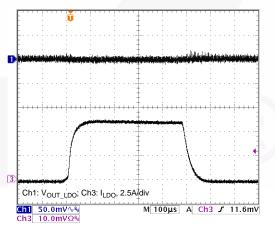

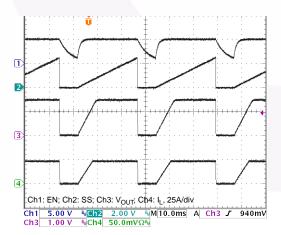

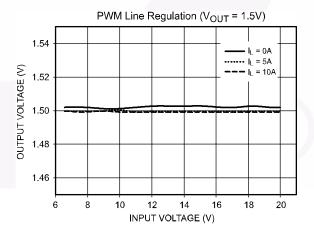

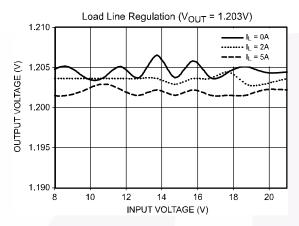

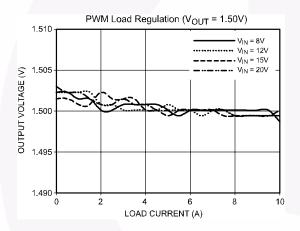

$V_{IN} = 12 \text{V}, \ V_{dd} = 5 \text{V}, \ V_{OUT} = 1.5 \text{V}, \ V_{Ido} = 1.2 \text{V}, \ I_{load} = 5 \text{A}, \ I_{Ido} = 2 \text{A}, \ f_{osc} = 300 \text{kHz}, \ unless \ otherwise \ noted.$

Figure 3. Dead Time Waveform

Figure 6. PWM Load Transient (0 to 15A)

Figure 4. PWM Load Transient (0 to 5A)

Figure 7. LDO Load Transient (0 to 2A)

Figure 5. PWM Load Transient (0 to 10A)

Figure 8. LDO Load Transient (0 to 5A)

## Typical Performance Characteristics (Continued)

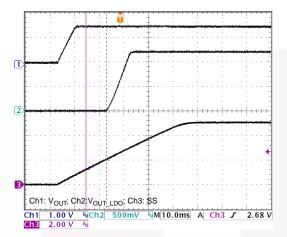

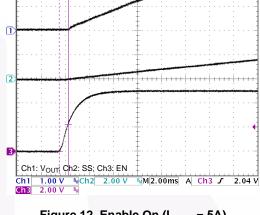

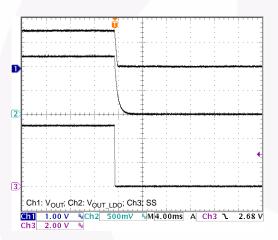

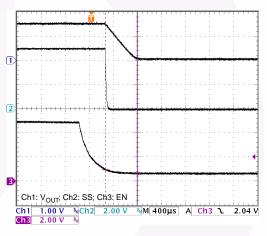

$V_{IN}$  = 12V,  $V_{dd}$  = 5V,  $V_{OUT}$  = 1.5V,  $V_{Ido}$  = 1.2V,  $I_{load}$  = 5A,  $I_{Ido}$  = 2A,  $I_{osc}$  = 300kHz, unless otherwise noted.

Figure 9. PWM/LDO Power Up

Figure 12. Enable On  $(I_{PWM} = 5A)$

Figure 10. PWM/LDO Power Down

Figure 13. Enable Off  $(I_{PWM} = 5A)$

Figure 11. Auto Restart

Figure 14. PWM Line Regulation

## Typical Performance Characteristics (Continued)

$V_{IN} = 12 \text{V}, \ V_{dd} = 5 \text{V}, \ V_{OUT} = 1.5 \text{V}, \ V_{Ido} = 1.2 \text{V}, \ I_{load} = 5 \text{A}, \ I_{Ido} = 2 \text{A}, \ f_{osc} = 300 \text{kHz}, \ unless \ otherwise \ noted.$

Figure 15. LDO Load Regulation

Figure 16. PWM Load Regulation

Figure 17. LDO Load Regulation

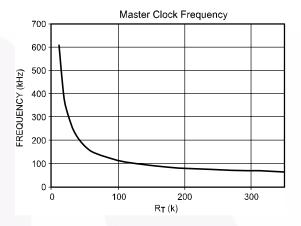

Figure 18. R<sub>T</sub> vs. Frequency

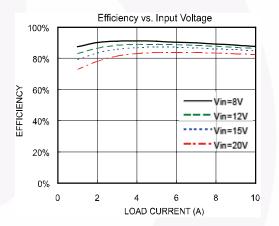

Figure 19. 1.5V PWM Efficiency

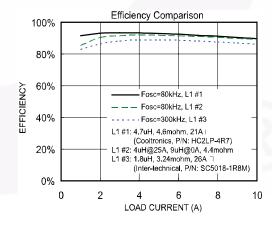

Figure 20. Efficiency Comparison at  $V_{\text{IN}}$ =12V

## **Block Diagram**

Figure 21. Block Diagram

## **Detailed Operation Description**

FAN5099 combines a high-efficiency, fixed-frequency PWM controller designed for single-phase synchronous buck Point-Of-Load converters with an integrated LDO controller to support GTL-type loads. This controller is ideally suited to deliver low-voltage, high-current power supplies needed in desktop computers, notebooks, workstations, and servers. The controller comes with an integrated boot diode which helps reduce component cost and increase space savings. With this controller, the input to the power supply can be varied from 3V to 24V and the output voltage can be set to regulate at 0.8V to 15V on the switcher output. The LDO output can be configured to regulate between 0.8V to 3V and the input to the LDO can be from 1.5V to 5V, respectively. An internal shunt regulator at the V<sub>CC</sub> pin facilitates the controller operation from either a 5V or 12V power source.

#### **V<sub>CC</sub>** Bias Supply

FAN5099 can be configured to operate from 5V or 12V for  $V_{CC}$ . When 5V supply is used for  $V_{CC}$ , no resistor is required to be connected between the supply and the  $V_{CC}$ . When the 12V supply is used, a resistor  $R_{VCC}$  is connected between the 12V supply and the  $V_{CC}$ , as shown in Figure 1. The internal shunt regulator at the  $V_{CC}$  pin is capable of sinking 150mA of current to ensure the controller's internal  $V_{CC}$  is maintained at 5.6V maximum.

Choose a resistor such that:

- It is rated to handle the power dissipation.

- Current sunk within the controller is minimized to prevent IC temperature rise.

## R<sub>VCC</sub> Selection (IC)

The selection of R<sub>VCC</sub> is dependent on:

- Variation of the 12V supply

- Sum of gate charges of top and bottom FETs (Q<sub>FFT</sub>)

- Switching frequency (f<sub>SW</sub>)

- Shunt regulator minimum current (1mA)

- Quiescent Current of the IC (I<sub>O</sub>)

Calculate  $R_{VCC}$  based on the minimum input voltage for the  $V_{CC}\!:$

$$R_{VCC} = \frac{V_{IN_{MIN}} - 5.6}{(I_{Q} + 1 \bullet 10^{-3} + Q_{FET} \bullet f_{SW} \bullet 1.2)}$$

(EQ. 1)

For a typical example, where:

$V_{INMIN}$  = 11.5V,  $I_Q$  = 3mA,  $Q_{FET}$  = 30nC,  $f_{SW}$  = 300kHz,  $R_{VCC}$  is calculated to be 398.65 $\Omega$ .

#### **PWM Section**

The FAN5099's PWM controller combines the conventional voltage mode control and current sensing through lower MOSFET  $R_{DS\_ON}$  to generate the PWM signals. This method of current sensing is loss-less and cost effective. For more accurate current sense requirements, an optional external resistor can be connected with the bottom MOSFET in series.

#### **PWM Operation**

Refer to Figure 21 for the PWM control mechanism. The FAN5099 uses the summing mode method of control to generate the PWM pulses. The amplified output of the current-sense amplifier is summed with an internally generated ramp and the combined signal is amplified and compared with the output of the error amplifier to get the pulse width to drive the high-side MOSFET. The sensed current from the previous cycle is used to modulate the output of the summing block. The output of the summing block is also compared against the voltage threshold set by the  $R_{\rm LIM}$  resistor to limit the inductor current on a cycle-by-cycle basis. The controller facilitates external compensation for enhanced flexibility.

#### Initialization

When the PWM is disabled, the SW node is connected to GND through an internal  $500\Omega$  MOSFET to slowly discharge the output. As long as the PWM controller is enabled, this internal MOSFET remains OFF.

#### Soft-Start (PWM and LDO)

When  $V_{CC}$  exceeds the UVLO threshold and EN is high, the circuit releases SS and enables the PWM regulator. The capacitor connected to the SS pin and GND is charged by a 10µA internal current source, causing the voltage on the capacitor to rise. When this voltage exceeds 1.2V, all protection circuits are enabled. When this voltage exceeds 2.2V, the LDO output is enabled. The input to the error amplifier at the non-inverting pin is clamped by the voltage on the SS pin until it crosses the reference voltage.

The time it takes the PWM output to reach regulation  $(t_{Rise})$  is calculated using the following equation:

$$t_{RISE} = 8 \times 10^{-2} \times C_{SS}$$

(C<sub>SS</sub> is in µf) (EQ. 2)

## **Oscillator Clock Frequency (PWM)**

The clock frequency on the oscillator is set using an external resistor, connected between R(T) pin and ground. The frequency follows the graph, as shown in Figure 18. The minimum clock frequency is 50kHz, which is when R(T) pin is left open. Select the value of R(T) as shown in the equation below. This equation is valid for all  $F_{OSC} > 50 \text{kHz}$ :

$$R(t) = \frac{4 \times 10^{7}}{6.25 \times f_{OSC} - 2.99 \times 10^{5}} k\Omega$$

(EQ. 3)

where, f<sub>OSC</sub> is in Hz.

For example, for  $f_{OSC} = 80kHz$ ,  $R(t) = 199k\Omega$ .

## **RRAMP** Selection and Feedforward Operation

The FAN5099 provides for input voltage feedforward compensation through  $R_{RAMP}$ . The value of  $R_{RAMP}$  effective feedback of the second second

tively changes the slope of the internal ramp, minimizing the variation of the PWM modulator gain when input voltage varies. The  $R_{RAMP}$  effect on the current limit is explained in later sections. The  $R_{RAMP}$  value can be approximated using the following equation:

$$R_{RAMP} = \frac{V_{(IN, nom)} - 1.8}{6.3 \times 10^{-8} \times F_{OSC}} K\Omega$$

(EQ. 4)

where  $f_{OSC}$  is in Hz. For example, for  $f_{OSC}$  = 80kHz and  $V_{IN}$  = 12V,  $R_{RAMP}$  =  $2M\Omega.$

#### **Gate Drive Section**

The adaptive gate control logic translates the internal PWM control signal into the MOSFET gate drive signals and provides necessary amplification, level shifting, and shoot-through protection. It also has functions that help optimize the IC performance over a wide range of operating conditions. Since the MOSFET switching time can vary dramatically from device to device and with the input voltage, the gate control logic provides adaptive dead time by monitoring the gate-to-source voltages of both upper and lower MOSFETs. The lower MOSFET drive is not turned on until the gate-to-source voltage of the upper MOSFET has decreased to less than approximately 1V. Similarly, the upper MOSFET is not turned on until the gate-to-source voltage of the lower MOSFET has decreased to less than approximately 1V. This allows a wide variety of upper and lower MOSFETs to be used without a concern for simultaneous conduction, or shoot-through.

A low impedance path between the driver pin and the MOSFET gate is recommended for the adaptive dead-time circuit to work properly. Any delay along this path reduces the delay generated by the adaptive dead-time circuit, thereby increasing the chances for shoot-through.

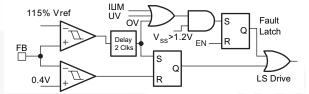

#### **Protection**

In the FAN5099, the converter is protected against overload, short-circuit, over-voltage, and under-voltage conditions. All of these extreme conditions generate an internal "fault latch" which shuts down the converter. For all fault conditions, both the high-side and the low-side drives are off, except in the case of OVP, where the low-side MOSFET is turned on until the voltage on the FB pin goes below 0.4V. The fault latch can be reset either by toggling the EN pin or recycling  $V_{\rm CC}$  to the chip.

## **Over-Current Limit (PWM)**

The PWM converter is protected against overloading through a cycle-by-cycle current limit set by selecting  $R_{\rm ILIM}$  resistor. An internal 10µA current source sets the threshold voltage for the output of the summing amplifier. When the summing amplifier output exceeds this threshold level, the current limit comparator trips and the PWM starts skipping pulses. If the current limit tripping occurs for 16 continuous clock cycles, a fault latch is set and the

controller shuts down the converter. This shutdown feature is disabled during the start-up until the voltage on the SS capacitor crosses 1.2V.

To achieve current limit, the FAN5099 monitors the inductor current during the OFF time by monitoring and holding the voltage across the lower MOSFET. The voltage across the lower MOSFET is sensed between the PGND and the SW pins.

The output of the summing amplifier is a function of the inductor current,  $R_{DS\_ON}$  of the bottom FET and the gain of the current sense amplifier. With the  $R_{DS\_ON}$  method of current sensing, the current limit can vary widely from unit to unit.  $R_{DS\_ON}$  not only varies from unit to unit, but also has a typical junction temperature coefficient of about 0.4%/°C (consult the MOSFET datasheet for actual values). The set point of the actual current limit decreases in proportion to increase in MOSFET die temperature. A factor of 1.6 in the current limit set point typically compensates for all MOSFET  $R_{DS\_ON}$  variations, assuming the MOSFET's heat sinking keeps its operating die temperature below 125°C.

For more accurate current limit setting, use resistor sensing. In a resistor sensing scheme, an appropriate current sense resistor is connected between the source terminal of the bottom MOSFET and PGND.

Set the current limit by choosing R<sub>ILIM</sub> as follows:

$$\mathsf{R}_{\mathsf{ILIM}} = \left[ 128 + \frac{\mathsf{K1} \cdot \mathsf{I}_{\mathsf{MAX}} \cdot \mathsf{R}_{\mathsf{DSON}} \cdot 10^{3}}{1.43} + \left( \left(1 - \frac{1.8}{\mathsf{V}_{\mathsf{IN}}}\right) \cdot \frac{\mathsf{V}_{\mathsf{OUT}} \cdot 33.32 \cdot 10^{11}}{f_{\mathsf{SW}} \cdot \mathsf{R}_{\mathsf{RAMP}}} \right) \right]$$

(EQ. 5)

where:

$R_{ILIM}$  is in  $K\Omega$ ;

I<sub>MAX</sub> is the maximum load current; and

K1 is a constant to accommodate for the variation of MOSFET  $R_{DS(ON)}$  (typically 1.6).

With K<sub>1</sub> = 1.6, I<sub>MAX</sub> = 20A, R<sub>DS(ON)</sub> =  $7m\Omega$ , V<sub>IN</sub> = 24V, V<sub>OUT</sub> = 1.5V, f<sub>SW</sub> = 300 kHz, R<sub>RAMP</sub> = 400 K $\Omega$ , R<sub>ILIM</sub> calculates to be 323.17K $\Omega$ .

#### **Auto Restart (PWM)**

The FAN5099 supports two modes of response when the internal fault latch is set. The user can configure it to keep the power supply latched in the OFF state OR in the auto restart mode. When the EN pin is tied to  $V_{\rm CC}$ , the power supply is latched OFF. When the EN pin is terminated with a 100nF to GND, the power supply is in auto restart mode. The table below describes the relationship between PWM restart and setting on EN pin. Do not leave the EN pin open without any capacitor.

| EN Pin          | PWM/Restart                                                               |

|-----------------|---------------------------------------------------------------------------|

| Pull to GND     | OFF                                                                       |

| V <sub>CC</sub> | No restart after fault                                                    |

| Cap to GND      | Restart after<br>t <sub>DELAY</sub> (Sec.) = 0.85 x C<br>where C is in μF |

The fault latch can also be reset by recycling the  $V_{\mbox{\footnotesize CC}}$  to the controller.

#### **Under Voltage Protection (PWM)**

The PWM converter output is monitored constantly for under voltage at the FB pin. If the voltage on the FB pin stays lower than 75% of internal  $V_{REF}$  for 16 clock cycles, the fault latch is set and the converter shuts down. This shutdown feature is disabled during startup until the voltage on the SS capacitor reaches 1.2V.

#### **Over-Voltage Protection (PWM)**

The PWM converter output voltage is monitored constantly at the FB pin for over voltage. If the voltage on the FB pin stays higher than 115% of internal  $V_{REF}$  for two-clock cycles, the controller turns OFF the upper MOSFET and turns ON the lower MOSFET. This crowbar action stops when the voltage on the FB pin comes down to 0.4V to prevent the output voltage from becoming negative. This over-voltage protection (OVP) feature is active when the voltage on the EN pin becomes HIGH.

Turning ON the low-side MOSFETs on an OVP condition pulls down the output, resulting in a reverse current, which starts to build up in the inductor. If the output overvoltage is due to failure of the high-side MOSFET, this crowbar action pulls down the input supply or blows its fuse, protecting the system, which is very critical.

During soft-start, if the output overshoots beyond 115% of  $V_{REF}$ , the output voltage is brought down by the low-side MOSFET until the voltage on the FB pin goes below 0.4V. The fault latch is NOT set until the voltage on the SS pin reaches 1.2V. Once the fault latch is set, the converter shuts down.

Figure 22. Over-Voltage Protection

#### **Thermal Fault Protection**

The FAN5099 features thermal protection where the IC temperature is monitored. When the IC junction temperature exceeds +160°C, the controller shuts down and when the junction temperature gets down to +125°C, the converter restarts.

#### **LDO Section**

The LDO controller is designed to provide ultra low voltages, as low as 0.8V for GTL-type loads. The regulating loop employs a very fast response feedback loop and small capacitors can be used to keep track of the changing output voltage during transients. For stable operation, the minimum capacitance on the output needs to be  $100\mu F$  and the typical ESR needs to be around  $100m\Omega$ .

The maximum voltage at the gate drive for the MOSFET can reach close to 0.5V below the  $V_{CC}$  of the controller. For example, for a 1.2V output, the minimum enhancement voltage required with 4.75V on  $V_{CC}$  is 3.05V (4.75V-0.5V-1.2V = 3.05V). The dropout voltage for the LDO is dependent on the load current and the MOSFET chosen. It is recommended to use low enhancement voltage MOSFETs for the LDO. In an application where LDO is not needed, pull up the FBLDO pin (Pin 1) higher than 1V to disable the LDO.

The soft-start on the LDO output (ramp) is controlled by the capacitor on the SS pin to GND. The LDO output is enabled only when the voltage on the SS pin reaches 2.2V. Refer to Figure 9 for startup waveform.

## **Design Section**

#### **General Design Guidelines**

Establishing the input voltage range and the maximum current loading on the converter before choosing the switching frequency and the inductor ripple current is highly recommended. There are design tradeoffs choosing optimum switching frequency and ripple current.

The input voltage range should accommodate the worstcase input voltage with which the converter may ever operate. This voltage needs to account for the cable drop encountered from the source to the converter. Typically, the converter efficiency tends to be higher at lower input voltage conditions.

When selecting maximum loading conditions, consider the transient and steady-state (continuous) loading separately. The transient loading affects the selection of the inductor and the output capacitors. Steady-state loading affects the selection of MOSFETs, input capacitors, and other critical heat-generating components.

The selection of switching frequency is challenging. While higher switching frequency results in smaller components, it also results in lower efficiency. Ideal selection of switching frequency takes into account the maximum operating voltage. The MOSFET switching losses are directly proportional to  $f_{\text{SW}}$  and the square function of the input voltage.

When selecting the inductor, consider the minimum and maximum load conditions. Lower inductor values produce better transient response, but result in higher ripple and lower efficiency due to high RMS currents. Optimum minimum inductance value enables the converter to

operate at the boundary of continuous and discontinuous conduction modes.

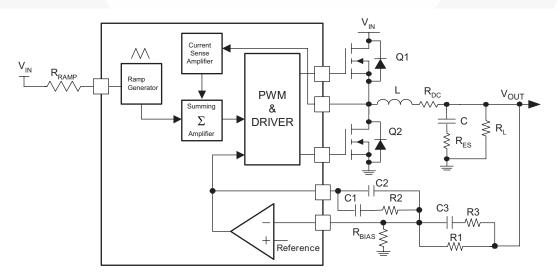

#### **Setting the Output Voltage (PWM)**

The internal reference for the PWM controller is at 0.8V. The output voltage of the PWM regulator can be set in the range of 0.8V to 90% of its power input by an external resistor divider. The output is divided down by an external voltage divider to the FB pin (for example, R1 and  $R_{BIAS}$  as in Figure 25). The output voltage is given by the following equation:

$$V_{OUT} = 0.8V \times \left(1 + \frac{R1}{R_{BIAS}}\right)$$

(EQ. 6)

To minimize noise pickup on this node, keep the resistor to GND (R\_{BIAS}) below 10K  $\!\Omega_{\!.}$

#### Inductor Selection (PWM)

When the ripple current, switching frequency of the converter, and the input-output voltages are established, select the inductor using the following equation:

$$L_{MIN} = \frac{\left(V_{OUT} - \frac{V_{OUT}^2}{V_{IN}}\right)}{I_{Ripple} \times f_{SW}}$$

(EQ. 7)

where I<sub>Ripple</sub> is the ripple current.

This number typically varies between 20% to 50% of the maximum steady-state load on the converter.

When selecting an inductor from the vendors, select the inductance value which is close to the value calculated at the rated current (including half the ripple current).

#### Input Capacitor Selection (PWM)

The input capacitors must have an adequate RMS current rating to withstand the temperature rise caused by the internal power dissipation. The combined RMS current rating for the input capacitor should be greater than the value calculated using the following equation:

$$I_{\text{INPUT}(\text{RMS})} = I_{\text{LOAD}(\text{MAX})} \times \left( \sqrt{\frac{V_{\text{OUT}}}{V_{\text{IN}}} - \left(\frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)^2} \right)_{\text{(EQ. 8)}}$$

Common capacitor types used for such application include aluminum, ceramic, POS CAP, and OSCON.

#### **Output Capacitor Selection (PWM)**

The output capacitors chosen must have low enough ESR to meet the output ripple and load transient requirements. The ESR of the output capacitor should be lower than both of the values calculated below to satisfy both the transient loading and steady-state ripple conditions as given by the following equation:

$$ESR \leq \frac{V_{STEP}}{\Delta I_{LOAD(MAX)}} \text{ and } ESR \leq \frac{V_{Ripple}}{I_{Ripple}}$$

(EQ. 9)

In the case of aluminum and polymer-based capacitors, the output capacitance is typically higher than normally required to meet these requirements. While selecting the ceramic capacitors for the output; although lower ESR can be achieved easily, higher capacitance values are required to meet the  $V_{\rm OUT(MIN)}$  restrictions during a load transient. From the stability point of view, the zero caused by the ESR of the output capacitor plays an important role in the stability of the converter.

#### **Output Capacitor Selection (LDO)**

For stable operation, the minimum capacitance of  $100\mu F$  with ESR around  $100m\Omega$  is recommended. For other values, contact the factory.

#### **Power MOSFET Selection (PWM)**

The FAN5099 is capable of driving N-Channel MOSFETs as circuit switch elements. For better performance, MOSFET selection should address these key parameters:

- The maximum Drain-to-Source Voltage (V<sub>DS</sub>) should be at least 25% higher than the worst-case input voltage.

- The MOSFETs should have low Q<sub>G</sub>, Q<sub>GD</sub>, and Q<sub>GS</sub>.

- The R<sub>DS ON</sub> of the MOSFETs should be as low as possible.

In typical applications for a buck converter, the duty cycles are lower than 20%. To optimize the selection of MOSFETs for both the high-side and low-side, follow different selection criteria. Select the high-side MOSFET to minimize the switching losses and the low-side MOSFET to minimize the conduction losses due to the channel and the body diode losses. Note that the gate drive losses also affect the temperature rise on the controller.

For loss calculation, refer to Fairchild's Application Note AN-6005 and the associated spreadsheet.

#### **High-Side Losses**

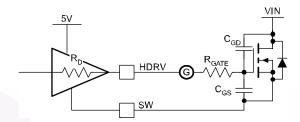

To understand losses in the MOSFET, follow the MOSFET switching interval shown in Figure 23. The MOSFET gate drive equivalent circuit is shown in Figure 24.

Figure 23. Switching Losses and Q<sub>q</sub>

Figure 24. Drive Equivalent Circuit

The upper graph in Figure 23 represents Drain-to-Source Voltage ( $V_{DS}$ ) and Drain Current ( $I_D$ ) waveforms. The lower graph details Gate-to-Source Voltage ( $V_{GS}$ ) versus time with a constant current charging the gate. The x-axis is representative of Gate Charge ( $Q_G$ ).  $C_{ISS} = C_{GD} + C_{GS}$  and controls t1, t2, and t4 timing.  $C_{GD}$  receives current from the gate driver during t3 (as VDS is falling). Obtain the gate charge ( $Q_G$ ) parameters shown on the lower graph from the MOSFET datasheets.

Assuming switching losses are about the same for both the rising edge and falling edge, Q1's switching losses occur during the shaded time when the MOSFET has voltage across it and current through it.

Losses are given by Equations 10-12:

$$P_{UPPER} = P_{SW} + P_{COND}$$

(EQ. 10)

$$P_{SW} = \left(\frac{V_{DS} \times I_{L}}{2} \times 2 \times t_{s}\right) f_{SW}$$

(EQ. 11)

$$P_{COND} = \left(\frac{V_{OUT}}{V_{IN}}\right) \times I_{OUT}^2 \times R_{DS(ON)}$$

(EQ. 12)

where  $P_{UPPER}$  is the upper MOSFET's total losses and  $P_{SW}$  and  $P_{COND}$  are the switching and conduction losses for a given MOSFET  $R_{DS(ON)}$  is at the maximum junction temperature  $(T_J)$  and  $t_S$  is the switching period (rise or fall time) and equals t2+t3, as shown in Figure 23.

The driver's impedance and  $C_{ISS}$  determine t2 while t3's period is controlled by the driver's impedance and  $Q_{GD}$ . Since most of  $t_S$  occurs when  $V_{GS} = V_{SP}$ , assume a constant current for the driver to simplify the calculation of  $t_S$  with the following equation:

$$t_{s} = \frac{Q_{G(SW)}}{I_{Driver}} \approx \frac{Q_{G(SW)}}{\left(\frac{V_{CC} - V_{SP}}{R_{Driver} + R_{Gate}}\right)}$$

(EQ. 13)

Most MOSFET vendors specify  $Q_{GD}$  and  $Q_{GS}$ .  $Q_{G(SW)}$  can be determined as:

$Q_{G(SW)} = Q_{GD} + Q_{GS} - Q_{TH}$  where  $Q_{TH}$  is the gate charge required to reach the MOSFET threshold (V<sub>TH</sub>).

Note that for the high-side MOSFET,  $V_{DS}$  equals  $V_{IN}$ , which can be as high as 20V in a typical portable application. Include the power delivered to the MOSFET's ( $P_{GATE}$ ) in calculating the power dissipation required for the FAN5099.

P<sub>GATE</sub> is determined by the following equation:

$$P_{Gate} = Q_G \times V_{CC} \times f_{SW}$$

(EQ. 14)

where Q<sub>G</sub> is the total gate charge to reach V<sub>CC</sub>.

#### **Low-Side Losses**

Q2 switches on or off with its parallel Schottky diode simultaneously conducting, so the  $V_{DS}\approx 0.5 V.$  Since  $P_{SW}$  is proportional to  $V_{DS},$  Q2's switching losses are negligible and Q2 is selected based on  $R_{DS(ON)}$  alone.

Conduction losses for Q2 are given by the equation:

$$P_{COND} = (1 - D) \times I_{OUT}^2 \times R_{DS(ON)}$$

(EQ. 15)

where  $R_{DS(ON)}$  is the  $R_{DS(ON)}$  of the MOSFET at the highest operating junction temperature and D=V<sub>OUT</sub>/V<sub>IN</sub> is the minimum duty cycle for the converter.

Since D<sub>MIN</sub> < 20% for portable computers, (1-D)  $\approx$  1 produces a conservative result, simplifying the calculation.

The maximum power dissipation ( $P_{D(MAX)}$ ) is a function of the maximum allowable die temperature of the low-side MOSFET, the  $\theta_{JA}$ , and the maximum allowable ambient temperature rise.  $P_{D(MAX)}$  is calculated using the following equation:

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_{A(MAX)}}{\theta_{JA}}$$

(EQ. 16)

$\theta_{\mbox{\scriptsize JA}}$  depends primarily on the amount of PCB area devoted to heat sinking.

#### **Selection of MOSFET Snubber Circuit**

The switch node (SW) ringing is caused by fast switching transitions due to energy stored in parasitic elements. This ringing on the SW node couples to other circuits around the converter if they are not handled properly. To dampen ringing, an R-C snubber is connected across the SW node and the source of the low-side MOSFET.

R-C components for the snubber are selected as follows:

- a) Measure the SW node ringing frequency (f<sub>ring</sub>) with a low capacitance scope probe.

- b) Connect a capacitor (C<sub>SNUB</sub>) from SW node to GND so that it reduces this ringing by half.

- c) Place a resistor (R<sub>SNUB</sub>) in series with this capacitor.

R<sub>SNUB</sub> is calculated using the following equation:

$$R_{SNUB} = \frac{2}{\pi \times F_{ring} \times C_{SNUB}}$$

(EQ. 17)

d) Calculate the power dissipated in the snubber resistoras shown in the following equation:

$$\begin{split} P_{R(SNUB)} &= C_{SNUB} \times V_{IN(MAX)}^2 \times f_{SW} & \text{(EQ. 18)} \\ \text{where, } V_{IN(MAX)} \text{ is the maximum input voltage and FSW} \\ \text{is the converter switching frequency.} \end{split}$$

The snubber resistor chosen should be de-rated to handle the worst-case power dissipation. **Do not use wire-wound resistors for R**<sub>SNUB</sub>.

#### **Loop Compensation**

Typically, the closed-loop crossover frequency ( $f_{cross}$ ), where the overall gain is unity, should be selected to achieve optimal transient and steady-state response to disturbances in line and load conditions. It is recommended to keep  $f_{cross}$  below one-fifth of the switching frequency of the converter. Higher phase margin tends to have a more stable system with more sluggish response to load transients. Optimum phase margin is about  $60^\circ$ , a good compromise between steady-state and transient responses. A typical design should address variations over a wide range of load conditions and over a large sample of devices.

Figure 25. Closed-Loop System with Type-3 Network

FAN5099 has a high gain error amplifier around which the loop is closed. Figure 25 shows a type-3 compensation network. For type-2 compensation, R3 and C3 are not used. Since the FAN5099 architecture employs summing current mode, type-2 compensation can be used for most applications. For for further information about type-2 compensation networks, refer to the following:

Venable, H. Dean, "The K factor: A new mathematical tool for stability analysis and synthesis," Proceedings of Powercon, March 1983. **Note**: For critical applications requiring wide loop bandwidth using very low ESR output capacitors, use type-3 compensation.

## **Type-3 Feedback Component Calculations**

Use these steps to calculate feedback components:

#### Notation:

C<sub>0</sub> = Net Output Filter Capacitance

$G_n(s)$  = Net Gain of Plant = control-to-output transfer function

L = Inductor Value

R<sub>DSON</sub> = On-State Drain-to Source Resistance of Low-side MOSFET

R<sub>es</sub> = Net ESR of the output filter capacitors

R<sub>I</sub> = Load Resistance

t<sub>s</sub> = Switching Period

V<sub>i</sub> = Input Voltage

f<sub>SW</sub> = Switching Frequency

## **Equations:**

Effective current sense resistance =

$$R_i = 7 \times R_{DSON}$$

(EQ. 19)

Current modulator DC gain =

$$M_i = \frac{R_L}{R_i}$$

(EQ. 20)

Effective ramp amplitude =

$$V_m = 3.33 \times 10^{10} \times \frac{(V_i - 1.8) \times T_s}{R_{ramp}}$$

Voltage modulator DC gain =  $M_V = \frac{V_i}{V_m}$  (EQ. 21)

Plant DC gain =

$$M_o = M_v \parallel M_i = \frac{M_v \times M_i}{M_v + M_i}$$

(EQ. 23)

Sampling gain natural frequency =

$$\omega_{\text{n}} = \frac{\pi}{T_{\text{s}}}$$

(EQ. 24)

Effective inductance =

$$L_e = \frac{M_O}{M_v} \times \left(L + \frac{M_v \times R_i}{\omega_n \times Q_v}\right)$$

(EQ. 25)

$$R_{p} = \frac{M_{v} \times R_{i} \times R_{L}}{M_{v} \times R_{i} + R_{L}} = (M_{v} \times R_{i}) \parallel R_{L}$$

(EQ. 26)

#### **Poles and Zeros of Plant Transfer Function:**

Plant zero frequency =

$$f_z = \frac{1}{2 \times \pi \times C_0 \times R_{es}}$$

(EQ. 27)

Plant 1<sup>st</sup> pole frequency =

$$f_{p1} = \frac{1}{2 \times \pi \times \left(C_o \times R_p + \frac{L_e}{R_1}\right)}$$

(EQ. 28)

Plant 2<sup>nd</sup> pole frequency =

$$f_{p2} = \frac{1}{2 \times \pi} \times \left( \frac{1}{C_o \times R_L} + \frac{R_p}{L_e} \right)$$

(EQ. 29)

Plant 3<sup>rd</sup> pole frequency =

$$f_{p3} = \frac{\omega_n^2 \times L_e}{2 \times \pi \times R_p}$$

(EQ. 30)

## Plant gain (magnitude) response:

$$\left|G_{p}\right|(f) = 20 \times log M_{0} + 10 \times log \left[\frac{1 + \left(\frac{f}{f_{p1}}\right)^{2}}{\left[1 + \left(\frac{f}{f_{p1}}\right)^{2}\right] \times \left[1 + \left(\frac{f}{f_{p2}}\right)^{2}\right] \times \left[1 + \left(\frac{f}{f_{p3}}\right)^{2}\right]}\right] \tag{EQ. 31}$$

#### Plant phase response:

$$\angle G_{P}(f) = tan^{-1} \left(\frac{f}{f_{Z}}\right) - tan^{-1} \left(\frac{f}{f_{D1}}\right) - tan^{-1} \left(\frac{f}{f_{D2}}\right) - -tan^{-1} \left(\frac{f}{f_{D3}}\right)$$

(EQ. 32)

Choose R1,  $R_{BIAS}$  to set the output voltage using Equation 5. Choose the zero crossover frequency  $f_{cross}$  of the overall loop. Typically  $F_{cross}$  should be less than 1/5th of  $f_{sw}$ . Choose the desired phase margin. Typically this number should be between 60° to 90°.

Calculate plant gain at  $f_{cross}$  using Equation 30 by substituting  $f_{cross}$  in place of f. The gain that the amplifier needs to provide to get the required crossover is given by:

$$G_{AMP} = \frac{1}{|G_p|(f_{cross})}$$

(EQ. 33)

The phase boost required is calculated as given in (EQ. 34).

Phase Boost =

$$M - \angle G_p(F_{cross}) - 90^{\circ}$$

(EQ. 34)

where M is the desired phase margin in degrees.

The feedback component values are now calculated as given in equations below:

$$K = \left\{ Tan \left[ \left( \frac{Boost}{4} \right) + 45 \right] \right\}^{2}$$

(EQ. 35)

$$C2 = \frac{1}{2 \times \pi \times f_{cross} \times G_{AMP} \times R1}$$

(EQ. 36)

$$C1 = C2 \times (K-1)$$

(EQ. 37)

$$C3 = \frac{1}{2 \times \pi \times f_{cross} \times \sqrt{K} \times R3}$$

(EQ. 38)

$$R2 = \frac{\sqrt{K}}{2 \times \pi \times f_{cross} \times C1}$$

(EQ. 39)

$$R3 = \frac{R1}{(K-1)} \tag{EQ. 40}$$

#### **Design Tools**

Fairchild application note **AN-6020** provides a PSPICE model and spreadsheet calculator for the PWM regulator, simplifying external component selections and verifying loop stability. The topics covered in the datasheet provide an understanding behind the calculations in the spreadsheet.

The spreadsheet calculator, which is part of AN-6020 can be used to calculate all external component values for designing around FAN5099. The spreadsheet provides optimized compensation components and generates a Bode plot to ensure loop stability.

Based on the input values entered, **AN-6020**'s PSPICE model can be used to simulate Bode plots (for loop stability) as well as transient analysis that help customize the design for a wide range of applications.

Use Fairchild application note **AN-6005** for prediction of the losses and die temperatures for the power semiconductors used in the circuit.

Both AN-6020 and AN-6005 can be downloaded from www.fairchildsemi.com/apnotes/.

#### **Layout Considerations**

The switching power converter layout needs careful attention and is critical to achieving low losses and clean and stable operation. Below are specific recommendations for a good board layout:

- Keep the high current traces and load connections as short as possible.

- Use thick copper boards whenever possible to achieve higher efficiency.

- Keep the loop area between the SW node, low-side MOSFET, inductor, and the output capacitor as small as possible.

- Route high dV/dt signals, such as SW node, away from the error amplifier input/output pins. Keep components connected to these pins close to the pins.

- Place ceramic de-coupling capacitors very close to V<sub>CC</sub> pin.

- All input signals are referenced with respect to AGND pin. Dedicate one layer of the PCB for a GND plane. Use at least four layers for the PCB.

- Minimize GND loops in the layout to avoid EMI-related issues.

- Use wide traces for the lower gate drive to keep the drive impedances low.

- Connect PGND directly to the lower MOSFET source pin.

- Use wide land areas with appropriate thermal vias to effectively remove heat from the MOSFETs.

- Use snubber circuits to minimize high-frequency ringing at the SW nodes.

- Place the output capacitor for the LDO close to the source of the LDO MOSFET.

# **Application Board Schematic**

$V_{IN}$  = 3 to 24V;  $V_{OUT}$  =1.5V at 20A;  $f_{OSC}$  = 300kHz.

Figure 26. Application Board Schematic

## **Bill of Materials**

| Part Description                                           | Quantity | Designator      | Vendor                  | Vendor Part<br>Number |

|------------------------------------------------------------|----------|-----------------|-------------------------|-----------------------|

| Capacitor, 1500pF, 10%, 50V, 0603, X7R                     | 1        | C1              | Panasonic               | ECJ1VB1H152K          |

| Capacitor, 220pF, 5%, 50V, 0603, NPO                       | 1        | C2              | Panasonic               | ECJ1VC1H221J          |

| Capacitor, 3300pF, 10%, 50V, 0603, X7R                     | 1        | C3              | Panasonic               | ECJ1VB1H332K          |

| Capacitor, 0.1µF, 10%, 25V, 0603, X7R                      | 4        | C4, C5, C6, C15 | Panasonic               | ECJ1VB1E104K          |

| Capacitor, 0.22µF, 20%, 25V, 0603, X7R                     | 2        | C7, C8          | TDK                     | C1608JB1E224K         |

| Capacitor, 0.01µF, 10%, 50V, 0603, X7R                     | 1        | C9              | Panasonic               | ECJ1VB1H103K          |