### Freescale Semiconductor Data Sheet: Technical Data

An Energy-Efficient Solution from Freescale

# MC9S08MM128 series

Covers: MC9S08MM128, and MC9S08MM64, MC9S08MM32, and MC9S08MM32A

#### 8-Bit HCS08 Central Processor Unit (CPU)

- Up to 48-MHz CPU above 2.4 V, 40 MHz CPU above 2.1 V, and 20 MHz CPU above 1.8 V across temperature of -40°C to 105°C

- HCS08 instruction set with added BGND instruction

- Support for up to 33 interrupt/reset sources

#### **On-Chip Memory**

- 128 K Dual Array Flash read/program/erase over full operating voltage and temperature

- 12 KB Random-access memory (RAM)

- Security circuitry to prevent unauthorized access to RAM and Flash

#### **Power-Saving Modes**

- Two ultra-low power stop modes. Peripheral clock enable register can disable clocks to unused modules to reduce currents

- Time of Day (TOD) Ultra-low power 1/4 sec counter with up to 64s timeout.

- Ultra-low power external oscillator that can be used in stop modes to provide accurate clock source to the TOD. 6 usec typical wake up time from stop3 mode

#### **Clock Source Options**

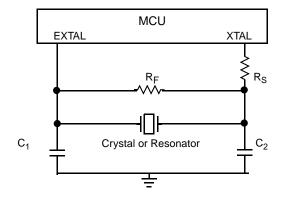

- Oscillator (XOSC1) Loop-control Pierce oscillator; 32.768 kHz crystal or ceramic resonator dedicated for TOD operation.

- Oscillator (XOSC2) for high frequency crystal input for MCG reference to be used for system clock and USB operations.

- Multipurpose Clock Generator (MCG) PLL and FLL; precision trimming of internal reference allows 0.2% resolution and 2% deviation over temperature and voltage; supports CPU frequencies from 4 kHz to 48 MHz.

#### System Protection

- Watchdog computer operating properly (COP) reset Watchdog computer operating properly (COP) reset with option to run from dedicated 1-kHz internal clock source or bus clock

- Low-voltage detection with reset or interrupt; selectable trip points; separate low-voltage warning with optional interrupt; selectable trip points

- Illegal opcode and illegal address detection with reset

- Flash block protection for each array to prevent accidental write/erasure

- Hardware CRC to support fast cyclic redundancy checks

#### **Development Support**

- Single-wire background debug interface

- Real-time debug with 6 hardware breakpoints (4 PC, 1 address and 1 data) Breakpoint capability to allow single breakpoint setting during in-circuit debugging

- On-chip in-circuit emulator (ICE) debug module containing 3 comparators and 9 trigger modes

#### Peripherals

- CMT— Carrier Modulator timer for remote control communications. Carrier generator, modulator and driver for dedicated infrared out. Can be used as an output compare timer.

- IIC— Up to 100 kbps with maximum bus loading; Multi-master operation; Programmable slave address; Interrupt driven

Document Number: MC9S08MM128

Rev. 3, 10/2010

byte-by-byte data transfer; supports broadcast mode and 11-bit addressing

- PRACMP Analog comparator with selectable interrupt; compare option to programmable internal reference voltage; operation in stop3

- SCI Two serial communications interfaces with optional 13-bit break; option to connect Rx input to PRACMP output on SCI1 and SCI2; High current drive on Tx on SCI1 and SCI2; wake-up from stop3 on Rx edge

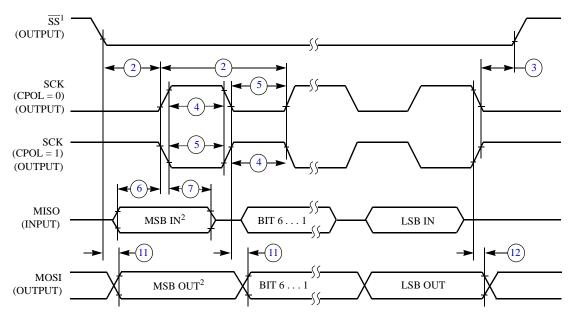

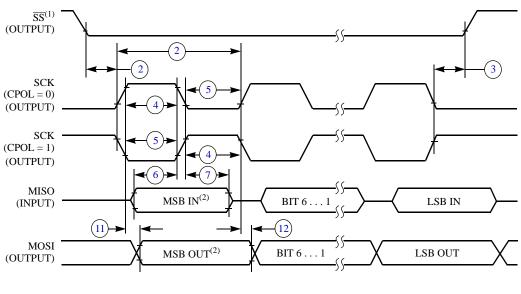

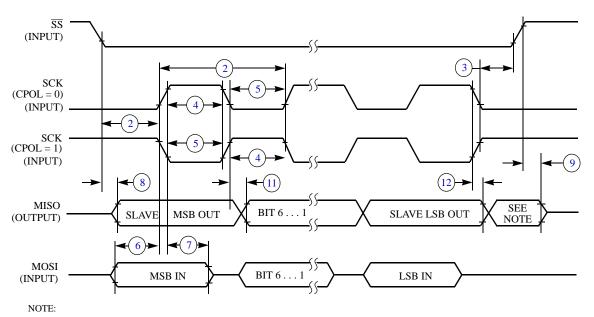

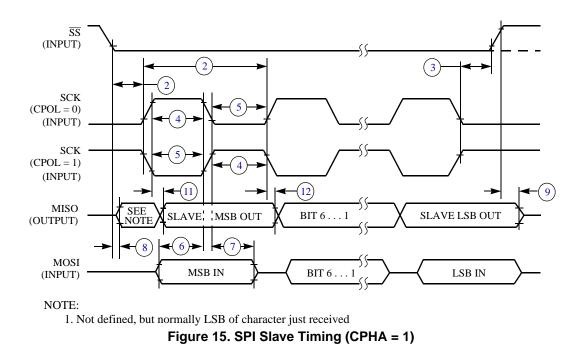

- SPI1— Serial peripheral interface (SPI) with 64-bit FIFO buffer; 16-bit or 8-bit data transfers; full-duplex or single-wire bidirectional; double-buffered transmit and receive; master or slave mode; MSB-first or LSB-first shifting

- SPI2— Serial peripheral interface with full-duplex or single-wire bidirectional; Double-buffered transmit and receive; Master or Slave mode; MSB-first or LSB-first shifting

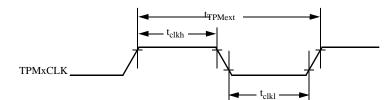

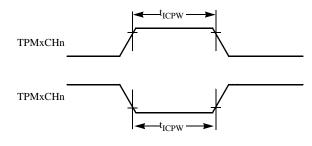

- TPM Two 4-channel Timer/PWM Module; Selectable input capture, output compare, or buffered edge- or center-aligned PWM on each channel; external clock input/pulse accumulator

- USB Supports USB in full-speed device configuration. On-chip transceiver and 3.3V regulator help save system cost, fully compliant with USB Specification 2.0. Allows control, bulk, interrupt and isochronous transfers. Not available on MC9S08MM32A devices.

- ADC16 16-bit Successive approximation ADC with up to 4 dedicated differential channels and 8 single-ended channels; range compare function; 1.7 mV/°C temperature sensor; internal bandgap reference channel; operation in stop3; fully functional from 3.6V to 1.8V, Configurable hardware trigger for 8 Channel select and result registers

- PDB Programmable delay block with 16-bit counter and modulus and prescale to set reference clock to bus divided by 1 to bus divided by 2048; 8 trigger outputs for ADC16 module provides periodic coordination of ADC sampling sequence with sequence completion interrupt; Back-to-Back mode and Timed mode

- DAC 12-bit resolution; 16-word data buffers with configurable watermark.

- OPAMP Two flexible operational amplifiers configurable for general operations; Low offset and temperature drift.

- TRIAMP Two trans-impedance amplifiers dedicated for converting current inputs into voltages.

#### Input/Output

- Up to 47 GPIOs and 2 output-only pin and 1 input-only pin.

- Voltage Reference output (VREFO).

- Dedicated infrared output pin (IRO) with high current sink capability.

- Up to 16 KBI pins with selectable polarity.

#### Package Options

- 81-MBGA 10x10 mm

- 80-LQFP 12x12 mm

- 64-LQFP 10x10 mm

© Freescale Semiconductor, Inc., 2009-2010. All rights reserved.

# Contents

| 1 Devices  | s in the MC9S08MM128 series    |

|------------|--------------------------------|

| 1.1        | Pin Assignments6               |

|            | 1.1.1 64-Pin LQFP              |

|            | 1.1.2 80-Pin LQFP              |

|            | 1.1.3 81-Pin MAPBGA            |

| 1.2        | Pin Assignments by Packages10  |

| 2 Electric | al Characteristics             |

| 2.1        | Parameter Classification       |

| 2.2        | Absolute Maximum Ratings14     |

| 2.3        | Thermal Characteristics15      |

| 2.4        | ESD Protection Characteristics |

| 2.5        | DC Characteristics             |

| 2.6        | Supply Current Characteristics |

| 2.7        | PRACMP Electricals             |

| 2.8        | 12-Bit DAC Electricals         |

| 2.9        | ADC Characteristics            |

|            |                                |

| 2.10<br>2.11 | MCG and External Oscillator (XOSC) Characteristics .33<br>AC Characteristics |

|--------------|------------------------------------------------------------------------------|

| 2.12         | SPI Characteristics                                                          |

| 2.13         | Flash Specifications                                                         |

| 2.14         | USB Electricals                                                              |

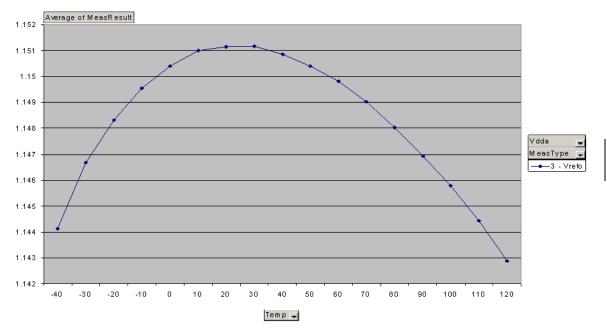

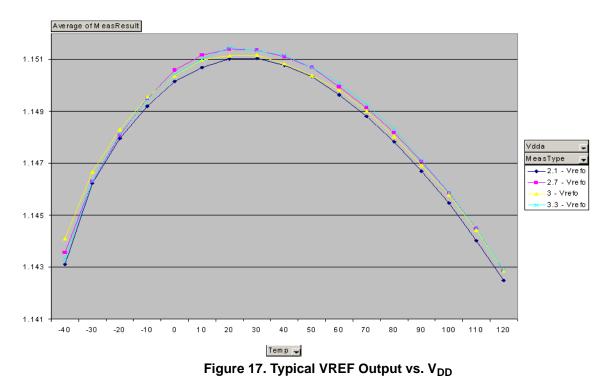

| 2.15         | VREF Electrical Specifications                                               |

| 2.16         | TRIAMP Electrical Parameters                                                 |

| 2.17         | OPAMP Electrical Parameters                                                  |

| 3 Orderin    | g Information                                                                |

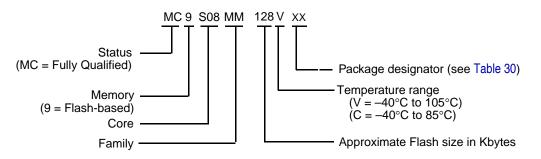

| 3.1          | Device Numbering System                                                      |

| 3.2          | Package Information                                                          |

| 3.3          | Mechanical Drawings                                                          |

| 4 Revisio    | n History                                                                    |

# **Related Documentation**

Find the most current versions of all documents at: http://www.freescale.com.

#### Reference Manual —MC9S08MM128RM

Contains extensive product information including modes of operation, memory, resets and interrupts, register definition, port pins, CPU, and all module information.

The following table summarizes the feature set available in the MC9S08MM128 series of MCUs.

| Feature                                     | МС    | 9S08MN | 1128 | MC9S08MM64 | MC9S08MM32 | MC9S08MM32A |

|---------------------------------------------|-------|--------|------|------------|------------|-------------|

| Pin quantity                                | 81    | 80     | 64   | 64         | 64         | 64          |

| FLASH size (bytes)                          |       | 131072 |      | 65535      | 32768      | 32768       |

| RAM size (bytes)                            |       | 12K    |      | 12K        | 4K         | 2K          |

| Programmable Analog Comparator (PRACMP)     |       | yes    |      | yes        | yes        | yes         |

| Debug Module (DBG)                          |       | yes    |      | yes        | yes        | yes         |

| Multipurpose Clock Generator (MCG)          |       | yes    |      | yes        | yes        | yes         |

| Inter-Integrated Communication (IIC)        |       | yes    |      | yes        | yes        | yes         |

| Interrupt Request Pin (IRQ)                 |       | yes    |      | yes        | yes        | yes         |

| Keyboard Interrupt (KBI)                    | 16    | 16     | 6    | 6          | 6          | 6           |

| Port I/O <sup>1</sup>                       | 47    | 46     | 33   | 33         | 33         | 33          |

| Dedicated Analog Input Pins                 |       | 12     |      | 12         | 12         | 12          |

| Power and Ground Pins                       |       | 8      |      | 8          | 8          | 8           |

| Time Of Day (TOD)                           |       | yes    |      | yes        | yes        | yes         |

| Serial Communications (SCI1)                |       | yes    |      | yes        | yes        | yes         |

| Serial Communications (SCI2)                |       | yes    |      | yes        | yes        | yes         |

| Serial Peripheral Interface 1 (SPI1 (FIFO)) |       | yes    |      | yes        | yes        | yes         |

| Serial Peripheral Interface 2 (SPI2)        |       | yes    |      | yes        | yes        | yes         |

| Carrier Modulator Timer pin (IRO)           |       | yes    |      | yes        | yes        | yes         |

| TPM input clock pin (TPMCLK)                |       | yes    |      | yes        | yes        | yes         |

| TPM1 channels                               |       | 4      |      | 4          | 4          | 4           |

| TPM2 channels                               | 4     | 4      | 2    | 2          | 2          | 2           |

| XOSC1                                       |       | yes    |      | yes        | yes        | yes         |

| XOSC2                                       |       | yes    |      | yes        | yes        | yes         |

| USB                                         |       | yes    |      | yes        | yes        | no          |

| Programmable Delay Block (PDB)              |       | yes    |      | yes        | yes        | yes         |

| SAR ADC differential channels <sup>2</sup>  | 4     | 4 4 3  |      | 3          | 3          | 3           |

| SAR ADC single-ended channels               | 8 8 6 |        | 6    | 6          | 6          |             |

| DAC ouput pin (DACO)                        | yes   |        |      | yes        | yes        | yes         |

| Voltage reference output pin (VREFO)        |       | yes    |      | yes        | yes        | yes         |

| General Purpose OPAMP (OPAMP)               |       | yes    |      | yes        | yes        | yes         |

| Trans-Impedance Amplifier (TRIAMP)          |       | yes    |      | yes        | yes        | yes         |

<sup>1</sup> Port I/O count does not include two (2) output-only and one (1) input-only pins.

<sup>2</sup> Each differential channel is comprised of 2 pin inputs.

A complete description of the modules included on each device is provided in the following table.

| Module                                         | Version |

|------------------------------------------------|---------|

| Analog-to-Digital Converter (ADC16)            | 1       |

| General Purpose Operational Amplifier (OPAMP)  | 1       |

| Trans-Impedance Operational Amplifier (TRIAMP) | 1       |

| Digital to Analog Converter (DAC)              | 1       |

| Programmable Delay Block                       | 1       |

| Inter-Integrated Circuit (IIC)                 | 3       |

| Central Processing Unit (CPU)                  | 5       |

| On-Chip In-Circuit Debug/Emulator (DBG)        | 3       |

| Multi-Purpose Clock Generator (MCG)            | 3       |

| Low Power Oscillator (XOSCVLP)                 | 1       |

| Carrier Modulator Timer (CMT)                  | 1       |

| Programable Analog Comparator (PRACMP)         | 1       |

| Serial Communications Interface (SCI)          | 4       |

| Serial Peripheral Interface (SPI)              | 5       |

| Time of Day (TOD)                              | 1       |

| Universal Serial Bus (USB) <sup>1</sup>        | 1       |

| Timer Pulse-Width Modulator (TPM)              | 3       |

| System Integration Module (SIM)                | 1       |

| Cyclic Redundancy Check (CRC)                  | 3       |

| Keyboard Interrupt (KBI)                       | 2       |

| Voltage Reference (VREF)                       | 1       |

| Voltage Regulator (VREG)                       | 1       |

| Interrupt Request (IRQ)                        | 3       |

| Flash Wrapper                                  | 1       |

| GPIO                                           | 2       |

| Port Control                                   | 1       |

| Table 2. Versions | of | <b>On-Chip</b> | Modules |

|-------------------|----|----------------|---------|

|-------------------|----|----------------|---------|

<sup>1</sup> USB Module not available on MC9S08MM32A devices.

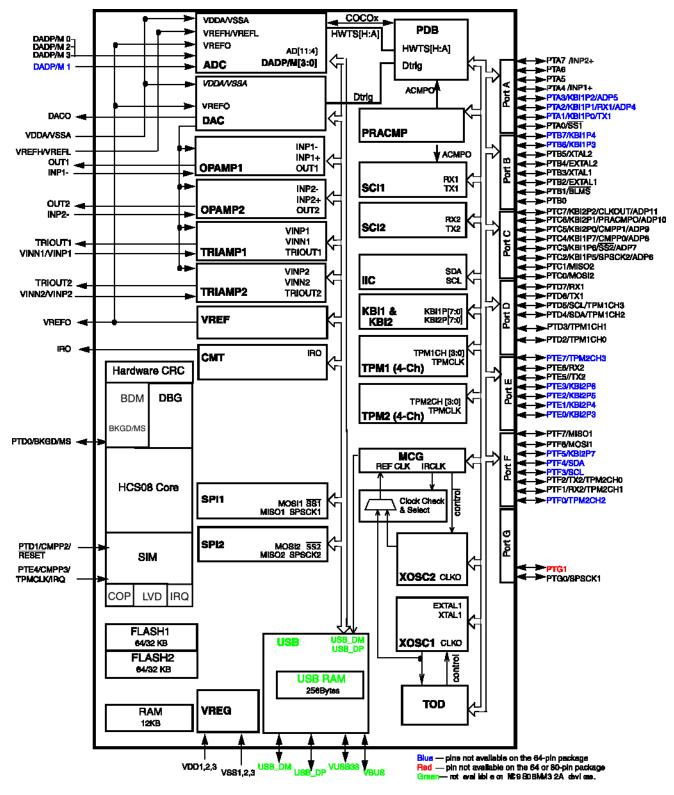

The block diagram in Figure 1 shows the structure of the MC9S08MM128 series MCU.

Figure 1. MC9S08MM128 series Block Diagram

### 1.1 Pin Assignments

This section shows the pin assignments for the MC9S08MM128 series devices.

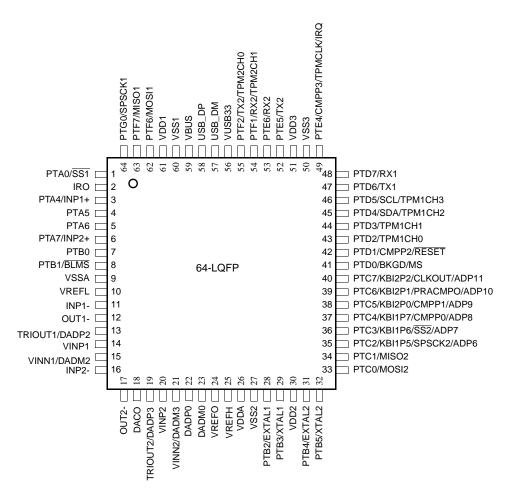

### 1.1.1 64-Pin LQFP

The following two figures show the 64-pin LQFP pinout configuration. The first illustrates the pinout configuration for MC9S08MM128, MC9S08MM64, and MC9S08MM32 devices.

#### Figure 2. 64-Pin LQFP for MC9S08MM128, MC9S08MM64, and MC9S08MM32 devices

For MC9S08MM32A devices, pins 56, 57, 58, and 59 are no connects (NC) as illustrated in the following figure.

Figure 3. 64-Pin LQFP for MC9S08MM32A devices

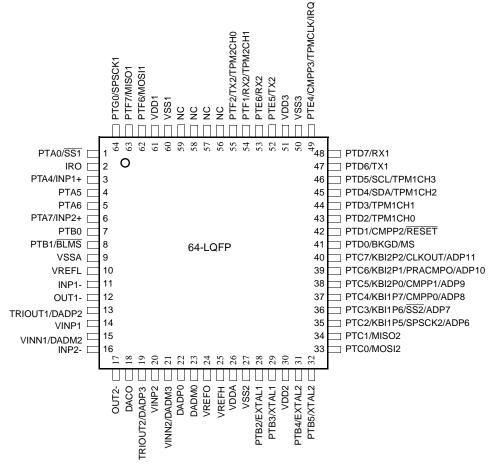

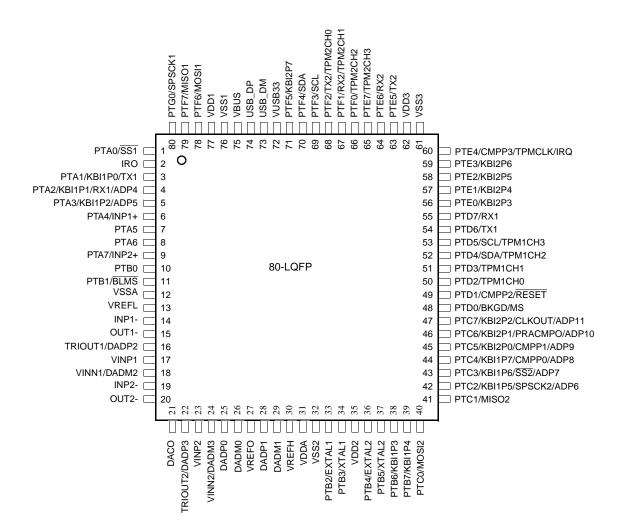

### 1.1.2 80-Pin LQFP

The following figure shows the 80-pin LQFP pinout configuration.

Figure 4. 80-Pin LQFP

### 1.1.3 81-Pin MAPBGA

The following figure shows the 81-pin MAPBGA pinout configuration.

|   | 1     | 2       | 3       | 4      | 5     | 6      | 7    | 8    | 9    |

|---|-------|---------|---------|--------|-------|--------|------|------|------|

| A | IRO   | PTG0    | PTF6    | USB_DP | VBUS  | VUSB33 | PTF4 | PTF3 | PTE4 |

| В | PTF7  | PTA0    | PTG1    | USB_DM | PTF5  | PTE7   | PTF1 | PTF0 | PTE3 |

| С | PTA4  | PTA5    | PTA6    | PTA1   | PTF2  | PTE6   | PTE5 | PTE2 | PTE1 |

| D | INP1- | PTA7    | PTB0    | PTB1   | PTA2  | PTA3   | PTD5 | PTD7 | PTE0 |

| Е | OUT1  | VINN1   | OUT2    | VDD2   | VDD3  | VDD1   | PTD2 | PTD3 | PTD6 |

| F | VINP1 | TRIOUT1 | INP2-   | VSS2   | VSS3  | VSS1   | PTB7 | PTC7 | PTD4 |

| G | DADP0 | DACO    | TRIOUT2 | VINN2  | VREFO | PTB6   | PTC0 | PTC1 | PTC2 |

| н | DADM0 | DADM1   | DADP1   | VINP2  | PTC3  | PTC4   | PTD0 | PTC5 | PTC6 |

| J | VSSA  | VREFL   | VREFH   | VDDA   | PTB2  | PTB3   | PTD1 | PTB4 | PTB5 |

Figure 5. 81-Pin MAPBGA

# 1.2 Pin Assignments by Packages

| Pa        | ackag   | ige     |                     |         |      |      |                      |

|-----------|---------|---------|---------------------|---------|------|------|----------------------|

| 81 MAPBGA | 80 LQFP | 64 LQFP | Default<br>Function | ALT1    | ALT2 | ALT3 | Composite Pin Name   |

| B2        | 1       | 1       | PTA0                | SS1     | —    | —    | PTA0/SS1             |

| A1        | 2       | 2       | IRO                 |         |      |      | IRO                  |

| C4        | 3       | _       | PTA1                | KBI1P0  | TX1  |      | PTA1/KBI1P0/TX1      |

| D5        | 4       | _       | PTA2                | KBI1P1  | RX1  | ADP4 | PTA2/KBI1P1/RX1/ADP4 |

| D6        | 5       | _       | PTA3                | KBI1P2  | ADP5 | —    | PTA3/KBI1P2/ADP5     |

| C1        | 6       | 3       | PTA4                | INP1+   | _    | —    | PTA4/INP1+           |

| C2        | 7       | 4       | PTA5                | _       | _    |      | PTA5                 |

| C3        | 8       | 5       | PTA6                | _       | —    | —    | PTA6                 |

| D2        | 9       | 6       | PTA7                | INP2+   | —    | —    | PTA7/INP2+           |

| D3        | 10      | 7       | PTB0                | _       | —    | —    | PTB0                 |

| D4        | 11      | 8       | PTB1                | BLMS    | —    | —    | PTB1/BLMS            |

| J1        | 12      | 9       | VSSA                | _       | —    | —    | VSSA                 |

| J2        | 13      | 10      | VREFL               | _       | _    |      | VREFL                |

| D1        | 14      | 11      | INP1-               | _       | —    | —    | INP1-                |

| E1        | 15      | 12      | OUT1                | _       | _    |      | OUT1                 |

| F2        | 16      | 13      | DADP2               | TRIOUT1 | _    | _    | DADP2/TRIOUT1        |

| F1        | 17      | 14      | VINP1               | _       | —    | —    | VINP1                |

| E2        | 18      | 15      | DADM2               | VINN1   | _    |      | DADM2/VINN1          |

| F3        | 19      | 16      | INP2-               | _       | —    | —    | INP2-                |

| E3        | 20      | 17      | OUT2                | _       | _    |      | OUT2                 |

| G2        | 21      | 18      | DACO                | _       | _    |      | DACO                 |

| G3        | 22      | 19      | DADP3               | TRIOUT2 | —    | —    | DADP3/TRIOUT2        |

| H4        | 23      | 20      | VINP2               | _       | _    |      | VINP2                |

| G4        | 24      | 21      | DADM3               | VINN2   | _    |      | DADM3/VINN2          |

| G1        | 25      | 22      | DADP0               | —       | —    | —    | DADP0                |

| H1        | 26      | 23      | DADM0               |         |      | —    | DADM0                |

| G5        | 27      | 24      | VREFO               | —       |      | —    | VREFO                |

| H3        | 28      | _       | DADP1               |         | —    | —    | DADP1                |

| H2        | 29      | _       | DADM1               | _       | —    | —    | DADM1                |

Table 3. Package Pin Assignments

| Pa        | ackag   | e       |                     |         |         |       |                           |

|-----------|---------|---------|---------------------|---------|---------|-------|---------------------------|

| 81 MAPBGA | 80 LQFP | 64 LQFP | Default<br>Function | ALT1    | ALT2    | ALT3  | Composite Pin Name        |

| J3        | 30      | 25      | VREFH               | _       | —       | _     | VREFH                     |

| J4        | 31      | 26      | VDDA                | —       | —       | _     | VDDA                      |

| F4        | 32      | 27      | VSS2                |         | —       |       | VSS2                      |

| J5        | 33      | 28      | PTB2                | EXTAL1  | —       |       | PTB2/EXTAL1               |

| J6        | 34      | 29      | PTB3                | XTAL1   | —       | —     | PTB3/XTAL1                |

| E4        | 35      | 30      | VDD2                | —       | —       | —     | VDD2                      |

| J8        | 36      | 31      | PTB4                | EXTAL2  | —       |       | PTB4/EXTAL2               |

| J9        | 37      | 32      | PTB5                | XTAL2   | —       | —     | PTB5/XTAL2                |

| G6        | 38      | _       | PTB6                | KBI1P3  | —       | —     | PTB6/KBI1P3               |

| F7        | 39      | _       | PTB7                | KBI1P4  | —       | —     | PTB7/KBI1P4               |

| G7        | 40      | 33      | PTC0                | MOSI2   | —       | _     | PTC0/MOSI2                |

| G8        | 41      | 34      | PTC1                | MISO2   | —       | _     | PTC1/MISO2                |

| G9        | 42      | 35      | PTC2                | KBI1P5  | SPSCK2  | ADP6  | PTC2/KBI1P5/SPSCK2/ADP6   |

| H5        | 43      | 36      | PTC3                | KBI1P6  | SS2     | ADP7  | PTC3/KBI1P6/SS2/ADP7      |

| H6        | 44      | 37      | PTC4                | KBI1P7  | CMPP0   | ADP8  | PTC4/KBI1P7/CMPP0/ADP8    |

| H8        | 45      | 38      | PTC5                | KBI2P0  | CMPP1   | ADP9  | PTC5/KBI2P0/CMPP1/ADP9    |

| H9        | 46      | 39      | PTC6                | KBI2P1  | PRACMPO | ADP10 | PTC6/KBI2P1/PRACMPO/ADP10 |

| F8        | 47      | 40      | PTC7                | KBI2P2  | CLKOUT  | ADP11 | PTC7/KBI2P2/CLKOUT/ADP11  |

| H7        | 48      | 41      | PTD0                | BKGD    | MS      |       | PTD0/BKGD/MS              |

| J7        | 49      | 42      | PTD1                | CMPP2   | RESET   | —     | PTD1/CMPP2/RESET          |

| E7        | 50      | 43      | PTD2                | TPM1CH0 | —       | —     | PTD2TPM1CH0               |

| E8        | 51      | 44      | PTD3                | TPM1CH1 | —       | _     | PTD3/TPM1CH1              |

| F9        | 52      | 45      | PTD4                | SDA     | TPM1CH2 | _     | PTD4/SDA/TPM1CH2          |

| D7        | 53      | 46      | PTD5                | SCL     | TPM1CH3 |       | PTD5/SCL/TPM1CH3          |

| E9        | 54      | 47      | PTD6                | TX1     | —       | _     | PTD6/TX1                  |

| D8        | 55      | 48      | PTD7                | RX1     | —       | —     | PTD7/RX1                  |

| D9        | 56      | _       | PTE0                | KBI2P3  | —       |       | PTE0/KBI2P3               |

| C9        | 57      | —       | PTE1                | KBI2P4  | -       | —     | PTE1/KBI2P4               |

| C8        | 58      | —       | PTE2                | KBI2P5  | —       | _     | PTE2/KBI2P5               |

| B9        | 59      | _       | PTE3                | KBI2P6  | —       |       | PTE3/KBI2P6               |

| A9        | 60      | 49      | PTE4                | CMPP3   | TPMCLK  | IRQ   | PTE4/CMPP3/TPMCLK/IRQ     |

| Table 3. Package Pin Assignments | (Continued) |

|----------------------------------|-------------|

|----------------------------------|-------------|

| Pa        | ackag   | е       |                     |         |         |      |                    |

|-----------|---------|---------|---------------------|---------|---------|------|--------------------|

| 81 MAPBGA | 80 LQFP | 64 LQFP | Default<br>Function | ALT1    | ALT2    | ALT3 | Composite Pin Name |

| F5        | 61      | 50      | VSS3                | —       | —       | —    | VSS3               |

| E5        | 62      | 51      | VDD3                | —       | —       | —    | VDD3               |

| C7        | 63      | 52      | PTE5                | TX2     | —       |      | PTE5/TX2           |

| C6        | 64      | 53      | PTE6                | RX2     | —       |      | PTE6/RX2           |

| B6        | 65      |         | PTE7                | TPM2CH3 | —       |      | PTE7/TPM2CH3       |

| B8        | 66      | _       | PTF0                | TPM2CH2 | —       | —    | PTF0/TPM2CH2       |

| B7        | 67      | 54      | PTF1                | RX2     | TPM2CH1 | —    | PTF1/RX2/TPM2CH1   |

| C5        | 68      | 55      | PTF2                | TX2     | TPM2CH0 | —    | PTF2/TX2/TPM2CH0   |

| A8        | 69      | —       | PTF3                | SCL     | —       | —    | PTF3/SCL           |

| A7        | 70      | _       | PTF4                | SDA     | —       |      | PTF4/SDA           |

| B5        | 71      | —       | PTF5                | KBI2P7  | —       |      | PTF5/KBI2P7        |

| A6        | 72      | 56      | VUSB33 <sup>1</sup> | _       | —       |      | VUSB33             |

| B4        | 73      | 57      | USB_DM <sup>2</sup> | —       | —       |      | USB_DM             |

| A4        | 74      | 58      | USB_DP <sup>3</sup> | —       | —       | —    | USB_DP             |

| A5        | 75      | 59      | VBUS <sup>4</sup>   | _       | —       | —    | VBUS               |

| F6        | 76      | 60      | VSS1                | —       | _       | —    | VSS1               |

| E6        | 77      | 61      | VDD1                | _       | —       |      | VDD1               |

| A3        | 78      | 62      | PTF6                | MOSI1   |         | _    | PTF6/MOSI1         |

| B1        | 79      | 63      | PTF7                | MISO1   |         | _    | PTF7/MISO1         |

| A2        | 80      | 64      | PTG0                | SPSCK1  | —       | —    | PTG0/SPSCK1        |

| B3        | —       | —       | PTG1                | _       | —       | _    | PTG1               |

Table 3. Package Pin Assignments (Continued)

<sup>1</sup> NC on MC9S08MM32A devices.

<sup>2</sup> NC on MC9S08MM32A devices.

<sup>3</sup> NC on MC9S08MM32A devices.

<sup>4</sup> NC on MC9S08MM32A devices.

This section contains electrical specification tables and reference timing diagrams for the MC9S08MM128/64/32/32A microcontroller, including detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications.

The electrical specifications are preliminary and are from previous designs or design simulations. These specifications may not be fully tested or guaranteed at this early stage of the product life cycle. These specifications will, however, be met for production silicon. Finalized specifications will be published after complete characterization and device qualifications have been completed.

#### NOTE

The parameters specified in this data sheet supersede any values found in the module specifications.

### 2.1 Parameter Classification

The electrical parameters shown in this supplement are guaranteed by various methods. To give the customer a better understanding, the following classification is used and the parameters are tagged accordingly in the tables where appropriate:

#### **Table 4. Parameter Classifications**

| Р | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| с | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| т | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

#### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

### 2.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in the following table may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section.

| # | Rating                                                                                          | Symbol           | Value                         | Unit |

|---|-------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| 1 | Supply voltage                                                                                  | V <sub>DD</sub>  | -0.3 to +3.8                  | V    |

| 2 | Maximum current into V <sub>DD</sub>                                                            | I <sub>DD</sub>  | 120                           | mA   |

| 3 | Digital input voltage                                                                           | V <sub>In</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| 4 | Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | ۱ <sub>D</sub>   | ± 25                          | mA   |

| 5 | Storage temperature range                                                                       | T <sub>stg</sub> | -55 to 150                    | °C   |

| Table 5. | Absolute | Maximum | Ratings |

|----------|----------|---------|---------|

|----------|----------|---------|---------|

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

$^2\,$  All functional non-supply pins are internally clamped to  $V_{SS}$  and  $V_{DD}.$

<sup>3</sup> Power supply must maintain regulation within operating V<sub>DD</sub> range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{In} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low (which would reduce overall power consumption).

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ).

## 2.3 Thermal Characteristics

This section provides information about operating temperature range, power dissipation, and package thermal resistance. Power dissipation on I/O pins is usually small compared to the power dissipation in on-chip logic and it is user-determined rather than being controlled by the MCU design. In order to take  $P_{I/O}$  into account in power calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  will be very small.

| # | Symbol            |                                    | Rating                                     | Value      | Unit |

|---|-------------------|------------------------------------|--------------------------------------------|------------|------|

| 1 | T <sub>A</sub>    | Operating temperature              | e range (packaged):                        |            | °C   |

|   |                   |                                    | MC9S08MM128                                | -40 to 105 | 1    |

|   |                   |                                    | MC9S08MM64                                 | -40 to 105 | 1    |

|   |                   |                                    | MC9S08MM32                                 | -40 to 105 | 1    |

|   |                   |                                    | MC9S08MM32A                                | -40 to 105 | 1    |

| 2 | T <sub>JMAX</sub> | Maximum junction temperature       |                                            | 135        | °C   |

| 3 | $\theta_{JA}$     | Thermal resistance <sup>1,2</sup>  | <sup>,3,4</sup> Single-layer board — 1s    |            | °C/W |

|   |                   |                                    | 81-pin MBGA                                | 77         | 1    |

|   |                   |                                    | 80-pin LQFP                                | 55         | 1    |

|   |                   |                                    | 64-pin LQFP                                | 68         | 1    |

| 4 | $\theta_{JA}$     | Thermal resistance <sup>1, 2</sup> | <sup>2, 3, 4</sup> Four-layer board — 2s2p |            | °C/W |

|   |                   |                                    | 81-pin MBGA                                | 47         | 1    |

|   |                   |                                    | 80-pin LQFP                                | 40         | 1    |

|   |                   |                                    | 64-pin LQFP                                | 49         | 1    |

| $\mathcal{O}$ |    | 22     | DD      | 2          |

|---------------|----|--------|---------|------------|

| Table         | 6. | Therma | I Chara | cteristics |

<sup>1</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- <sup>2</sup> Junction to Ambient Natural Convection

- <sup>3</sup> 1s Single layer board, one signal layer

- <sup>4</sup> 2s2p Four layer board, 2 signal and 2 power layers

The average chip-junction temperature  $(T_I)$  in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \times \theta_{JA})$$

Eqn. 1

where:

$T_A$  = Ambient temperature, °C

$\theta_{IA}$  = Package thermal resistance, junction-to-ambient, °C/W

$P_D = P_{int} + P_{I/O}$

$P_{int} = I_{DD} \times V_{DD}$ , Watts — chip internal power

$P_{I/O}$  = Power dissipation on input and output pins — user determined

Freescale Semiconductor

For most applications,  $P_{I/O} \ll P_{int}$  and can be neglected. An approximate relationship between  $P_D$  and  $T_J$  (if  $P_{I/O}$  is neglected) is:

$$P_{D} = K \div (T_{J} + 273^{\circ}C)$$

Eqn. 2

Solving Equation 1 and Equation 2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2$$

Eqn. 3

where K is a constant pertaining to the particular part. K can be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving Equation 1 and Equation 2 iteratively for any value of  $T_A$ .

### 2.4 ESD Protection Characteristics

Although damage from static discharge is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with CDF-AEC-Q00 Stress Test Qualification for Automotive Grade Integrated Circuits. (http://www.aecouncil.com/) This device was qualified to AEC-Q100 Rev E.

A device is considered to have failed if, after exposure to ESD pulses, the device no longer meets the device specification requirements. Complete dc parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Model      | Description                 | Symbol           | Value | Unit |

|------------|-----------------------------|------------------|-------|------|

| Human Body | Series Resistance           | R1               | 1500  | Ω    |

|            | Storage Capacitance         | С                | 100   | pF   |

|            | Number of Pulse per pin     | —                | 3     | _    |

| Machine    | Series Resistance           | es Resistance R1 |       | Ω    |

|            | Storage Capacitance         | С                | 200   | pF   |

|            | Number of Pulse per pin     | —                | 3     | _    |

| Latch-up   | Minimum input voltage limit | —                | -2.5  | V    |

|            | Maximum input voltage limit | —                | 7.5   | V    |

Table 7. ESD and Latch-up Test Conditions

| # | Rating                                     | Symbol           | Min   | Max | Unit | С |

|---|--------------------------------------------|------------------|-------|-----|------|---|

| 1 | Human Body Model (HBM)                     | V <sub>HBM</sub> | ±2000 |     | V    | Т |

| 2 | Machine Model (MM)                         | V <sub>MM</sub>  | ±200  |     | V    | Т |

| 3 | Charge Device Model (CDM)                  | V <sub>CDM</sub> | ±500  |     | V    | Т |

| 4 | Latch-up Current at T <sub>A</sub> = 125°C | I <sub>LAT</sub> | ±100  |     | mA   | Т |

# 2.5 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

| Num | Symbol           | Characteristic         |                                            | Condition                                                                                                | Min                    | Typ <sup>1</sup> | Max | Unit | С |

|-----|------------------|------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------------|------------------|-----|------|---|

| 1   | V <sub>DD</sub>  | Operating<br>Voltage   |                                            |                                                                                                          | 1.8 <sup>2</sup>       | —                | 3.6 | V    |   |

| 2   | V <sub>OH</sub>  | Output high<br>voltage | All I/O pins, low-o                        | drive strength                                                                                           |                        |                  |     |      |   |

|     |                  |                        |                                            | $\label{eq:VDD} \begin{split} V_{DD} &\geq 1.8 \text{ V}, \\ I_{Load} &= -600 \ \mu\text{A} \end{split}$ | V <sub>DD</sub> – 0.5  | _                |     | V    | С |

|     |                  |                        | All I/O pins, high                         | -drive strength                                                                                          |                        |                  | 1   |      |   |

|     |                  |                        |                                            | $V_{DD} \ge 2.7$ V,<br>$I_{Load} = -10$ mA                                                               | V <sub>DD</sub> – 0.5  |                  |     | V    | Ρ |

|     |                  |                        |                                            | $V_{DD} \ge 1.8V,$<br>$I_{Load} = -3 \text{ mA}$                                                         | V <sub>DD</sub> – 0.5  | _                | —   | V    | С |

| 3   | I <sub>OHT</sub> | Output high<br>current | Max total I <sub>OH</sub> for              | Max total I <sub>OH</sub> for all ports                                                                  |                        |                  |     |      |   |

|     |                  |                        |                                            | _                                                                                                        | _                      | —                | 100 | mA   | D |

| 4   | V <sub>OL</sub>  | Output low voltage     | All I/O pins, low-drive strength           |                                                                                                          |                        |                  |     |      |   |

|     |                  |                        |                                            | $\label{eq:VDD} \begin{split} V_{DD} &\geq 1.8 \text{ V}, \\ I_{Load} &= 600  \mu\text{A} \end{split}$   | _                      | _                | 0.5 | V    | С |

|     |                  |                        | All I/O pins, high                         | -drive strength                                                                                          |                        |                  | L   |      |   |

|     |                  |                        |                                            | $V_{DD} \ge 2.7$ V,<br>$I_{Load} = 10$ mA                                                                | _                      | _                | 0.5 | V    | Р |

|     |                  |                        |                                            | $V_{DD} \ge 1.8 \text{ V},$<br>$I_{Load} = 3 \text{ mA}$                                                 | _                      | —                | 0.5 | V    | С |

| 5   | I <sub>OLT</sub> | Output low current     | Max total I <sub>OL</sub><br>for all ports | —                                                                                                        | _                      | —                | 100 | mA   | D |

| 6   | V <sub>IH</sub>  | Input high volta       | ge all digital inputs                      | •                                                                                                        |                        |                  |     |      |   |

|     |                  |                        |                                            | all digital inputs, $V_{DD} > 2.7 \ V$                                                                   | 0.70 x V <sub>DD</sub> | _                | —   | V    | Ρ |

|     |                  |                        |                                            | all digital inputs, 2.7 V > V_{DD} $\ge$ 1.8 V                                                           | 0.85 x V <sub>DD</sub> | —                | —   | V    | Ρ |

#### **Table 9. DC Characteristics**

| Num | Symbol              | Charac                                                            | teristic                                 | Condition                                                                            | Min                    | Typ <sup>1</sup> | Max                       | Unit | С |

|-----|---------------------|-------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------|------------------------|------------------|---------------------------|------|---|

| 7   | V <sub>IL</sub>     | Input low voltage                                                 | all digital inputs                       |                                                                                      |                        |                  |                           |      | L |

|     | 12                  |                                                                   | с .                                      | all digital inputs, $V_{DD} > 2.7 \ V$                                               | _                      | _                | 0.35 x<br>V <sub>DD</sub> | V    | Р |

|     |                     |                                                                   |                                          | all digital inputs, $\begin{array}{c} \text{2.7} > V_{DD} \geq 1.8 \\ V \end{array}$ | _                      | _                | 0.30 x<br>V <sub>DD</sub> | V    | Р |

| 8   | V <sub>hys</sub>    | Input hysteresis                                                  | all digital inputs                       | —                                                                                    | 0.06 x V <sub>DD</sub> | —                |                           | mV   | С |

| 9   | I <sub>In </sub>    | Input leakage<br>current                                          | all input only<br>pins<br>(Per pin)      | $V_{In} = V_{DD} \text{ or } V_{SS}$                                                 | _                      | _                | 0.5                       | μΑ   | Ρ |

| 10  | I <sub>OZ </sub>    | Hi-Z (off-state)<br>leakage current <sup>3</sup>                  | all digital<br>input/output<br>(per pin) | $V_{In} = V_{DD} \text{ or } V_{SS}$                                                 | _                      | 0.003            | 0.5                       | μΑ   | Ρ |

| 11  | R <sub>PU</sub>     | Pull-up resistors                                                 |                                          | —                                                                                    | 17.5                   | —                | 52.5                      | kΩ   | Р |

| 12  | R <sub>PD</sub>     | Internal<br>pull-down<br>resistors <sup>4</sup>                   |                                          | _                                                                                    | 17.5                   | _                | 52.5                      | kΩ   | Ρ |

| 13  | I <sub>IC</sub>     | DC injection<br>current <sup>5, 6, 7</sup>                        | Single pin limit                         |                                                                                      |                        |                  |                           | •    |   |

|     |                     |                                                                   |                                          | $V_{SS} > V_{IN} > V_{DD}$                                                           | -0.2                   | —                | 0.2                       | mA   | D |

|     |                     |                                                                   | Total MCU limit,                         | includes sum of a                                                                    | Il stressed pin:       | S                |                           |      |   |

|     |                     |                                                                   |                                          | $V_{SS} > V_{IN} > V_{DD}$                                                           | -5                     | _                | 5                         | mA   | D |

| 14  | C <sub>In</sub>     | Input Capacitance                                                 | e, all pins                              | —                                                                                    | _                      | —                | 8                         | pF   | С |

| 15  | V <sub>RAM</sub>    | RAM retention vo                                                  | Itage                                    | —                                                                                    | _                      | 0.6              | 1.0                       | V    | С |

| 16  | V <sub>POR</sub>    | POR re-arm volta                                                  | ge <sup>8</sup>                          | —                                                                                    | 0.9                    | 1.4              | 1.79                      | V    | С |

| 17  | t <sub>POR</sub>    | POR re-arm time                                                   |                                          | —                                                                                    | 10                     | —                |                           | μS   | D |

| 18  | V <sub>LVDH</sub> 9 | Low-voltage<br>detection<br>threshold —<br>high range             | V <sub>DD</sub> falling                  |                                                                                      |                        |                  |                           |      |   |

|     |                     |                                                                   |                                          | —                                                                                    | 2.11                   | 2.16             | 2.22                      | V    | Ρ |

|     |                     |                                                                   | $V_{\text{DD}}$ rising                   |                                                                                      |                        |                  |                           |      |   |

|     |                     |                                                                   |                                          | _                                                                                    | 2.16                   | 2.23             | 2.27                      | V    | Ρ |

| 19  | V <sub>LVDL</sub>   | Low-voltage<br>detection<br>threshold —<br>low range <sup>9</sup> | V <sub>DD</sub> falling                  |                                                                                      |                        |                  |                           |      |   |

|     |                     |                                                                   |                                          | _                                                                                    | 1.80                   | 1.84             | 1.88                      | V    | Ρ |

|     |                     |                                                                   | V <sub>DD</sub> rising                   |                                                                                      |                        |                  |                           |      |   |

|     |                     |                                                                   |                                          | —                                                                                    | 1.88                   | 1.93             | 1.96                      | V    | Р |

#### Table 9. DC Characteristics (Continued)

| Num | Symbol            | Chara                                                            | acteristic                | Condition | Min      | Typ <sup>1</sup> | Max  | Unit     | С |

|-----|-------------------|------------------------------------------------------------------|---------------------------|-----------|----------|------------------|------|----------|---|

| 20  | V <sub>LVWH</sub> | Low-voltage<br>warning<br>threshold —<br>high range <sup>9</sup> | V <sub>DD</sub> falling   |           | <u> </u> | <u> </u>         |      | <u> </u> |   |

|     |                   |                                                                  |                           |           | 2.36     | 2.46             | 2.56 | V        | Р |

|     |                   |                                                                  | V <sub>DD</sub> rising    |           | I        |                  |      |          |   |

|     |                   |                                                                  |                           |           | 2.36     | 2.46             | 2.56 | V        | Р |

| 21  | V <sub>LVWL</sub> | Low-voltage<br>warning<br>threshold —<br>low range <sup>9</sup>  | V <sub>DD</sub> falling   |           |          |                  |      |          |   |

|     |                   |                                                                  |                           | _         | 2.11     | 2.16             | 2.22 | V        | Р |

|     |                   |                                                                  | V <sub>DD</sub> rising    |           |          |                  |      | •        |   |

|     |                   |                                                                  |                           |           | 2.16     | 2.23             | 2.27 | V        | Р |

| 22  | V <sub>hys</sub>  | Low-voltage inhibit reset/recover hysteresis <sup>10</sup>       |                           | _         | —        | 50               | _    | mV       | С |

| 23  | $V_{BG}$          | Bandgap Voltag                                                   | e Reference <sup>11</sup> | —         | 1.15     | 1.17             | 1.18 | V        | Ρ |

#### Table 9. DC Characteristics (Continued)

<sup>1</sup> Typical values are measured at 25°C. Characterized, not tested

<sup>2</sup> As the supply voltage rises, the LVD circuit will hold the MCU in reset until the supply has risen above V<sub>LVDL</sub>.

- $^3$  Does not include analog module pins. Dedicated analog pins should not be pulled to V<sub>DD</sub> or V<sub>SS</sub> and should be left floating when not used to reduce current leakage.

- <sup>4</sup> Measured with  $V_{In} = V_{DD}$ .

- $^{5}$  All functional non-supply pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> except PTD1.

- <sup>6</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

- <sup>7</sup> Power supply must maintain regulation within operating  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{In} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

- <sup>8</sup> Maximum is highest voltage that POR is guaranteed.

- <sup>9</sup> Run at 1 MHz bus frequency

- <sup>10</sup> Low voltage detection and warning limits measured at 1 MHz bus frequency.

- <sup>11</sup> Factory trimmed at V<sub>DD</sub> = 3.0 V, Temp = 25°C

### Supply Current Characteristics Table 10. Supply Current Characteristics 2.6

| # | Symbol           | Parar                 | neter      | Bus<br>Freq                        | V <sub>DD</sub> (V) | Typ <sup>1</sup> | Max  | Unit | Temp<br>(°C)  | С |

|---|------------------|-----------------------|------------|------------------------------------|---------------------|------------------|------|------|---------------|---|

| 1 | RI <sub>DD</sub> | Run supply current    | FEI mode;  | all modules                        | ON <sup>2</sup>     |                  |      | I    |               |   |

|   |                  |                       |            | 24 MHz                             | 3                   | 20               | 24   | mA   | -40 to<br>25  | Р |

|   |                  |                       |            | 24 MHz                             | 3                   | 20               | 24   | mA   | 105           | Р |

|   |                  |                       |            | 20 MHz                             | 3                   | 18               | _    | mA   | -40 to<br>105 | Т |

|   |                  |                       |            | 8 MHz                              | 3                   | 8                | _    | mA   | -40 to<br>105 | Т |

|   |                  |                       |            | 1 MHz                              | 3                   | 1.8              | _    | mA   | -40 to<br>105 | Т |

| 2 | RI <sub>DD</sub> | Run supply<br>current | FEI mode;  | mode; all modules OFF <sup>3</sup> |                     |                  |      |      |               |   |

|   |                  |                       |            | 24 MHz                             | 3                   | 12.3             | 14.1 | mA   | -40 to<br>105 | С |

|   |                  |                       |            | 20 MHz                             | 3                   | 10.5             | _    | mA   | -40 to<br>105 | Т |

|   |                  |                       |            | 8 MHz                              | 3                   | 4.8              | _    | mA   | -40 to<br>105 | Т |

|   |                  |                       |            | 1 MHz                              | 3                   | 1.3              | _    | mA   | -40 to<br>105 | Т |

| 3 | RI <sub>DD</sub> | Run supply<br>current | LPS=0; all | modules OF                         | F <sup>3</sup>      |                  |      |      |               |   |

|   |                  |                       |            | 16 kHz<br>FBILP                    | 3                   | 153              | 222  | μA   | -40 to<br>105 | Т |

|   |                  |                       |            | 16 kHz<br>FBELP                    | 3                   | 143              | 200  | μA   | -40 to<br>105 | Т |

| 4 | RI <sub>DD</sub> | Run supply current    | LPS=1, all | modules OF                         |                     |                  |      | T    |               |   |

|   |                  |                       |            | 16 kHz<br>FBELP                    | 3                   | 20               | 26   | μA   | 0 to 70       | Т |

|   |                  |                       |            | 16 kHz<br>FBELP                    | 3                   | 20               | 70   | μA   | -40 to<br>105 | Т |

| # | Symbol             | Parameter                                      | Bus<br>Freq | V <sub>DD</sub> (V) | Typ <sup>1</sup> | Мах  | Unit | Temp<br>(°C)  | С |

|---|--------------------|------------------------------------------------|-------------|---------------------|------------------|------|------|---------------|---|

| 5 | WI <sub>DD</sub>   | Wait mode FEI mode, supply current             | all modules | OFF <sup>3</sup>    |                  |      |      |               |   |

|   |                    |                                                | 24 MHz      | 3                   | 6.7              | _    | mA   | -40 to<br>105 | С |

|   |                    |                                                | 20 MHz      | 3                   | 5.6              |      | mA   | -40 to<br>105 | Т |

|   |                    |                                                | 8 MHz       | 3                   | 2.4              |      | mA   | -40 to<br>105 | Т |

|   |                    |                                                | 1 MHz       | 3                   | 1                |      | mA   | -40 to<br>105 | Т |

| 6 | LPWI <sub>DD</sub> | Low-Power<br>Wait mode<br>supply current       |             |                     |                  |      |      |               |   |

|   |                    |                                                | 16 KHz      | 3                   | 10               | 40   | μA   | -40 to<br>105 | Т |

| 7 | S2I <sub>DD</sub>  | Stop2 mode<br>supply cur-<br>rent <sup>4</sup> |             |                     |                  |      |      |               |   |

|   |                    |                                                | N/A         | 3                   | 0.39             | 0.8  | μΑ   | -40 to<br>25  | Ρ |

|   |                    |                                                | N/A         | 3                   | 2.4              | 4.5  | μA   | 70            | С |

|   |                    |                                                | N/A         | 3                   | 7                | 11   | μA   | 85            | С |

|   |                    |                                                | N/A         | 3                   | 16               | 22   | μA   | 105           | Р |

|   |                    |                                                | N/A         | 2                   | 0.2              | 0.45 | μΑ   | -40 to<br>25  | С |

|   |                    |                                                | N/A         | 2                   | 2                | 3.8  | μA   | 70            | С |

|   |                    |                                                | N/A         | 2                   | 8                | 12   | μA   | 85            | С |

|   |                    |                                                | N/A         | 2                   | 10               | 20   | μA   | 105           | С |

#### Table 10. Supply Current Characteristics (Continued)

| # | Symbol            | Parameter                                              | Bus<br>Freq | V <sub>DD</sub> (V) | Typ <sup>1</sup> | Мах | Unit | Temp<br>(°C) | С |

|---|-------------------|--------------------------------------------------------|-------------|---------------------|------------------|-----|------|--------------|---|

|   | S3I <sub>DD</sub> | Stop3 mode No clocks<br>supply<br>current <sup>4</sup> | active      |                     |                  |     |      |              |   |

|   |                   |                                                        | N/A         | 3                   | 0.55             | 0.9 | μΑ   | -40 to<br>25 | Р |

|   |                   |                                                        | N/A         | 3                   | 5.5              | 8.9 | μA   | 70           | С |

|   |                   |                                                        | N/A         | 3                   | 14               | 18  | μA   | 85           | С |

| 8 |                   |                                                        | N/A         | 3                   | 37               | 42  | μA   | 105          | Р |

|   |                   |                                                        | N/A         | 2                   | 0.35             | 0.5 | μA   | -40 to<br>25 | С |

|   |                   |                                                        | N/A         | 2                   | 3.8              | 6.8 | μA   | 70           | С |

|   |                   |                                                        | N/A         | 2                   | 14               | 20  | μA   | 85           | С |

|   |                   |                                                        | N/A         | 2                   | 25               | 46  | μA   | 105          | С |

| Table 10. Supply Current Characteristics (Co | ontinued) |

|----------------------------------------------|-----------|

|----------------------------------------------|-----------|

<sup>1</sup> Data in Typical column was characterized at 3.0 V, 25 °C or is typical recommended value.

$^{2}$  ON = System Clock Gating Control registers turn on system clock to the corresponding modules.

<sup>3</sup> OFF = System Clock Gating Control registers turn off system clock to the corresponding modules.

<sup>4</sup> All digital pins must be configured to a known state to prevent floating pins from adding current. Smaller packages may have some pins that are not bonded out; however, software must still be configured to the largest pin package available so that all pins are in a known state. Otherwise, floating pins that are not bonded in the smaller packages may result in a higher current draw.

NOTE: I/O pins are configured to output low, input-only pins are configured to pullup enabled. IRO pin connects to ground. TRIAMP*x*, OPAMP*x*, DACO, and VREFO pins are at reset state and unconnected.

| # | Parameter             | Condition                                                 |     | Temperature (℃) |     |     |      |       |   |

|---|-----------------------|-----------------------------------------------------------|-----|-----------------|-----|-----|------|-------|---|

| " |                       |                                                           | -40 | 25              | 70  | 85  | 105  | Units | С |

| 1 | LPO                   | —                                                         | 50  | 75              | 100 | 150 | 250  | nA    | D |

| 2 | EREFSTEN              | RANGE = HGO = 0                                           | 600 | 650             | 750 | 850 | 1000 | nA    | D |

| 3 | IREFSTEN <sup>1</sup> | _                                                         | —   | 73              | 80  | 92  | 125  | μA    | Т |

| 4 | TOD                   | Does not include clock source<br>current                  | 50  | 75              | 100 | 150 | 250  | nA    | D |

| 5 | PRACMP <sup>1</sup>   | Not using the bandgap<br>(BGBE = 0)                       | 30  | 35              | 40  | 55  | 75   | μA    | Т |

| 6 | ADC <sup>1</sup>      | ADLPC = ADLSMP = 1<br>Not using the bandgap<br>(BGBE = 0) | 190 | 195             | 210 | 220 | 260  | μA    | Т |

Table 11. Typical Stop Mode Adders

| # | Parameter           | Condition                        |     |     | Units | с   |     |       |   |

|---|---------------------|----------------------------------|-----|-----|-------|-----|-----|-------|---|

| # | Farameter           | Condition                        | -40 | 25  | 70    | 85  | 105 | Units | C |

| 7 | DAC <sup>1</sup>    | High-Power mode; no load on DACO | 369 | 377 | 377   | 390 | 410 | μA    | Т |

|   |                     | Low-Power mode                   | 50  | 51  | 51    | 52  | 60  | μA    | Т |

| 8 | OPAMP <sup>1</sup>  | High-Power mode                  | 453 | 538 | 538   | 540 | 540 | μA    | Т |

| 0 |                     | Low-Power mode                   | 56  | 67  | 67    | 68  | 70  | μA    | Т |

| 9 | TRIAMP <sup>1</sup> | High-Power mode                  | 430 | 432 | 433   | 438 | 478 | μA    | Т |

| 9 |                     | Low-Power mode                   | 52  | 52  | 52    | 55  | 60  | μA    | Т |

#### Table 11. Typical Stop Mode Adders (Continued)

<sup>1</sup> Not available in stop2 mode.

### 2.7 PRACMP Electricals

| #  | Characteristic                                 | Symbol                                | Min                   | Typical | Max             | Unit | С |

|----|------------------------------------------------|---------------------------------------|-----------------------|---------|-----------------|------|---|

| 1  | Supply voltage                                 | V <sub>PWR</sub>                      | 1.8                   | _       | 3.6             | V    | P |

| 2  | Supply current (active) (PRG enabled)          | I <sub>DDACT1</sub>                   |                       |         | 80              | μA   | D |

| 3  | Supply current (active) (PRG disabled)         | I <sub>DDACT2</sub>                   | —                     | _       | 40              | μA   | D |

| 4  | Supply current (ACMP and PRG all disabled)     | I <sub>DDDIS</sub>                    | —                     | —       | 2               | nA   | D |

| 5  | Analog input voltage                           | VAIN                                  | V <sub>SS</sub> – 0.3 | _       | V <sub>DD</sub> | V    | D |

| 6  | Analog input offset voltage                    | VAIO                                  | —                     | 5       | 40              | mV   | D |

| 7  | Analog comparator hysteresis                   | V <sub>H</sub>                        | 3.0                   |         | 20.0            | mV   | D |

| 8  | Analog input leakage current                   | I <sub>ALKG</sub>                     | —                     |         | 1               | nA   | D |

| 9  | Analog comparator initialization delay         | tAINIT                                | —                     |         | 1.0             | μS   | D |

| 10 | Programmable reference generator inputs        | V <sub>In2</sub> (V <sub>DD25</sub> ) | 1.8                   |         | 2.75            | V    | D |

| 11 | Programmable reference generator setup delay   | t <sub>PRGST</sub>                    | —                     | 1       | —               | μs   | D |

| 12 | Programmable reference generator step size     | Vstep                                 | 0.75                  | 1       | 1.25            | LSB  | D |

| 13 | Programmable reference generator voltage range | Vprgout                               | V <sub>In</sub> /32   | _       | V <sub>in</sub> | V    | Р |

#### Table 12. PRACMP Electrical Specifications

## 2.8 12-Bit DAC Electricals

#### Table 13. DAC 12LV Operating Requirements

| # | Characteristic          | Symbol            | Min  | Max | Unit | С | Notes                                                                                       |

|---|-------------------------|-------------------|------|-----|------|---|---------------------------------------------------------------------------------------------|

| 1 | Supply voltage          | V <sub>DDA</sub>  | 1.8  | 3.6 | V    | Р |                                                                                             |

| 2 | Reference voltage       | V <sub>DACR</sub> | 1.15 | 3.6 | V    | С |                                                                                             |

| 3 | Temperature             | T <sub>A</sub>    | -40  | 105 | c    | С |                                                                                             |

| 4 | Output load capacitance | CL                | _    | 100 | pF   | с | A small load capacitance<br>(47 pF) can improve the<br>bandwidth performance<br>of the DAC. |

| 5 | Output load current     | ١ <sub>L</sub>    | _    | 1   | mA   | С |                                                                                             |

#### Table 14. DAC 12-Bit Operating Behaviors

| # | Characteristic                                                                                                                  | Symbol                 | Min | Тур | Max | Unit | С | Notes                                                                          |

|---|---------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|-----|------|---|--------------------------------------------------------------------------------|

| 1 | Resolution                                                                                                                      | N                      | 12  | —   | 12  | bit  | Т |                                                                                |

| 2 | Supply current low-power mode                                                                                                   | I <sub>DDA_DACLP</sub> | _   | 50  | 100 | μA   | т |                                                                                |

| 3 | Supply current high-power mode                                                                                                  | I <sub>DDA_DACHP</sub> | —   | 345 | 500 | μA   | Т |                                                                                |

| 4 | Full-scale Settling time<br>(±1 LSB)<br>(0x080 to 0xF7F or 0xF7F to<br>0x080)<br>low-power mode                                 | Ts <sub>FS</sub> LP    | _   | _   | 200 | μs   | т | • $V_{DDA} = 3 V$<br>or 2.2 V<br>• $V_{REFSEL} = 1$<br>• Temperature<br>= 25°C |

| 5 | Full-scale Settling time<br>(±1 LSB)<br>(0x080 to 0xF7F or 0xF7F to<br>0x080)<br>high-power mode                                | Ts <sub>FS</sub> HP    | _   | _   | 30  | μs   | т | • $V_{DDA} = 3 V$<br>or 2.2 V<br>• $V_{REFSEL} = 1$<br>• Temperature<br>= 25°C |

| 6 | Code-to-code Settling time<br>(±1 LSB)<br>(0xBF8 to 0xC08 or 0xC08 to<br>0xBF8)<br>low-power mode                               | Ts <sub>C-C</sub> LP   | _   | _   | 5   | μs   | т | • $V_{DDA} = 3 V$<br>or 2.2 V<br>• $V_{REFSEL} = 1$<br>• Temperature<br>= 25°C |

| 7 | Code-to-code Settling time<br>(±1 LSB)<br>(0xBF8 to 0xC08 or 0xC08 to<br>0xBF8)<br>high-power mode (3 V at Room<br>Temperature) | Ts <sub>C-C</sub> HP   | _   | 1   | _   | μs   | т | • $V_{DDA} = 3 V$<br>or 2.2 V<br>• $V_{REFSEL} = 1$<br>• Temperature<br>= 25°C |

| 8 | DAC output voltage range low<br>(high-power mode, no load, DAC<br>set to 0) (3 V at Room<br>Temperature)                        | V <sub>dacoutl</sub>   | _   | _   | 100 | mV   | т |                                                                                |

| #  | Characteristic                                                                    | Symbol               | Min                        | Тур  | Max   | Unit  | С | Notes                                                                                               |

|----|-----------------------------------------------------------------------------------|----------------------|----------------------------|------|-------|-------|---|-----------------------------------------------------------------------------------------------------|

| 9  | DAC output voltage range high<br>(high-power mode, no load, DAC<br>set to 0x0FFF) | V <sub>dacouth</sub> | V <sub>DACR</sub> -<br>100 | _    | _     | mV    | т |                                                                                                     |

| 10 | Integral non-linearity error                                                      | INL                  | —                          | —    | ± 8   | LSB   | Т |                                                                                                     |

| 11 | Differential non-linearity error<br>VDACR is > 2.4 V                              | DNL                  | _                          | _    | ± 1   | LSB   | т |                                                                                                     |

| 12 | Offset error                                                                      | E <sub>O</sub>       | _                          | ±0.4 | ± 3   | %FSR  | т | Calculated by a<br>best fit curve<br>from V <sub>SS</sub> +<br>100mV to<br>V <sub>REFH</sub> -100mV |

| 13 | Gain error, V <sub>REFH</sub> = V <sub>ext</sub> = V <sub>DD</sub>                | E <sub>G</sub>       | _                          | ±0.1 | ± 0.5 | %FSR  | т | Calculated by a<br>best fit curve<br>from V <sub>SS</sub> +<br>100mV to<br>V <sub>REFH</sub> –100mV |

| 14 | Power supply rejection ratio $V_{DD} \ge 2.4 \text{ V}$                           | PSRR                 | 60                         | _    | _     | dB    | т |                                                                                                     |

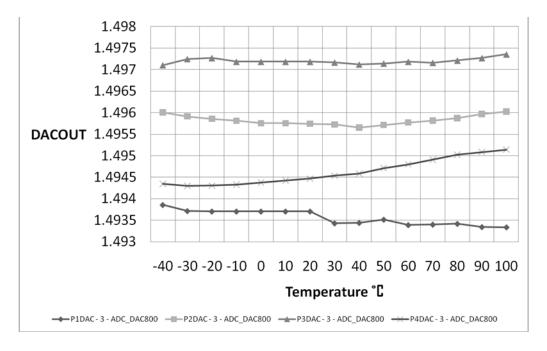

| 15 | Temperature drift of offset voltage<br>(DAC set to 0x0800)                        | T <sub>co</sub>      | _                          |      | 2     | mV    | т | See Typical<br>Drift figure that<br>follows.                                                        |

| 16 | Offset aging coefficient                                                          | A <sub>c</sub>       | _                          | _    | 8     | μV/yr | Т |                                                                                                     |

Figure 6. Offset at Half Scale vs Temperature

### 2.9 ADC Characteristics

| # | Symb              | Characteristic              | Conditions                                                                    | Min               | Typ <sup>1</sup> | Max              | Unit | С | Comment                                   |

|---|-------------------|-----------------------------|-------------------------------------------------------------------------------|-------------------|------------------|------------------|------|---|-------------------------------------------|