MMC2114 MMC2113 MMC2112

Advance Information

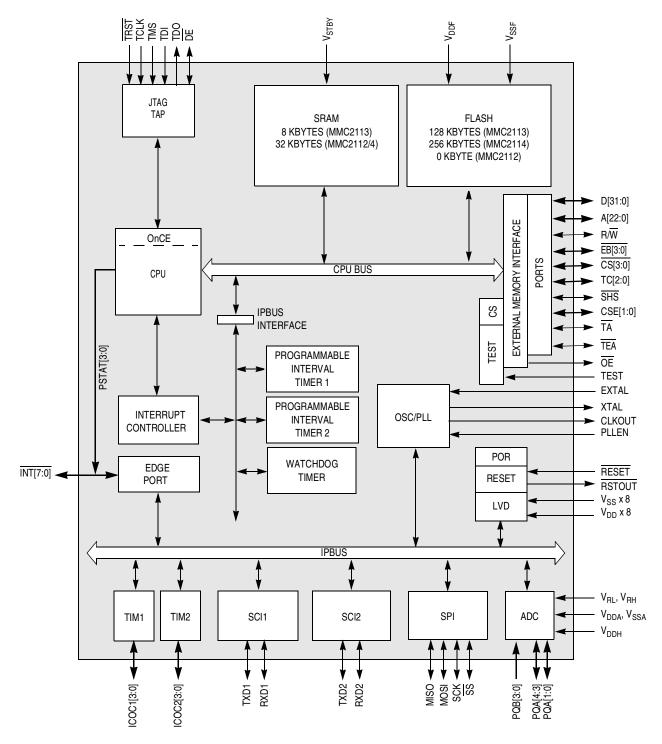

M•CORE Microcontrollers

> MMC2114/D Rev. 1, 4/2002

WWW.MOTOROLA.COM/SEMICONDUCTORS

# Freescale Semiconductor, Inc.

#### Freescale Semiconductor, Inc.

# MMC2114 MMC2113 MMC2112

#### **Advance Information**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.motorola.com/semiconductors/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

Motorola and the Stylized M Logo are registered trademarks of Motorola, Inc. DigitalDNA is a trademark of Motorola, Inc.

© Motorola, Inc., 2002

MMC2114 • MMC2113 • MMC2112 — Rev. 1.0

### **Advance Information**

#### **Revision History**

| Date        | Revision<br>Level | Description                                                                                                                                                | Page<br>Number(s) |

|-------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| March, 2002 | N/A               | Original release                                                                                                                                           | N/A               |

| April, 2002 | 1.0               | Figure 4-4. Chip Identification Register (CIR) — Corrrected reset condition for bits 11 and 8                                                              | 131               |

|             |                   | <b>20.9.3 Show Strobe (SHS)</b> — Corrected description in first paragraph                                                                                 | 542               |

|             |                   | 23.5 Junction Temperature Determination — Changed subsection title from Power Dissipation to Junction Temperature Determination                            | 614               |

|             |                   | 23.7 DC Electrical Specifications — Under operating supply current, external oscillator clocking changed stop mode maximum value from 10 μA to 200 μA      | 616               |

|             |                   | 23.7 DC Electrical Specifications — Under operating supply current, crystal/PLL clock changed maximum value for OSC and PLL disabled from 150 μA to 200 μA | 617               |

|             |                   | Appendix A. Security — Updated for clarity                                                                                                                 | 649               |

### Advance Information — MMC2114, MMC2113, and MMC2112

# **List of Sections**

| Section 1. General Description45                                    |

|---------------------------------------------------------------------|

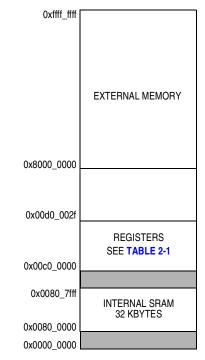

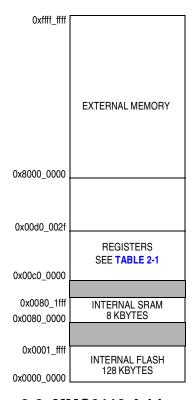

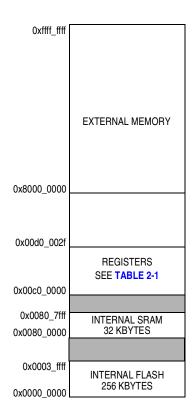

| Section 2. System Memory Map53                                      |

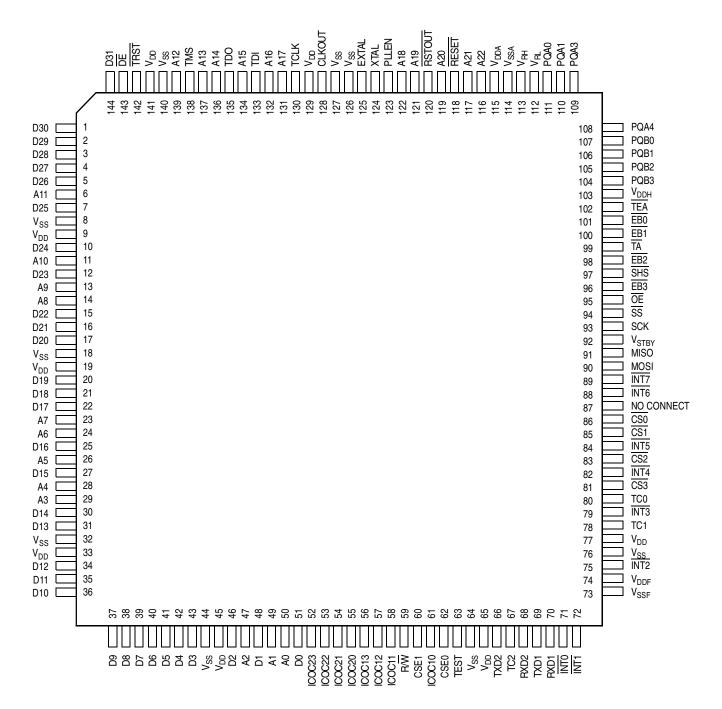

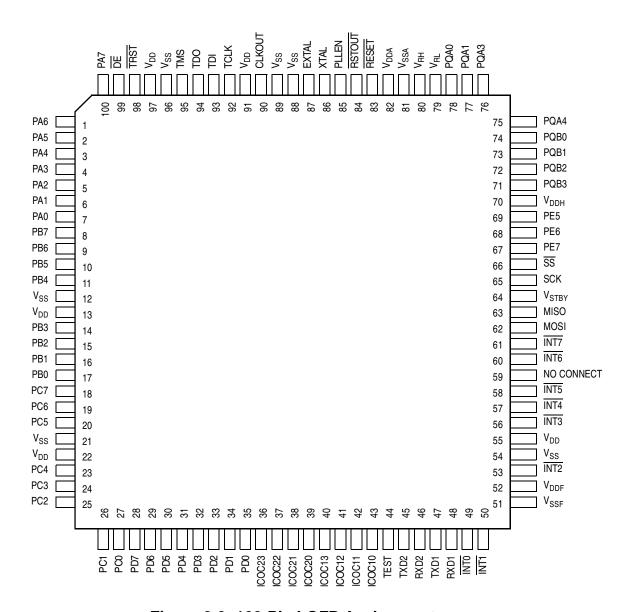

| Section 3. Signal Description95                                     |

| Section 4. Chip Configuration Module (CCM)121                       |

| Section 5. Reset Controller Module139                               |

| Section 6. Power Management155                                      |

| Section 7. M•CORE M210 Central Processor Unit (CPU)                 |

| Section 8. Interrupt Controller Module                              |

| Section 9. Static Random Access Memory (SRAM)199                    |

| Section 10. Second Generation FLASH for M•CORE (SGFM)               |

| Section 11. Clock Module243                                         |

| Section 12. Ports Module271                                         |

| Section 13. Edge Port Module (EPORT)285                             |

| Section 14. Watchdog Timer Module295                                |

| Section 15. Programmable Interrupt Timer Modules (PIT1 and PIT2)305 |

| Section 16. Timer Modules (TIM1 and TIM2)317                        |

MMC2114 • MMC2113 • MMC2112 — Rev. 1.0

### **List of Sections**

| Section 17. | Serial Communications Interface  Modules (SCI1 and SCI2) |

|-------------|----------------------------------------------------------|

| Section 18. | Serial Peripheral Interface Module (SPI)397              |

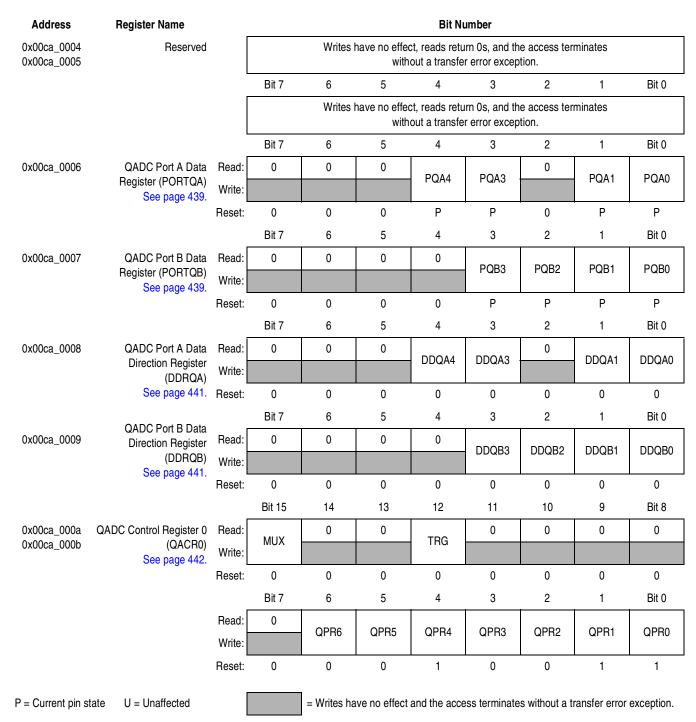

| Section 19. | Queued Analog-to-Digital Converter (QADC)425             |

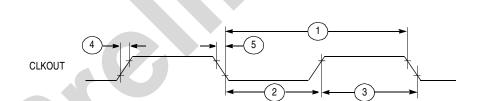

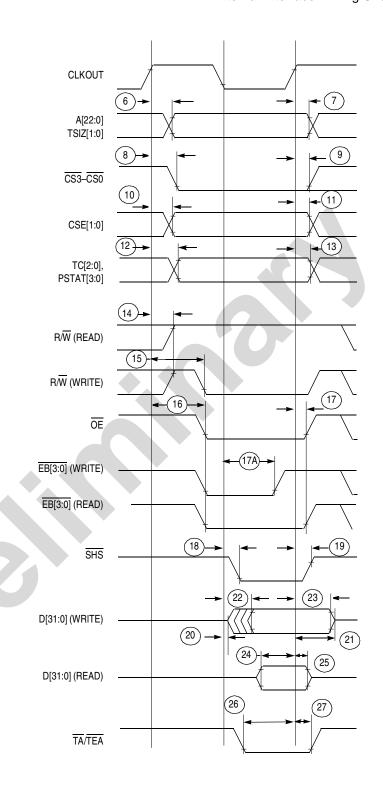

| Section 20  | External Bus Interface Module (EBI) 527                  |

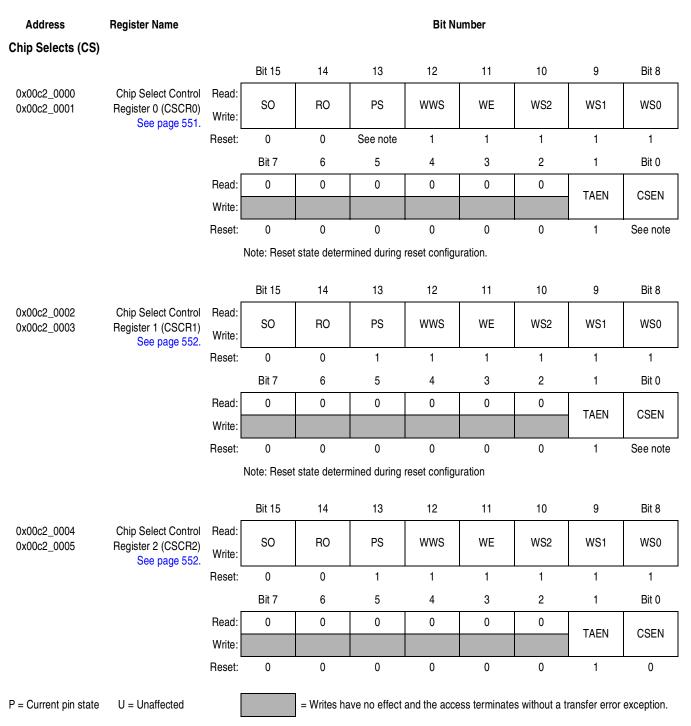

| Section 21. | Chip Select Module547                                    |

| Section 22  | JTAG Test Access Port and OnCE559                        |

| Section 23. | Preliminary Electrical Specifications611                 |

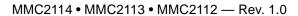

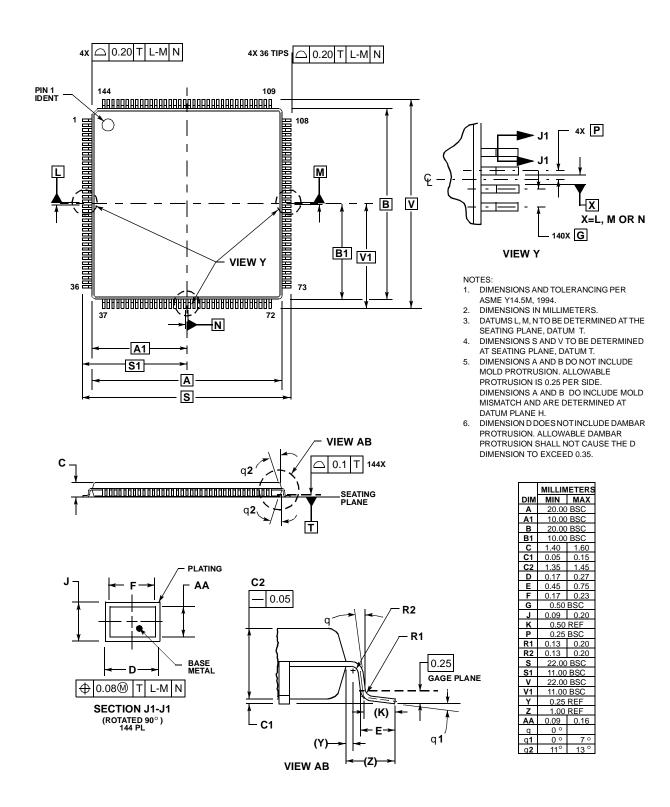

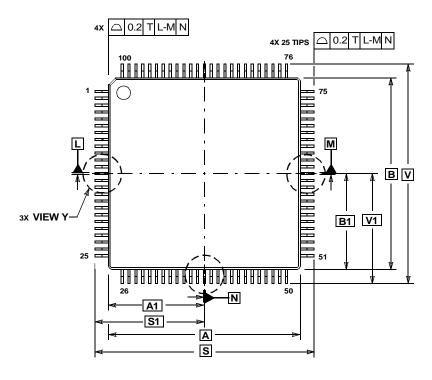

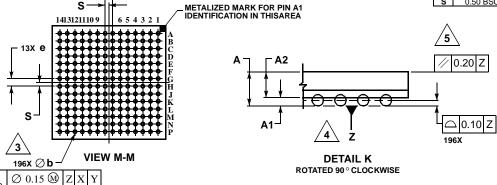

| Section 24  | Mechanical Specifications 639                            |

| Section 25. | Ordering Information647                                  |

| Appendix A  | A. Security                                              |

Advance Information

#### Advance Information — MMC2114, MMC2113, and MMC2112

#### **Table of Contents**

#### **Section 1. General Description** 1.1 1.2 1.3 1.4 **Section 2. System Memory Map** 2.1 2.2 2.3 2.4 **Section 3. Signal Description** 3.1 3.2 3.3 3.4 Chip Specific Implementation Signal Issues......109 3.4.1 3.4.2 3.4.3 3.4.4 Serial Communications Interface (SCI1 and SCI2) 3.4.5

Queued Analog-to-Digital Converter (QADC)

MMC2114 • MMC2113 • MMC2112 — Rev. 1.0

3.4.6

| 3.5 Si   | gnal Descriptions113                           |

|----------|------------------------------------------------|

| 3.5.1    | Reset Signals                                  |

| 3.5.1.1  | Reset In (RESET)113                            |

| 3.5.1.2  | Reset Out (RSTOUT)113                          |

| 3.5.2    | Phase-Lock Loop (PLL) and Clock Signals        |

| 3.5.2.1  | External Clock In (EXTAL)                      |

| 3.5.2.2  | Crystal (XTAL)                                 |

| 3.5.2.3  | Clock Out (CLKOUT)                             |

| 3.5.2.4  | PLL Enable (PLLEN)                             |

| 3.5.3    | External Memory Interface Signals              |

| 3.5.3.1  | Data Bus (D[31:0])                             |

| 3.5.3.2  | Show Cycle Strobe (SHS)                        |

| 3.5.3.3  | Transfer Acknowledge (TA)                      |

| 3.5.3.4  | Transfer Error Acknowledge (TEA)               |

| 3.5.3.5  | Emulation Mode Chip Selects (CSE[1:0])         |

| 3.5.3.6  | Transfer Code (TC[2:0])115                     |

| 3.5.3.7  | Read/Write (R/W)115                            |

| 3.5.3.8  | Address Bus (A[22:0])                          |

| 3.5.3.9  | Enable Byte (EB[3:0])                          |

| 3.5.3.10 | Chip Select (CS[3:0])                          |

| 3.5.3.11 | Output Enable (OE)                             |

| 3.5.4    | Edge Port Signals                              |

| 3.5.4.1  | External Interrupts (INT[7:6])                 |

| 3.5.4.2  | External Interrupts (INT[5:2])                 |

| 3.5.4.3  | External Interrupts (INT[1:0])                 |

| 3.5.5    | Serial Peripheral Interface Module Signals     |

| 3.5.5.1  | Master Out/Slave In (MOSI)117                  |

| 3.5.5.2  | Master In/Slave Out (MISO)117                  |

| 3.5.5.3  | Serial Clock (SCK)117                          |

| 3.5.5.4  | Slave Select (SS)117                           |

| 3.5.6    | Serial Communications Interface Module Signals |

| 3.5.6.1  | Receive Data (RXD1 and RXD2)117                |

| 3.5.6.2  | Transmit Data (TXD1 and TXD2)118               |

| 357      | Timer Signals (ICOC1[3:0] and ICOC2[3:0]) 118  |

**Advance Information**

| 3.5.8 Analog-to-Digital Converter Signals                      |

|----------------------------------------------------------------|

|                                                                |

| 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1 2 1                        |

| O (RII RE)                                                     |

| 3.5.8.3 Analog Supply (V <sub>DDA</sub> and V <sub>SSA</sub> ) |

|                                                                |

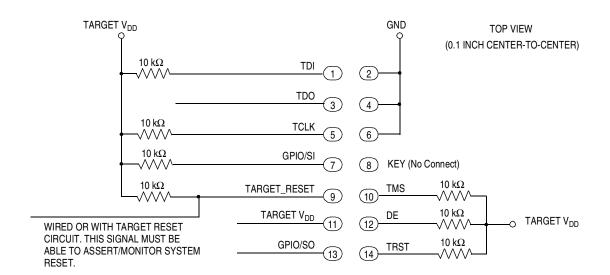

| 3.5.9 Debug and Emulation Support Signals                      |

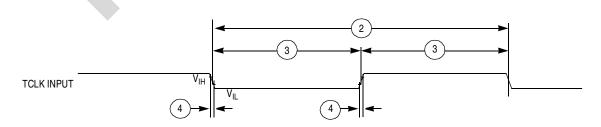

| 3.5.9.2 Test Clock (TCLK)                                      |

| 3.5.9.3 Test Mode Select (TMS)                                 |

| 3.5.9.4 Test Data Input (TDI)                                  |

| 3.5.9.5 Test Data Output (TDO)                                 |

| 3.5.9.6 Debug Event (DE)                                       |

| 3.5.10 Test Signal (TEST)                                      |

| 3.5.11 Power and Ground Signals                                |

| 3.5.11.1 Standby Power (V <sub>STBY</sub> )                    |

| 3.5.11.2 Positive Supply (V <sub>DD</sub> )                    |

| 3.5.11.3 Ground (V <sub>SS</sub> )                             |

| 0.00.000 (1.00.000)                                            |

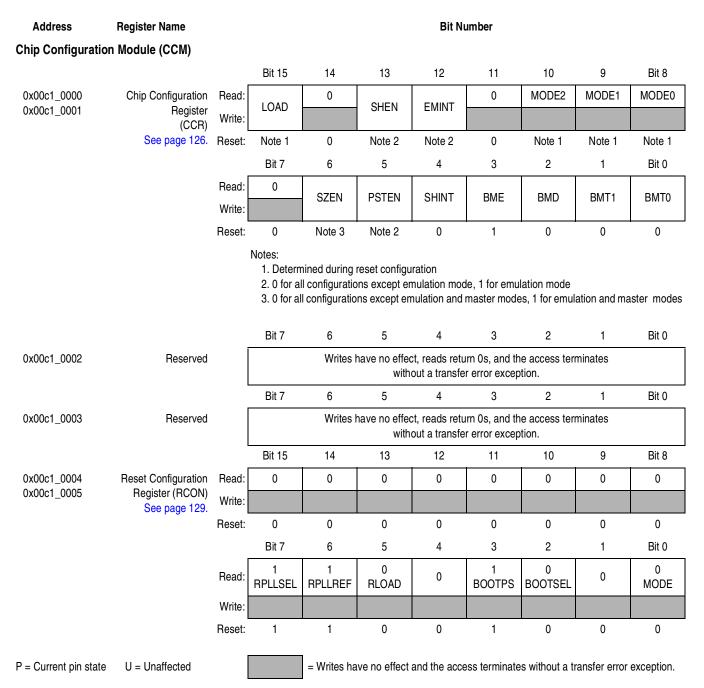

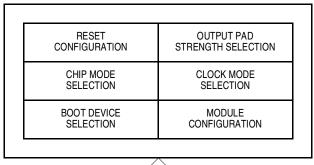

| Section 4. Chip Configuration Module (CCM)                     |

| 4.1 Contents                                                   |

| 4.2 Introduction                                               |

| 4.3 Features                                                   |

|                                                                |

| 4.4       Modes of Operation                                   |

| 4.4.2 Single-Chip Mode                                         |

| 4.4.3 Emulation Mode                                           |

| 4.4.4 Factory Access Slave Test (FAST) Mode                    |

|                                                                |

| 4.5 Block Diagram                                              |

| 4.6 Signal Descriptions                                        |

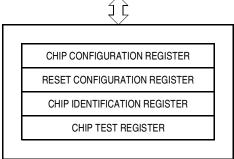

| 4.7 Memory Map and Registers                                   |

| 4.7.1 Programming Model                                        |

| 4.7.2 Memory Map                                               |

| 4.7.3 Register Descriptions                                    |

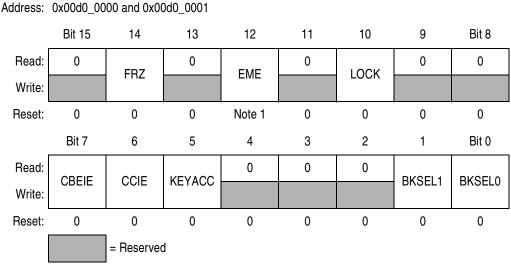

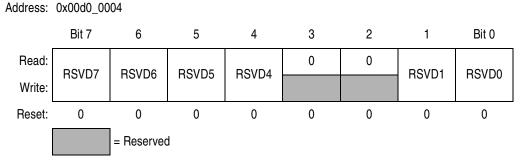

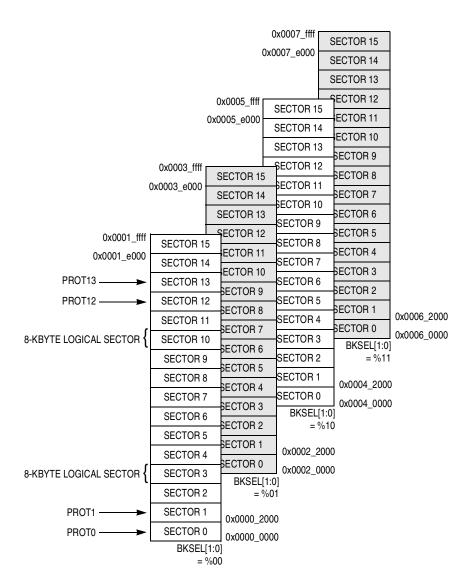

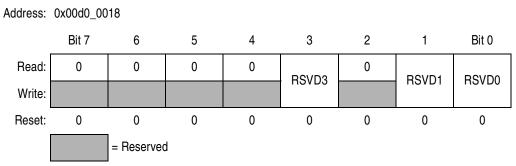

| 4.7.3.1 Chip Configuration Register126                         |

| 4.7.3.2 Reset Configuration Register129                        |

| 4.7.0.0 Ohin Identification Deviator 404                       |

| 4.7.3.3 Chip Identification Register                           |

| 4.7.3.4 Chip Test Register                                     |

| 4.8    | Functional Description                    |

|--------|-------------------------------------------|

| 4.8.1  | Reset Configuration                       |

| 4.8.2  | Chip Mode Selection                       |

| 4.8.3  | Boot Device Selection                     |

| 4.8.4  | Output Pad Strength Configuration137      |

| 4.8.5  | Clock Mode Selection                      |

| 4.8.6  | Internal FLASH Configuration138           |

| 4.9    | Reset                                     |

| 4.10   | Interrupts138                             |

|        |                                           |

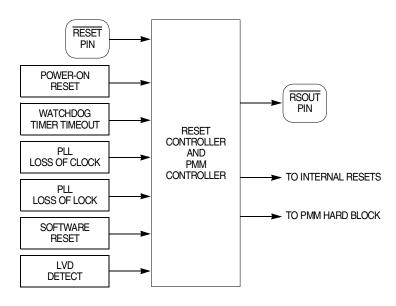

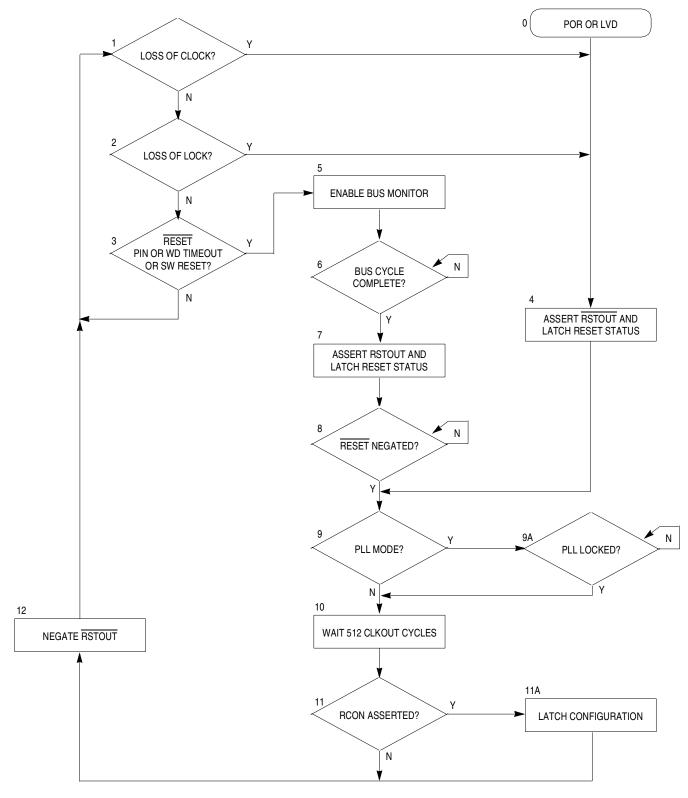

|        | Section 5. Reset Controller Module        |

| 5.1    | Contents                                  |

| 5.2    | Overview140                               |

| 5.3    | Features                                  |

| 5.4    | Block Diagram141                          |

| 5.5    | Signals                                   |

| 5.5.1  | RESET142                                  |

| 5.5.2  | RSTOUT142                                 |

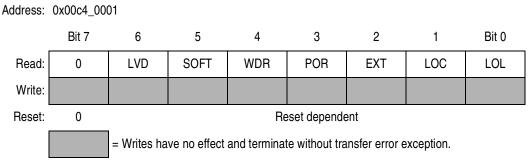

| 5.6    | Memory Map and Registers                  |

| 5.6.1  | Reset Control Register                    |

| 5.6.2  | Reset Status Register145                  |

| 5.7    | Functional Description                    |

| 5.7.1  | Reset Sources                             |

| 5.7.1. | 1 Power-On Reset                          |

| 5.7.1. |                                           |

| 5.7.1. | 3 Watchdog Timer Reset148                 |

| 5.7.1. |                                           |

| 5.7.1. |                                           |

| 5.7.1. |                                           |

| 5.7.1. |                                           |

| 5.7.2  | Reset Control Flow149                     |

| 5.7.2. | · · · · · · · · · · · · · · · · · · ·     |

| 5.7.2. | •                                         |

| 5.7.2. | 3 Power-On Reset/Low-Voltage Detect Reset |

Advance Information

| 5.7.3          | Concurrent Resets                                     | 2 |

|----------------|-------------------------------------------------------|---|

| 5.7.3          | .1 Reset Flow                                         | 2 |

| 5.7.3          | .2 Reset Status Flags15                               | 2 |

|                |                                                       |   |

|                | Section 6. Power Management                           |   |

| 6.1            | Contents                                              | 5 |

| 6.2            | Introduction                                          | 6 |

| 6.3            | Low-Power Modes                                       | 6 |

| 6.3.1          | Run Mode15                                            | 6 |

| 6.3.2          | Wait Mode                                             | 7 |

| 6.3.3          |                                                       |   |

| 6.3.4          | ·                                                     |   |

| 6.3.5          | •                                                     |   |

| 6.4            | Peripheral Behavior in Low-Power Modes                |   |

| 6.4.1          | Reset                                                 |   |

| 6.4.2          |                                                       |   |

| 6.4.3          |                                                       |   |

| 6.4.4<br>6.4.5 |                                                       |   |

| 6.4.6          | •                                                     |   |

| 6.4.7          | 3                                                     |   |

| 6.4.8          |                                                       |   |

| 6.4.9          |                                                       |   |

| 6.4.1          |                                                       |   |

| 6.4.1          | 1 Programmable Interrupt Timers (PIT1 and PIT2)16     | 2 |

| 6.4.1          | 2 Serial Peripheral Interface (SPI)                   | 2 |

| 6.4.1          | <b>\</b>                                              |   |

| 6.4.1          | 4 Timers (TIM1 and TIM2)16                            | 3 |

| 6.5            | Summary of Peripheral State During Low-Power Modes 16 | 3 |

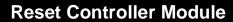

|                | Section 7. M•CORE M210 Central Processor              |   |

|                | Unit (CPU)                                            |   |

| 7.1            | Contents                                              | 5 |

| 7.2            | Introduction                                          |   |

|                |                                                       |   |

| 7.3            | Features                                              |   |

| 7.4            | Microarchitecture Summary                             | 7 |

|                |                                                       |   |

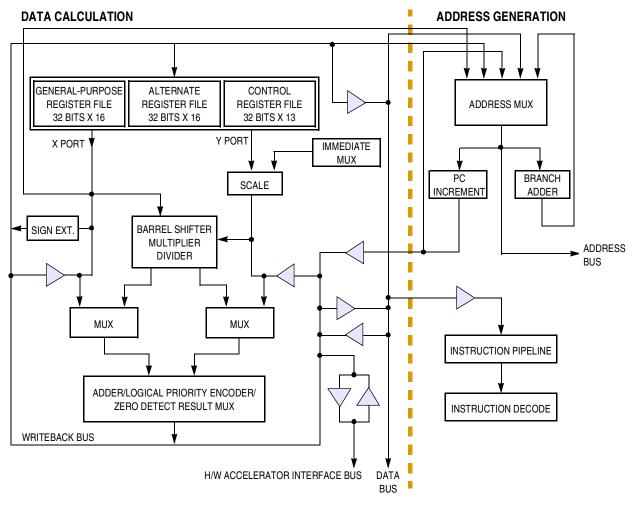

| 7.5            | Programming Model                      |

|----------------|----------------------------------------|

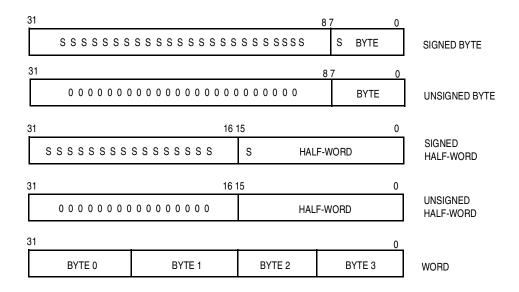

| 7.6            | Data Format Summary                    |

| 7.7            | Operand Addressing Capabilities        |

| 7.8            | Instruction Set Overview172            |

|                | Section 8. Interrupt Controller Module |

| 8.1            | Contents                               |

| 8.2            | Introduction                           |

| 8.3            | Features                               |

| 8.4            | Low-Power Mode Operation               |

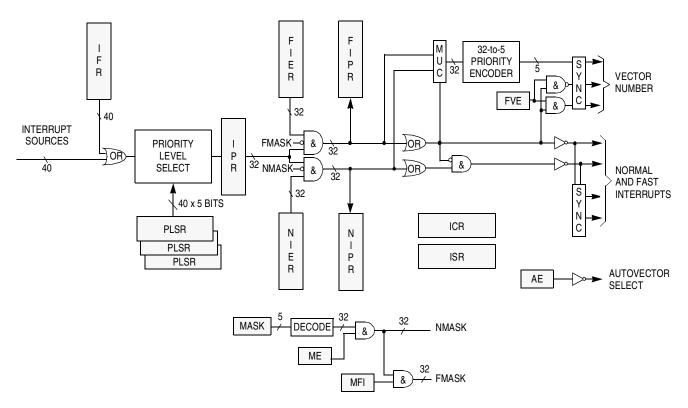

| 8.5            | Block Diagram179                       |

| 8.6            | External Signals                       |

| 8.7            | Memory Map and Registers               |

| 8.7.1          |                                        |

| 8.7.2          |                                        |

| 8.7.2          | •                                      |

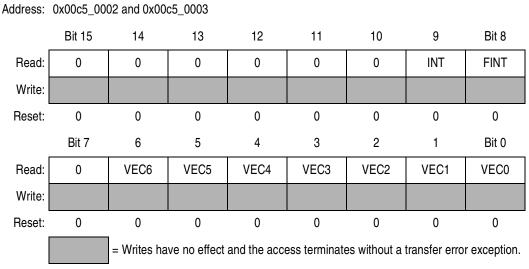

| 8.7.2          | .2 Interrupt Status Register           |

| 8.7.2          |                                        |

| 8.7.2          | 3 3 3                                  |

| 8.7.2          | 3                                      |

| 8.7.2          | 3 3 3                                  |

| 8.7.2          | 3                                      |

| 8.7.2          | 1 3 3                                  |

| 8.7.2          | 3                                      |

| 8.8            | Functional Description                 |

| 8.8.1<br>8.8.2 |                                        |

| 8.8.3          |                                        |

| 8.8.4          |                                        |

| 8.8.4          |                                        |

| 8.8.4          | _                                      |

| 8.8.4          |                                        |

| 8.8.5          | Interrupts                             |

|                |                                        |

**Advance Information**

| S                  | Section 9. Static Random Access Memory (SRAM)         |    |

|--------------------|-------------------------------------------------------|----|

| 9.1                | Contents                                              | 9  |

| 9.2                | Introduction19                                        | 9  |

| 9.3                | Modes of Operation                                    | 0  |

| 9.4                | Low-Power Modes                                       | 0  |

| 9.5                | Standby Power Supply Pin (V <sub>STBY</sub> )         | 0  |

| 9.6                | Standby Operation                                     |    |

| 9.7                | Reset Operation                                       |    |

| 9.8                | Interrupts20                                          |    |

|                    |                                                       |    |

|                    | Section 10. Second Generation FLASH for M•CORE (SGFM) |    |

| 10.1               | Contents                                              | 12 |

| 10.1               | Introduction                                          |    |

| _                  |                                                       |    |

| 10.3               | Glossary                                              |    |

| 10.4               | Features                                              |    |

| 10.5               | Modes of Operation                                    |    |

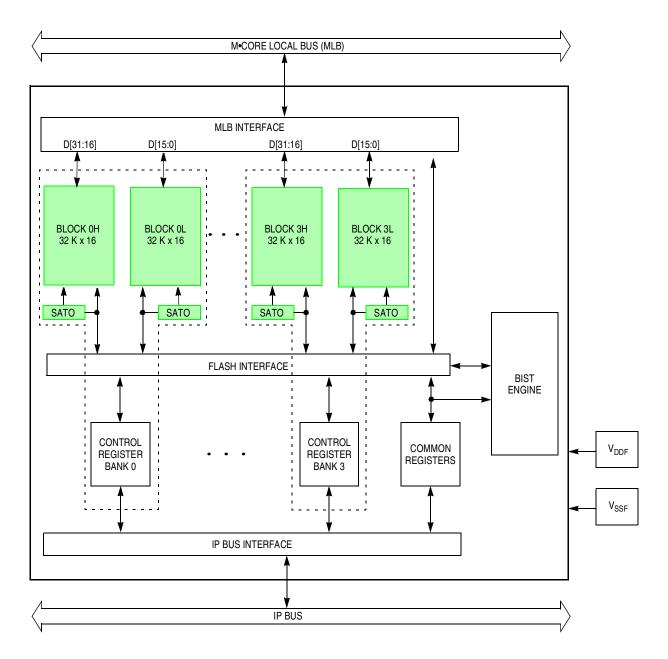

| 10.6               | Block Diagram20                                       |    |

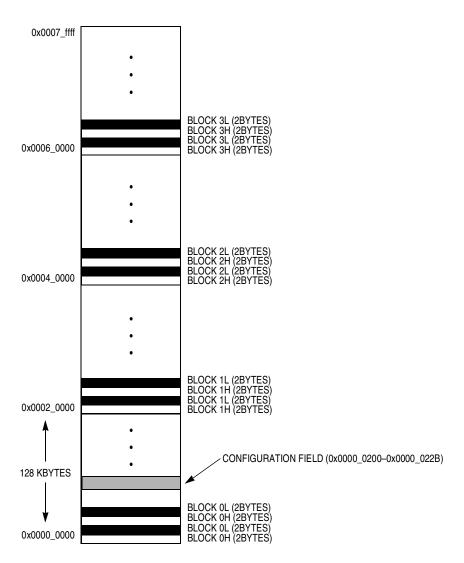

| 10.7               | Module Memory Map                                     |    |

| 10.7. <sup>2</sup> |                                                       |    |

| 10.7.              | 3, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1, 1,             |    |

| 10.7.              |                                                       |    |

| 10.7.              | _                                                     |    |

| 10.7.              |                                                       |    |

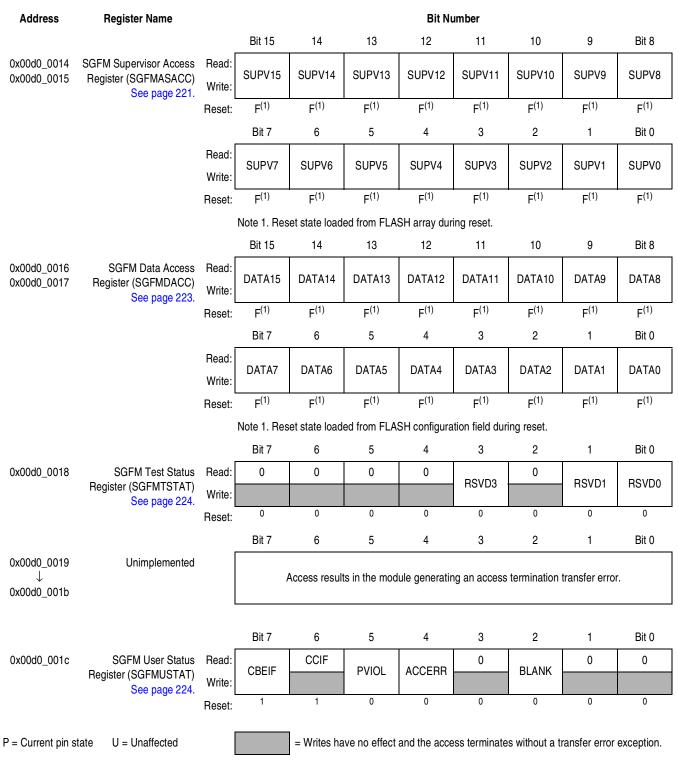

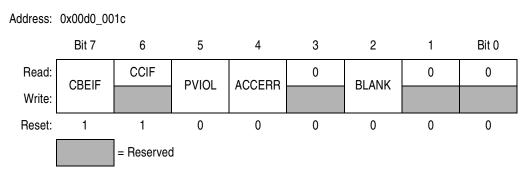

| 10.7.2             | 2 Banked Register Descriptions                        | 20 |

| 10.7.2             |                                                       |    |

| 10.7.2             |                                                       |    |

| 10.7.2             |                                                       |    |

| 10.7.2             | <b>5</b>                                              |    |

| 10.7.2             | <u> </u>                                              |    |

| 10.7.2             |                                                       |    |

| 10.7.2             | <b>5</b>                                              |    |

| 10.7.2             |                                                       |    |

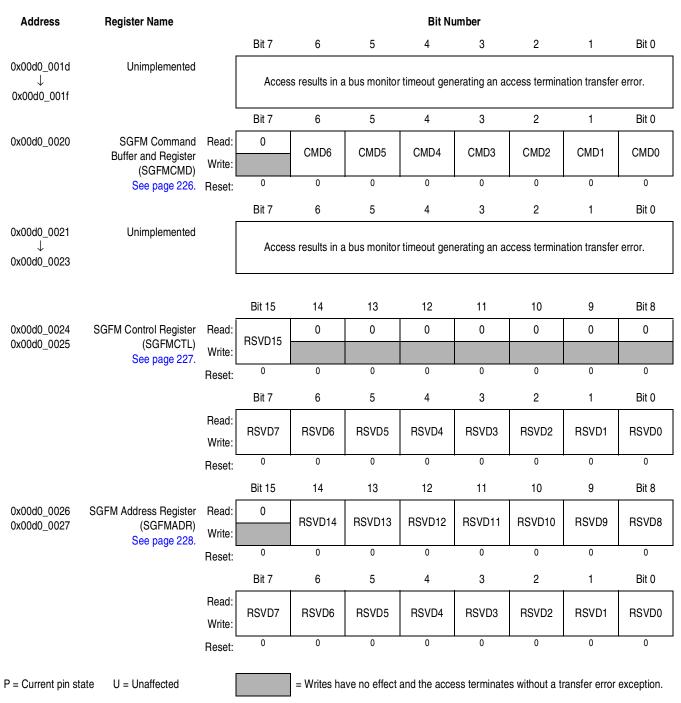

| 10.8 SGFM User Mode                                                                                                                                                                                                                                                                                                                                                                                                                          | 230                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 10.8.1 Read Operations                                                                                                                                                                                                                                                                                                                                                                                                                       | 230                                                                              |

| 10.8.2 Write Operations                                                                                                                                                                                                                                                                                                                                                                                                                      | 230                                                                              |

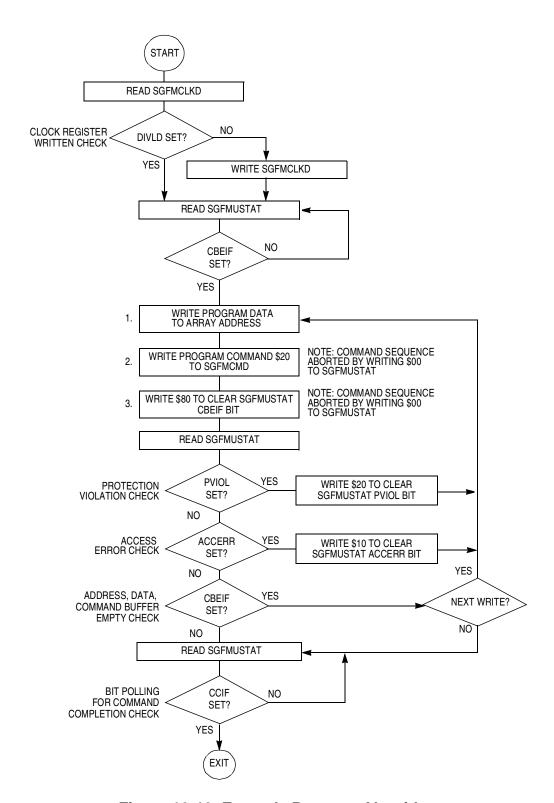

| 10.8.3 Program and Erase Operations                                                                                                                                                                                                                                                                                                                                                                                                          | 231                                                                              |

| 10.8.3.1 Setting the SGFMCLKD Register                                                                                                                                                                                                                                                                                                                                                                                                       | 231                                                                              |

| 10.8.3.2 Program, Erase, and Verify Sequences                                                                                                                                                                                                                                                                                                                                                                                                | 232                                                                              |

| 10.8.3.3 FLASH User Mode Valid Commands                                                                                                                                                                                                                                                                                                                                                                                                      | 234                                                                              |

| 10.8.3.4 FLASH User Mode Illegal Operations                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| 10.8.4 Stop Mode                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| 10.8.5 Master Mode                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

| 10.8.6 Emulation Mode                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| 10.8.7 Debug Mode                                                                                                                                                                                                                                                                                                                                                                                                                            | 238                                                                              |

| 10.9 FLASH Security Operation                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| 10.9.1 Back Door Access                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| 10.9.2 Erase Verify Check                                                                                                                                                                                                                                                                                                                                                                                                                    | 239                                                                              |

| 10.10 Resets                                                                                                                                                                                                                                                                                                                                                                                                                                 | 240                                                                              |

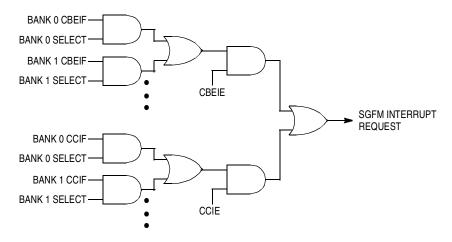

| 10.11 Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                             | 240                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| Section 11. Clock Module                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Section 11. Clock Module 11.1 Contents                                                                                                                                                                                                                                                                                                                                                                                                       | 243                                                                              |

| 11.1 Contents                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| 11.1 Contents       2         11.2 Introduction       2                                                                                                                                                                                                                                                                                                                                                                                      | 244                                                                              |

| 11.1 Contents       2         11.2 Introduction       2         11.3 Features       2                                                                                                                                                                                                                                                                                                                                                        | 244<br>244                                                                       |

| 11.1 Contents       2         11.2 Introduction       2         11.3 Features       2         11.4 Modes of Operation       2                                                                                                                                                                                                                                                                                                                | 244<br>244<br>245                                                                |

| 11.1 Contents       2         11.2 Introduction       2         11.3 Features       2         11.4 Modes of Operation       2         11.4.1 Normal PLL Mode       2                                                                                                                                                                                                                                                                         | 244<br>244<br>245<br>245                                                         |

| 11.1 Contents       2         11.2 Introduction       2         11.3 Features       2         11.4 Modes of Operation       2         11.4.1 Normal PLL Mode       2         11.4.2 1:1 PLL Mode       2                                                                                                                                                                                                                                     | 244<br>244<br>245<br>245<br>245                                                  |

| 11.1 Contents       2         11.2 Introduction       2         11.3 Features       2         11.4 Modes of Operation       2         11.4.1 Normal PLL Mode       2         11.4.2 1:1 PLL Mode       2         11.4.3 External Clock Mode       2                                                                                                                                                                                          | 244<br>244<br>245<br>245<br>245<br>245                                           |

| 11.1 Contents       2         11.2 Introduction       2         11.3 Features       2         11.4 Modes of Operation       2         11.4.1 Normal PLL Mode       2         11.4.2 1:1 PLL Mode       2         11.4.3 External Clock Mode       2         11.4.4 Low-Power Options       2                                                                                                                                                 | 244<br>245<br>245<br>245<br>245<br>245<br>245                                    |

| 11.1 Contents       2         11.2 Introduction       2         11.3 Features       2         11.4 Modes of Operation       2         11.4.1 Normal PLL Mode       2         11.4.2 1:1 PLL Mode       2         11.4.3 External Clock Mode       2         11.4.4 Low-Power Options       2         11.4.4.1 Wait and Doze Modes       2                                                                                                    | 244<br>245<br>245<br>245<br>245<br>245<br>245<br>245                             |

| 11.1 Contents       2         11.2 Introduction       2         11.3 Features       2         11.4 Modes of Operation       2         11.4.1 Normal PLL Mode       2         11.4.2 1:1 PLL Mode       2         11.4.3 External Clock Mode       2         11.4.4 Low-Power Options       2         11.4.4.1 Wait and Doze Modes       2         11.4.4.2 Stop Mode       2                                                                 | 244<br>245<br>245<br>245<br>245<br>245<br>245<br>246                             |

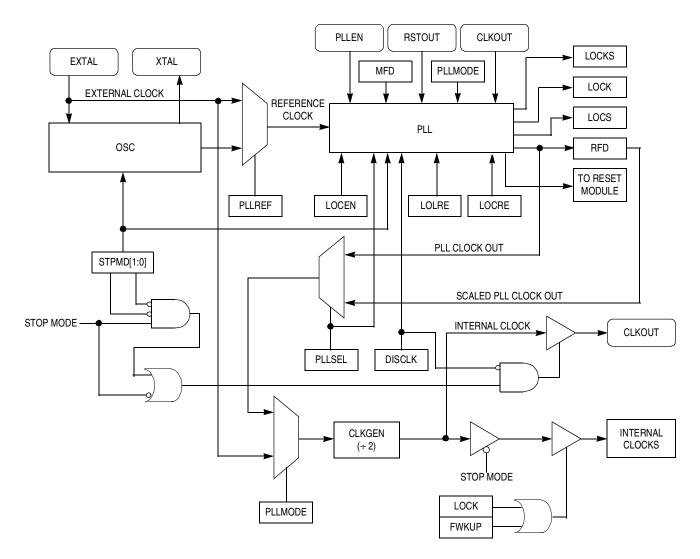

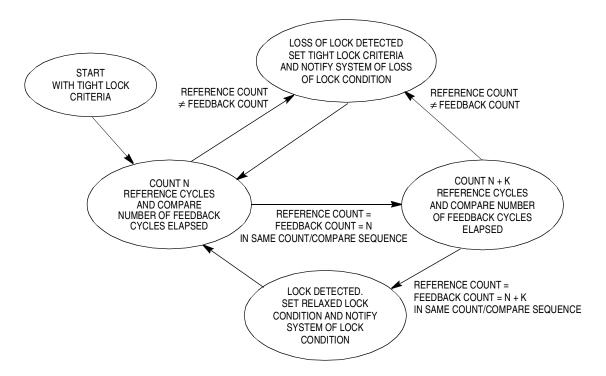

| 11.1 Contents       2         11.2 Introduction       2         11.3 Features       2         11.4 Modes of Operation       2         11.4.1 Normal PLL Mode       2         11.4.2 1:1 PLL Mode       2         11.4.3 External Clock Mode       2         11.4.4 Low-Power Options       2         11.4.4.1 Wait and Doze Modes       2         11.4.4.2 Stop Mode       2         11.5 Block Diagram       2                              | 244<br>244<br>245<br>245<br>245<br>245<br>245<br>245<br>246<br>247               |

| 11.1 Contents  11.2 Introduction  11.3 Features  11.4 Modes of Operation  11.4.1 Normal PLL Mode  11.4.2 1:1 PLL Mode  11.4.3 External Clock Mode  11.4.4 Low-Power Options  11.4.4.1 Wait and Doze Modes  11.4.2 Stop Mode  11.5 Block Diagram  11.6 Signal Descriptions                                                                                                                                                                    | 244<br>245<br>245<br>245<br>245<br>245<br>245<br>245<br>246<br>247               |

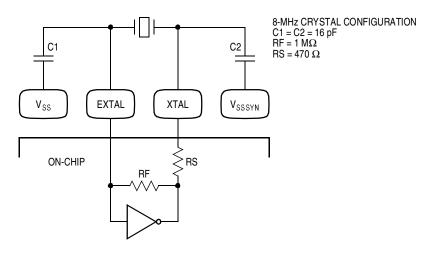

| 11.1 Contents111.2 Introduction111.3 Features111.4 Modes of Operation111.4.1 Normal PLL Mode111.4.2 1:1 PLL Mode111.4.3 External Clock Mode111.4.4 Low-Power Options111.4.4.1 Wait and Doze Modes111.4.4.2 Stop Mode111.5 Block Diagram111.6 Signal Descriptions111.6.1 EXTAL1                                                                                                                                                               | 244<br>245<br>245<br>245<br>245<br>245<br>245<br>246<br>247<br>248               |

| 11.1 Contents  11.2 Introduction  11.3 Features  11.4 Modes of Operation  11.4.1 Normal PLL Mode  11.4.2 1:1 PLL Mode  11.4.3 External Clock Mode  11.4.4 Low-Power Options  11.4.4.1 Wait and Doze Modes  11.4.2 Stop Mode  11.5 Block Diagram  11.6 Signal Descriptions  11.6.1 EXTAL  11.6.2 XTAL                                                                                                                                         | 244<br>245<br>245<br>245<br>245<br>245<br>245<br>246<br>247<br>248<br>248        |

| 11.1 Contents  11.2 Introduction  11.3 Features  11.4 Modes of Operation  11.4.1 Normal PLL Mode  11.4.2 1:1 PLL Mode  11.4.3 External Clock Mode  11.4.4 Low-Power Options  11.4.4.1 Wait and Doze Modes  11.4.2 Stop Mode  11.5 Block Diagram  11.6 Signal Descriptions  11.6.1 EXTAL  11.6.2 XTAL  11.6.3 CLKOUT                                                                                                                          | 244<br>245<br>245<br>245<br>245<br>245<br>245<br>246<br>247<br>248<br>248<br>248 |

| 11.1 Contents         11.2 Introduction         11.3 Features         11.4 Modes of Operation         11.4.1 Normal PLL Mode         11.4.2 1:1 PLL Mode         11.4.3 External Clock Mode         11.4.4 Low-Power Options         11.4.4.1 Wait and Doze Modes         11.4.4.2 Stop Mode         11.5 Block Diagram         11.6 Signal Descriptions         11.6.1 EXTAL         11.6.2 XTAL         11.6.3 CLKOUT         11.6.4 PLLEN | 244<br>245<br>245<br>245<br>245<br>245<br>245<br>246<br>247<br>248<br>248<br>248 |

| 11.1 Contents  11.2 Introduction  11.3 Features  11.4 Modes of Operation  11.4.1 Normal PLL Mode  11.4.2 1:1 PLL Mode  11.4.3 External Clock Mode  11.4.4 Low-Power Options  11.4.4.1 Wait and Doze Modes  11.4.2 Stop Mode  11.5 Block Diagram  11.6 Signal Descriptions  11.6.1 EXTAL  11.6.2 XTAL  11.6.3 CLKOUT                                                                                                                          | 244<br>245<br>245<br>245<br>245<br>245<br>245<br>246<br>247<br>248<br>248<br>248 |

14

| 11.7 Memory Map and Registers                | 249 |

|----------------------------------------------|-----|

| 11.7.1 Module Memory Map                     | 249 |

| 11.7.2 Register Descriptions                 | 250 |

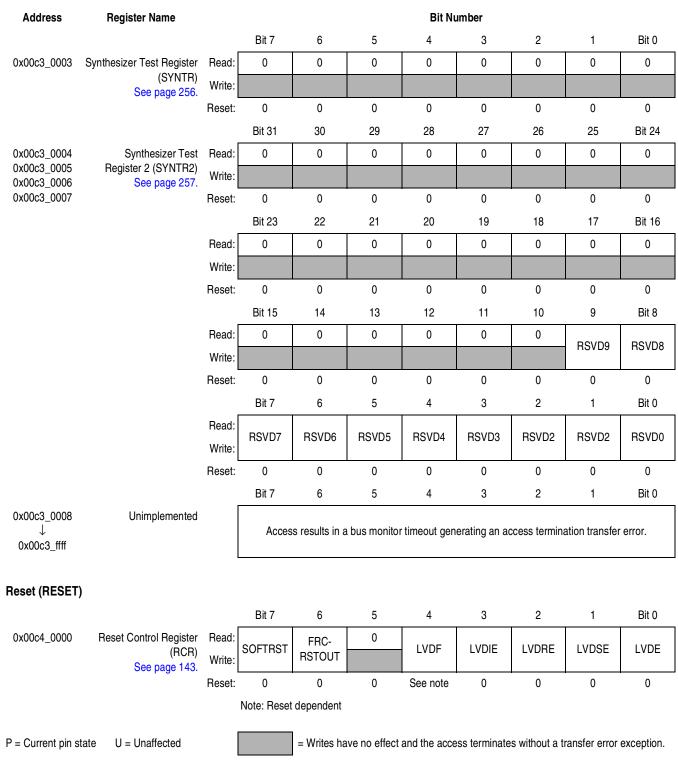

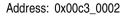

| 11.7.2.1 Synthesizer Control Register        | 250 |

| 11.7.2.2 Synthesizer Status Register         | 253 |

| 11.7.2.3 Synthesizer Test Register           | 256 |

| 11.7.2.4 Synthesizer Test Register 2         | 257 |

| 11.8 Functional Description                  | 258 |

| 11.8.1 System Clock Modes                    | 258 |

| 11.8.2 System Clocks Generation              | 259 |

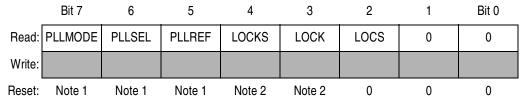

| 11.8.3 PLL Lock Detection                    | 259 |

| 11.8.3.1 PLL Loss of Lock Conditions         | 261 |

| 11.8.3.2 PLL Loss of Lock Reset              | 261 |

| 11.8.4 Loss of Clock Detection               | 261 |

| 11.8.4.1 Alternate Clock Selection           | 262 |

| 11.8.4.2 Loss-of-Clock Reset                 | 265 |

| 11.8.5 Clock Operation During Reset          |     |

| 11.8.6 PLL Operation                         |     |

| 11.8.6.1 Phase and Frequency Detector (PFD)  | 268 |

| 11.8.6.2 Charge Pump/Loop Filter             |     |

| 11.8.6.3 Voltage Control Output (VCO)        |     |

| 11.8.6.4 Multiplication Factor Divider (MFD) | 269 |

| 11.9 Reset                                   | 269 |

| 11.10 Interrupts                             | 269 |

|                                              |     |

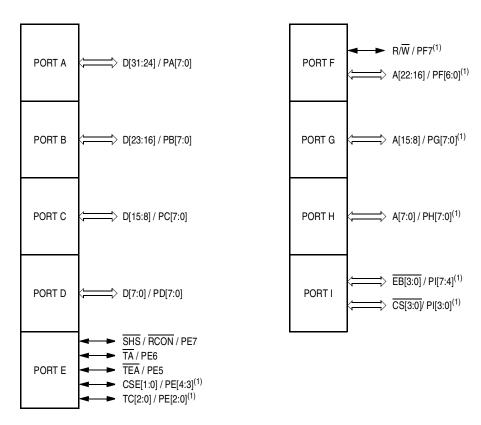

| Section 12. Ports Module                     |     |

| 12.1 Contents                                | 271 |

| 12.2 Introduction                            | 272 |

| 12.3 Signals                                 | 273 |

| 12.4 Memory Map and Registers                | 273 |

| 12.4.1 Memory Map                            |     |

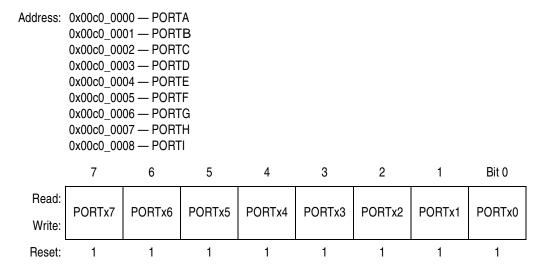

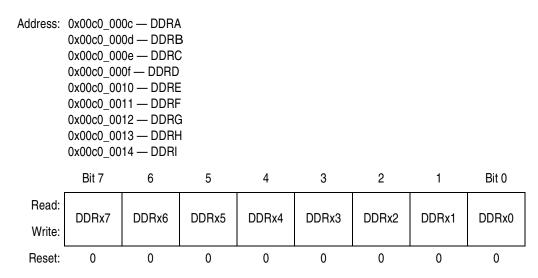

| 12.4.2 Register Descriptions                 |     |

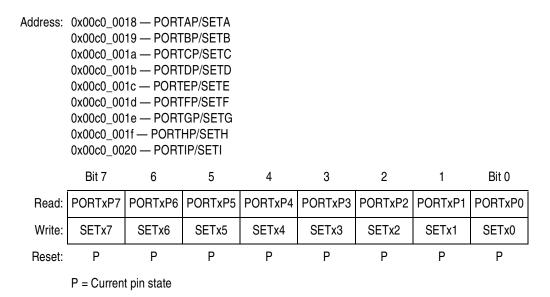

| 12.4.2.1 Port Output Data Registers          |     |

| 12.4.2.2 Port Data Direction Registers       |     |

| 12.4.2.3 Port Pin Data/Set Data Registers    |     |

| 12.4.2.4 Port Clear Output Data Registers    |     |

| 12.4.2.5 Port C/D Pin Assignment Register279        |

|-----------------------------------------------------|

| 12.4.2.6 Port E Pin Assignment Register280          |

| 12.5 Functional Description                         |

| 12.5.1 Pin Functions                                |

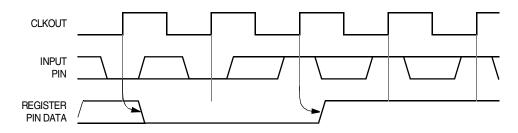

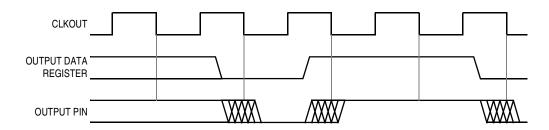

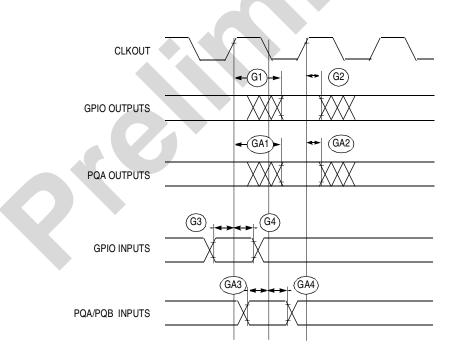

| 12.5.2 Port Digital I/O Timing283                   |

| 12.6 Interrupts                                     |

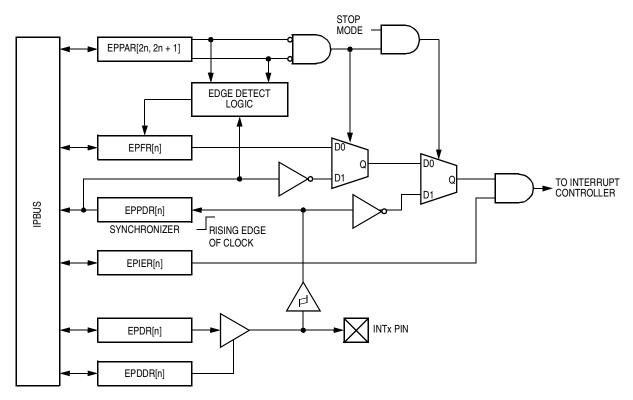

| Section 13. Edge Port Module (EPORT)                |

| 13.1 Contents                                       |

| 13.2 Introduction                                   |

| 13.3 Low-Power Mode Operation                       |

| 13.3.1 Wait and Doze Modes                          |

| 13.3.2 Stop Mode                                    |

| 13.4 Interrupt/General-Purpose I/O Pin Descriptions |

| 13.5 Memory Map and Registers                       |

| 13.5.1 Memory Map                                   |

| 13.5.2 Registers                                    |

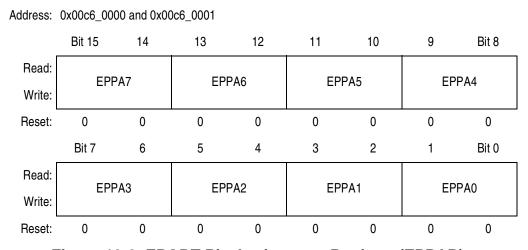

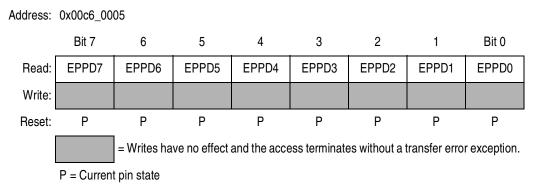

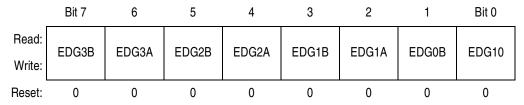

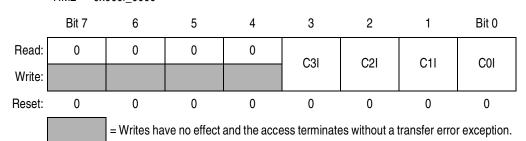

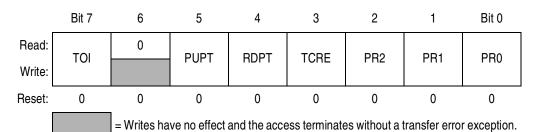

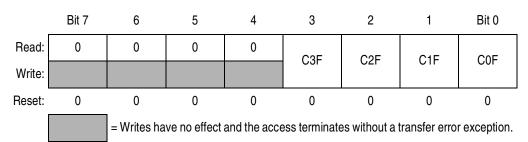

| 13.5.2.1 EPORT Pin Assignment Register              |

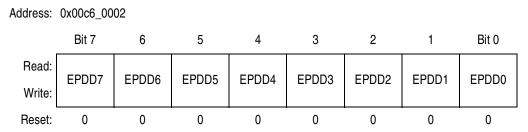

| 13.5.2.2 EPORT Data Direction Register              |

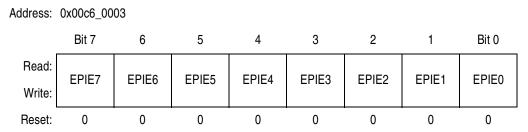

| 13.5.2.3 Edge Port Interrupt Enable Register        |

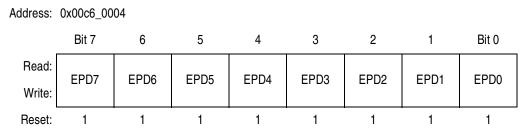

| 13.5.2.4 Edge Port Data Register                    |

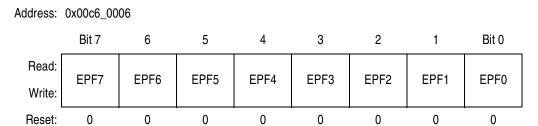

| 13.5.2.6 Edge Port Flag Register                    |

| 10.0.2.0 Eage Fort Flag Register                    |

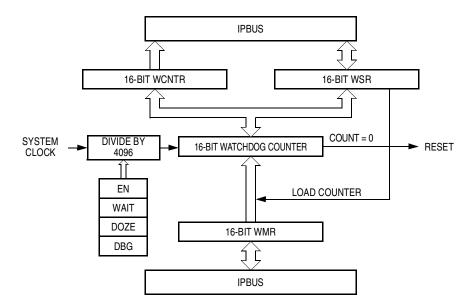

| Section 14. Watchdog Timer Module                   |

| 14.1 Contents                                       |

| 14.2 Introduction                                   |

| 14.3 Modes of Operation                             |

| 14.3.1 Wait Mode                                    |

| 14.3.2 Doze Mode                                    |

| 14.3.3 Stop Mode                                    |

| 14.3.4 Debug Mode                                   |

| 14.4 Block Diagram                                  |

| 14.5 Signals                                        |

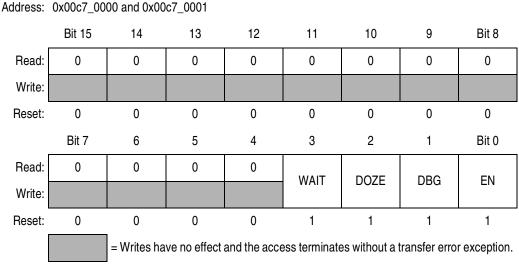

| 14.6 Memory Map and Registers                       |

| MMC2114 • MMC2113 • MMC2112 — Rev. 1 (              |

| 14.6.1           | Memory Map                                                        |

|------------------|-------------------------------------------------------------------|

| 14.6.2           | Registers                                                         |

| 14.6.2           | 3                                                                 |

| 14.6.2           | 3                                                                 |

| 14.6.2           | 3 3                                                               |

| 14.6.2           | 4 Watchdog Service Register                                       |

| Se               | ction 15. Programmable Interrupt Timer Modules<br>(PIT1 and PIT2) |

| 15.1             | ,                                                                 |

|                  | Contents                                                          |

| 15.2             | Introduction306                                                   |

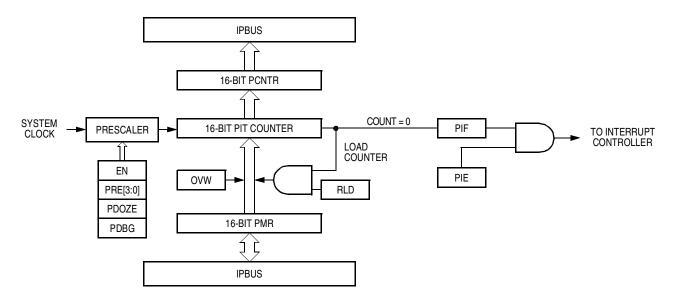

| 15.3             | Block Diagram306                                                  |

| 15.4             | Modes of Operation                                                |

| 15.4.1           | Wait Mode                                                         |

| 15.4.2           | Doze Mode                                                         |

| 15.4.3           | Stop Mode                                                         |

| 15.4.4           | Debug Mode                                                        |

| 15.5             | Signals                                                           |

| 15.6             | Memory Map and Registers                                          |

| 15.6.1           | Memory Map                                                        |

| 15.6.2           | Registers                                                         |

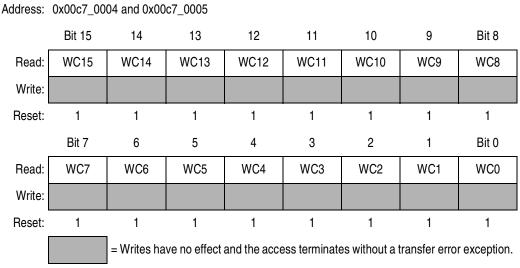

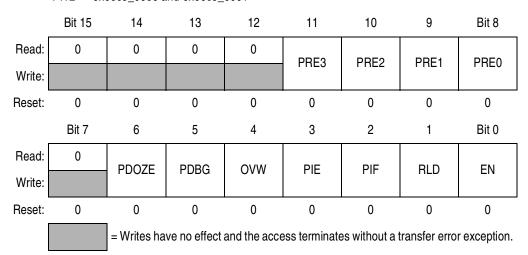

| 15.6.2           | <b>5</b>                                                          |

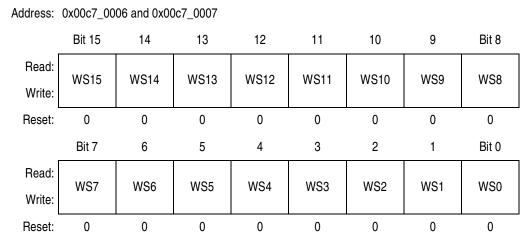

| 15.6.2<br>15.6.2 | 9                                                                 |

|                  | S .                                                               |

| 15.7.1           | Functional Description                                            |

| 15.7.1           |                                                                   |

| 15.7.3           | Timeout Specifications                                            |

|                  | Interrupt Operation                                               |

| 13.0             | interrupt Operation                                               |

|                  | Section 16. Timer Modules (TIM1 and TIM2)                         |

| 16.1             | Contents                                                          |

| 16.2             | Introduction                                                      |

| 16.3             | Features                                                          |

|                  |                                                                   |

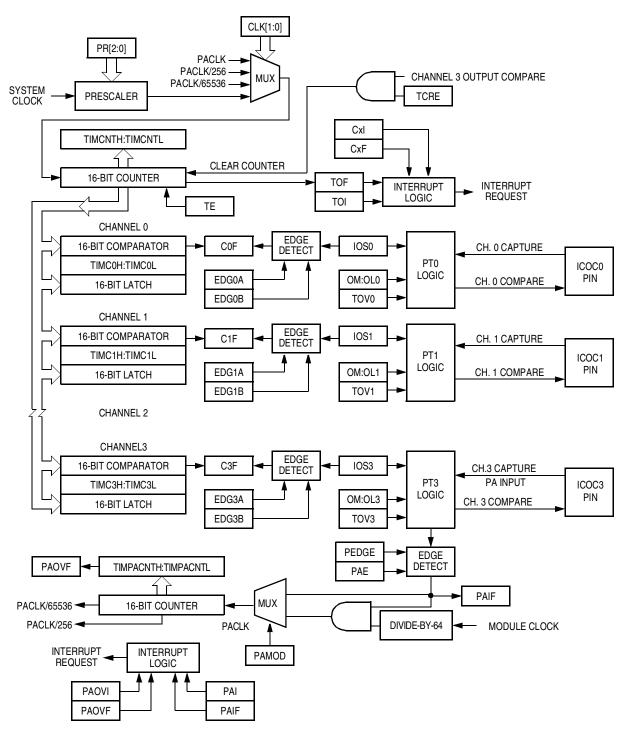

| 16.4             | Block Diagram320                                                  |

| 16.5 M   | odes of Operation                                    | 321 |

|----------|------------------------------------------------------|-----|

| 16.5.1   | Supervisor and User Modes                            | 321 |

| 16.5.2   | Run Mode                                             | 321 |

| 16.5.3   | Stop Mode                                            | 321 |

| 16.5.4   | Wait, Doze, and Debug Modes                          | 321 |

| 16.5.5   | Test Mode                                            | 322 |

| 16.6 Si  | gnal Description                                     | 322 |

| 16.6.1   | ICOC[2:0]                                            | 322 |

| 16.6.2   | ICOC3                                                | 322 |

| 16.7 M   | emory Map and Registers                              | 323 |

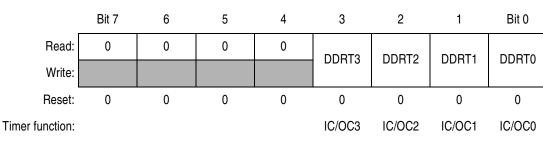

| 16.7.1   | Timer Input Capture/Output Compare Select Register . | 324 |

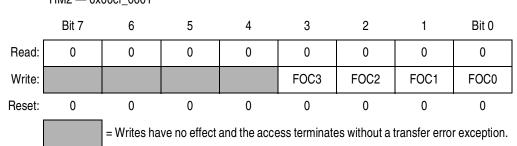

| 16.7.2   | Timer Compare Force Register                         | 325 |

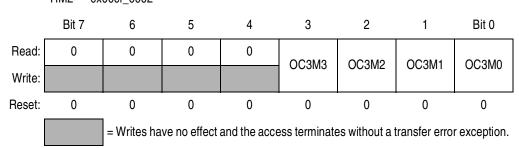

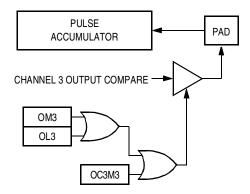

| 16.7.3   | Timer Output Compare 3 Mask Register                 | 326 |

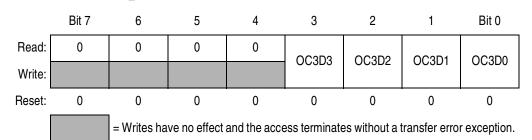

| 16.7.4   | Timer Output Compare 3 Data Register                 | 327 |

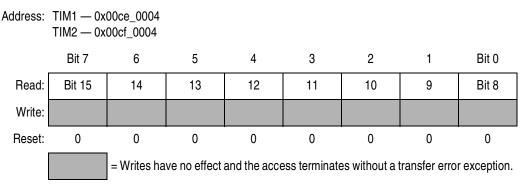

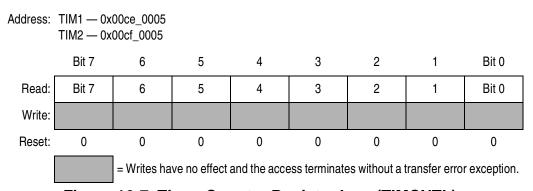

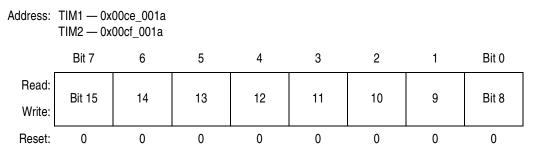

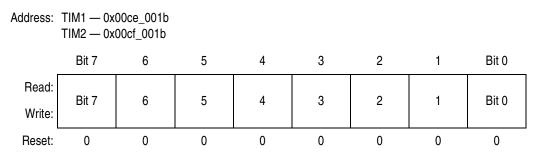

| 16.7.5   | Timer Counter Registers                              | 328 |

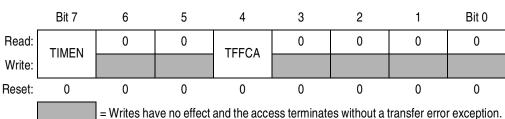

| 16.7.6   | Timer System Control Register 1                      | 329 |

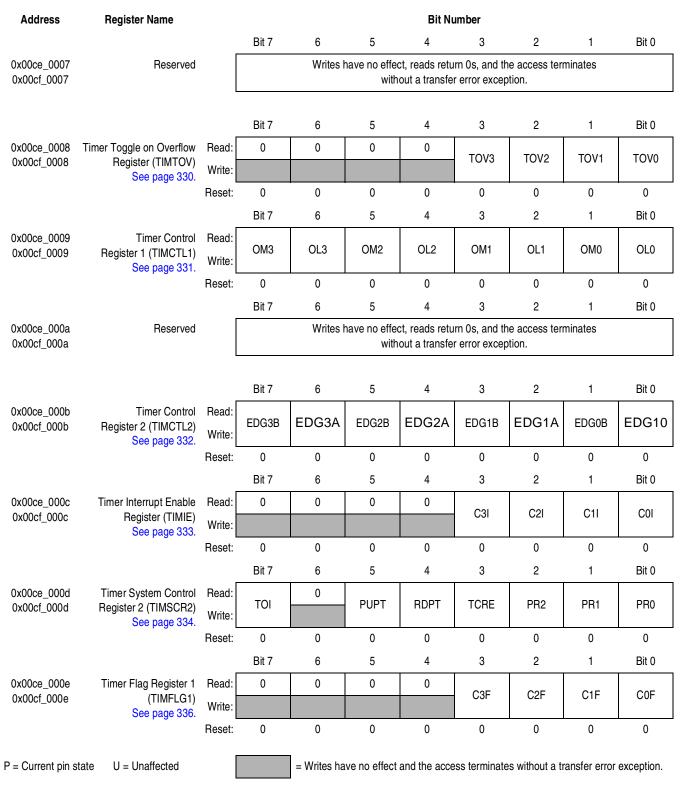

| 16.7.7   | Timer Toggle-On-Overflow Register                    | 330 |

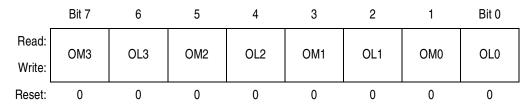

| 16.7.8   | Timer Control Register 1                             | 331 |

| 16.7.9   | Timer Control Register 2                             | 332 |

| 16.7.10  | Timer Interrupt Enable Register                      | 333 |

| 16.7.11  | Timer System Control Register 2                      | 334 |

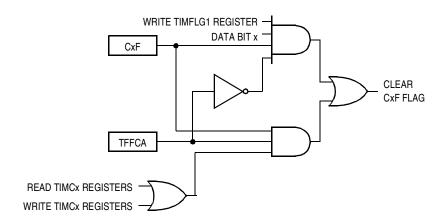

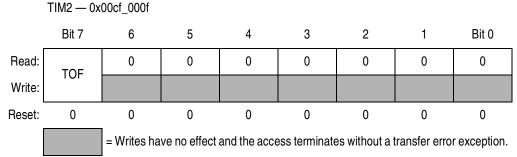

| 16.7.12  | Timer Flag Register 1                                | 336 |

| 16.7.13  | Timer Flag Register 2                                | 337 |

| 16.7.14  | Timer Channel Registers                              | 338 |

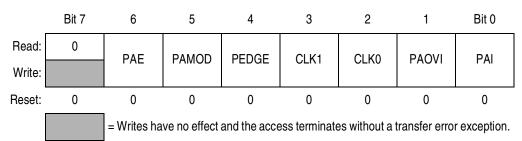

| 16.7.15  | Pulse Accumulator Control Register                   | 339 |

| 16.7.16  | Pulse Accumulator Flag Register                      | 341 |

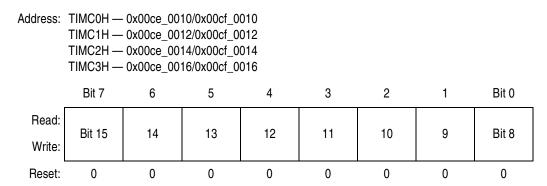

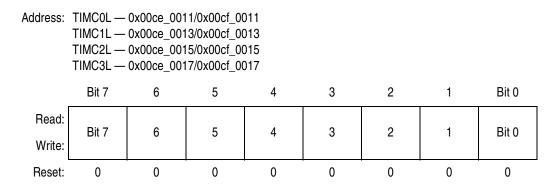

| 16.7.17  | Pulse Accumulator Counter Registers                  | 342 |

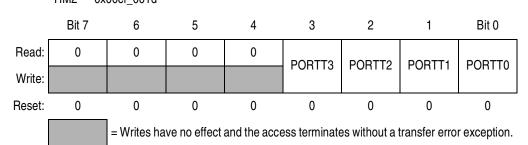

| 16.7.18  | Timer Port Data Register                             | 343 |

| 16.7.19  | Timer Port Data Direction Register                   | 344 |

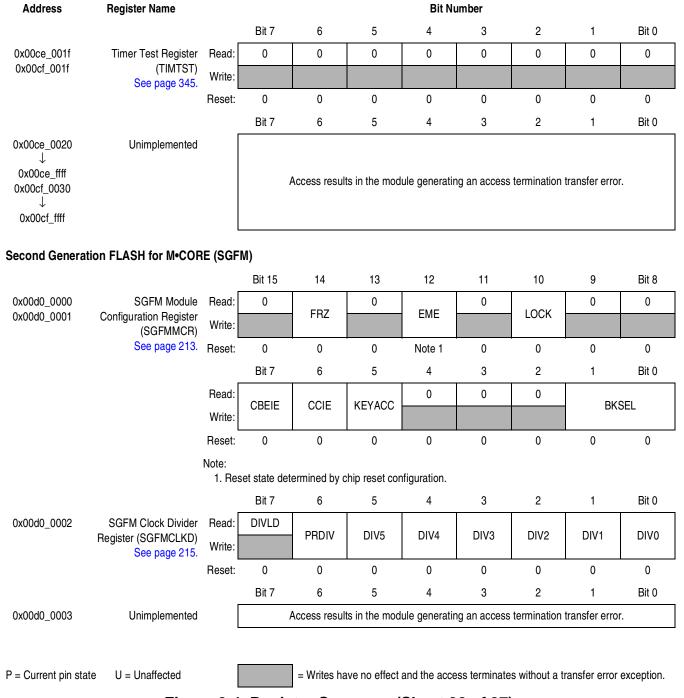

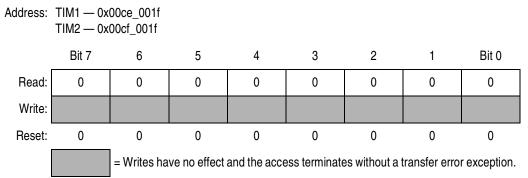

| 16.7.20  | Timer Test Register                                  | 345 |

| 16.8 Fu  | unctional Description                                | 345 |

| 16.8.1   | Prescaler                                            | 345 |

| 16.8.2   | Input Capture                                        | 345 |

| 16.8.3   | Output Compare                                       | 346 |

| 16.8.4   | Pulse Accumulator                                    | 347 |

| 16.8.4.1 | Event Counter Mode                                   | 347 |

| 16.8.4.2 | Gated Time Accumulation Mode                         | 348 |

Advance Information

18

| 16.8.5 General-Purpose I/O Ports                    |

|-----------------------------------------------------|

| 16.9 Reset                                          |

| 16.10 Interrupts351                                 |

| 16.10.1 Timer Channel Interrupts (CxF)              |

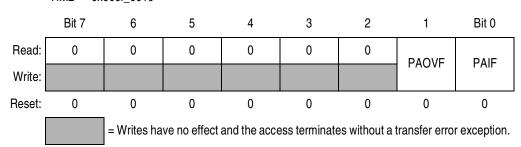

| 16.10.2 Pulse Accumulator Overflow (PAOVF)352       |

| 16.10.3 Pulse Accumulator Input (PAIF)352           |

| 16.10.4 Timer Overflow (TOF)                        |

| Section 17. Serial Communications Interface Modules |

| (SCI1 and SCI2)                                     |

| 17.1 Contents                                       |

| 17.2 Introduction                                   |

| 17.3 Features                                       |

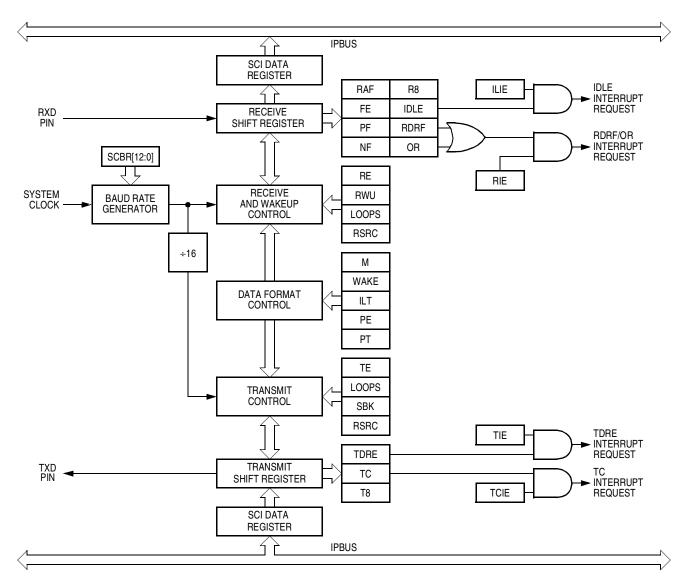

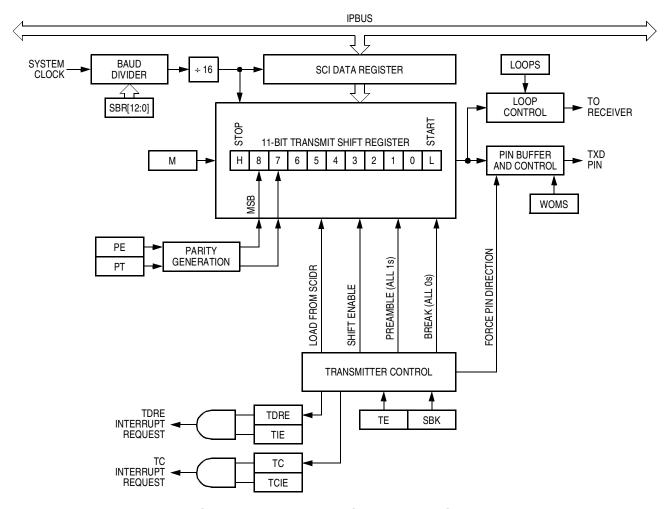

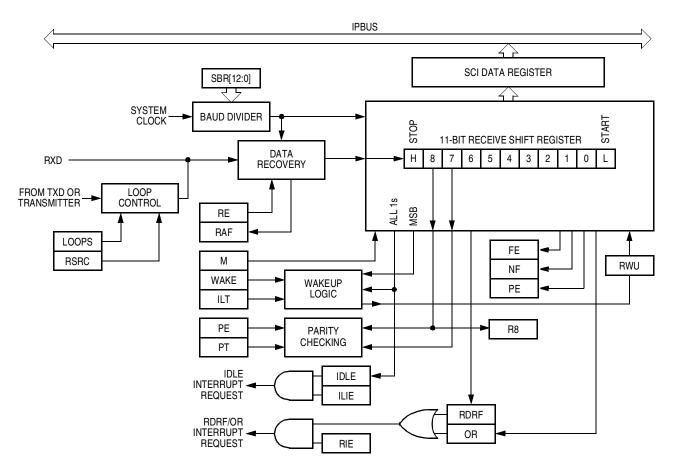

| 17.4 Block Diagram                                  |

| 17.5 Modes of Operation                             |

| 17.5.1 Doze Mode357                                 |

| 17.5.2 Stop Mode                                    |

| 17.6 Signal Description358                          |

| 17.6.1 RXD                                          |

| 17.6.2 TXD                                          |

| 17.7 Memory Map and Registers                       |

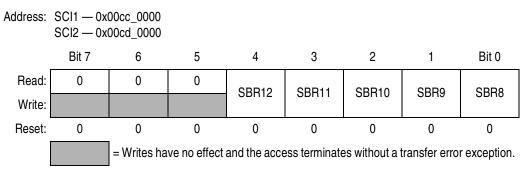

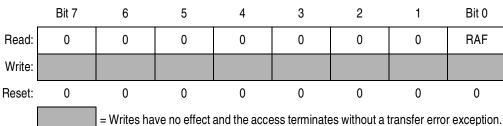

| 17.7.1 SCI Baud Rate Registers                      |

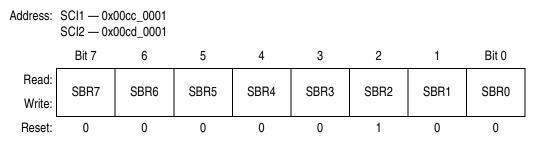

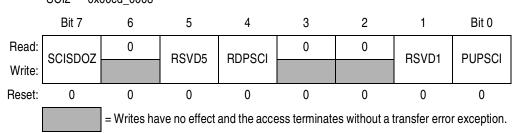

| 17.7.2 SCI Control Register 1                       |

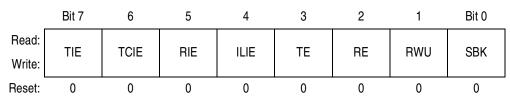

| 17.7.3 SCI Control Register 2                       |

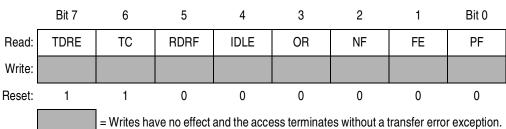

| 17.7.4 SCI Status Register 1                        |

| 17.7.5       SCI Status Register 2                  |

| 17.7.7 SCI Pullup and Reduced Drive Register        |

| 17.7.8 SCI Port Data Register                       |

| 17.7.9 SCI Data Direction Register                  |

| 17.8 Functional Description                         |

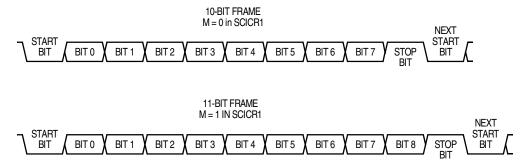

| 17.9 Data Format                                    |

| 17.10 Baud Rate Generation                          |

| 17.11 Transmitter                                   |

| 17.11.1 Frame Length                                |

|                                                     |

| 17.11.2 Transmitting a Frame                         |

|------------------------------------------------------|

| 17.11.3 Break Frames380                              |

| 17.11.4 Idle Frames                                  |

| 17.12 Receiver                                       |

| 17.12.1 Frame Length                                 |

| 17.12.2 Receiving a Frame                            |

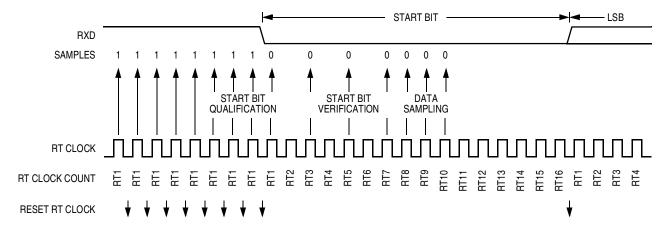

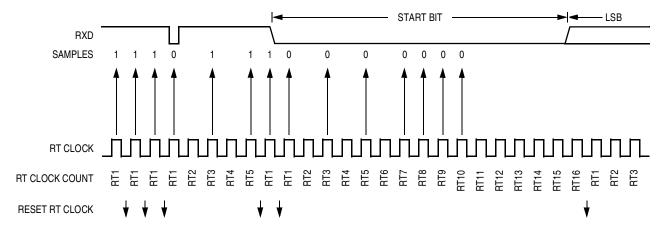

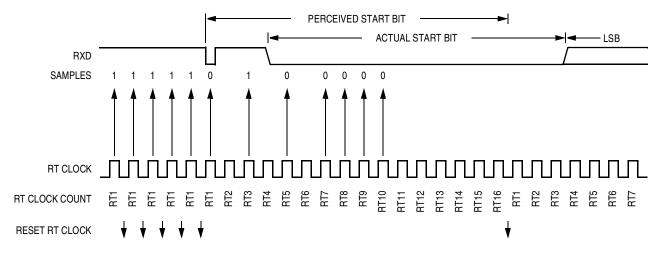

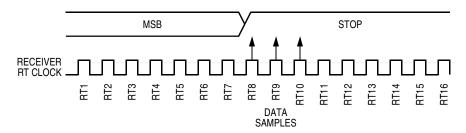

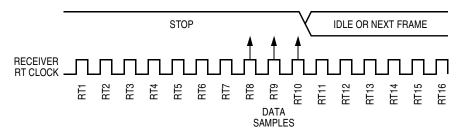

| 17.12.3 Data Sampling                                |

| 17.12.4 Framing Errors                               |

| 17.12.5 Baud Rate Tolerance                          |

| 17.12.5.1 Slow Data Tolerance                        |

| 17.12.5.2 Fast Data Tolerance                        |

| 17.12.6 Receiver Wakeup                              |

| 17.12.6.1 Idle Input Line Wakeup (WAKE = 0)          |

|                                                      |

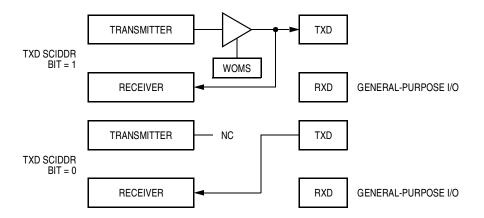

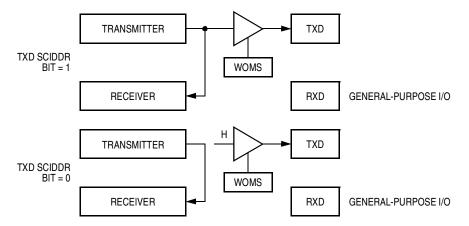

| 17.13 Single-Wire Operation                          |

| 17.14 Loop Operation393                              |

| 17.15 I/O Ports                                      |

| 17.16 Reset                                          |

| 17.17 Interrupts395                                  |

| 17.17.1 Transmit Data Register Empty                 |

| 17.17.2 Transmission Complete                        |

| 17.17.3 Receive Data Register Full396                |

| 17.17.4 Idle Receiver Input                          |

| 17.17.5 Overrun                                      |

|                                                      |

| Section 18. Serial Peripheral Interface Module (SPI) |

| 18.1 Contents                                        |

| 18.2 Introduction                                    |

| 18.3 Features                                        |

| 18.4 Modes of Operation                              |

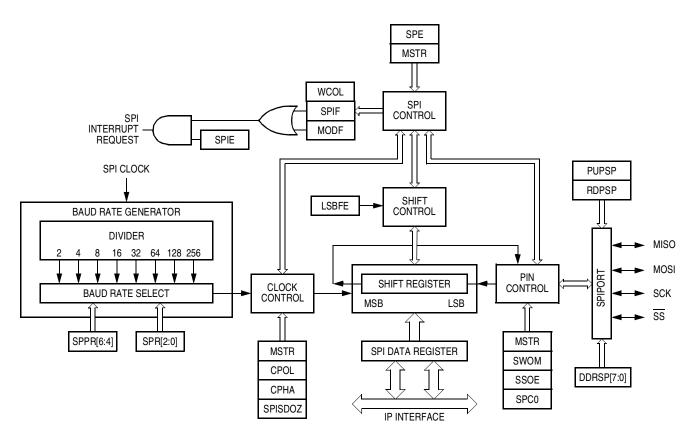

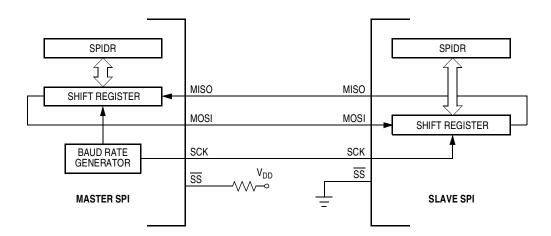

| 18.5 Block Diagram                                   |

| 18.6 Signal Description                              |

| 18.6.1 MISO (Master In/Slave Out)                    |

| 18.6.2 MOSI (Master Out/Slave In)                    |

| 18.6.3 SCK (Serial Clock)                            |

| 18.6.4 SS (Slave Select)                             |

|                                                      |

| MMC2114 • MMC2113 • MMC2112 — Rev. 1.0               |

| 18.7.2       SPI Control Register 2       405         18.7.3       SPI Baud Rate Register       406         18.7.4       SPI Status Register       408         18.7.5       SPI Data Register       409         18.7.6       SPI Pullup and Reduced Drive Register       410         18.7.7       SPI Port Data Register       411         18.7.8       SPI Port Data Direction Register       412         18.8       Functional Description       413         18.8.1       Master Mode       414         18.8.2       Slave Mode       415         18.8.3       Transmission Formats       416         18.8.3.1       Transfer Format When CPHA = 1       416         18.8.3.2       Transfer Format When CPHA = 0       417         18.8.4       SPI Baud Rate Generation       420         18.8.5       Slave-Select Output       420         18.8.6       Bidirectional Mode       421         18.8.7       Error Conditions       422         18.8.7.1       Write Collision Error       422         18.8.8.2       Doze Mode       423         18.8.8.3       Stop Mode       424         18.9       Reset       424                                                                           | 18.7 Memory Map and Registers                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

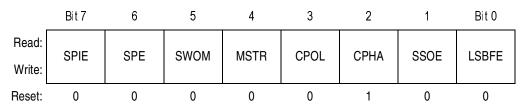

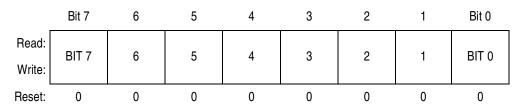

| 18.7.3       SPI Baud Rate Register       406         18.7.4       SPI Status Register       408         18.7.5       SPI Data Register       409         18.7.6       SPI Pullup and Reduced Drive Register       410         18.7.7       SPI Port Data Register       411         18.7.8       SPI Port Data Direction Register       412         18.8       Functional Description       413         18.8.1       Master Mode       414         18.8.2       Slave Mode       415         18.8.3       Transmission Formats       416         18.8.3.1       Transfer Format When CPHA = 1       416         18.8.3.2       Transfer Format When CPHA = 0       417         18.8.4       SPI Baud Rate Generation       420         18.8.5       Slave-Select Output       420         18.8.6       Bidirectional Mode       421         18.8.7       Error Conditions       422         18.8.7.1       Write Collision Error       422         18.8.8.2       Doze Mode       423         18.8.8.3       Stop Mode       423         18.8.8.3       Stop Mode       424         18.9       Reset       424         18.10.1 <td>18.7.1 SPI Control Register 1</td>                               | 18.7.1 SPI Control Register 1                                                                  |

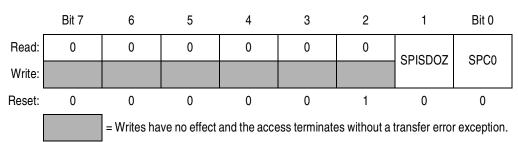

| 18.7.4       SPI Status Register       408         18.7.5       SPI Data Register       409         18.7.6       SPI Pullup and Reduced Drive Register       410         18.7.7       SPI Port Data Register       411         18.7.8       SPI Port Data Direction Register       412         18.8       Functional Description       413         18.8.1       Master Mode       414         18.8.2       Slave Mode       415         18.8.3       Transmission Formats       416         18.8.3.1       Transfer Format When CPHA = 1       416         18.8.3.2       Transfer Format When CPHA = 0       417         18.8.4       SPI Baud Rate Generation       420         18.8.5       Slave-Select Output       420         18.8.6       Bidirectional Mode       421         18.8.7       Error Conditions       422         18.8.7.1       Write Collision Error       422         18.8.8       Low-Power Mode Options       423         18.8.8.1       Run Mode       423         18.8.8.2       Doze Mode       424         18.9       Reset       424         18.10       Interrupts       424         18.10.1                                                                         | 18.7.2 SPI Control Register 2                                                                  |

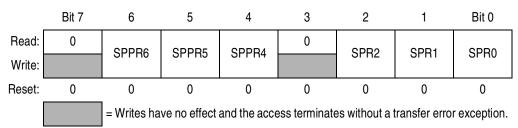

| 18.7.5       SPI Data Register.       409         18.7.6       SPI Pullup and Reduced Drive Register       410         18.7.7       SPI Port Data Register.       411         18.7.8       SPI Port Data Direction Register       412         18.8       Functional Description       413         18.8.1       Master Mode       414         18.8.2       Slave Mode       415         18.8.3       Transmission Formats       416         18.8.3.1       Transfer Format When CPHA = 1       416         18.8.3.2       Transfer Format When CPHA = 0       417         18.8.4       SPI Baud Rate Generation       420         18.8.5       Slave-Select Output       420         18.8.6       Bidirectional Mode       421         18.8.7       Error Conditions       422         18.8.7.1       Write Collision Error       422         18.8.7.2       Mode Fault Error       422         18.8.8.3       Low-Power Mode Options       423         18.8.8.2       Doze Mode       423         18.8.8.3       Stop Mode       424         18.9       Reset       424         18.10.1       Mode Fault (MODF) Flag       424                                                                       | 18.7.3 SPI Baud Rate Register                                                                  |

| 18.7.6       SPI Pullup and Reduced Drive Register       .410         18.7.7       SPI Port Data Register       .411         18.7.8       SPI Port Data Direction Register       .412         18.8       Functional Description       .413         18.8.1       Master Mode       .414         18.8.2       Slave Mode       .415         18.8.3.1       Transmission Formats       .416         18.8.3.2       Transfer Format When CPHA = 1       .416         18.8.3.2       Transfer Format When CPHA = 0       .417         18.8.4       SPI Baud Rate Generation       .420         18.8.5       Slave-Select Output       .420         18.8.6       Bidirectional Mode       .421         18.8.7       Error Conditions       .422         18.8.7.1       Write Collision Error       .422         18.8.7.2       Mode Fault Error       .422         18.8.8.3       Low-Power Mode Options       .423         18.8.8.1       Run Mode       .423         18.8.8.2       Doze Mode       .424         18.9       Reset       .424         18.10.1       Mode Fault (MODF) Flag       .424         18.10.2       SPI Interrupt Flag (SPIF)       .424 </td <td>18.7.4 SPI Status Register</td> | 18.7.4 SPI Status Register                                                                     |

| 18.7.7       SPI Port Data Register       .411         18.7.8       SPI Port Data Direction Register       .412         18.8       Functional Description       .413         18.8.1       Master Mode       .414         18.8.2       Slave Mode       .415         18.8.3.1       Transmission Formats       .416         18.8.3.2       Transfer Format When CPHA = 1       .416         18.8.3.2       Transfer Format When CPHA = 0       .417         18.8.4       SPI Baud Rate Generation       .420         18.8.5       Slave-Select Output       .420         18.8.6       Bidirectional Mode       .421         18.8.7       Error Conditions       .422         18.8.7.1       Write Collision Error       .422         18.8.7.2       Mode Fault Error       .422         18.8.8.1       Run Mode       .423         18.8.8.2       Doze Mode       .423         18.8.8.3       Stop Mode       .424         18.9       Reset       .424         18.10.1       Mode Fault (MODF) Flag       .424         18.10.2       SPI Interrupt Flag (SPIF)       .424                                                                                                                             | 18.7.5 SPI Data Register                                                                       |

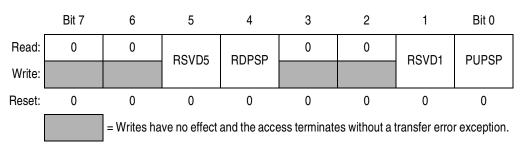

| 18.7.8       SPI Port Data Direction Register       .412         18.8       Functional Description       .413         18.8.1       Master Mode       .414         18.8.2       Slave Mode       .415         18.8.3.1       Transmission Formats       .416         18.8.3.2       Transfer Format When CPHA = 1       .416         18.8.3.2       Transfer Format When CPHA = 0       .417         18.8.4       SPI Baud Rate Generation       .420         18.8.5       Slave-Select Output       .420         18.8.6       Bidirectional Mode       .421         18.8.7       Error Conditions       .422         18.8.7.1       Write Collision Error       .422         18.8.8.7       Mode Fault Error       .422         18.8.8       Low-Power Mode Options       .423         18.8.8.2       Doze Mode       .423         18.8.8.3       Stop Mode       .424         18.10       Interrupts       .424         18.10.1       Mode Fault (MODF) Flag       .424         18.10.2       SPI Interrupt Flag (SPIF)       .424                                                                                                                                                                  | 18.7.6 SPI Pullup and Reduced Drive Register                                                   |

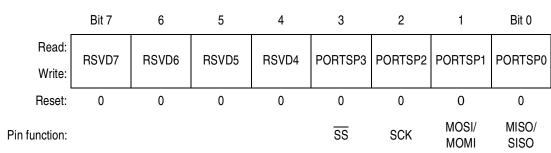

| 18.8 Functional Description       413         18.8.1 Master Mode       414         18.8.2 Slave Mode       415         18.8.3 Transmission Formats       416         18.8.3.1 Transfer Format When CPHA = 1       416         18.8.3.2 Transfer Format When CPHA = 0       417         18.8.4 SPI Baud Rate Generation       420         18.8.5 Slave-Select Output       420         18.8.6 Bidirectional Mode       421         18.8.7 Error Conditions       422         18.8.7.1 Write Collision Error       422         18.8.7.2 Mode Fault Error       422         18.8.8 Low-Power Mode Options       423         18.8.8.1 Run Mode       423         18.8.8.2 Doze Mode       424         18.9 Reset       424         18.10 Interrupts       424         18.10.1 Mode Fault (MODF) Flag       424         18.10.2 SPI Interrupt Flag (SPIF)       424                                                                                                                                                                                                                                                                                                                                       | 18.7.7 SPI Port Data Register                                                                  |

| 18.8.1       Master Mode       .414         18.8.2       Slave Mode       .415         18.8.3       Transmission Formats       .416         18.8.3.1       Transfer Format When CPHA = 1       .416         18.8.3.2       Transfer Format When CPHA = 0       .417         18.8.4       SPI Baud Rate Generation       .420         18.8.5       Slave-Select Output       .420         18.8.6       Bidirectional Mode       .421         18.8.7       Error Conditions       .422         18.8.7.1       Write Collision Error       .422         18.8.7.2       Mode Fault Error       .422         18.8.8       Low-Power Mode Options       .423         18.8.8.1       Run Mode       .423         18.8.8.2       Doze Mode       .423         18.8.8.3       Stop Mode       .424         18.10       Interrupts       .424         18.10.1       Mode Fault (MODF) Flag       .424         18.10.2       SPI Interrupt Flag (SPIF)       .424                                                                                                                                                                                                                                               | 18.7.8 SPI Port Data Direction Register                                                        |

| 18.8.2       Slave Mode       .415         18.8.3       Transmission Formats       .416         18.8.3.1       Transfer Format When CPHA = 1       .416         18.8.3.2       Transfer Format When CPHA = 0       .417         18.8.4       SPI Baud Rate Generation       .420         18.8.5       Slave-Select Output       .420         18.8.6       Bidirectional Mode       .421         18.8.7       Error Conditions       .422         18.8.7.1       Write Collision Error       .422         18.8.7.2       Mode Fault Error       .422         18.8.8       Low-Power Mode Options       .423         18.8.8.1       Run Mode       .423         18.8.8.2       Doze Mode       .423         18.8.8.3       Stop Mode       .424         18.10       Interrupts       .424         18.10.1       Mode Fault (MODF) Flag       .424         18.10.2       SPI Interrupt Flag (SPIF)       .424                                                                                                                                                                                                                                                                                           | 18.8 Functional Description                                                                    |

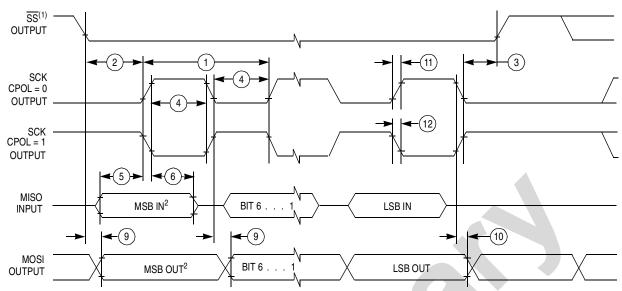

| 18.8.3       Transmission Formats       .416         18.8.3.1       Transfer Format When CPHA = 1       .416         18.8.3.2       Transfer Format When CPHA = 0       .417         18.8.4       SPI Baud Rate Generation       .420         18.8.5       Slave-Select Output       .420         18.8.6       Bidirectional Mode       .421         18.8.7       Error Conditions       .422         18.8.7.1       Write Collision Error       .422         18.8.7.2       Mode Fault Error       .422         18.8.8       Low-Power Mode Options       .423         18.8.8.1       Run Mode       .423         18.8.8.2       Doze Mode       .423         18.8.8.3       Stop Mode       .424         18.9       Reset       .424         18.10.1       Interrupts       .424         18.10.1       Mode Fault (MODF) Flag       .424         18.10.2       SPI Interrupt Flag (SPIF)       .424                                                                                                                                                                                                                                                                                                | 18.8.1 Master Mode                                                                             |

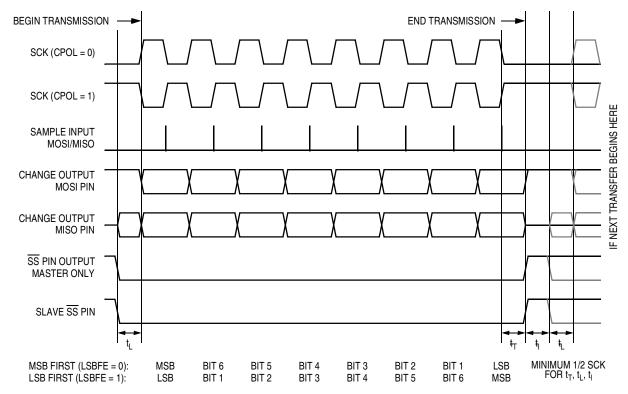

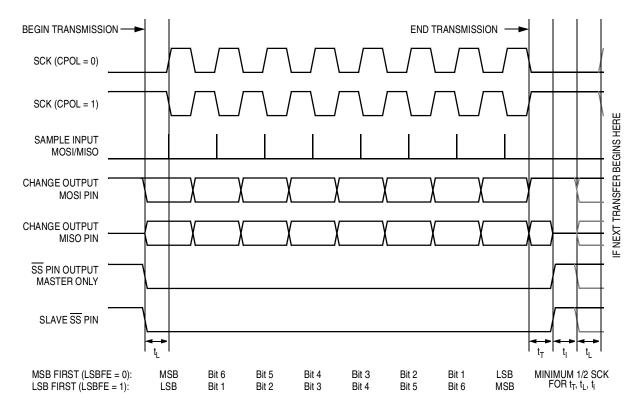

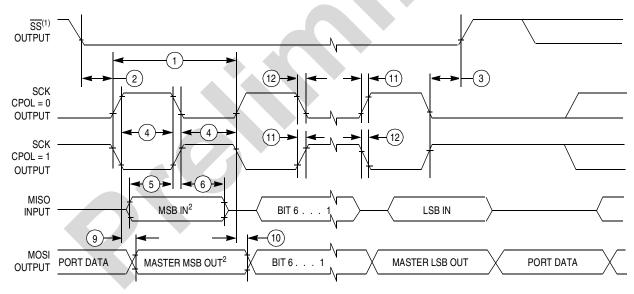

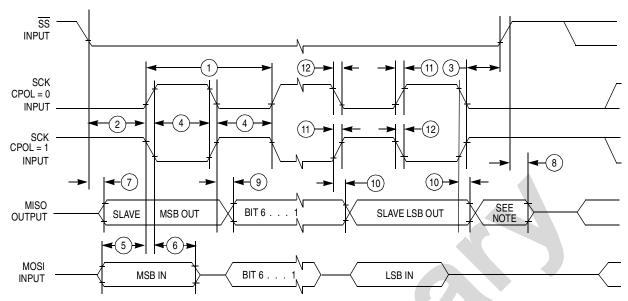

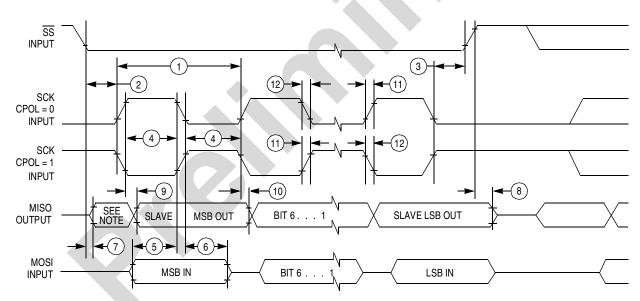

| 18.8.3.1       Transfer Format When CPHA = 1       416         18.8.3.2       Transfer Format When CPHA = 0       417         18.8.4       SPI Baud Rate Generation       420         18.8.5       Slave-Select Output       420         18.8.6       Bidirectional Mode       421         18.8.7       Error Conditions       422         18.8.7.1       Write Collision Error       422         18.8.7.2       Mode Fault Error       422         18.8.8       Low-Power Mode Options       423         18.8.8.1       Run Mode       423         18.8.8.2       Doze Mode       424         18.9       Reset       424         18.10       Interrupts       424         18.10.1       Mode Fault (MODF) Flag       424         18.10.2       SPI Interrupt Flag (SPIF)       424                                                                                                                                                                                                                                                                                                                                                                                                                  | 18.8.2 Slave Mode                                                                              |

| 18.8.3.2       Transfer Format When CPHA = 0       .417         18.8.4       SPI Baud Rate Generation       .420         18.8.5       Slave-Select Output       .420         18.8.6       Bidirectional Mode       .421         18.8.7       Error Conditions       .422         18.8.7.1       Write Collision Error       .422         18.8.7.2       Mode Fault Error       .422         18.8.8       Low-Power Mode Options       .423         18.8.8.1       Run Mode       .423         18.8.8.2       Doze Mode       .424         18.9       Reset       .424         18.10       Interrupts       .424         18.10.1       Mode Fault (MODF) Flag       .424         18.10.2       SPI Interrupt Flag (SPIF)       .424                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 18.8.3 Transmission Formats                                                                    |

| 18.8.4       SPI Baud Rate Generation       .420         18.8.5       Slave-Select Output       .420         18.8.6       Bidirectional Mode       .421         18.8.7       Error Conditions       .422         18.8.7.1       Write Collision Error       .422         18.8.7.2       Mode Fault Error       .422         18.8.8       Low-Power Mode Options       .423         18.8.8.1       Run Mode       .423         18.8.8.2       Doze Mode       .423         18.8.8.3       Stop Mode       .424         18.9       Reset       .424         18.10       Interrupts       .424         18.10.1       Mode Fault (MODF) Flag       .424         18.10.2       SPI Interrupt Flag (SPIF)       .424                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18.8.3.1 Transfer Format When CPHA = 1                                                         |

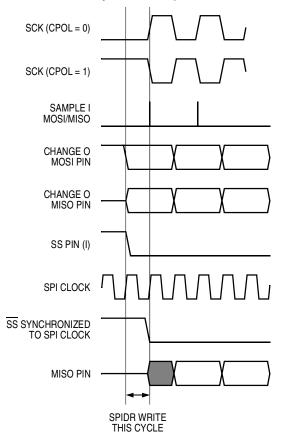

| 18.8.5       Slave-Select Output       420         18.8.6       Bidirectional Mode       421         18.8.7       Error Conditions       422         18.8.7.1       Write Collision Error       422         18.8.7.2       Mode Fault Error       422         18.8.8       Low-Power Mode Options       423         18.8.8.1       Run Mode       423         18.8.8.2       Doze Mode       424         18.9       Reset       424         18.10       Interrupts       424         18.10.1       Mode Fault (MODF) Flag       424         18.10.2       SPI Interrupt Flag (SPIF)       424                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 18.8.3.2 Transfer Format When CPHA = 0                                                         |

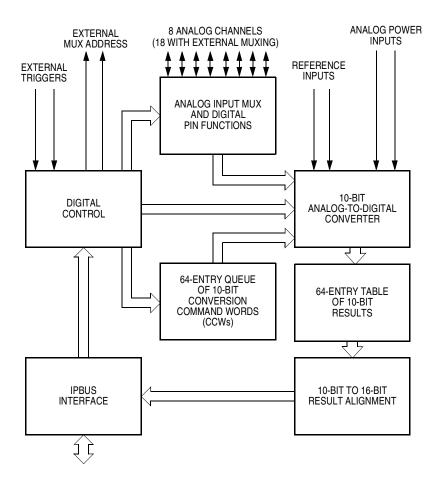

| 18.8.6       Bidirectional Mode       .421         18.8.7       Error Conditions       .422         18.8.7.1       Write Collision Error       .422         18.8.7.2       Mode Fault Error       .422         18.8.8       Low-Power Mode Options       .423         18.8.8.1       Run Mode       .423         18.8.8.2       Doze Mode       .423         18.8.8.3       Stop Mode       .424         18.9       Reset       .424         18.10       Interrupts       .424         18.10.1       Mode Fault (MODF) Flag       .424         18.10.2       SPI Interrupt Flag (SPIF)       .424                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18.8.4 SPI Baud Rate Generation420                                                             |