# ANALOG CONTROLLED VARIABLE GAIN AMPLIFIER

Package: MCM, 7mm x7mm

#### **Features**

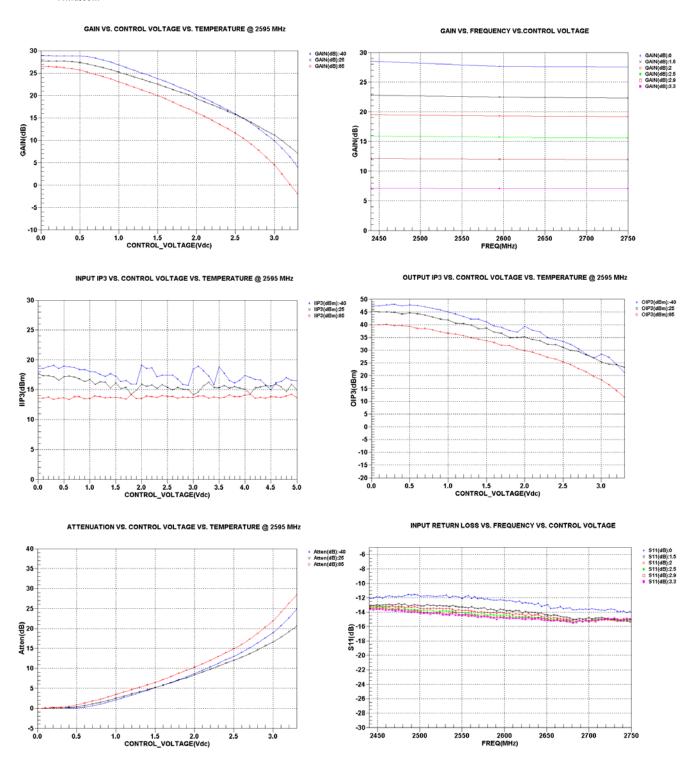

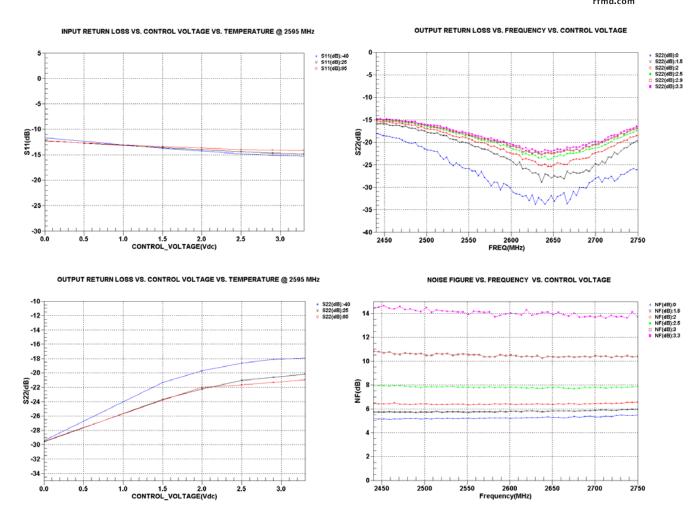

- 2440MHz to 2750MHz Operation

- Gain=28dB Typical

- Gain Adjustment Range > 19 dB

- ACPR=-64dBc Typ. at +12dBm P<sub>OUT</sub> (Dual Carrier WCDMA)

- Small, 7 mmx7 mm, Multi-Chip Module

### **Applications**

- Cellular, 3G and 4G Infrastructure

- WiBro, WiMax, LTE

- Microwave Radio

- High Linearity Power Control

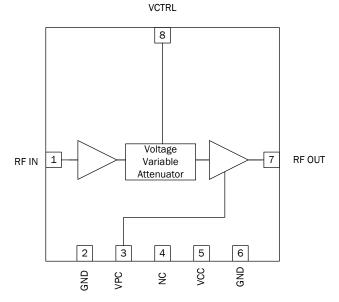

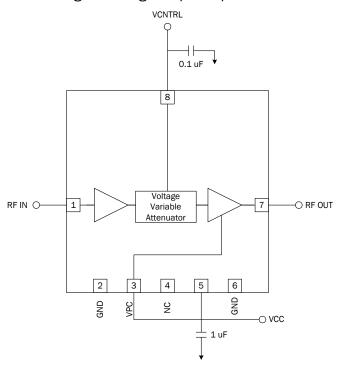

Functional Block Diagram

#### **Product Description**

RFMD's RVA3007L is a fully integrated analog controlled variable gain amplifier featuring exceptional linearity over a greater than 19dB gain control range. This variable gain amplifier is controlled by a single OV to 3.3V positive supply voltage. The RVA3007L is packaged in a small 7 mmx7 mm leadless laminate MCM which contains solid thermal vias for ultra low thermal resistance. This module is internally matched to  $50\Omega$  and is easy to use with no external matching components required.

#### **Ordering Information**

RVA3007LSQ Sample bag with 25 pieces

RVA3007LSR 7" Sample reel with 100 pieces

RVA3007LTR7 7" Reel with 1500 pieces

RVA3007LTR13 13" Reel with 2500 pieces

RVA3007LPCK-410 2440MHz to 2750MHz PCBA with 5-piece sample bag

#### **Optimum Technology Matching® Applied**

| ☐ GaAs HBT    | □ SiGe BiCMOS | ☐ GaAs pHEMT | ☐ GaN HEMT |

|---------------|---------------|--------------|------------|

| ☐,GaAs MESFET | ☐ Si BiCMOS   | ☐ Si CMOS    | ☐ RF MEMS  |

| ▼ InGaP HBT   | ☐ SiGe HBT    | ☐ Si BJT     | ☐ LDMOS    |

### **Absolute Maximum Ratings**

| Parameter                                           | Rating               | Unit |

|-----------------------------------------------------|----------------------|------|

| Max Device Current                                  | 770                  | mA   |

| Max Device Voltage                                  | 5.5                  | V    |

| Max Control Line Voltage                            | 6                    | V    |

| Max RF Input Power*                                 | 12                   | dBm  |

| Max Junction Temp (T <sub>J</sub> )                 | +150                 | °C   |

| Max Storage Temp                                    | +150                 | °C   |

| Thermal Resistance (junction to backside of module) | 14.8                 | °C/W |

| ESD                                                 | Class 1C (1000V min) |      |

| Moisture Sensitivity Level                          | MSL3                 |      |

<sup>\*</sup>Load condition:  $Z_L = 50 \Omega$

### Caution! ESD sensitive device.

Caution! ESD sensitive device.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application or circuitry and specifications at any time without prior notice.

RoHS (Restriction of Hazardous Substances): Compliant per EU Directive 2002/95/EC.

| Parameter                      | Specification |                | Unit | Condition |                                                                                      |  |

|--------------------------------|---------------|----------------|------|-----------|--------------------------------------------------------------------------------------|--|

| Faiailicici                    | Min.          | Min. Typ. Max. |      | Onit      | Condition                                                                            |  |

|                                |               |                |      |           |                                                                                      |  |

| Frequency                      | 2440          |                | 2750 | MHz       |                                                                                      |  |

| Temperature Range              | -40           | 25             | +85  | °C        | Operating range                                                                      |  |

| Gain                           | 25            | 28             | 31   | dB        | Min attenuator setting                                                               |  |

| Nominal Operating Output Power |               | 12             |      | dBm       | Operating power for ACPR rating                                                      |  |

| Output IP3                     | 39            | 45             |      | dBm       | In high gain setting                                                                 |  |

| P1dB                           | 27            | 29.5           |      | dBm       | High gain setting                                                                    |  |

| ACPR                           | -58           | -64            |      | dBc       | Dual carrier WCDMA, 7.5dB CF at nominal operating power; over full attenuation range |  |

| Gain Flatness                  |               | 0.2            | 0.4  | dB        | Over 50 MHz BW                                                                       |  |

| Gain Adjustment Range          | 19            |                |      | dB        |                                                                                      |  |

| Control Voltage Range          | 0             |                | 3.3  | V         |                                                                                      |  |

| Noise Figure                   |               | 5.0            | 6.5  | dB        | Min attenuator setting                                                               |  |

| Impedance                      |               | 50             |      | Ω         |                                                                                      |  |

| Input Return Loss              | 9             | 12             |      | dB        | Over attenuation range                                                               |  |

| Output Return Loss             | 11            | 18             |      | dB        | Over attenuation range                                                               |  |

| Supply Voltage                 | 4.75          | 5.0            | 5.25 | V         |                                                                                      |  |

| Supply Current                 | 300           | 410            | 550  | mA        | Max current is at -40°C                                                              |  |

| Supply Current (VPC=0V)        | 65            | 85             | 100  | mA        | Output amplifier shutdown total current; VPC=0V                                      |  |

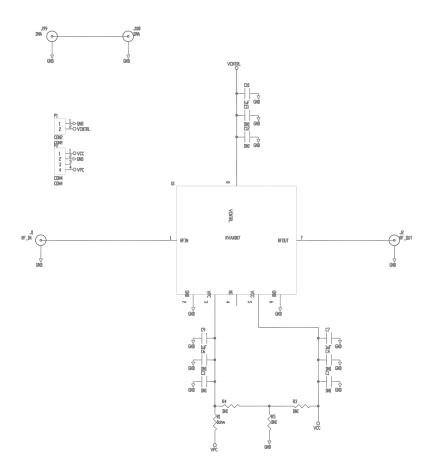

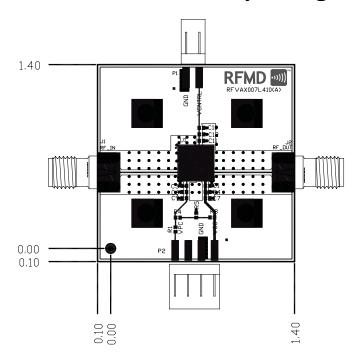

## **Evaluation Board Schematic**

# **Evaluation Board Bill of Materials (BOM)**

| Description                               | Reference                        | Manufacturer        | Manufacturer's P/N |

|-------------------------------------------|----------------------------------|---------------------|--------------------|

|                                           | Designator                       |                     |                    |

| EVALUATION BOARD                          |                                  | DDI                 | RFVAx007L410(A)    |

| CAP, 1µF, 10%, 10V, X5R, 0402             | C7, C9-C10                       | MURATA ELECTRONICS  | GRM155R61A105KE15D |

| RES, 0Ω, 0402                             | R1                               | KAMAYA, INC         | RMC1/16SJPTH       |

| CONN, SMA, END LAUNCH, UNIV, HYB MNT, FLT | J1-J2                            | HEILIND ELECTRONICS | PER MAT-21-1038    |

| CONN, HDR, ST, PLRZD, 4-PIN, 0.100"       | P2                               | ITW PANCON          | MPSS100-4-C        |

| CONN, HDR, ST, PLRZD, 2-PIN, 0.100"       | P1                               | ITW PANCON          | MPSS100-2-C        |

| DNP                                       | C1, C3-C4, C6, C11-C12,<br>R3-R5 |                     |                    |

| RVA3007L MODULE                           | U1                               | RFMD                | RVA3007L           |

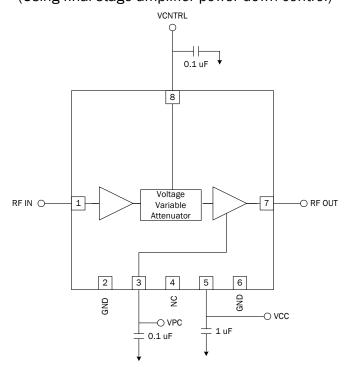

# **Pin Table and Description**

| Pin           | Function | Description                                                                                                                                                                                                                                                                               |

|---------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | RFIN     | RF input pin. Internal DC block.                                                                                                                                                                                                                                                          |

| 2             | GND      | Ground pin.                                                                                                                                                                                                                                                                               |

| 3             | VPC      | Power up/down control for 2nd stage amplifier. Apply $V_{CC}$ to power on 2nd stage amplifier. Apply 0V to disable 2nd stage amplifier. Do not exceed $V_{CC}+0.5$ V. Connect to $V_{CC}$ if not needed. Decoupling capacitor may be desired on application board for control line noise. |

| 4             | NC       | No connection.                                                                                                                                                                                                                                                                            |

| 5             | VCC      | Power supply for the module. Recommending 1uF decoupling cap on the application board.                                                                                                                                                                                                    |

| 6             | GND      | Ground pin.                                                                                                                                                                                                                                                                               |

| 7             | RFOUT    | RF output pin. Internal DC block.                                                                                                                                                                                                                                                         |

| 8             | VCTRL    | Gain control voltage; 0V to 3.3V range. Maximum gain at 0V. Recommending 0.1uF decoupling on the application board.                                                                                                                                                                       |

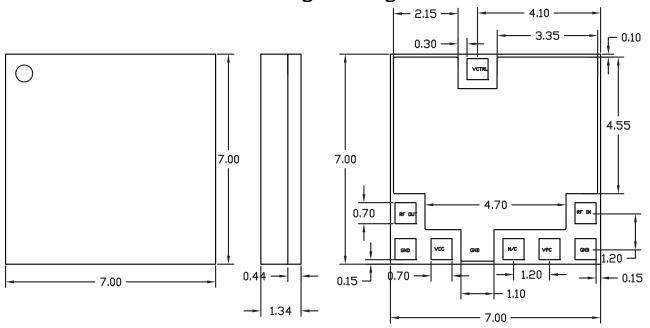

| Center<br>Pad | GND      | Center ground pads need to have a good thermal path on the application board. Use solder stencil pattern shown in the document to define solder paste during assembly.                                                                                                                    |

# **Application Schematic**

(Without using final stage amplifier power down control)

## **Application Schematic**

(Using final stage amplifier power down control)

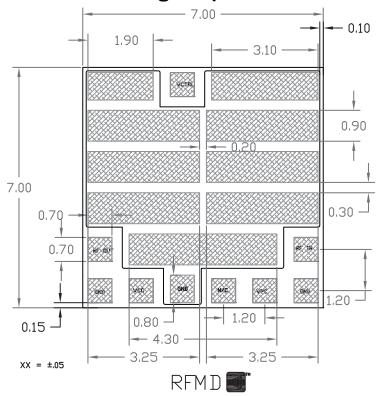

# **Package Drawing**

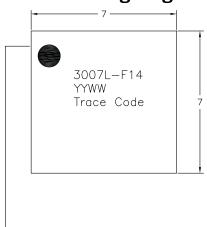

## **Branding Diagram**

Pin 1 Indicator

Fill in the YYWW Notation with the Date Code YY = Year WW = Week

Trace Code to be assigned by SubCon

# **Evaluation Board Assembly Drawing**

## **PCB Design Requirements**

Note: This solder stencil pattern is required to prevent solder voiding that may impact thermal dissipation.