rfmd.com

# RF6001

### FRACTIONAL-N RF SYNTHESIZER WITH MODULATOR AND DIGITAL IF FILTER

#### Part of the POLARIS<sup>™</sup> TOTAL RADIO<sup>™</sup> Solution RoHS Compliant & Pb-Free Product Package Style: QFN, 48-Pin, 7 x 7

### **Features**

- Fractional-N Synthesizer with Digital GMSK Modulator

- Signal Processing Circuitry for use with RF2722 VLIF Receiver

- Versatile Baseband Interface

- Integrated RF Transmit VCO's

### **Applications**

- GSM/DCS Handsets

- GSM/DCS/PCS Handsets

- Quad-Band GSM Handsets

- Multi-Band EDGE<sub>RX</sub> Handsets

- Multi-Band GPRS Handsets

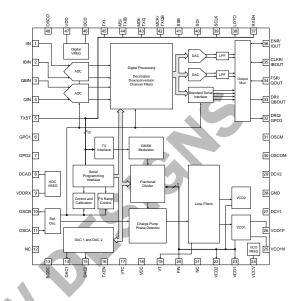

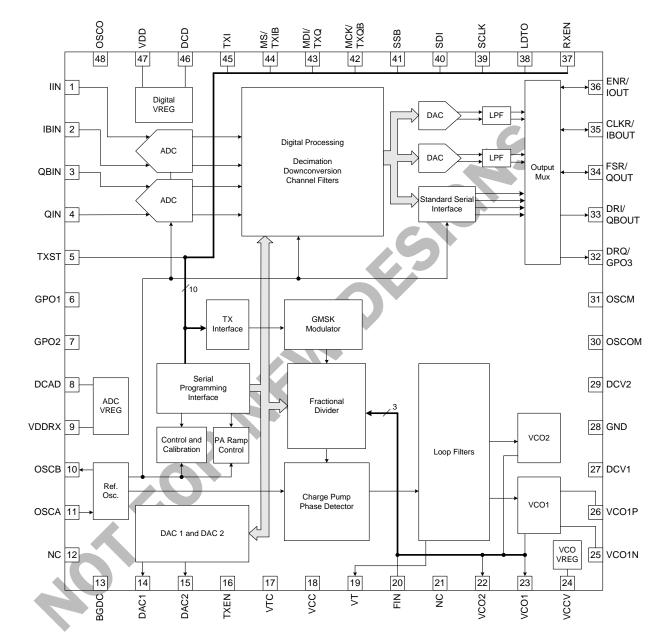

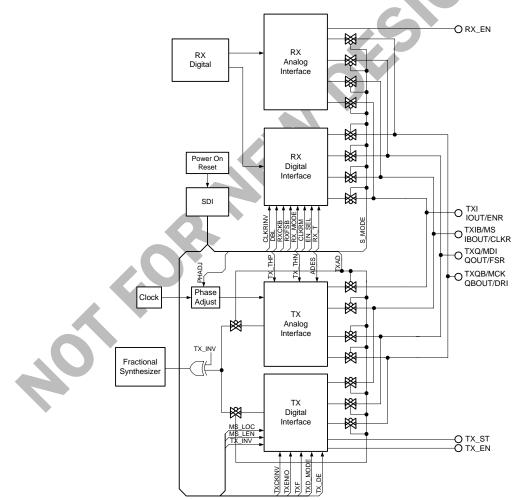

Functional Block Diagram

### **Product Description**

The RF6001 is a combination synthesizer and signal processing IC, which along with the RF2722 Very-Low-IF Receive IC, constitutes RFMD's low-cost GSM transceiver solution. The high-performance fractional-N synthesizer offers numerous features including a fully digital GMSK modulator with provisions for an analog I/Q interface and extremely low current consumption. The signal processor section provides a digital receive filter path designed to complement the RF2722. The IF inputs are digitized, filtered and downconverted to baseband I and Q signals. The flexible baseband interface can be configured for either analog or digital operation. Chip functionality is controlled through a three-wire serial data interface (SDI) bus. The RF2722 is part of the POLARIS<sup>TM</sup> TOTAL RADIO<sup>TM</sup> solution.

#### **Ordering Information**

RF6001

Fractional-N RF Synthesizer with Modulator and Digital IF Filter

### **Optimum Technology Matching® Applied**

| 🗌 GaAs HBT  | □ SiGe BiCMOS | ☐ GaAs pHEMT |

|-------------|---------------|--------------|

| GaAs MESFET | 🗌 Si BiCMOS   | Si CMOS      |

| 🗌 InGaP HBT | SiGe HBT      | 🗌 Si BJT     |

RF MICRO DEVICES®, RFMD®, Optimum Technology Matching®, Enabling Wireless Connectivity<sup>w</sup>, PowerStar®, POLARIS<sup>w</sup> TOTAL RADIO<sup>w</sup> and UttimateBlue<sup>w</sup> are trademarks of RFMD, LLC. BLUETOOTH is a trademark owned by Bluetooth SIG, Inc., U.S.A. and licensed for use by RFMD. All other trade names, trademarks and registered trademarks are the property of their respective owners. ©2006, RF Micro Devices, Inc.

7628 Thorndike Road, Greensboro, NC 27409-9421 · For sales or technical support, contact RFMD at (+1) 336-678-5570 or sales-support@rfmd.com.

GaN HEMT

#### Part of the POLARIS™ TOTAL RADIO™ Solution

| Parameter                                          | Rating      | Unit |

|----------------------------------------------------|-------------|------|

| Storage Temperature                                | -40 to +150 | °C   |

| Input Voltage, IIN, IBIN, QIN, QBIN                | 2.7         | V    |

| Input Voltage, all others                          | 3.6         | V    |

| Supply Voltage, V <sub>CC</sub>                    | -0.5 to 5.0 | V    |

| Supply Voltage, $V_{DD}$ , $V_{RXVDD}$ , $V_{CCV}$ | -0.5 to 3.6 | V    |

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice.

RoHS status based on EUDirective 2002/95/EC (at time of this document revision).

| Devemeter                                           |      | Specification |      | Unit | Condition                                                                       |

|-----------------------------------------------------|------|---------------|------|------|---------------------------------------------------------------------------------|

| Parameter                                           | Min. | Тур.          | Max. | Unit | Condition                                                                       |

| Operating Range                                     |      |               |      |      | All specifications met over listed operating range, unless otherwise specified. |

| Supply Voltage (V_{RXVDD}, V_{DD}, V_{CCV}, V_{CC}) | 2.7  | 2.75          | 3.0  | V    |                                                                                 |

| Temperature (T <sub>OP</sub> )                      | -40  | +25           | +85  | °C   |                                                                                 |

| Frequency Range                                     |      |               |      |      |                                                                                 |

| Receive                                             |      |               |      |      |                                                                                 |

| Cellular 850                                        | 869  |               | 894  | MHz  | Low Band Receive                                                                |

| EGSM900                                             | 925  |               | 960  | MHz  | Low Band Receive                                                                |

| DCS1800                                             | 1805 |               | 1880 | MHz  | High Band Receive                                                               |

| PCS1900                                             | 1930 |               | 1990 | MHz  | High Band Receive                                                               |

| Transmit                                            |      |               |      |      |                                                                                 |

| Cellular 850                                        | 824  |               | 849  | MHz  | Low Band Transmit                                                               |

| EGSM900                                             | 880  |               | 915  | MHz  | Low Band Transmit                                                               |

| DCS1800                                             | 1710 |               | 1785 | MHz  | High Band Transmit                                                              |

| PCS1900                                             | 1850 |               | 1910 | MHz  | High Band Transmit                                                              |

| Power Supply                                        |      |               |      |      |                                                                                 |

| Supply Current RX I <sub>RXD</sub>                  |      |               | 30   | mA   | Digital interface                                                               |

| Supply Current RX I <sub>RXA</sub>                  |      |               | 34   | mA   | Analog interface                                                                |

| Supply Current TX I <sub>TXHGD</sub>                |      |               | 80   | mA   | High band GMSK, digital                                                         |

| Supply Current TX I <sub>TXLGD</sub>                |      |               | 65   | mA   | Low band GMSK, digital                                                          |

| Supply Current TX I <sub>TXHGA</sub>                |      |               | 80   | mA   | High band GMSK, analog                                                          |

| Supply Current TX ITXLGA                            |      |               | 65   | mA   | Low band GMSK, analog                                                           |

| Supply Current Idle I <sub>MODE1</sub>              |      |               | 5    | mA   | Reference and buffers on                                                        |

| Supply Current Idle I <sub>MODE2</sub>              |      |               | 9    | mA   | Reference, buffer and AFC DAC                                                   |

| Supply Current Standby I <sub>SB</sub>              |      | 130           | 170  | uA   | Digital supply on, clocks off                                                   |

| Maximum Current by Pin                              |      |               |      |      |                                                                                 |

| V <sub>DDRX</sub> (pin 9)                           |      | 14.5          | TBD  | mA   | Worst case mode of operation                                                    |

| V <sub>CC</sub> (pin 18)                            |      | 10.5          | TBD  | mA   | Worst case mode of operation                                                    |

| V <sub>CCV</sub> (pin 24)                           |      | 42.0          | TBD  | mA   | Worst case mode of operation                                                    |

| V <sub>DD</sub> (pin 47)                            |      | 11.2          | TBD  | mA   | Worst case mode of operation                                                    |

| Parameter                              |      | Specification | 1     | Unit   | Condition                            |  |

|----------------------------------------|------|---------------|-------|--------|--------------------------------------|--|

|                                        | Min. | Тур.          | Max.  | Onit   |                                      |  |

| Performance Specifications             |      |               |       |        |                                      |  |

| SDI Write to RXEN or TXST              | 200  |               |       | ns     | Delay from SDI write to RXEN or TXST |  |

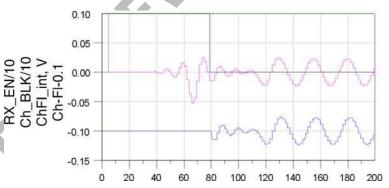

| RX_EN to Valid Data Start              |      |               | 200   | μs     | DCR mode                             |  |

|                                        |      |               | 160   | μs     | VLIF mode                            |  |

| TX_ST to Valid Data Start              |      |               | 140   | μs     |                                      |  |

| Modulation Accuracy                    |      |               |       |        |                                      |  |

| TX RMS Phase Error                     |      | 1.1           | 3.0   | ٥      | 6                                    |  |

| TX Peak Phase Error                    |      | 5.0           | 7.0   | ٥      |                                      |  |

| TX 400 kHz GMSK Spectrum               |      |               | -60   | dBc    | 30 kHz RBW rel to mod peak           |  |

| VCO1                                   |      |               |       |        | External inductor Q≥30.              |  |

| Frequency Range (F <sub>VCO1</sub> )   | 824  |               | 915   | MHz    |                                      |  |

| Phase Noise at 20MHz (L <sub>F</sub> ) |      |               | -164  | dBc/Hz |                                      |  |

| Power Out                              | 3    |               |       | dBm    |                                      |  |

| Frequency Pushing                      |      | 4             |       | MHz/V  | V <sub>CCV</sub> ±0.15V              |  |

| Frequency Pulling                      |      |               | 1     | MHz    | 2:1 VSWR all phases                  |  |

| Output VSWR                            |      |               | 2.5:1 |        |                                      |  |

| VCO2                                   |      |               |       |        |                                      |  |

| Frequency Range (F <sub>VCO2</sub> )   | 1710 |               | 1910  | MHz    |                                      |  |

| Phase Noise at 20MHz (L <sub>F</sub> ) |      |               | -155  | dBc/Hz |                                      |  |

| Power Out                              | 3    |               |       | dBm    |                                      |  |

| Frequency Pushing                      |      | 4             |       | MHz/V  | V <sub>CCV</sub> <u>+</u> 0.15V      |  |

| Frequency Pulling                      |      |               | 1     | MHz    | 2:1 VSWR all phases                  |  |

|                                        |      |               | 2.5:1 |        |                                      |  |

| Deverseter                                      |      | Specification |        | 11                |                                            |

|-------------------------------------------------|------|---------------|--------|-------------------|--------------------------------------------|

| Parameter                                       | Min. | Тур.          | Max.   | Unit              | Condition                                  |

| PLL Specification                               |      |               |        |                   |                                            |

| Frequency Range                                 | 0    |               | 2100   | MHz               | Internal                                   |

|                                                 | 0    |               | 550    | MHz               | FIN pin                                    |

| Input Level (FIN pin)                           | 50   |               |        | mV <sub>RMS</sub> |                                            |

| Input Impedance (FIN pin)                       |      | 2kΩ//2pF      |        |                   | On PC board                                |

| Phase Detector Frequency (F <sub>R</sub> )      |      |               | 26     | MHz               |                                            |

| PLL Bandwidth                                   |      | 90            |        | kHz               | TX mode                                    |

|                                                 |      | 50            |        | kHz               | RX mode                                    |

| Phase Noise at 50 kHz                           |      | -80           |        | dBc/Hz            | RX mode                                    |

|                                                 |      | -102          |        | dBc/Hz            | TX mode, VCO1                              |

|                                                 |      | -95           |        | dBc/Hz            | TX mode, VCO2                              |

| Output RF Spectrum due to Modu-                 |      |               |        |                   |                                            |

| lation                                          |      |               |        |                   |                                            |

| 200kHz                                          |      | -86.3         | -83.3  | dBc/Hz            |                                            |

| 250kHz                                          |      | -89.3         | -86.3  | dBc/Hz            |                                            |

| 400kHz                                          |      | -116.3        | -113.3 | dBc/Hz            | Low band                                   |

| 400kHz                                          |      | -113.8        | -110.8 | dBc/Hz            | High band                                  |

| 600 kHz to <1800 kHz                            |      | -116.3        | -113.3 | dBc/Hz            |                                            |

| 1800kHz to <3000kHz                             |      | -126.5        | -123.5 | dBc/Hz            |                                            |

| 3000kHz to <6000kHz                             |      | -126.5        | -123.5 | dBc/Hz            |                                            |

| <u>≥</u> 6000kHz                                |      | -134.5        | -131.5 | dBc/Hz            |                                            |

| Total Integrated Noise                          |      |               | 1      | °rms              |                                            |

| RX PLL Spurious Outputs                         | •    |               | -65    | dBc               | 600 kHz to 1.6 MHz                         |

| ETSI Spec Limits                                |      |               | -75    | dBc               | 1.6MHz to 3MHz                             |

|                                                 |      |               | -85    | dBc               | >3MHz low band                             |

|                                                 |      |               | -82    | dBc               | >3MHz high band                            |

|                                                 |      |               | -108   | dBc               | Out of band                                |

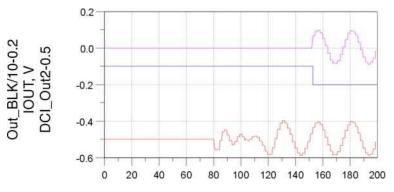

| PLL Warm-up Time                                |      |               | 140    | μs                | TX mode                                    |

|                                                 |      |               | 150    | μs                | RX mode                                    |

| Reference Oscillator Input                      |      |               |        |                   |                                            |

| VCTCXO (OSCA Pin)                               |      |               |        |                   |                                            |

| Frequency Range (F <sub>R</sub> )               | 0    |               | 26     | MHz               |                                            |

| Input Level (V <sub>INR</sub> )                 | 250  |               |        | mV <sub>RMS</sub> |                                            |

| Input Impedance (Z <sub>INR</sub> )             |      | 5kΩ//2pF      |        |                   | On PC board                                |

| Phase Noise                                     |      |               | -150   | dBc/Hz            | At 100kHz offset and above (external TCXO) |

| Reference Oscillator Input<br>Crystal (If Used) |      |               |        |                   |                                            |

| Beckmann Curve Discontinuities                  |      |               | 0.2    | ppm               |                                            |

| Crystal Startup Time                            |      |               | 1      | ms                |                                            |

| Crystal Load Capacitance                        |      | 10.5          |        | pF                |                                            |

| Crystal Case Capacitance                        |      | 2.5           | 4.0    | pF                |                                            |

| Pullability                                     |      | 30            |        | ppm/pF            |                                            |

| Parameter                                        | Specification |      |         | Unit              | Condition                  |

|--------------------------------------------------|---------------|------|---------|-------------------|----------------------------|

| Parameter                                        | Min.          | Тур. | Max.    |                   | Condition                  |

| Oscillator Output Buffer                         |               |      |         |                   |                            |

| Output Voltage (V <sub>OUT</sub> )               | 800           |      |         | mV <sub>P-P</sub> | Load: 10 kΩ//10 pF         |

| Output Frequency                                 | 13            |      | 26      | MHz               | Selected by OSCOM pin      |

| Phase Noise                                      |               |      | -115    | dBc/Hz            | SSB @ 50kHz                |

|                                                  |               |      | -120    | kHz               | SSB @ 100 kHz              |

|                                                  |               |      | -125    | dBc/Hz            | SSB @ 400 kHz              |

| Harmonic Level                                   |               |      | -10     | dBc               | 3rd harmonic               |

|                                                  |               |      | -60     | dBc               | 35th harmonic              |

| Load Resistance                                  | 10            |      |         | kΩ                | Shunt                      |

| Load Capacitance                                 | 5             |      | 30      | pF                | Shunt                      |

| DAC1 and DAC2<br>Specifications                  |               |      |         |                   |                            |

| Resolution (RES <sub>D/A</sub> )                 | 12.5          | 14.0 |         | bits              | Effective number of bits   |

| Sample Rate (F <sub>S</sub> )                    |               | 26   |         | MHz               |                            |

| Lowpass Filter Bandwidth<br>(BW <sub>D/A</sub> ) | 120           | 128  | 136     | kHz               |                            |

| Lowpass Filter Order (N <sub>D/AF</sub> )        |               | 6    |         |                   | Butterworth                |

| Turn On Time                                     |               |      | 15      | μs                | Within 10mV                |

| Output Noise Floor                               |               |      | 500     | nV/rtHz           | At 100kHz offset           |

| Offset Error (V <sub>OFF</sub> )                 |               | 20   | 40      | mV                |                            |

| Gain Error (G <sub>ERROR</sub> )                 |               | TBD  |         | %                 |                            |

| Output Range (FS <sub>D/A</sub> )                | 0.1           |      | VCC-0.1 | V                 |                            |

| Output Resistive Load (R <sub>D/A</sub> )        | 30            |      |         | kΩ                |                            |

| Output Capacitive Load (C <sub>D/A</sub> )       |               |      | 500     | pF                |                            |

| DAC2 (AFC) Tri-State Output<br>Impedance         |               | 160  |         | kΩ                | DAC2EN=0                   |

| RX ADC Specifications                            |               |      |         |                   | Pins: IIN, IBIN, QIN, QBIN |

| Bandwidth (BW <sub>A/D</sub> )                   | 200           |      |         | kHz               |                            |

| Resolution (RES <sub>A/D</sub> )                 | 12            | 13   |         | bits              | Effective number of bits   |

| Input Voltage (V <sub>CMA/D</sub> )              |               | 1.25 |         | V                 | Common mode voltage        |

| Input Level (FS <sub>A/D</sub> )                 |               |      | 1       | V <sub>P-P</sub>  | Measured differentially    |

| Input Impedance (Z <sub>INA/D</sub> )            |               | 30   |         | kΩ                | Single-ended               |

| Sample Rate (F1)                                 |               | 13   |         | MHz               |                            |

| Parameter                                      |       | Specification |       | Unit | Condition                        |

|------------------------------------------------|-------|---------------|-------|------|----------------------------------|

| Farameter                                      | Min.  | Тур.          | Max.  | Unit | Condition                        |

| Composite Digital Filtering and Downconversion |       |               |       |      |                                  |

| Output Word Length                             | 12    |               | 16    | bits |                                  |

| Output Word Rate                               | 13/48 |               | 13/12 | MHz  |                                  |

| 100kHz VLIF Mode                               |       |               |       |      |                                  |

| Passband Ripple                                |       |               | 1     | dB   | All bandwidths                   |

| Group Delay                                    |       |               |       |      | Composite with RF2716            |

|                                                | 43.0  | 43.2          | 43.5  | us   | BW=80kHz and 85kHz               |

|                                                | 30.1  | 30.3          | 30.6  | US   | BW=90kHz and greater             |

| Group Delay Variance                           |       | 2             |       | ns   | RF6001 only                      |

| Group Delay Variance at<br>Bandwidth Edge      |       |               |       |      | Worst case composite with RF2716 |

|                                                | 237   | 273           | 367   | ns   | BW=80kHz                         |

|                                                | 250   | 289           | 409   | ns   | BW=85kHz                         |

|                                                | 264   | 307           | 464   | ns   | BW=90kHz                         |

|                                                | 281   | 330           | 538   | ns   | BW=95kHz                         |

|                                                | 301   | 358           | 634   | ns   | BW=100kHz                        |

|                                                | 360   | 443           | 911   | ns   | BW=110kHz                        |

|                                                | 453   | 582           | 1321  | ns   | BW=120kHz                        |

|                                                | 693   | 944           | 2108  | ns   | BW=135kHz                        |

| 3dB Corner Frequency                           |       |               |       |      | Composite with RF2716            |

|                                                |       | 80.0          |       | MHz  | BW=80kHz                         |

|                                                |       | 85.4          |       | MHz  | BW=85kHz                         |

|                                                |       | 87.2          |       | MHz  | BW=90kHz                         |

|                                                |       | 94.0          |       | MHz  | BW=95kHz                         |

|                                                |       | 97.2          |       | MHz  | BW=100kHz                        |

|                                                |       | 107.8         |       | MHz  | BW=110kHz                        |

|                                                |       | 118.3         |       | MHz  | BW=120kHz                        |

|                                                |       | 133.3         |       | MHz  | BW=135kHz                        |

| Attenuation at -600 kHz                        | -100  |               |       | dB   | All bandwidths                   |

| Attenuation at -400kHz                         | -60   |               |       | dB   | All bandwidths                   |

| Attenuation at -200kHz                         | -35   |               |       | dB   | BW=80kHz and 85kHz               |

|                                                | -40   |               |       | dB   | BW=90kHz and 95kHz               |

|                                                | -50   |               |       | dB   | BW=100kHz and greater            |

| Attenuation at +200kHz                         | -40   |               |       | dB   | BW=80kHz and 85kHz               |

|                                                | -55   |               |       | dB   | BW=90 kHz and greater            |

| Attenuation at +400 kHz                        | -100  |               |       | dB   | All bandwidths                   |

| Attenuation at +600 kHz                        | -100  |               |       | dB   | All bandwidths                   |

| Devenator                                               |           | Specification |      | Unit |                              |  |

|---------------------------------------------------------|-----------|---------------|------|------|------------------------------|--|

| Parameter                                               | Min. Typ. |               | Max. |      | Condition                    |  |

| Composite Digital Filtering and Downconversion, cont'd. |           |               |      |      |                              |  |

| DCR Mode                                                |           |               |      |      |                              |  |

| Passband Ripple                                         |           |               | 0.5  | dB   | All bandwidths except 85 kHz |  |

|                                                         |           |               | 1.0  | dB   | BW=85kHz                     |  |

| Group Delay                                             |           |               |      |      | Composite with RF2716        |  |

|                                                         | 43.0      | 43.2          | 43.5 | us   | BW=80kHz and 85kHz           |  |

|                                                         | 30.1      | 30.3          | 3.06 | us   | BW=90kHz and greater         |  |

| Group Delay Variance                                    |           | 2             |      | ns   | RF6001 only                  |  |

| Group Delay Variance at<br>Bandwidth Edge               |           |               |      |      | Composite with RF2716        |  |

|                                                         | 228       | 256           | 341  | ns   | BW=80kHz                     |  |

|                                                         | 241       | 271           | 369  | ns   | BW=85kHz                     |  |

|                                                         | 253       | 286           | 406  | ns   | BW=90kHz                     |  |

|                                                         | 267       | 303           | 456  | ns   | BW=95kHz                     |  |

|                                                         | 282       | 324           | 521  | ns   | BW=100kHz                    |  |

|                                                         | 325       | 383           | 720  | ns   | BW=110kHz                    |  |

|                                                         | 392       | 481           | 1035 | ns   | BW=120kHz                    |  |

|                                                         | 572       | 752           | 1750 | ns   | BW=135kHz                    |  |

| 3dB Corner Frequency                                    |           |               |      |      | Composite with RF2716        |  |

|                                                         |           | 80.8          |      | MHz  | BW=80kHz                     |  |

|                                                         |           | 85.4          |      | MHz  | BW=85kHz                     |  |

|                                                         | •         | 89.8          |      | MHz  | BW=90kHz                     |  |

|                                                         |           | 96.5          |      | MHz  | BW=95kHz                     |  |

|                                                         |           | 100.1         |      | MHz  | BW=100kHz                    |  |

|                                                         |           | 110.2         |      | MHz  | BW=110kHz                    |  |

|                                                         |           | 119.8         |      | MHz  | BW=120kHz                    |  |

|                                                         |           | 136.1         |      | MHz  | BW=135kHz                    |  |

| Attenuation at -600 kHz                                 | -100      |               |      | dB   | All bandwidths               |  |

| Attenuation at -400kHz                                  | -60       |               |      | dB   | All bandwidths               |  |

| Attenuation at ±200kHz                                  | -35       |               |      | dB   | BW=80kHz and 85kHz           |  |

|                                                         | -45       |               |      | dB   | BW=90kHz and 95kHz           |  |

|                                                         | -50       |               |      | dB   | BW=100kHz and greater        |  |

| Attenuation at +400 kHz                                 | -100      |               |      | dB   | All bandwidths               |  |

| Attenuation at +600kHz                                  | -100      |               |      | dB   | All bandwidths               |  |

#### Part of the POLARIS™ TOTAL RADIO™ Solution

| Deveneetev                                          |                       | Specification        |                    | 11               | O an diti an                                                                        |  |

|-----------------------------------------------------|-----------------------|----------------------|--------------------|------------------|-------------------------------------------------------------------------------------|--|

| Parameter                                           | Min.                  | Тур.                 | Max.               | Unit             | Condition                                                                           |  |

| RX D/A Converters                                   |                       |                      |                    |                  | pins: IOUT, IBOUT, QOUT, QBOUT                                                      |  |

| Resolution (RES <sub>D/A</sub> )                    | 12                    |                      |                    | bits             | Effective number of bits                                                            |  |

| Sample Rate (Fs)                                    |                       | 13                   |                    | MHz              |                                                                                     |  |

| Lowpass Filter Bandwidth (BW <sub>D/A</sub> )       | 140                   | 150                  | 160                | kHz              |                                                                                     |  |

| Lowpass Filter Order (N <sub>D/AF</sub> )           |                       | 6                    |                    |                  | hybrid Butterworth/Bessel                                                           |  |

| IQ Differential Offset                              |                       | 10                   |                    | mV               |                                                                                     |  |

| IQ Gain Mismatch                                    |                       | 0.1                  | 0.5                | dB               |                                                                                     |  |

| Common Mode Voltage                                 |                       | V <sub>DDRX</sub> /2 |                    | V                |                                                                                     |  |

| Output Voltage Range (FS <sub>D/A</sub> )           | 0                     |                      | 2.0                | V <sub>P-P</sub> | differential, OdB gain                                                              |  |

| Output Resistive Load (R <sub>D/A</sub> )           | 30                    |                      |                    | kΩ               | each signal                                                                         |  |

| Output Capacitive Load (C <sub>D/A</sub> )          |                       |                      | 50                 | pF               | each signal                                                                         |  |

| GMSK I/Q Interface                                  |                       |                      |                    |                  | Pins: TXI, TXIB, TXQ, TXQB                                                          |  |

| I/Q Input Voltage (V <sub>CMI/Q</sub> )             | 1.00                  | 1.25                 | 1.50               | V                | Common mode                                                                         |  |

| I/Q Input Level (V <sub>PI/Q</sub> )                | 0.5                   | 1.0                  | 1.20               | V <sub>PK</sub>  | Differential                                                                        |  |

| Input Impedance (Z <sub>INI/Q</sub> )               | 30                    |                      |                    | kΩ               |                                                                                     |  |

| Digital Input Specifications                        |                       |                      |                    |                  | Apply to pins: SSB, SDI, SCLK, RXEN, TXST,<br>TXEN, MCK, MDI, MS, OSCM, OSCOM, CLKR |  |

| Input High Voltage (V <sub>IH</sub> )               | 0.7V <sub>DD</sub>    |                      |                    | V                |                                                                                     |  |

| Input Low Voltage (V <sub>IL</sub> )                |                       |                      | 0.3V <sub>DD</sub> | V                |                                                                                     |  |

| Input High Current (I <sub>IH</sub> )               |                       |                      | 50                 | μΑ               |                                                                                     |  |

| Input Low Current (I <sub>IL</sub> )                |                       |                      | 50                 | μΑ               |                                                                                     |  |

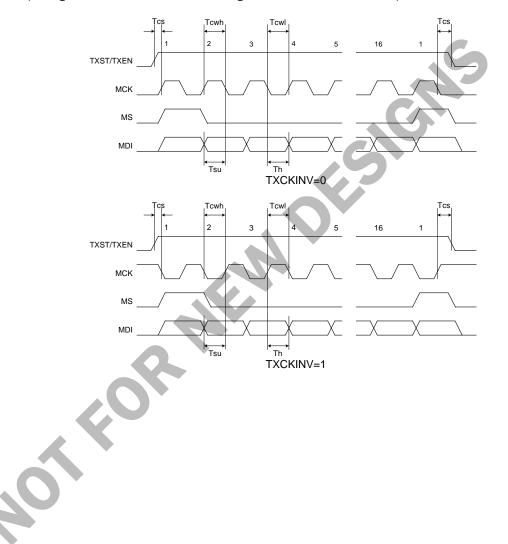

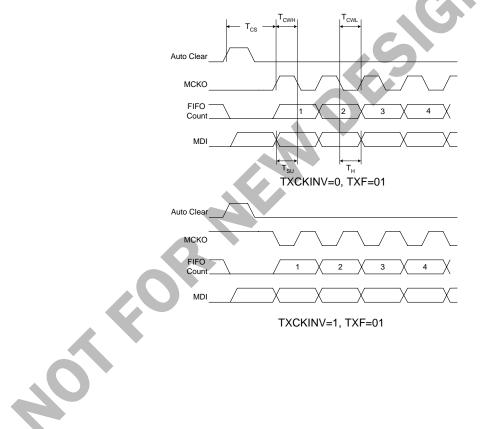

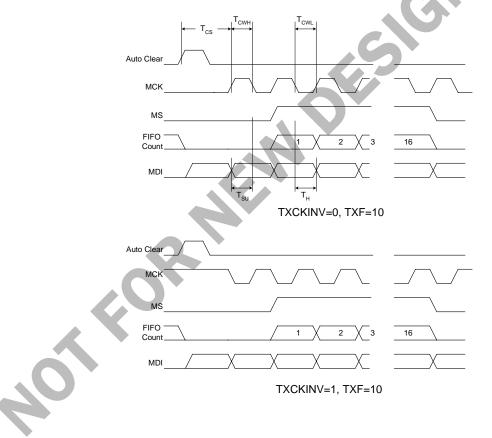

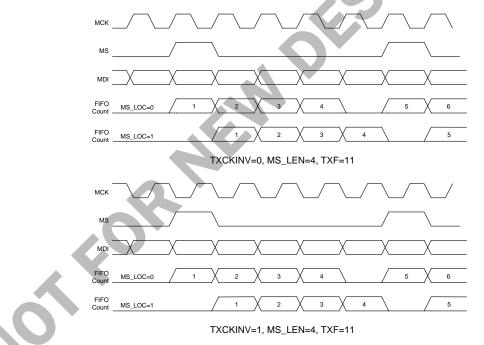

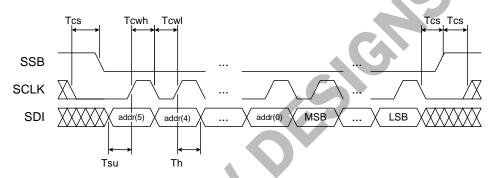

| Input Setup Time* (T <sub>SU</sub> )                | 10                    |                      |                    | ns               |                                                                                     |  |

| Input Hold Time* (T <sub>HLD</sub> )                | 10                    |                      |                    | ns               |                                                                                     |  |

| Input Rise/Fall Time (T <sub>RFI</sub> )            |                       |                      | 15                 | ns               |                                                                                     |  |

| Input Clock to Select Time (T <sub>CS</sub> )       | 10                    |                      |                    | ns               |                                                                                     |  |

| Input Clock Pulse Width High<br>(T <sub>CWH</sub> ) | 15                    |                      |                    | ns               |                                                                                     |  |

| Input Clock Pulse Width Low (T <sub>CWL</sub> )     | 15                    |                      |                    | ns               |                                                                                     |  |

| Input Capacitance (C <sub>IN</sub> )                |                       |                      | 650                | fF               |                                                                                     |  |

| Digital Output Drivers                              |                       |                      |                    |                  | Apply to pins: LDTO, ENR, CLKR, FSR, DRI,<br>MCK, MS                                |  |

| Output High Voltage (V <sub>OH</sub> )              | 0.8V <sub>DD</sub>    |                      |                    | V                | With 1mA load                                                                       |  |

| Output Low Voltage (V <sub>OL</sub> )               |                       |                      | 0.2V <sub>DD</sub> | V                | With 1mA load                                                                       |  |

| Output Rise/Fall Time (T <sub>RFO</sub> )           |                       |                      | 5                  | ns               | With 20pF maximum load capacitance                                                  |  |

| GPO Output Drivers                                  |                       |                      |                    |                  | Apply to pins: GP01, GP02 and DRQ/GP03.                                             |  |

| Output High Voltage (V <sub>OH</sub> )              | V <sub>DD</sub> -0.05 |                      |                    | V                | With 1mA load                                                                       |  |

|                                                     | V <sub>DD</sub> -0.45 |                      |                    | V                | With 10 mA load                                                                     |  |

| Output Low Voltage (V <sub>OL</sub> )               |                       |                      | 0.02               | V                | With 1mA load                                                                       |  |

|                                                     |                       |                      | 0.2                | V                | With 10mA load                                                                      |  |

$\ast$  Setup and Hold Times are measured from the time where the waveforms cross V\_DD/2.

#### rfmd.com

# RF6001

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Interface Schematic |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1   | IIN      | Non-inverting input of the I channel A/D converter, to be connected to I out of the RF2722. Analog input.                                                                                                                                                                                                                                                                                                                                                                                                  |                     |

| 2   | IBIN     | Inverting input of the I channel A/D converter, to be connected to IB out of the RF2722. Analog input.                                                                                                                                                                                                                                                                                                                                                                                                     |                     |

| 3   | QBIN     | Inverting input of the Q channel A/D converter, to be connected to QB out of the RF2722. Analog input.                                                                                                                                                                                                                                                                                                                                                                                                     |                     |

| 4   | QIN      | Non-inverting input of the Q channel A/D converter, to be connected to Q out of the RF2722. Analog input.                                                                                                                                                                                                                                                                                                                                                                                                  |                     |

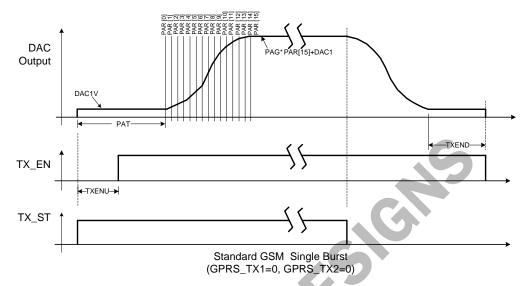

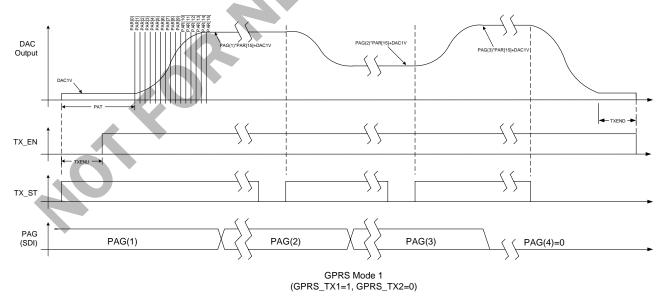

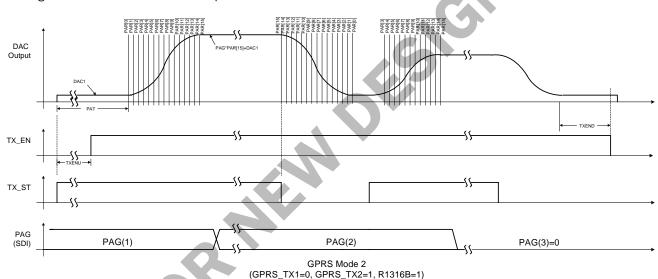

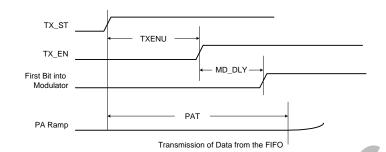

| 5   | TXST     | Transmit start. A rising edge on this signal initiates the transmit sequence<br>(PA ramp up). A falling edge on this signal begins the transmit shut down<br>sequence (PA ramp down). Digital input with weak pulldown.                                                                                                                                                                                                                                                                                    |                     |

| 6   | GP01     | General purpose output 1. This pin can be used to control a T/R switch.<br>General purpose digital output (GPO).                                                                                                                                                                                                                                                                                                                                                                                           |                     |

| 7   | GPO2     | General purpose output 2. This pin can be used to control a T/R switch.<br>General purpose digital output (GPO).                                                                                                                                                                                                                                                                                                                                                                                           |                     |

| 8   | DCAD     | Digital Receiver, ADC, and DAC voltage regulator output. A decoupling capacitor is required to ground. DC output voltage of 2.5V when the receive circuits are enabled.                                                                                                                                                                                                                                                                                                                                    |                     |

| 9   | VDDRX    | Receive power supply. Supply filtering components may be required in some applications (e.g. series resistor and shunt capacitor). Note that series resistance to this pin will drop the supply voltage. The specified supply voltage range needs to be present on this pin during operation.                                                                                                                                                                                                              |                     |

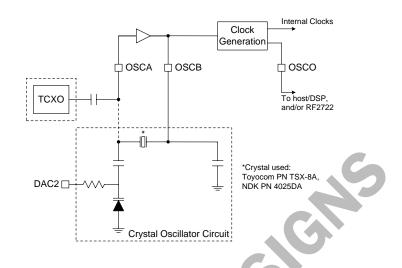

| 10  | OSCB     | Reference oscillator B input. When used with the internal reference oscilla-<br>tor this pin is connected to an external 26MHz crystal. If an external TCXO<br>is used, this pin should be floating. This pin possesses a DC voltage and<br>may require a DC-blocking cap in some applications. DC voltage equal to<br>VDD when the oscillator is off (OSCM pin low); DC voltage of approximately<br>1V when used with a crystal; DC voltage of approximately 2.4V when used<br>with a TCXO. Analog input. |                     |

| 11  | OSCA     | Reference oscillator A input. When used with the internal reference oscilla-<br>tor this pin is connected to an external 26MHz crystal. If an external TCXO<br>is used, this pin should be connected to the TCXO output through a decou-<br>pling capacitor. This pin possesses a DC voltage of approximately 1.25V<br>and may require a DC-blocking capacitor in some applications. DC voltage<br>equal to VDD when the oscillator is off (OSCM pin low). Analog input.                                   |                     |

| 12  | NC       | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |

| Pin | Function | Description                                                                                                                                                                                                                                                                                                                                                      | Interface Schematic |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 13  | BGDC     | Bandgap voltage regulator output. A decoupling capacitor is required to ground. DC output voltage of 1.25V.                                                                                                                                                                                                                                                      |                     |

| 14  | DAC1     | DAC1 output. This pin is dedicated for the PA ramp control system when PAEN bit is set to logic 1. Buffered analog output.                                                                                                                                                                                                                                       |                     |

| 15  | DAC2     | DAC2 output. General purpose DAC that can be used for AFC control of the reference oscillator. Buffered analog output.                                                                                                                                                                                                                                           |                     |

| 16  | TXEN     | Transmit enable. Bi-directional digital pin. This pin can be used as an input<br>or as an output of the PA ramp system. This signal is also used to enable<br>the PA; for example, it should be connected to TX enable pin of the RF3146<br>PA. The direction of the pin is determined by the TXENIO bit. Digital input<br>with weak pulldown or digital output. |                     |

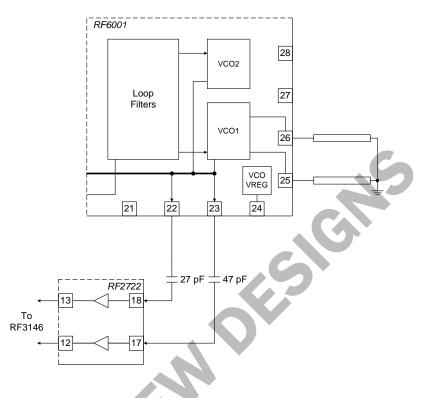

| 17  | VTC      | VCO coarse tuning control. This pin is connected to VTC pin on the RF2722 front end IC. Digital output.                                                                                                                                                                                                                                                          |                     |

| 18  | VCC      | PLL power supply. Supply filtering components may be required in some applications (e.g., series resistor and shunt capacitor). Note that series resistance to this pin will drop the supply voltage. The specified supply voltage range needs to be present on this pin during operation.                                                                       |                     |

| 19  | VT       | PLL loop filter output. This pin should be connected to VT pin on the RF2722. Provides the correct tuning voltage to set the RX VCO to the pro-<br>grammed frequency. Low impedance analog output.                                                                                                                                                               |                     |

| 20  | FIN      | PLL prescaler input. This pin should be connected to VCO OUT pin on the RF2722. Input impedance is specified in the PLL section of the electrical specifications. When probing this pin, the probe must have an effective DC resistance of $180 \text{ k}\Omega$ minimum and < 10 pF capacitance.                                                                |                     |

| 21  | NC       | No connect.                                                                                                                                                                                                                                                                                                                                                      |                     |

| 22  | VC02     | VCO2 output. DCS/PCS VCO output to the PA. This pin possesses a DC volt-<br>age and may require a DC blocking cap in some applications. Output<br>impedance is specified in the VCO2 section of the electrical specifications.                                                                                                                                   |                     |

| 23  | VCO1     | VCO1 output. US cellular/EGSM output to the PA. This pin possesses a DC voltage and may require a DC blocking cap in some applications. Output impedance is specified in the VCO1 section of the electrical specifications.                                                                                                                                      |                     |

| 24  | VCCV     | VCO power supply. Supply filtering components may be required in some applications (e.g. series resistor and shunt capacitor). Note that series resistance to this pin will drop the supply voltage. The specified supply voltage range needs to be present on this pin during operation.                                                                        |                     |

rfmd.com

# **RF6001**

| Pin | Function       | Description                                                                                                                                                                                                                                                                                                                                                         | Interface Schematic |

|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 25  | VCO1N          | VC01 tank inductance, negative side. Used to complete resonant circuit for VC01. Refer to the applications section of the datasheet for details.                                                                                                                                                                                                                    |                     |

| 26  | VCO1P          | VCO1 tank inductance, positive side. Used to complete resonant circuit for VCO1. Refer to the applications section of the datasheet for details.                                                                                                                                                                                                                    |                     |

| 27  | DCV1           | VCO1 regulator output. A decoupling capacitor is required to ground. DC output voltage of approximately 1.4V when VCO1 is enabled.                                                                                                                                                                                                                                  |                     |

| 28  | GND            | This pin should be tied to ground.                                                                                                                                                                                                                                                                                                                                  |                     |

| 29  | DCV2           | VCO2 regulator output. A decoupling capacitor is required to ground. DC output voltage of approximately 1.4V when VCO2 is enabled.                                                                                                                                                                                                                                  |                     |

| 30  | OSCOM          | Oscillator buffered output mode control. This pin controls the frequency of the OSCO (pin 48) output. A logic 0 on this pin results in 13MHz output and a logic 1 results in a 26MHz output. Digital input with weak pulldown.                                                                                                                                      |                     |

| 31  | OSCM           | Oscillator mode control. This pin controls the internal reference oscillator<br>mode as described in the Reference Oscillator section. Digital input with<br>weak pulldown.                                                                                                                                                                                         |                     |

| 32  | DRQ/GP03       | Digital serial RX data interface output for Q data. This pin provides the Q data while in digital RX interface mode and RXMODE(2:0) is set to 001 or 110. When S_MODE is low or RXMODE(2:0) is not equal to 001 or 110, this pin can be multiplexed and used as a third general purpose output(GPO3). This GPO can be used to control a T/R switch. Digital output. |                     |

| 33  | DRI/QBOUT      | Digital serial RX data interface output or QB analog output. This pin is mul-<br>tiplexed between analog and digital RX output modes. The S_MODE bit<br>sets the interface mode. Digital output or buffered analog output.                                                                                                                                          |                     |

| 34  | FSR/QOUT       | Digital serial RX data interface frame sync or Q analog output. This pin is<br>multiplexed between analog and digital RX interface modes. The S_MODE<br>bit sets the interface mode. The RXFSB bit determines the direction of the<br>pin in digital mode. Digital input, digital output, or buffered analog output.                                                |                     |

| 35  | CLKR/<br>IBOUT | Digital serial RX data interface clock or IB analog output. This pin is multi-<br>plexed between analog and digital RX output interface modes. The<br>S_MODE bit sets the interface mode. The RXCKB bit determines the direc-<br>tion of the pin in digital mode. Digital input, digital output, or buffered ana-<br>log output.                                    |                     |

#### Part of the POLARIS™ TOTAL RADIO™ Solution

rfmd.com

| Pin | Function | Description                                                                                                                                                                                                                                                                                              | Interface Schematic |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

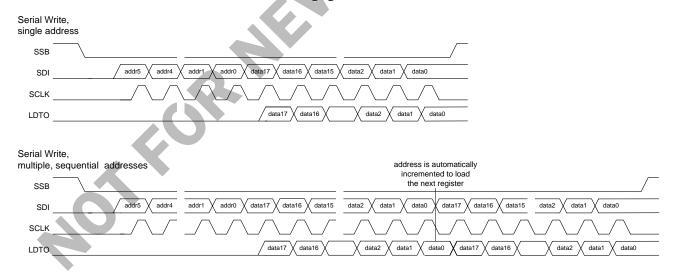

| 36  | ENR/IOUT | Digital serial RX data interface enable input or I analog output. This pin is multiplexed between analog and digital RX interface modes. The S_MODE bit sets the interface mode. Digital input or buffered analog output.                                                                                |                     |

| 37  | RXEN     | Receive path enable. Receive circuitry is active when a logic 1 is applied to this pin. Digital input with weak pulldown.                                                                                                                                                                                |                     |

| 38  | LDTO     | Lock detect/test digital output. This pin is multiplexed between various internal signals on the IC as defined by the TMUX and TEN bits. Digital output.                                                                                                                                                 |                     |

| 39  | SCLK     | Serial data interface clock input. Digital input.                                                                                                                                                                                                                                                        |                     |

| 40  | SDI      | Serial data interface data input. Digital input.                                                                                                                                                                                                                                                         |                     |

| 41  | SSB      | Serial data interface select input. The serial interface accepts clock and data when SSB is at a logic 0 (active low). Digital input with weak pullup.                                                                                                                                                   |                     |

| 42  | МСК/ТХQВ | Modulation clock input/output or TXQB transmit analog input. This pin is<br>multiplexed between analog and digital TX interface modes. The TXAD bit<br>sets the interface mode. The TXD_MODE bit determines the direction of<br>the pin in digital mode. Digital input, digital output, or analog input. |                     |

| 43  | MDI/TXQ  | Modulation data input or TXQ transmit analog input. This pin is multiplexed<br>between analog and digital TX interface modes. The TXAD bit sets the inter-<br>face mode. Digital input or analog input.                                                                                                  |                     |

| 44  | MS/TXIB  | Modulation sync input/output or TXIB transmit analog input. This pin is<br>multiplexed between analog and digital TX interface modes. The TXAD bit<br>sets the interface mode. Digital input/output or analog input.                                                                                     |                     |

| 45  | тхі      | TXI transmit analog input.                                                                                                                                                                                                                                                                               |                     |

#### rfmd.com

### Part of the POLARIS™ TOTAL RADIO™ Solution

**RF6001**

| Pin | Function | Description                                                                                                                                                                                                                                                                                   | Interface Schematic |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 46  | DCD      | Digital voltage regulator output. A decoupling capacitor is required to ground. DC output voltage of 2.5V.                                                                                                                                                                                    |                     |

| 47  | VDD      | Digital power supply. Supply filtering components may be required in some applications (e.g. series resistor and shunt capacitor). Note that series resistance to this pin will drop the supply voltage. The specified supply voltage range needs to be present on this pin during operation. |                     |

| 48  | OSCO     | Buffered reference oscillator output. This pin can be used to provide the system clock for the radio. Analog output. DC output voltage of approximately 1.6V when OSCO is enabled.                                                                                                            |                     |

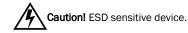

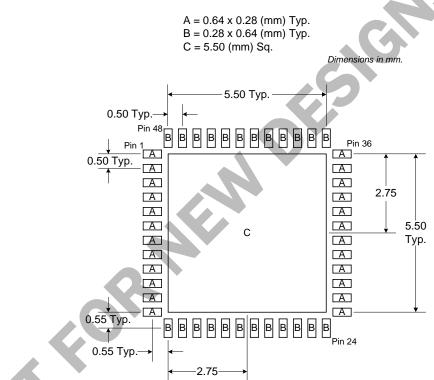

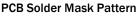

### Packaging

The device is packaged in a 48-pin leadless package with an outside dimension of 7mmx7mm and an exposed bottom-side ground flag.

### **Package Drawing**

#### Part of the POLARIS™ TOTAL RADIO™ Solution

### **Detailed Functional Block Diagram**

Part of the POLARIS™ TOTAL RADIO™ Solution

### **Application Information**

#### **Functional Description**

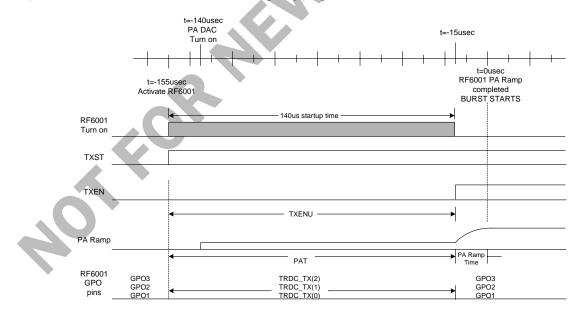

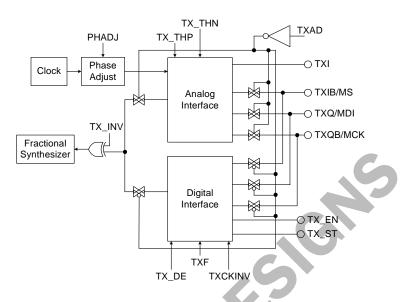

The RF6001 is a highly integrated receive and transmit processor intended for GSM/GPRS/EDGE<sub>RX</sub> applications. It contains the following functionality: A high performance fractional-N PLL, baseband digital filtering with A/D's and D/A's for GSM VLIF reception, two power transmit VCO's, GMSK modulator, PA ramp control DAC, and oscillator AFC control (reference oscillator circuitry). The fractional-N synthesizer section is multiplexed between transmit and receive functions, creating two sets of PLL parameters. PLL10-PLL12 registers are intended to be used with the receive VCO on the RF2722 VLIF receiver IC and PLL20-PLL21 registers are used with the two internal power VCO's on the RF6001. Each PLL configuration has a fully integrated loop filter. The internal power VCOs are designed for use in all GSM transmit bands; VCO1 has a frequency range of 824MHz to 915MHz and VCO2 has a frequency range of 1710MHz to 1910MHz. Each VCO has a +3dBm minimum output power. Down conversion from VLIF to baseband and all necessary baseband filtering for GSM/GPRS/EDGE reception is implemented digitally, with programmable bandwidths ranging from 80kHz to 135kHz. The receive and transmit baseband interfaces can be configured to work with standard analog differential I/Q signals or fully digital signals depending on SDI programming. The GMSK modulator necessary for GSM signaling is also provided and feeds into the transmit Fractional-N synthesizer for direct modulation of the VCO's. There are also two D/As (DAC1/DAC2) provided; DAC1 is configured to provide programmable ramp control function is provided, which has programmable ramp shaping and timing.

Features of the part include:

- A DC to 2.5 GHz fractional-N PLL having:

- Fine frequency resolution (typically 1.55 Hz)

- Charge pump with programmable current capability and operation to 5V

- Integrated Loop Filters

- Low Prescaler drive level requirement

- Two integrated RF transmit power VCO's with min +3dBm output power capability to drive PA's

- PA control system with GPRS support

- Power control DAC for PA ramp generation and programmable DAC for DC tuning voltage operation

- Programmable digital or analog TX interface to fractional-N GMSK modulation system

- I and Q channel digital filtering with 12-bit A/D's and D/A's for VLIF reception

- I and Q digital SSI interface with option for analog interface

This Device contains technology licensed under certain patents.

#### Part of the POLARIS™ TOTAL RADIO™ Solution

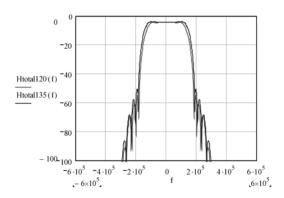

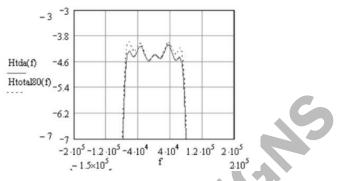

#### Composite Filter Responses

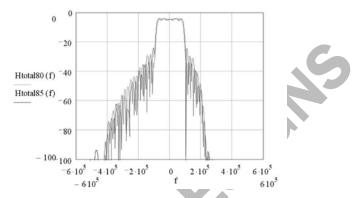

The stopband frequency response is shown below for the 80kHz and 85kHz channel bandwidths of the cascade of the RF2716/2722 and RF6001 in 100kHz VLIF mode. Note the notch at 100kHz. In this mode only the 80kHz and 85kHz bandwidths have this notch. Higher bandwidths may be used in this mode but a tone at 100kHz will be present due to any residual DC components converted by the VLIF offset.

For the bandwidths of 90kHz and greater, the DCR mode is suggested. Residual DC errors will be present in the output in this mode.

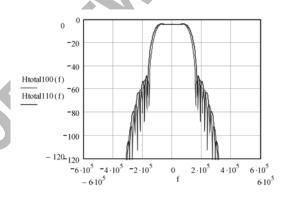

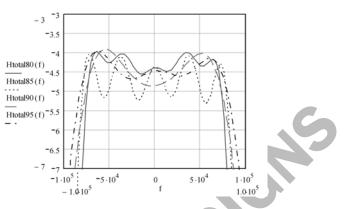

The stopband frequency response is shown below for the 100 kHz and 110 kHz channel bandwidths of the cascade of the RF2716/2722 and the RF6001 in DCR mode.

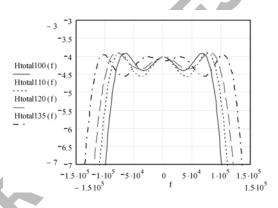

The stopband frequency response is shown below for the 120kHz and 135kHz channel bandwidths of the cascade of the RF2716/2722 and the RF6001 in DCR mode.

#### Part of the POLARIS™ TOTAL RADIO™ Solution

**RF6001**

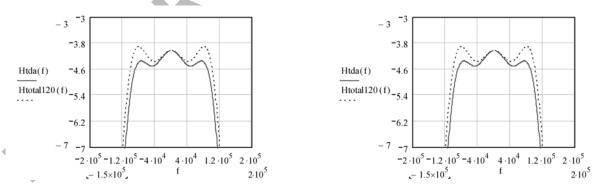

The passband frequency is shown below for the 80 kHz, 85 kHz, 90 kHz, and 95 kHz channel bandwidths of the cascade of the RF2716/2722 and the RF6001 in 100 kHz VLIF mode.

The passband frequency is shown below for channel bandwidths of 100kHz, 110kHz, 120kHz, and 135kHz channel bandwidths of the cascade of the RF2716/2722 and the RF6001 in DCR mode.

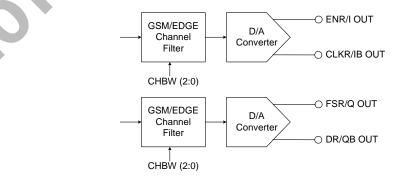

#### **Baseband Output Interface**

The output of the digital filtering system can be selected to be a digital SSI interface or to be an analog I and Q interface. The SPI bit S\_MODE selects the digital mode if programmed high and selects the analog mode if programmed low.

#### Analog Mode (S\_MODE=0)

The block diagram presented below shows the interface in this mode of operation.

The analog outputs are intended to interface directly with existing baseband ICs which already contain 12 bit A/D converters.

#### Part of the POLARIS™ TOTAL RADIO™ Solution

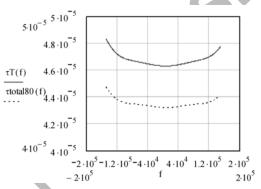

Due to the filters added to the D/A converter outputs, the group delay and channel bandwidths will be slightly modified. The plot below shows the amplitude response of the 80kHz channel bandwidth in 100kHz VLIF mode for the cascade of the RF2716/2722 and RF6001 with and without the D/A converter filter.

The plot below shows the group delay response of the cascade of the RF2716/2722 and the RF6001 with and without the D/A converter filter.

As a second example, the same two plots are repeated for a channel bandwidth of 120 kHz in DCR mode.

RX Digital Mode (S\_MODE=1)

If S\_MODE is set true, the receiver baseband interface is configured to digital mode. In this mode:

ENR acts as the SSI bus enable pin.

CLKR acts as the clock output for the serial data transfer.

FSR acts as the frame sync output for the serial data transfer.

DRI and DRQ are the serial data outputs.

The following sections describe the various operational modes available.

#### Part of the POLARIS™ TOTAL RADIO™ Solution

RF6001

<u>Selection of RX Clocks and Sync as Inputs or Outputs</u> FSR can be configured as an input (RXFSB=1) or as an output (RXFSB=0).

CLKR can be configured as an input (RXCKB=1) or as an output (RXCKB=0).

If CLKR is an input, then:

- 1. There must be at least two CLKR periods before valid data is output.

- 2. FSR can be an input or an output.

- 3. If FSR is also an input, then there must be at least two CLKR periods before FSR is externally set.

If CLKR is an output then FSR must be an output as well.

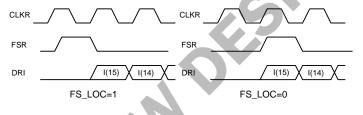

#### Selection of RX Sync Location Relative to Data

The position of FSR relative to the I channel MSB can be set with the SDI bit FS\_LOC. If FS\_LOC is set false then the FSR pulse occurs with the MSB of the I channel data as shown in all of the diagrams in the Digital RX SSI Mode section below. If FS\_LOC is set true then the FSR pulse will occur on the clock immediately before the MSB of the I channel data.

#### Selection of RX SSI Enable Method

The digital RX SSI can be enabled by two methods. The first method is a physical pin labeled ENR. If ENR is set high then the RX SSI will activate two CLKR pulses after ENR rises. The sampling point of the digital filters is set by the position of RX\_EN relative to the midamble and will not change with the position of ENR. The sample time of the SSI output word WILL move with the edge of ENR.

If ENR is set low then the RX SSI will deactivate after the current data transfer completes. This mode is active if the SDI bit EN\_SEL is programmed low.

If EN\_SEL is programmed high then the RX SSI activates with RX\_EN high and deactivates with RX\_EN low. All timing edges are relative to RX\_EN.

#### Summary of Digital RX SSI Modes

The various digital receive modes are explained in detail below.

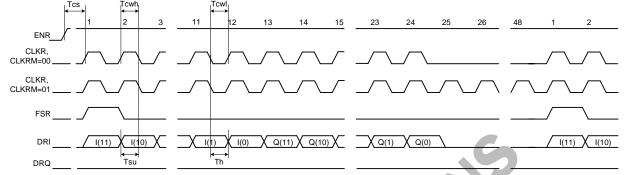

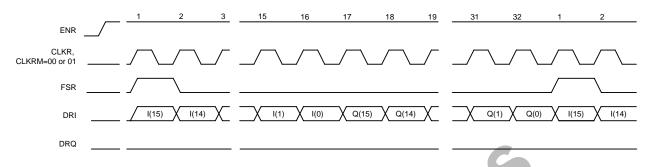

#### RXMODE=000, DBL=0

In this mode the SSI provides one sample of I and one sample of Q for each GSM symbol period. The output data pattern on DRI is 12 bits of I data followed by 12 bits of Q data followed by 24 blank bits. In this case FSR is (13/48)MHz=270.8333kbps and CLKR is 13MHz.

The various CLKR modes are defined as follows: with CLKRM=00 and RXCKB=0, CLKR will shut down after the Q data transfer completes until the next I data transfer to save power; with CLKRM=01 and RXCKB=0, CLKR is always enabled if ENR is true; with CLKRM=1x, CLKR is always disabled.

#### Part of the POLARIS™ TOTAL RADIO™ Solution

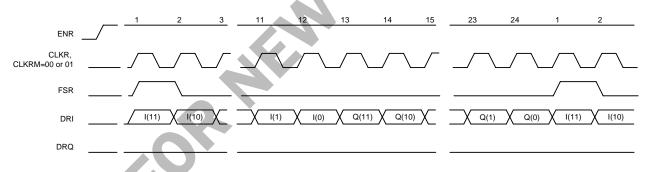

#### RXMODE=000, DBL=1

In this mode the SSI provides two samples of I and two samples of Q for each GSM symbol period. The output data pattern on DRI is 12 bits of I data followed by 12 bits of Q data. In this case, FSR is (13/24)MHz=541.667kbps and always marks the beginning of the I data transfer. CLKR is 13MHz.

The various CLKR modes are defined as follows: with CLKRM=00 and RXCKB=0, CLKR will shut down after the Q data transfer completes until the next I data transfer to save power (with RXMODE=000 and DBL=1, CLKR will always be enabled as there is no blank data); with CLKRM=01 and RXCKB=0, CLKR is always enabled if ENR is true; with CLKRM=1x, CLKR is always disabled.

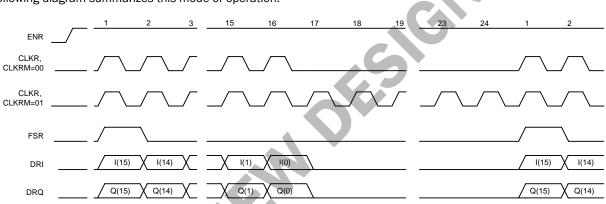

The following diagram summarizes this mode of operation.

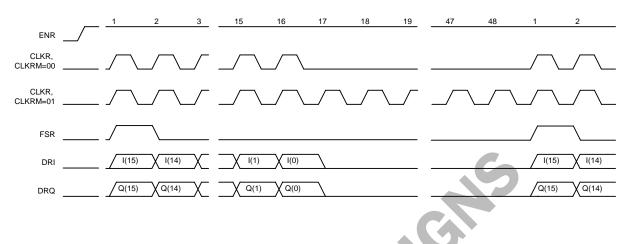

#### RXMODE=001, DBL=0

In this mode the SSI provides one sample of I and one sample of Q for each GSM symbol period. The output data pattern on DRI is 16 bits of I data followed by 32 blank bits, and the output data pattern on DRQ is 16 bits of Q data followed by 32 blank bits. In this case FSR is (13/48)MHz=270.8333kbps and CLKR is 13MHz.

The various CLKR modes are defined as follows: with CLKRM=00 and RXCKB=0, CLKR will shut down after the Q data transfer completes until the next I data transfer to save power; with CLKRM=01 and RXCKB=0, CLKR is always enabled if ENR is true; with CLKRM=1x, CLKR is always disabled.

#### Part of the POLARIS™ TOTAL RADIO™ Solution

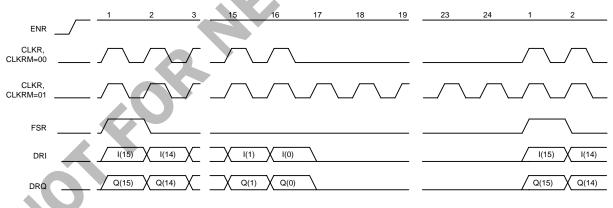

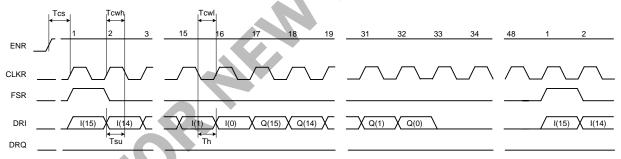

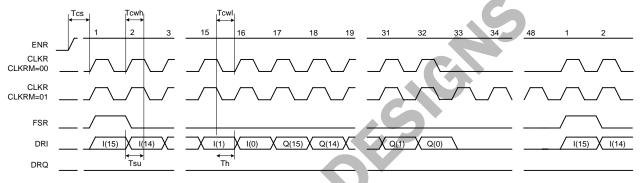

#### RXMODE=001, DBL=1

In this mode the SSI provides two samples of I and two samples of Q for each GSM symbol period. The output data pattern on DRI is 16 bits of I data followed by 8 blank bits, and the output data pattern on DRQ is 16 bits of Q data followed by 8 blank bits. In this case, FSR is (13/24)MHz=541.667kbps and always marks the beginning of the I and Q data transfer. CLKR is 13MHz.

The various CLKR modes are defined as follows: with CLKRM=00 and RXCKB=0, CLKR will shut down after the Q data transfer completes until the next I data transfer to save power; with CLKRM=01 and RXCKB=0, CLKR is always enabled if ENR is true; with CLKRM=1x, CLKR is always disabled.

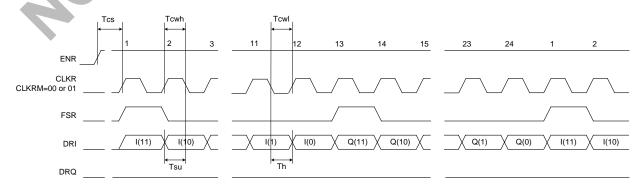

The following diagram summarizes this mode of operation.

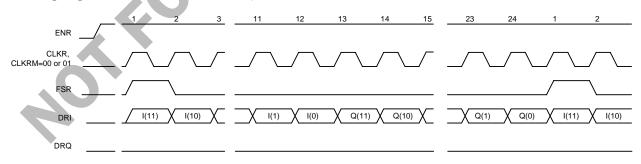

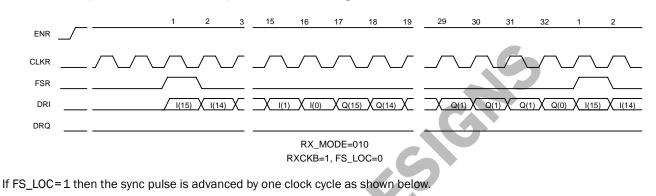

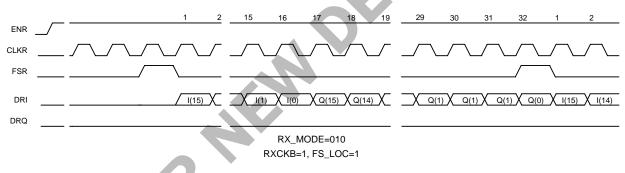

#### RXMODE=010

In this mode the SSI provides one sample of I and one sample of Q for each GSM symbol period. The output data pattern on DRI is 16 bits of I data followed by 16 bits of Q data. In this case, FSR is (8.667/32)MHz=270.833kbps and always marks the beginning of the I data transfer. CLKR is 8.667MHz.

The various CLKR modes are defined as follows: with CLKRM=00 and RXCKB=0, CLKR will shut down after the Q data transfer completes until the next I data transfer to save power (with RXMODE=010, CLKR will always be enabled as there is no blank data); with CLKRM=01 and RXCKB=0, CLKR is always enabled if ENR is true; with CLKRM=1x, CLKR is always disabled.

DBL has no effect in this mode.