16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

## Datasheet Brief

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

### **General Description**

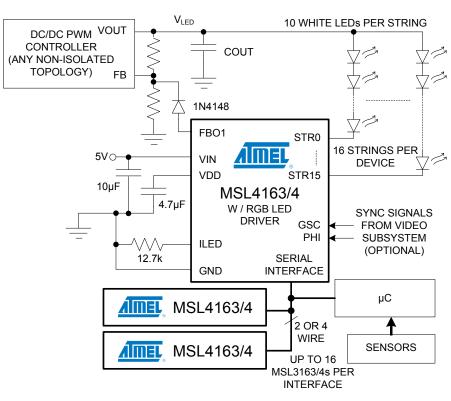

The Atmel<sup>®</sup> LED Drivers-MSL4163 and MSL4164 compact, high-power LED string drivers use internal current control MOSFETs to sink up to 100mA per string, with current accuracy and matching better than 3%. The MSL4163/4 drive 16 parallel strings of 10 white LEDs each, for a total of 160 white LEDs per device. Sixteen interconnected devices control up to 2560 white LEDs. The MSL4164 features a 20MHz SPI bus, and the MSL4163 offers a 1MHz I<sup>2</sup>C serial interface. Both interfaces support video frame-by-frame LED string intensity control for up to 16 interconnected devices to allow active area dimming. The devices include an advanced PWM engine that easily synchronizes to a video signal, and per-string phase adjustment to reduce unwanted LCD artifacts such as motion blur. Additionally, an on-chip EEPROM allows the power-up defaults to be customized through the serial interface.

The MSL4163/4 adaptively control the DC-DC converters that power the LED strings, using Atmel's Adaptive SourcePower™ technology. These efficiency optimizers minimize power use, while maintaining LED current accuracy.

A unique combination of peak current controls and pulse width management offer simple, full- screen brightness control, versatile area dimming, and a consistent white point. One external resistor sets the global peak reference current for all LED strings, and global peak current fine-tuning is available through an 8-bit register. Global string drive pulse width is adjusted with an 8-bit global intensity register, and individual string pulse width is modulated with 12-bit registers.

The MSL4163/4 feature fault monitoring of open circuit, short circuit, loss of video sync, and over-temperature conditions, and provide a fault output to notify the system controller. Detailed fault status and control are available through the serial interface.

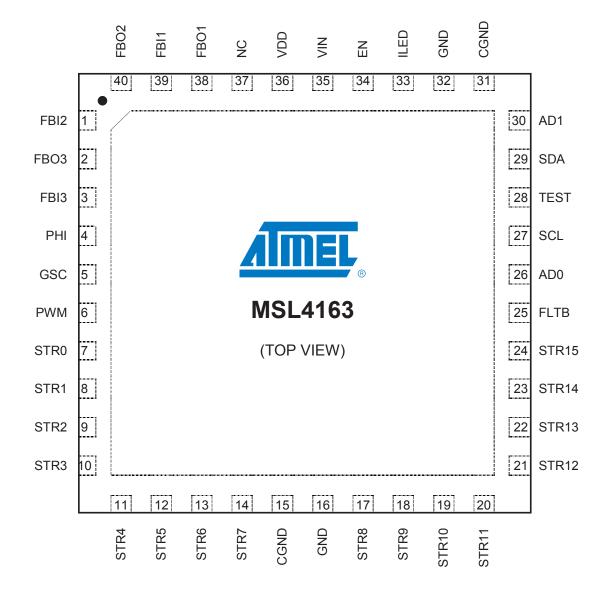

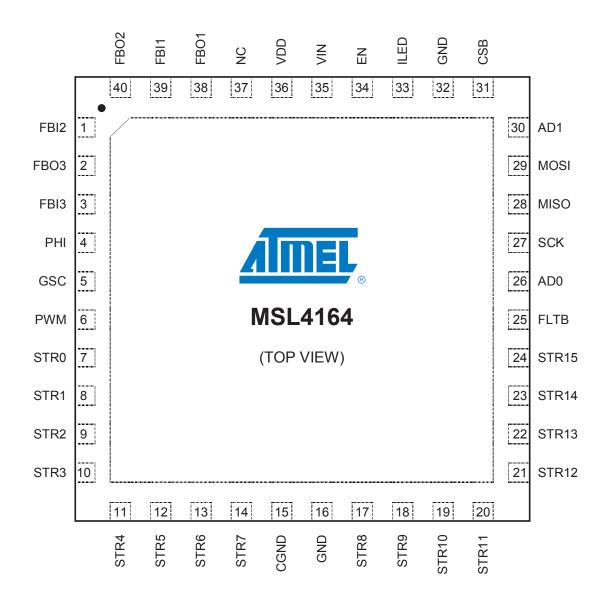

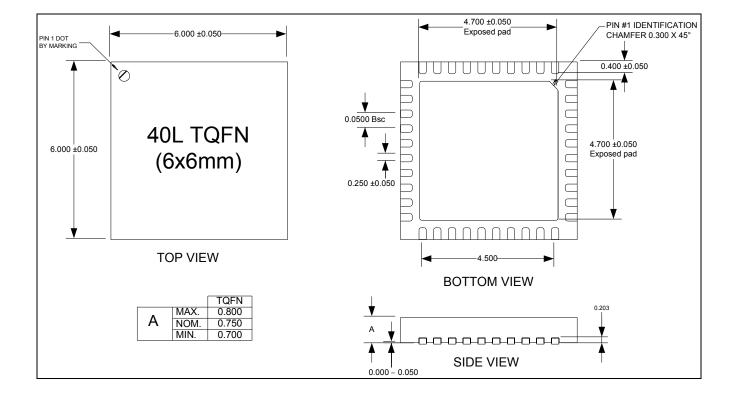

The MSL4163/4 are offered in  $6 \times 6 \times 0.75$ mm, 40-pin TQFN packages and operate over a -40°C to 85°C temperature range.

## Applications

#### Long Life, Efficient LED Backlighting for:

- Televisions and Desktop Monitors

- Medical and Industrial Instrumentation

- Automotive Audio-visual Displays

#### **Channel Signs**

#### Architectural Lighting

### **Ordering Information**

| 16-CHANNEL LED STRING DRIVERS |                  |                             |  |  |  |  |  |  |

|-------------------------------|------------------|-----------------------------|--|--|--|--|--|--|

| PART                          | INTERFACE        | PACKAGE                     |  |  |  |  |  |  |

| MSL4163BT                     | I <sup>2</sup> C | 40-pin, 6 x 6 x 0.75mm TQFN |  |  |  |  |  |  |

| MSL4164BT                     | SPI              | 40-pin, 6 x 6 x 0.75mm TQFN |  |  |  |  |  |  |

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

### **Key Features**

- 12-bit PWM String Dimming Operates at 240Hz

- Fast Serial Interfaces Support up to 16 Devices

per Bus:

- MSL4164: 20MHz SPI

- MSL4163: 1MHz I<sup>2</sup>C

- 8-bit Adaptive Power Correction Maximizes Efficiency of up to Three String Power Supplies

- Drives 16 Parallel LED Strings of 10 White LEDs Each, for up to 2560 White LEDs per Serial Bus

- Supports Adaptive, Real-time Area Dimming for Highest Dynamic Range LCD TVs and Monitors

- Programmable String Phase Reduces Motion Blur

- Global Intensity Control via Serial Interface

- 100mA Peak, 60mA Average LED String Current

- Single Resistor Sets Peak Current for all LED Strings

- ±3% Current Accuracy and Current Balance

- Video Frame (Vsync) and Line (Hsync) Sync Inputs

- Sync Loss Detectors Optionally Disable LED Strings

- Multiple MSL4163/4s Share String Power Supplies and Automatically Negotiate the Optimum Supply Voltage

- EEPROM Allows Customized Power-on Defaults

- Less than 1µa LED String-off Leakage Current

- String Open Circuit and LED Short Circuit Detection with Adjustable Short Circuit Threshold

- Individual Fault Detection Enable for Each String

- Over-temperature Shutoff Protection

- -40°C To +85°C Operating Temperature Range

- 4kv HBM ESD Rated String Drive Outputs

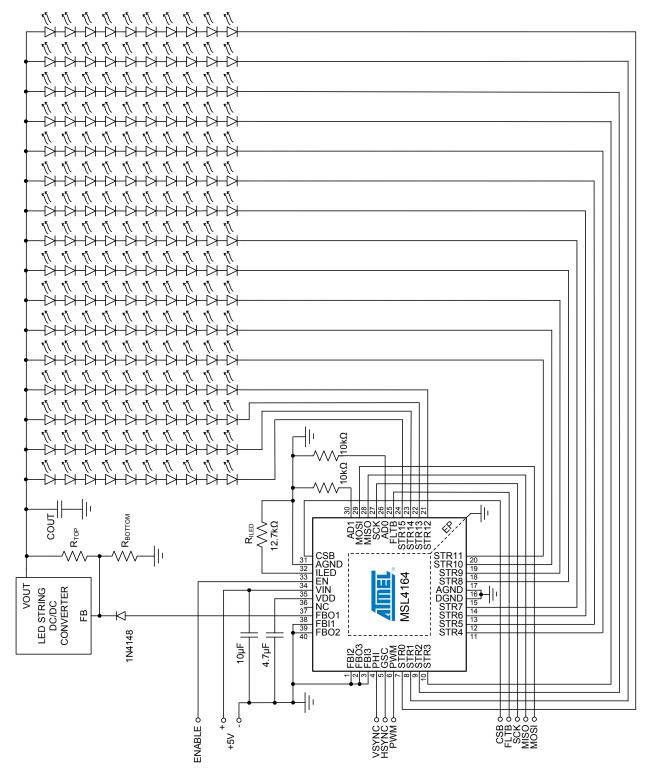

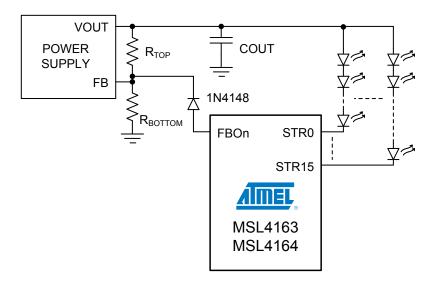

### **Application Circuit**

## Package Pin-out

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

Figure 2. Atmel LED Driver-MSL4164 Pin-out, 40-pin TQFN.

Figure 3. Package Dimensions: 40-pin, 6mm x 6mm x 0.75mm TQFN (0.5mm Pin Pitch) with Exposed Pad.

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

### Package Pin-out

#### Table 1. Pin Descriptions

|                    | PIN                   | IAME                  |                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|-----------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN                | MSL4163               | MSL4164               | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                            |

| 1                  | FBI2                  | FBI2                  | Efficiency Optimizer input 2<br>Connect FBI2 to FBO2 of the next device when chaining devices (Figure 7).<br>If unused, connect FBI2 to GND.                                                                                                                                                                                                                               |

| 2                  | FBO3                  | FBO3                  | Efficiency Optimizer output 3<br>Connect FBO3 to the third power supply's feedback node or to FBI3 of the previous device<br>when chaining devices (Figure 7).<br>If unused, connect FBO3 to GND.                                                                                                                                                                          |

| 3                  | FBI3                  | FBI3                  | Efficiency Optimizer input 3<br>Connect FBI3 to FBO3 of the next device when chaining devices (Figure 7).<br>If unused, connect FBI3 to GND.                                                                                                                                                                                                                               |

| 4                  | PHI                   | PHI                   | Phase synchronization input<br>Drive PHI with an external signal from 40Hz to 10kHz to synchronize the MSL4163/4 clock.<br>PHI is typically the VSYNC signal input.                                                                                                                                                                                                        |

| 5                  | GSC                   | GSC                   | Gate shift clock input<br>Drive GSC with the gate shift clock of the video signal from 0 to 10MHz.<br>GSC is typically the HSYNC signal input.                                                                                                                                                                                                                             |

| 6                  | PWM                   | PWM                   | <b>PWM input</b><br>PWM allows direct external control of the brightness of all LED strings.<br>The PWM input may also be used as a gate signal for the output of the PWM engine.<br>Drive PWM with a pulse-width modulated signal with duty ratio ranging from 0% to 100%<br>and frequency up to 5kHz.<br>When not configured for use as an input, PWM is high impedance. |

| 7 - 14,<br>17 - 24 | STR0<br>thru<br>STR15 | STR0<br>thru<br>STR15 | <b>LED string current sink outputs</b><br>Connect the cathode of the n <sup>th</sup> string's bottom LEDs to STRn.<br>Connect unused STRn outputs to GND.                                                                                                                                                                                                                  |

| 15                 | CGND                  | CGND                  | Connect to ground<br>Connect CGND to GND and to EP with short, wide traces.                                                                                                                                                                                                                                                                                                |

| 16, 32             | GND                   | GND                   | Signal ground<br>Connect all GNDs to system ground and to EP with short, wide traces.                                                                                                                                                                                                                                                                                      |

| 25                 | FLTB                  | FLTB                  | <b>Fault indication output (active low)</b><br>Open drain output FLTB sinks current to GND whenever a fault condition is verified.<br>Toggle EN low or read the fault registers to clear FLTB.<br>Once cleared, FLTB reasserts if the fault conditions persist.                                                                                                            |

| 26,30              | AD0, AD1              | AD0, AD1              | Slave ID selection inputs<br>Connect AD1 and AD0 to GND through resistors to set the device address for the serial interface.                                                                                                                                                                                                                                              |

| 27                 | 50                    | SCK                   | MSL4163: I <sup>2</sup> C serial clock input<br>SCL is the clock input for the I <sup>2</sup> C serial interface.                                                                                                                                                                                                                                                          |

| 21                 | SCL                   | JUN                   | MSL4164: SPI serial shift clock<br>SCK is the clock input for the SPI bus.                                                                                                                                                                                                                                                                                                 |

| 28                 | TEST                  | MISO                  | MSL4163: Factory test I/O<br>Factory test. Make no electrical connection to TEST.                                                                                                                                                                                                                                                                                          |

| 20                 | 1231                  | WISO                  | MSL4164: Master input slave output<br>MISO is the SPI serial data output.                                                                                                                                                                                                                                                                                                  |

#### Table 1. Pin Descriptions

\_\_\_\_

п

| DIN | PIN N   | IAME    |                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | MSL4163 | MSL4164 | PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

|     | 004     | MOGI    | MSL4163: I <sup>2</sup> C serial data I/O<br>SDA is the data I/O for the I <sup>2</sup> C serial interface.                                                                                                                                                                                                                                                                        |

| 29  | SDA     | MOSI    | MSL4164: Master input slave output<br>MOSI is the SPI serial data input.                                                                                                                                                                                                                                                                                                           |

| 31  | GND     | CSB     | <b>MSL4163: Ground.</b><br>Connect GND to system ground and to EP with short, wide traces.                                                                                                                                                                                                                                                                                         |

|     | GND     | 000     | MSL4164: Chip select (active low)<br>CSB is the chip select input for SPI transactions. CSB is active low.                                                                                                                                                                                                                                                                         |

| 33  | ILED    | ILED    | <b>Maximum LED string current setting input</b><br>Connect a resistor from ILED to GND to set the full-scale LED string current for all strings,<br>using $I_{\text{STRING}} = 762 / R_{\text{ILED}}$ .<br>For example, connect a 12.7k $\Omega$ resistor to GND to set a 60mA maximum sink current through<br>each LED string.                                                    |

| 34  | EN      | EN      | <b>Enable input (active high)</b><br>Drive EN high to turn on the MSL4163/4, and drive EN low to turn off the MSL4163/4.<br>For automatic start-up, connect EN to VIN.<br>When EN is low, the entire device, including the serial interface, is turned off.<br>Driving EN high initiates a boot load of the EEPROM data into the control registers,<br>simulating a cold start-up. |

| 35  | VIN     | VIN     | Supply voltage input<br>Connect a 5V supply to VIN.<br>Bypass VIN to GND with a 10µF ceramic capacitor placed close to VIN.                                                                                                                                                                                                                                                        |

| 36  | VDD     | VDD     | <b>2.5V internal LDO regulator output</b><br>VDD powers internal logic.<br>Bypass VDD to GND with a 4.7µF ceramic capacitor placed close to VDD.                                                                                                                                                                                                                                   |

| 37  | NC      | NC      | No connection<br>Leave NC unconnected.                                                                                                                                                                                                                                                                                                                                             |

| 38  | FBO1    | FBO1    | Efficiency Optimizer output 1<br>Connect FBO1 to the first power supply's feedback node or to FBI1 of the previous device<br>when chaining devices (Figure 7).<br>If unused, connect FBO1 to GND.                                                                                                                                                                                  |

| 39  | FBI1    | FBI1    | Efficiency Optimizer input 1<br>Connect FBI1 to FBO1 of the next device when chaining devices (Figure 7).<br>If unused, connect FBI1 to GND.                                                                                                                                                                                                                                       |

| 40  | FBO2    | FBO2    | Efficiency Optimizer output 2<br>Connect FBO2 to the second power supply's feedback node or to FBI2 of the previous<br>device when chaining devices (Figure 7).<br>If unused, connect FBO2 to GND.                                                                                                                                                                                 |

| EP  | EP      | EP      | <b>Exposed pad, power ground</b><br>EP is the path that the string currents take to ground. EP also provides thermal relief for the die.<br>Provide large traces from EP back to the string power supplies.<br>Also connect EP to system ground and to GND using short, wide traces.                                                                                               |

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

### **Absolute Maximum Ratings**

### Voltage (With Respect to GND, CGND = EP = GND) VDD.....-0.3V to +2.75V MSL4163: SDA, SCL ......-0.3V to +6V MSL4164: MISO, MOSI, CSB, SCK ......-0.3V to (VIN + 0.3V) ILED, AD0, AD1.....-0.3V to (VDD + 0.3V) PHI, GSC, PWM, FBO1, FBO2, FBO3, FBI1, FBI2, FBI3......-0.3V to (VIN + 0.3V) Current (Into Pin) EP.....-1700mA **Continuous Power Dissipation** Ambient Operating Temperature Range T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>...... -40°C to +85°C Junction Temperature ...... +125°C Storage Temperature Range...... -65°C to +125°C Lead Soldering Temperature, 10s .....+300°C

### **Electrical Characteristics**

Typical application circuit, VIN = 5V,  $T_A = T_{MIN}$  to  $T_{MAX'}$  unless otherwise noted. Typical values are at VIN = 5V,  $T_A = +25^{\circ}$ C.

| PARAMETER SYMBOL CONDITIONS AND NOT                         |                    |                                                                                         |                             | MIN          | ТҮР   | MAX          | UNIT |

|-------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|-----------------------------|--------------|-------|--------------|------|

| DC ELECTRICAL CHARACTERISTICS                               |                    |                                                                                         |                             |              |       |              |      |

| VIN operating supply voltage                                | VIN                |                                                                                         |                             | 4.75         | 5     | 5.5          | V    |

|                                                             |                    | $ \mathbf{B}_{\text{HED}} -  \mathbf{Z}_{\text{H}} / \mathbf{K} \mathbf{V}_{\text{H}} $ | <sup>p</sup> WMn =<br>)x7FF |              | 18    | 21           |      |

| VIN operating supply current                                | I <sub>vin</sub>   | POWERCTRL = 0x4F,<br>ISTR = 0xFF,<br>OSCCTRL = 0x04,                                    | PWMn =<br>)xFFF             |              | 24    | 27.5         | mA   |

| VIN shutdown supply current                                 | I <sub>SHDN</sub>  | EN = GND, SDA, SCL, AD0,<br>PWM, PHI and GSC = GND                                      |                             | 10           |       | μA           |      |

| VIN sleep current                                           | I <sub>SLEEP</sub> | EN = 1, SLEEP = 1, SDA, SO<br>AD0, AD1, PWM, PHI and<br>GSC = GND or VDD                |                             | 1.5          |       | mA           |      |

| VDD regulation voltage                                      | VDD                |                                                                                         |                             | 2.4          | 2.5   | 2.6          | V    |

| Input high voltage: SDA, SCL, PWM, PHI, GSC, MOSI, CSB, SCK | V <sub>IH</sub>    |                                                                                         |                             | 0.7 x<br>VDD |       |              | V    |

| Input low voltage: SDA, SCL, PWM, PHI, GSC, MOSI, CSB, SCK  | V <sub>IL</sub>    |                                                                                         |                             |              |       | 0.3 x<br>VDD | V    |

| Input high voltage: EN                                      |                    |                                                                                         |                             | 1.22         |       |              | V    |

| Input low voltage: EN                                       |                    |                                                                                         |                             |              |       | 0.8          | V    |

| Output high voltage: PHI, GSC, MISO                         | V <sub>OH</sub>    | I <sub>SOURCE</sub> = 5mA                                                               |                             | VIN –<br>0.4 |       |              | V    |

| Output low voltage:<br>PHI, GSC, SDA, MISO, FLTB            | V <sub>ol</sub>    | I <sub>SINK</sub> = 5mA                                                                 |                             |              |       | 0.4          | V    |

| ILED regulation voltage                                     |                    | $R_{ILED} = 12.7 k\Omega$                                                               |                             |              | 350   |              | mV   |

| FBI feedback input current                                  |                    |                                                                                         |                             | 0            |       | 365          | μA   |

| FBO feedback output current range                           |                    | $V_{FBO} \le VIN - 0.5V$                                                                |                             | 0            |       | 365          | μA   |

| FBO feedback output current step size                       |                    |                                                                                         |                             |              | 1.1   |              | μA   |

| FBI input disable threshold                                 |                    |                                                                                         |                             |              |       | 140          | mV   |

| STR0 thru STR15 sink current                                |                    | $R_{ILED} = 12.7 k\Omega$ , ISTR = 0xFF, V                                              | V <sub>STRn</sub> = 1V      | 55           | 60    | 67           | mA   |

| STR0 thru STR15 sink current maximum                        |                    | $R_{ILED} = 7.68 k\Omega$ , ISTR = 0xFF                                                 | (Note 1)                    |              | 100   |              | mA   |

| STR0 thru STR15 current load regulation                     |                    | $R_{ILED} = 12.7k\Omega; ISTR = 0xFF,$<br>FLDBKEN = 0, V <sub>STRn</sub> = 1V to 5V     |                             |              | 0.033 |              | %/V  |

| STR0 thru STR15 current matching                            |                    | $R_{ILED} = 12.7k\Omega$ , ISTR = 0x7F,                                                 | V <sub>STRn</sub> = 1V      | -5           |       | 5            | %    |

| STR0 thru STR15 minimum headroom                            | V <sub>STR</sub>   | $R_{ILED} = 12.7 k\Omega; ISTR = 0 xFF$                                                 |                             |              | 0.5   |              | V    |

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

| PARAMETER                           | PARAMETER SYMBOL  |                          | MIN | ТҮР   | MAX | UNIT  |  |

|-------------------------------------|-------------------|--------------------------|-----|-------|-----|-------|--|

|                                     |                   | SCTHR = 0x00             |     | 4.5   |     |       |  |

| STR0 thru STR15 short circuit fault | 60                | SCTHR = 0x01             |     | 5.0   |     |       |  |

| detection threshold                 | SC <sub>REF</sub> | SCTHR = 0x02             |     | 5.5   |     | V     |  |

|                                     |                   | SCTHR = 0x03             |     | 6.0   |     |       |  |

| STD0 thru: STD15 surrent close rate |                   | Current rising (Note 2)  |     | 608   |     |       |  |

| STR0 thru STR15 current slew rate   |                   | Current falling (Note 2) |     | 10868 |     | mA/µs |  |

| Thermal shutdown temperature        |                   | (Note 2)                 |     | 135   |     | °C    |  |

| PARAMETER                     | SYMBOL           | CONDITIONS AND NOTES | MIN   | ТҮР   | MAX   | UNIT          |

|-------------------------------|------------------|----------------------|-------|-------|-------|---------------|

| AC ELECTRICAL CHARACTERISTICS |                  |                      |       |       |       |               |

| OSC frequency                 | f <sub>osc</sub> | OSCCTRL = 0x04       | 18.15 | 20.00 | 21.88 | MHz           |

| PHI frequency                 | f <sub>PHI</sub> |                      | 0.04  |       | 10    | kHz           |

| PHI lock                      |                  |                      |       | 4     |       | PHI<br>cycles |

| GSC frequency                 | f <sub>gsc</sub> |                      | 0     |       | 10    | MHz           |

| PWM frequency                 | f <sub>PWM</sub> |                      |       |       | 50    | kHz           |

| PWM duty cycle                |                  |                      | 0     |       | 100   | %             |

| PARAMETER                                       | SYMBOL               | CONDITIONS AND NOTES              | MIN  | TYP                       | MAX  | UNIT |

|-------------------------------------------------|----------------------|-----------------------------------|------|---------------------------|------|------|

| I <sup>2</sup> C TIMING CHARACTERISTICS, MSL416 | 3                    |                                   |      |                           |      |      |

| SCL clock frequency                             | 1/t <sub>scl</sub>   | Bus timeout disabled (Note 3)     | 0    |                           | 1    | MHz  |

| Pup timeout period                              | +                    | OSCCTRL = 0x04                    |      | 30                        |      | ms   |

| Bus timeout period                              | t <sub>imeout</sub>  | f <sub>osc</sub> = 16MHz to 23MHz | 60   | 00,000 / f <sub>osc</sub> |      | s    |

| STOP to START condition bus free time           | t <sub>BUF</sub>     |                                   | 0.5  |                           |      | μs   |

| Repeated START condition hold time              | t <sub>HD:STA</sub>  |                                   | 0.26 |                           |      | μs   |

| Repeated START condition setup time             | t <sub>su:sta</sub>  |                                   | 0.26 |                           |      | μs   |

| STOP condition set-up time                      | t <sub>su:stop</sub> |                                   | 0.26 |                           |      | μs   |

| SDA data hold time                              | t <sub>HD:DAT</sub>  |                                   | 0    |                           |      | ns   |

| SDA data valid acknowledge time                 | t <sub>vD:ACK</sub>  | (Note 4)                          | 0.05 |                           | 0.45 | μs   |

| SDA data valid time                             | t <sub>vd:DAT</sub>  | (Note 5)                          | 0.05 |                           | 0.45 | μs   |

| SDA data set-up time                            | t <sub>SU:DAT</sub>  |                                   | 100  |                           |      | ns   |

| SCL clock low period                            | t <sub>LOW</sub>     |                                   | 0.5  |                           |      | μs   |

| SCL clock high period                           | t <sub>HIGH</sub>    |                                   | 0.26 |                           |      | μs   |

| SDA, SCL fall time                              | t <sub>r</sub>       | (Note 6) (Note 7)                 |      |                           | 120  | ns   |

| SDA, SCL rise time                              | t,                   |                                   |      |                           | 120  | ns   |

| SDA, SCL input suppression filter period        | t <sub>sP</sub>      | (Note 8)                          |      | 50                        |      | ns   |

| PARAMETER                              | SYMBOL                     | CONDITIONS AND NOTES     | MIN | ТҮР | MAX | UNIT |

|----------------------------------------|----------------------------|--------------------------|-----|-----|-----|------|

| SPI TIMING CHARACTERISTICS, MSL410     | 54                         |                          |     |     |     |      |

| SCK frequency                          |                            |                          |     |     | 20  | MHz  |

| CSB to rising edge of SCK set-up time  | t <sub>CSB:SCK(SU)</sub>   |                          | 20  |     |     | ns   |

| Rising edge of SCK to CSB hold time    | t <sub>CSB:SCK(HD)</sub>   |                          | 20  |     |     | ns   |

| MOSI to rising edge of SCK set-up time | t <sub>MOSI(SU)</sub>      |                          | 20  |     |     | ns   |

| Rising edge of SCK to MOSI hold time   | t <sub>MOSI(HD)</sub>      |                          | 20  |     |     | ns   |

| MOSI, CSB, SCK signal rise time        | t <sub>R(SPI)</sub>        | receiving                |     | 5.0 |     | ns   |

| MOSI, CSB, SCK signal fall time        | t <sub>F(SPI)</sub>        | receiving                |     | 5.0 |     | ns   |

| MISO signal rise time                  |                            | C <sub>load</sub> = 10pF |     |     | 20  | ns   |

| MISO signal fall time                  |                            | C <sub>load</sub> = 10pF |     |     | 20  | ns   |

| CSB falling edge to MISO data valid    | t <sub>CSB:MISO(DV)</sub>  |                          |     |     | 50  | ns   |

| CSB rising edge to MISO high impedance | t <sub>CSB:MISO(HIZ)</sub> |                          |     |     | 50  | ns   |

| SCK falling edge to MISO data valid    | t <sub>valid</sub>         |                          |     |     | 20  | ns   |

Note 1. Subject to thermal dissipation characteristics of the device

Note 2. Guaranteed by design, and not production tested.

Note 3. Minimum SCL clock frequency is limited by the bus timeout feature, which resets the serial bus interface if either SDA or SCL is held low for  $t_{imeout}$ . Disable bus timeout via the power control register 0x02[6].

Note 4.  $t_{VDACK}$  = SCL low to SDA (out) low acknowledge time.

Note 5.  $t_{vDDAT}$  = minimum SDA output data-valid time following SCL low transition.

Note 6. A master device must internally provide an SDA hold time of at least 300ns to ensure an SCL low state.

Note 7. The maximum SDA and SCL rise times are 300ns. The maximum SDA fall time is 250ns. This allows series protection resistors to be connected between SDA and SCL inputs and the SDA/SCL bus lines without exceeding the maximum allowable rise time.

Note 8. MSL4163/4 include input filters on SDA, SCL, ADO, and AD1 inputs that suppress noise less than 50ns.

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

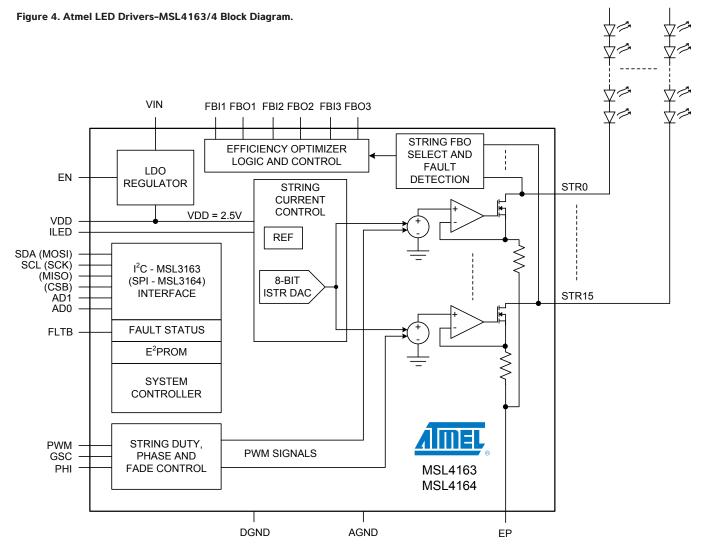

### **Block Diagram**

The block diagram for the MSL4163/4 is shown in Figure 4.

### **Typical Application Circuit**

Figure 5. Atmel LED Driverr-MSL4164 Driving 160 White LEDs in 16 Strings at 60mA per String.

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

### **Detailed Description**

The MSL4163 and MSL4164 are highly integrated, flexible multi-string LED drivers with power supply control to maximize system efficiency. The drivers easily connect to a video subsystem. Although optional, this offers a simple architecture for use in LCD TV backlight applications. Up to 16 drivers easily connect together to drive large numbers of LED strings in a system. The drivers provide multiple methods of controlling LED brightness through both peak current control and pulse width control of the string drive signals. Peak current control offers excellent color consistency, while pulse width control allows brightness management. An onchip EEPROM holds all the default control register values. At power-up, the data in the EEPROM are automatically copied directly to the control registers, setting up the device for operation.

The devices interface to an MCU via I<sup>2</sup>C (MSL4163) or SPI (MSL4164). The robust, 1MHz I<sup>2</sup>C interface supports up to 16 devices on the bus. The 20MHz bus addressable SPI bus supports up to 16 devices per chip select line. While typically the LED drive PWM signal is internally generated, both drivers also accept an external, direct-drive PWM signal and offer optional string drive phase spreading. With direct-drive PWIM, a pulse width modulated signal applied to the PWM input sets the PWM duty cycle and the frequency of the LED drive signal. With phase spreading enabled, a progressive 1/16 PWM-frame time delay per string helps reduce both the transient load on the LED power supplies and the power supply input capacitor size requirements.

The PWM frequency of the drivers is either synchronized to an external signal applied to PHI or generated from the internal oscillator for standalone applications. Typically, the VSYNC signal from the video system is used for the PHI input. The on time of each string is individually programmed via the device registers, providing a peak resolution of 12 bits when using the on-chip PWM generator. The actual resolution of the PWM frequency depends on the ratio of the GSC frequency (typically provided by a system's HSYNC signal, but can be internally generated) to the PHI frequency, because the on time of a string is programmed as a 12-bit count of the number of GSC clock cycles. This count can be further scaled by an 8-bit global intensity value, when enabled. The GSC clock is also used to precisely set each string's phase delay so that it is synchronized relative to the video frame.

The efficiency optimizers control a wide range of external DC-DC and AC-DC converter architectures. Multiple drivers in a system communicate with each other in real time to select an optimized operating voltage for the LEDs. This allows design of the power supply for the worst case forward voltage ( $V_r$ ) of the LEDs without concern about excessive power dissipation issues. During the start-up sequence, the MSL4163/4 automatically reduce the power supply voltage to the minimum voltage required to keep the LEDs in current regulation. The devices can be configured to periodically perform this optimization to compensate for changes in the LED forward voltage, and to assure continued optimum power savings.

#### Internal Regulators and Enable Input

The MSL4163/4 includes an internal linear regulator that operates from the 5V nominal input supply, VIN, and provides an internal 2.5V supply, VDD, to power the low-voltage internal circuitry. Bypass VDD (pin 36) to GND with a  $4.7\mu$ F capacitor. Bypass VIN (pin 35) to GND with a 10 $\mu$ F capacitor.

The MSL4163/4 enable input, EN, enables the device. Drive EN low to enter low power operation, which lowers quiescent current draw to less than 20µA. With EN low, the serial interface is ignored. Drive EN high to turn on the device. When EN is driven high, the contents of the EEPROM are boot loaded into the control registers, simulating a cold start-up.

### Setting the LED String Current with $\mathrm{R}_{_{\mathrm{LED}}}$ and ISTR

The MSL4163/4 features 16 current sink outputs rated at 40V, each designed to sink up to 100mA peak. Limit average current to 60mA if the PCB copper around the MSL4163/4 is the only heat sink employed. The maximum string current,  $I_{ILED}$ , for all 16 LED string inputs is set by a single external resistor,  $R_{ILED}$ , placed from ILED to GND, whose value is determined using:

$$R_{ILED} = \frac{762}{I_{ILED}}.$$

For example, a full-scale LED current of 60mA returns  $R_{ILED} = 12.7 k\Omega$ . The current for all LED strings is reduced from its full-scale value with 8-bit resolution using ISTR, the string current control register, 0x0F.

#### Figure 6. FBOn Connects to the Power Supply Voltage Divider through a Diode.

#### Connecting the Efficiency Optimizer to an LED String Power Supply and Selecting Resistors

The MSL4163/4 are designed to control LED string power supplies that use a voltage divider ( $R_{TOP}$  and  $R_{BOTTOM}$  in Figure 6) to set output voltage, and whose regulation feedback voltage is not more than 3.5V. The efficiency optimizer improves power efficiency by injecting a current of between 0 and 255µA into the voltage divider of the external power supply, dynamically adjusting the power supply's output to the minimum voltage required by the LED strings. To select the resistors, first determine  $V_{OUT(MIN)}$  and  $V_{OUT(MAX)'}$  the minimum and maximum string supply voltage limits, using:

$$V_{OUT(MIN)} = (V_{f(MIN)} * [\#ofLEDs]) + 0.5$$

, and

$$V_{OUT(MAX)} = (V_{f(MAX)} * [\# of LEDs]) + 0.5$$

#### 16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

where  $V_{f(MN)}$  and  $V_{f(MAX)}$  are the LEDs' minimum and maximum forward voltage drops at the peak current set by  $R_{ILED}$  (page 10). For example, if the LED data are  $V_{f(MN)} = 3.5$ V and  $V_{f(MAX)} = 3.8$ V, and 10 LEDs are used in a string, then the total minimum and maximum voltage drops across the LEDs are 35V and 38V, respectively. Adding an allowance of 0.5V to the string drive MOSFET headroom brings  $V_{OUT(MIN)}$  to 35.5V and  $V_{OUT(MAX)}$  to 38.5V. Do not to exceed the 40V maximum specification of string drivers STR1 – STR15. Then, determine  $R_{TOP}$  using:

$$R_{TOP} = \frac{V_{OUT(MAX)} - V_{OUT(MIN)}}{I_{FBOn(MAX)}},$$

where  $I_{FBOn(MAX)}$  is the 255µA maximum output current of the efficiency optimizer outputs, FBOn (if cascading multiple MSL4163/4s determine  $I_{FBOn(MAX)}$  as shown in the next section). Finally, determine  $R_{BOTTOM}$  using:

$$R_{BOTTOM} = R_{TOP} * \frac{V_{FB}}{V_{OUT(MAX)} - V_{FB}},$$

where  $V_{FB}$  is the regulation feedback voltage of the power supply. Place a diode (1N4148 or similar) between FBOn and the supply's feedback node to protect the MSL4163/4 against current flow into FBOn.

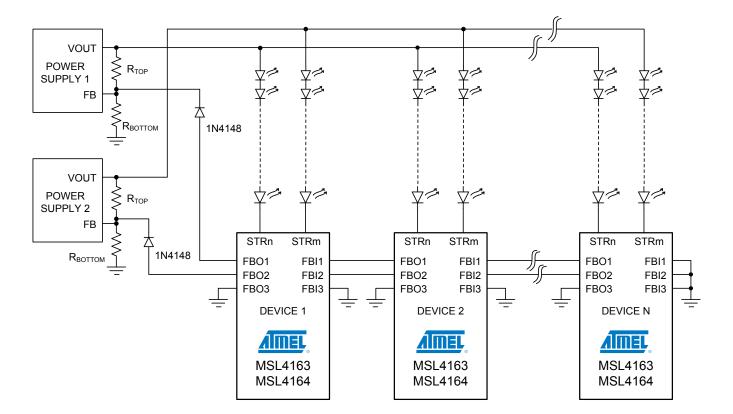

#### Using Multiple Atmel LED Drivers-MSL4163/4s to Control a Common Power Supply

Cascade multiple MSL4163/4 devices into a chain configuration, with the FBIn of one device connected to the FBOn of the next (Figure 7). Connect the first FBOn to the power supply feedback resistor node through a diode and the unused FBIn inputs (and any unused FBOn outputs) to GND as close to the MSL4163/4 as possible. Assign all strings powered by a common supply to the proper FBOn output using string set registers (STRnSET) 0x20 - 0x3F. The chained devices work together to ensure that the system operates at optimum efficiency. Note that the accuracy of the feedback chain may degrade through each link of the FBIn/FBOn chain by as much as 2%. Determine the potential worst case maximum FBOn current I<sub>EBOn(MAX/MNN)</sub> using:

$$I_{FBOn (MAX/MIN)} = 225 A^* (0.98)^{N-1} ,$$

where N is the number of MSL4163/4s connected in series. Use this result in the above  $R_{TOP}$  resistor equation for the term  $I_{FBOn(MAX)}$  instead of using 255µA.

Take care in laying out the traces for the efficiency optimizer connections. Minimize the FBIn/FBOn trace lengths as much as possible. Do not route the signals close to traces with large variations in voltage or current, because noise may couple into FBIn. If these traces must be routed near noisy signals, shield them from noise by using ground planes or guard traces.

Figure 7. Example of Cascading Multiple Devices to Optimize Common Power Supplies.

#### Direct PWM Control of the LED Strings

An external PWM signal applied to the PWM input allows direct PWM control over the strings when bits PWMEN and PWMDIRECT are set in PWM control register, 0x1E. This configuration bypasses PHI and GSC, but allows automatic LED string phase delay using bit D2 of register 0x1E.

The PWM input can also be configured as a gate for the output of the PWM engine using the PWM global enable bit D3 of the PWM control register, 0x1E.

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

### Register Map and the EEPROM

#### Register Map Summary

The MSL4163/4 controlled using the 96 registers in the range 0x00 – 0x5F (Table 2). It may be convenient, and it is allowed, to read and write to unused bits in this range when accessing registers, but always write zeros. Reads from unused bits always return zeros. Three additional registers, 0x90, 0x91, and 0x93, allow access to the EEPROM and provide efficiency optimizer status. The power-up default values for all control registers are stored within the on-chip EEPROM, and any of these EEPROM values may be changed through the serial interface.

#### Table 2. Atmel LED Drivers-MSL4163/4 Register Map

| AD   | DRESS AND  | FUNCTION                        |                |                      |           | REGIS     | TER DATA  |                      |                   |          |  |

|------|------------|---------------------------------|----------------|----------------------|-----------|-----------|-----------|----------------------|-------------------|----------|--|

| REG  | ISTER NAME | FUNCTION                        | D7             | D6                   | D5        | D4        | D3        | D2                   | D1                | D0       |  |

| 0x00 | CONTROL0   | LED string                      | STR7EN         | STR6EN               | STR5EN    | STR4EN    | STR3EN    | STR2EN               | STR1EN            | STR0EN   |  |

| 0x01 | CONTROL1   | enables                         | STR15EN        | STR14EN              | STR13EN   | STR12EN   | STR11EN   | STR10EN              | STR9EN            | STR8EN   |  |

| 0x02 | POWERCTRL  | Fault configuration             | SLEEP          | I <sup>2</sup> CTOEN | PHIMINFEN | GSCMAXFEN | STRSCFEN  | STROCFEN             | FBOOCEN           | FBOEN    |  |

| 0x03 | FLTSTATUS  | Fault status,<br>global         | -              | -                    | PHIMINFLT | GSCMAXFLT | STRSCDET  | STROCDET             | FBOOC             | FLTDET   |  |

| 0x04 | OCSTAT0    | String open                     | OC7            | OC6                  | OC5       | OC4       | OC3       | OC2                  | OC1               | OC0      |  |

| 0x05 | OCSTAT1    | circuit fault<br>status         | OC15           | OC14                 | OC13      | OC12      | OC11      | OC10                 | OC9               | OC8      |  |

| 0x06 | SCSTAT0    | String short                    | SC7            | SC6                  | SC5       | SC4       | SC3       | SC2                  | SC1               | SC0      |  |

| 0x07 | SCSTAT1    | circuit fault<br>status         | SC15           | SC14                 | SC13      | SC12      | SC11      | SC10                 | SC9               | SC8      |  |

| 0x08 | FLTMASK0   | String fault                    | FLTEN7         | FLTEN6               | FLTEN5    | FLTEN4    | FLTEN3    | FLTEN2               | FLTEN1            | FLTEN0   |  |

| 0x09 | FLTMASK1   | masks                           | FLTEN15        | FLTEN14              | FLTEN13   | FLTEN12   | FLTEN11   | FLTEN10              | FLTEN9            | FLTEN8   |  |

| 0x0A | FBOCTRL0   | Efficiency                      | HDRMS          | TEP[1:0]             | FBCL      | DLY[1:0]  | FBSD      | LY[1:0] FBCFDLY[1:0] |                   |          |  |

| 0x0B | FBOCTRL1   | optimizer<br>control            | SCCD           | LY[1:0]              | DECR      | STEP[1:0] | INITPWM   | ACAL100              | ACALEN            | ICHKDIS  |  |

| 0x0C | FBODAC1    | Efficiency                      |                |                      |           | FBOD      | DAC1[7:0] |                      |                   |          |  |

| 0x0D | FBODAC2    | optimizer DAC                   |                |                      |           | FBOD      | DAC2[7:0] |                      |                   |          |  |

| 0x0E | FBODAC3    | readback                        |                |                      |           | FBOD      | DAC3[7:0] |                      |                   |          |  |

| 0x0F | ISTR       | 8-bit global string current     |                |                      |           | IST       | FR[7:0]   |                      |                   |          |  |

| 0x10 | OSCCTRL    | Oscillator<br>frequency         | -              | -                    | -         | -         | -         |                      | OSCTRL[2:0]       |          |  |

| 0x11 | GSCCTRL    | GSC<br>processing<br>control    | GSCCHK-<br>SEL | -                    | -         | -         | GSCMAXEN  | GSCPOL               | GSCPHI-<br>SYNCEN | GSCINTEN |  |

| 0x12 |            | Internal                        |                |                      |           | GSC       | GEN[7:0]  |                      |                   |          |  |

| 0x13 | GSCGEN     | GSC clock<br>generator          |                |                      |           | GSCO      | GEN[15:8] |                      |                   |          |  |

| 0x14 | GSCMUL     | GSC multiplier                  | -              | -                    | -         |           |           | GSCMUL[4:0]          |                   |          |  |

| 0x15 | GSCDIV     | GSC divider                     | -              | -                    | -         | _         |           | GSCD                 | IV[3:0]           |          |  |

| 0x16 |            | Max oscillator                  |                |                      |           | GSC       | MAX[7:0]  | · · · · · · · · ·    |                   |          |  |

| 0x17 | GSCMAX     | cycles<br>between GSC<br>pulses |                |                      |           | GSCN      | MAX[15:8] |                      |                   |          |  |

#### Table 2. Atmel LED Drivers-MSL4163/4 Register Map

| ADI               | DRESS AND              | FUNCTION                                                                                       |                |                          |                                    | REG                             | ISTER DATA                                        | STER DATA      |                |          |  |  |  |

|-------------------|------------------------|------------------------------------------------------------------------------------------------|----------------|--------------------------|------------------------------------|---------------------------------|---------------------------------------------------|----------------|----------------|----------|--|--|--|

| REG               | ISTER NAME             | FUNCTION                                                                                       | D7             | D6                       | D5                                 | D4                              | D3                                                | D2             | D1             | D0       |  |  |  |

| 0x18              | PHICTRL                | PHI<br>processing<br>control                                                                   | -              | -                        | -                                  | -                               | -                                                 | PHIMINEN       | PHIPOL         | PHIINTEN |  |  |  |

| 0x19              |                        | Internal PHI                                                                                   |                |                          |                                    | PH                              | IIGEN[7:0]                                        |                |                | •        |  |  |  |

| 0x1A              | PHIGEN                 | clock<br>generator                                                                             |                |                          |                                    | PH                              | IGEN[15:8]                                        |                |                |          |  |  |  |

| 0x1B              | UNUSE                  | D                                                                                              | ,              |                          |                                    |                                 |                                                   | UNUSE          | Ð              |          |  |  |  |

| 0x1C              |                        | Min GSC                                                                                        |                |                          |                                    | Pł                              | HIMIN[7:0]                                        |                |                |          |  |  |  |

| 0x1D              | PHIMIN                 | pulses over<br>PHI period                                                                      | -              | -                        | -                                  | -                               | PHIMIN[11:8]                                      |                |                |          |  |  |  |

| 0x1E              | PWMCTRL                | PWM control                                                                                    | FLDBKEN        | -                        | GINTEN                             | PWM-<br>OFLOWEN                 | PWMGLBLEN PHA-<br>DLYEN                           |                | PWM-<br>DIRECT | PWMEN    |  |  |  |

| 0x1F              | GINT                   | Global PWM scaling                                                                             |                |                          |                                    | (                               | GINT[7:0]                                         |                |                |          |  |  |  |

| 0x20              |                        | Phase delay                                                                                    |                |                          |                                    | PH                              | IDLY0[7:0]                                        |                |                |          |  |  |  |

| 0x21              | STR0SET                | and EO<br>assignment<br>for string 0                                                           | COLST          | R0[1:0]                  | -                                  | -                               | PHDLY[11:8]                                       |                |                |          |  |  |  |

| ↓                 | Ļ                      | Ļ                                                                                              |                |                          |                                    |                                 | Ļ                                                 |                |                |          |  |  |  |

| 0x3E              |                        | Phase delay                                                                                    |                |                          |                                    | PH                              | DLY15[7:0]                                        |                |                |          |  |  |  |

| 0x3F              | STR15SET               | and EO<br>assignment<br>for string 15                                                          | COLSTI         | R15[1:0]                 | -                                  | -                               |                                                   | PHDL           | Y[11:8]        |          |  |  |  |

| 0x40              |                        | 12-bit                                                                                         |                |                          | •                                  |                                 |                                                   |                |                |          |  |  |  |

| 0x41              | PWM0                   |                                                                                                |                |                          |                                    | P                               | WM0[7:0]                                          |                |                |          |  |  |  |

|                   |                        | PWM setting<br>for string 0                                                                    | -              | -                        | -                                  | ۲<br>-                          | WM0[7:0]                                          | PWM0           | [11:8]         |          |  |  |  |

| ↓                 |                        |                                                                                                | -              | -                        | -                                  | ۲<br>-                          | WM0[7:0]<br>↓                                     | PWM0           | [11:8]         |          |  |  |  |

| ↓<br>0x5E         | ↓<br>DW4445            | for string 0<br>↓<br>12-bit                                                                    | -              | -                        | -                                  | -                               | WM0[7:0]<br>↓<br>VM15[7:0]                        | PWM0           | 11:8]          |          |  |  |  |

| ↓<br>0x5E<br>0x5F | ↓<br>PWM15             | for string 0<br>↓                                                                              | -              | -                        | -                                  | -                               | Ļ                                                 | PWM0 <br>PWM15 | -              |          |  |  |  |

|                   | ↓<br>PWM15             | for string 0<br>↓<br>12-bit<br>PWM setting                                                     | -<br>-<br>- D0 | -<br>-<br>NOT ACCE       | -<br>-<br>SS ADDRESS               | -<br>P\<br>-                    | ↓<br>VM15[7:0]                                    |                | -              |          |  |  |  |

|                   | ↓<br>PWM15<br>SCTHRESH | for string 0<br>↓<br>12-bit<br>PWM setting                                                     | -<br>-<br>- DO | -<br>-<br>NOT ACCE:<br>- | -<br>SS ADDRESS                    | -<br>P\<br>-                    | ↓<br>VM15[7:0]                                    |                | [11:8]         | HR[0:1]  |  |  |  |

| 0x5F              |                        | for string 0<br>12-bit<br>PWM setting<br>for string 15<br>Short circuit                        | -              | -                        | -<br>SS ADDRESS<br>-<br>SS ADDRESS | -<br>P\<br>-<br>RANGE 0X60<br>- | ↓<br>VM15[7:0]<br>THRU 0X73 -<br>-                |                | [11:8]         | HR[0:1]  |  |  |  |

| 0x5F              |                        | for string 0<br>12-bit<br>PWM setting<br>for string 15<br>Short circuit<br>threshold<br>EEPROM | -              | -                        | -                                  | -<br>P\<br>-<br>RANGE 0X60<br>- | ↓<br>VM15[7:0]<br>THRU 0X73 -<br>-                |                | [11:8]         | HR[0:1]  |  |  |  |

| 0x5F<br>0x74      | SCTHRESH               | for string 0<br>12-bit<br>PWM setting<br>for string 15<br>Short circuit<br>threshold           | -              | -                        | -                                  | -<br>P\<br>-<br>RANGE 0X60<br>- | ↓<br>VM15[7:0]<br>THRU 0X73 -<br>-<br>THRU 0X8F - |                | [11:8]         |          |  |  |  |

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

#### Register Power-Up Defaults

Register power-up default values are shown in Table 3.

#### Table 3. Atmel LED Drivers-MSL4163/4 Register Power-up Defaults

| REG  | ISTER NAME |                                                                                                                                                                                                                                                                                                                        |    |    | F  | REGIST | ER DA1 | A  |    |    |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|--------|--------|----|----|----|

| AN   | DADDRESS   | POWER-UP CONDITION                                                                                                                                                                                                                                                                                                     | D7 | D6 | D5 | D4     | D3     | D2 | D1 | D0 |

| 0x00 | CONTROL0   | LED strings STR0 thru STR7 enabled                                                                                                                                                                                                                                                                                     | 1  | 1  | 1  | 1      | 1      | 1  | 1  | 1  |

| 0x01 | CONTROL1   | LED Strings STR8 thru STR15 Enabled                                                                                                                                                                                                                                                                                    | 1  | 1  | 1  | 1      | 1      | 1  | 1  | 1  |

| 0x02 | POWERCTRL  | Efficiency optimizer outputs enabled<br>FBO open circuit detection enabled<br>String open circuit detection enabled<br>LED short circuit detection enabled<br>GSC maximum fault detection disabled<br>PHI minimum fault detection disabled<br>I <sup>2</sup> C bus timeout detection enabled<br>Device awake           | 0  | 1  | 0  | 0      | 1      | 1  | 1  | 1  |

| 0x08 | FLTMASK0   |                                                                                                                                                                                                                                                                                                                        |    | 1  | 1  | 1      | 1      | 1  | 1  | 1  |

| 0x09 | FLTMASK1   | Fault detection enabled on all strings                                                                                                                                                                                                                                                                                 | 1  | 1  | 1  | 1      | 1      | 1  | 1  | 1  |

| 0x0A | FBOCTRL0   | Current sink error confirmation delay = 4µS<br>FBO power supply correction delay = 2ms<br>Efficiency optimizer recalibration delay = 1s                                                                                                                                                                                | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  |

| 0x0B | FBOCTRL1   | Efficiency optimizer correction steps = 6<br>Current sink error detection not disabled<br>auto recalibration enabled<br>PWM settings used during auto recalibration<br>PWM duty cycle = 100% during initial calibration<br>Efficiency optimizer operates using 1µA steps<br>LED short circuit confirmation delay = 4µs | 0  | 0  | 0  | 1      | 0      | 0  | 1  | 0  |

| 0x0F | ISTR       | Strings current set to 50% of R <sub>ILED</sub> setting                                                                                                                                                                                                                                                                | 0  | 1  | 1  | 1      | 1      | 1  | 1  | 1  |

| 0x10 | OSCCTRL    | f <sub>osc</sub> = 20MHz                                                                                                                                                                                                                                                                                               | 0  | 0  | 0  | 0      | 0      | 1  | 0  | 0  |

| 0x11 | GSCCTRL    | GSC synchronized to the falling edge of the external signal                                                                                                                                                                                                                                                            | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  |

| 0x12 | GSCGEN     | Although disabled, internal GSC frequency                                                                                                                                                                                                                                                                              | 0  | 0  | 0  | 1      | 0      | 0  | 1  | 1  |

| 0x13 | GOUGEN     | = 20MHz / (19 + 1) = 1MHz                                                                                                                                                                                                                                                                                              | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  |

#### Table 3. Atmel LED Drivers-MSL4163/4 Register Power-up Defaults

| REG  | ISTER NAME |                                                                                                                                                                                                                                                                                     |    |    | F  | REGIST | ER DAI | ΓA |    |    |

|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|--------|--------|----|----|----|

| AN   | DADDRESS   | POWER-UP CONDITION                                                                                                                                                                                                                                                                  | D7 | D6 | D5 | D4     | D3     | D2 | D1 | D0 |

| 0x14 | GSCMUL     | GSC multiplied by 4                                                                                                                                                                                                                                                                 | 0  | 0  | 0  | 0      | 0      | 0  | 1  | 1  |

| 0x15 | GSCDIV     | GSC not divided                                                                                                                                                                                                                                                                     | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  |

| 0x16 | 000141     | Although disabled, GSC max count is set                                                                                                                                                                                                                                             | 0  | 0  | 0  | 1      | 0      | 0  | 1  | 1  |

| 0x17 | GSCMAX     | to 19 clock cycles                                                                                                                                                                                                                                                                  | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  |

| 0x18 | PHICTRL    | PHI synchronized to the falling edge of the external signal                                                                                                                                                                                                                         |    | 0  | 0  | 0      | 0      | 0  | 0  | 0  |

| 0x19 | DUIOEN     | Although disabled, internal PHI frequency                                                                                                                                                                                                                                           |    | 0  | 1  | 1      | 0      | 0  | 0  | 0  |

| 0x1A | PHIGEN     | = 20MHz / (8 * (10416 + 1)) = 240Hz                                                                                                                                                                                                                                                 | 0  | 0  | 1  | 0      | 1      | 0  | 0  | 0  |

| 0x1C |            |                                                                                                                                                                                                                                                                                     | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  |

| 0x1D | PHIMIN     | No PHI minimum                                                                                                                                                                                                                                                                      | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  |

| 0x1E | PWMCTRL    | PWM operation enabled<br>Internal PWM engine determines t <sub>oN</sub> and t <sub>OFF</sub><br>Phase delay enabled<br>PWM input not used as gate for PWM engine output<br>String on times allowed to extend beyond<br>PWM frame<br>GINT ignored<br>String current foldback enabled | 1  | 0  | 0  | 1      | 0      | 1  | 0  | 1  |

| 0x1F | GINT       | Although disabled, global intensity is set to (127) / 256 = 49.6%                                                                                                                                                                                                                   | 0  | 1  | 1  | 1      | 1      | 1  | 1  | 1  |

| 0x20 | OTDOOFT    |                                                                                                                                                                                                                                                                                     | 0  | 0  | 0  | 0      | 0      | 0  | 0  | 0  |

| 0x21 | STR0SET    | All strings set to zero phase delay                                                                                                                                                                                                                                                 | 0* | 1* | 0  | 0      | 0      | 0  | 0  | 0  |

| ↓    | Ļ          | Strings efficiency optimizer assignments are:<br>FBO1: Strings 0,4,8,12<br>FBO2: Strings 1,2,5,6,9,10,13,14<br>FBO3: Strings 3, 7, 11, 15                                                                                                                                           |    |    |    |        | Ļ      |    |    |    |

| 0x3E | STR15SET   |                                                                                                                                                                                                                                                                                     |    | 0  | 0  | 0      | 0      | 0  | 0  | 0  |

| 0x3F |            |                                                                                                                                                                                                                                                                                     | 1* | 1* | 0  | 0      | 0      | 0  | 0  | 0  |

16-string, White and RGB LED Drivers with Adaptive Power Control, EEPROM, and SPI/I<sup>2</sup>C/SMBus Serial Interface

| REGISTER NAME<br>AND ADDRESS |           | POWER-UP CONDITION                          | REGISTER DATA |    |    |    |    |    |    |    |

|------------------------------|-----------|---------------------------------------------|---------------|----|----|----|----|----|----|----|

|                              |           |                                             | D7            | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| 0x40                         | PWM0      | All strings have PWM value = 512 GSC cycles | 0             | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0x41                         |           |                                             | 0             | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| ↓                            |           |                                             | $\downarrow$  |    |    |    |    |    |    |    |

| 0x5E                         | PWM15     |                                             | 0             | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0x5F                         |           |                                             | 0             | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| 0x74                         | SCTHRESH  | SC <sub>REF</sub> = 6.0V                    | 0             | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 0x90                         | E2ADDR    | EEPROM 7-bit address = 0x00                 | 0             | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0x91                         | E2CTRLSTA | EEPROM read/write disabled                  | 0             | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 0x93                         | FBOSTATUS | Feedback output status                      | 0             | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

\* These bits set the FBOn string assignments.

#### Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA **Tel:** (+1)(408) 441-0311 **Fax:** (+1)(408) 487-2600 www.atmel.com

#### Atmel Asia Limited

Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG **Tel:** (+852) 2245-6100 **Fax:** (+852) 2722-1369

#### Atmel Munich GmbH

Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg, 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 JAPAN **Tel:** (+81)(3) 3523-3551 **Fax:** (+81)(3) 3523-7581

© 2011 Atmel Corporation. All rights reserved. / Rev.: MEM-MSL4163/64DB1-E-US\_06-11

Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE. ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUIDINS, BUT NOT LIMITED TO., THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFINIGEMENT. IN NO EVENT SHALL ATMELE BE CRANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARSING OUT OF THE USE OR INABILITY OF USE THIS DOCUMENT, EVEN IF ATMEL ASSUMES TO STATUTORY OR MERCINA. THE ATMEL WEBSITE ATMEL ASSUMES TOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARSING OUT OF THE USE OR INABILITY OF USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not sitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.