# **5 V ECL 1:6 Differential Clock Distribution Chip**

## Description

The MC10E/100E211 is a low skew 1:6 fanout device designed explicitly for low skew clock distribution applications.

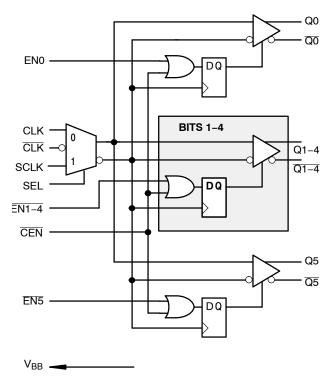

The E211 features a multiplexed clock input to allow for the distribution of a lower speed scan or test clock along with the high speed system clock. When LOW (or left open in which case it will be pulled LOW by the input pulldown resistor) the SEL pin will select the differential clock input.

Both a common enable and individual output enables are provided. When asserted the positive output will go LOW on the next negative transition of the CLK (or SCLK) input. The enabling function is synchronous so that the outputs will only be enabled/disabled when the outputs are already in the LOW state. In this way the problem of runt pulse generation during the disable operation is avoided. Note that the internal flip flop is clocked on the falling edge of the input clock edge, therefore all associated specifications are referenced to the negative edge of the CLK input.

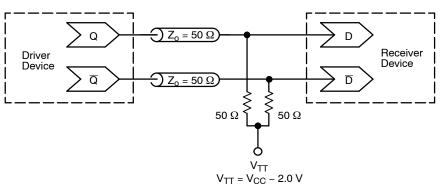

The output transitions of the E211 are faster than the standard ECLinPS edge rates. This feature provides a means of distributing higher frequency signals than capable with the E111 device. Because of these edge rates and the tight skew limits guaranteed in the specification, there are certain termination guidelines which must be followed. For more details on the recommended termination schemes please refer to the applications information section of this data sheet.

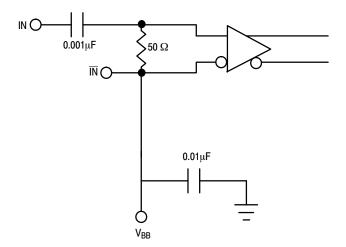

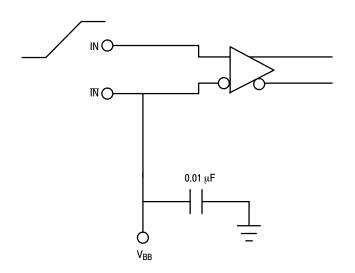

The V<sub>BB</sub> pin, an internally generated voltage supply, is available to this device only. For single-ended input conditions, the unused differential input is connected to V<sub>BB</sub> as a switching reference voltage. V<sub>BB</sub> may also rebias AC coupled inputs. When used, decouple V<sub>BB</sub> and V<sub>CC</sub> via a 0.01  $\mu$ F capacitor and limit current sourcing or sinking to 0.5 mA. When not used, V<sub>BB</sub> should be left open.

The 100 Series contains temperature compensation.

## Features

- Guaranteed Low Skew Specification

- Synchronous Enabling/Disabling

- Multiplexed Clock Inputs

- V<sub>BB</sub> Output for Single-Ended Use

- Common and Individual Enable/Disable Control

- High Bandwidth Output Transistors

- PECL Mode Operating Range:

- $V_{CC} = 4.2 \text{ V}$  to 5.7 V with  $V_{EE} = 0 \text{ V}$

- NECL Mode Operating Range:

- $V_{CC} = 0$  V with  $V_{EE} = -4.2$  V to -5.7 V

- Internal Input 75 kΩ Pulldown Resistors

- ESD Protection:

- Human Body Model; > 2 kV

- Machine Model; > 100 V

## **ON Semiconductor®**

www.onsemi.com

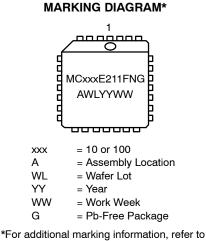

PLCC-28 FN SUFFIX CASE 776-02

\*For additional marking information, refer to Application Note <u>AND8002/D</u>.

## **ORDERING INFORMATION**

| Device       | Package              | Shipping <sup>†</sup> |

|--------------|----------------------|-----------------------|

| MC10E211FNG  | PLCC-28<br>(Pb-Free) | 37 Units/Tube         |

| MC100E211FNG | PLCC-28<br>(Pb-Free) | 37 Units/Tube         |

- Meets or Exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

- Moisture Sensitivity Level: 3 (Pb-Free)

- For Additional Information, see Application Note <u>AND8003/D</u>

- Flammability Rating:

- UL 94 V-0 @ 0.125 in, Oxygen Index: 28 to 34

- Transistor Count = 457 devices

- These Devices are Pb-Free, Halogen Free and are RoHS Compliant

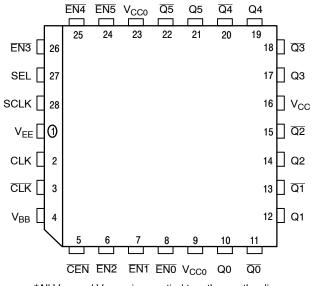

\*All  $V_{CC}$  and  $V_{CCO}$  pins are tied together on the die.

Warning: All  $V_{CC},\,V_{CCO},\,$  and  $V_{EE}$  pins must be externally connected to Power Supply to guarantee proper operation.

Figure 1. Pinout: PLCC-28 (Top View)

Figure 2. Logic Diagram

#### Table 1. PIN DESCRIPTION

| PIN                                                                                                                                                | FUNCTION                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{c} EN0-EN5\\ SEL\\ SCLK\\ CLK, CLK\\ CEN\\ Q0-Q5, \overline{Q0}-\overline{Q5}\\ V_{BB}\\ V_{CC}, V_{CCO}\\ V_{EE}\\ NC \end{array}$ | ECL Enable<br>ECL Select (Clock)<br>ECL Single Clock<br>ECL Differential Clock<br>ECL Common Enable<br>ECL Differential Outputs<br>Reference Voltage Output<br>Positive Supply<br>Negative Supply<br>No Connect |

Table 2. FUNCTION TABLE

| CLK | SCLK | SEL | ENx | Q    |

|-----|------|-----|-----|------|

| H/L | X    | L   | L   | CLK  |

| X   | H/L  | H   | L   | SCLK |

| Z*  | Z*   | X   | H   | L    |

\*Z = Negative transition of CLK or SCLK

## Table 3. MAXIMUM RATINGS

| Symbol               | Parameter                                          | Condition 1                                    | Condition 2                                                       | Rating                     | Unit |

|----------------------|----------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------|----------------------------|------|

| V <sub>CC</sub>      | PECL Mode Power Supply                             | V <sub>EE</sub> = 0 V                          |                                                                   | 8                          | V    |

| $V_{EE}$             | NECL Mode Power Supply                             | V <sub>CC</sub> = 0 V                          |                                                                   | -8                         | V    |

| VI                   | PECL Mode Input Voltage<br>NECL Mode Input Voltage | V <sub>EE</sub> = 0 V<br>V <sub>CC</sub> = 0 V | $\begin{array}{l} V_I \leq V_{CC} \\ V_I \geq V_{EE} \end{array}$ | 6<br>-6                    | V    |

| I <sub>out</sub>     | Output Current                                     | Continuous<br>Surge                            |                                                                   | 50<br>100                  | mA   |

| I <sub>BB</sub>      | V <sub>BB</sub> Sink/Source                        |                                                |                                                                   | ± 0.5                      | mA   |

| T <sub>A</sub>       | Operating Temperature Range                        |                                                |                                                                   | 0 to +85                   | °C   |

| T <sub>stg</sub>     | Storage Temperature Range                          |                                                |                                                                   | -65 to +150                | °C   |

| $\theta_{JA}$        | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | PLCC-28                                                           | 63.5<br>43.5               | °C/W |

| $\theta_{\text{JC}}$ | Thermal Resistance (Junction-to-Case)              | Standard Board                                 | PLCC-28                                                           | 22 to 26                   | °C/W |

| $V_{\text{EE}}$      | PECL Operating Range<br>NECL Operating Range       |                                                |                                                                   | 4.2 to 5.7<br>-5.7 to -4.2 | V    |

| T <sub>sol</sub>     | Wave Solder (Pb-Free)                              |                                                |                                                                   | 265                        | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

|                 |                                                                                  |      | 0°C  |      |      | 25°C |      |      | 85°C |      |      |

|-----------------|----------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|

| Symbol          | Characteristic                                                                   | Min  | Тур  | Max  | Min  | Тур  | Max  | Min  | Тур  | Max  | Unit |

| I <sub>EE</sub> | Power Supply Current                                                             |      | 119  | 160  |      | 119  | 160  |      | 119  | 160  | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 2)                                                     | 3980 | 4070 | 4160 | 4020 | 4105 | 4190 | 4090 | 4185 | 4280 | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 2)                                                      | 3050 | 3210 | 3370 | 3050 | 3210 | 3370 | 3050 | 3227 | 3405 | mV   |

| $V_{\text{IH}}$ | Input HIGH Voltage (Single-Ended)                                                | 3830 | 3995 | 4160 | 3870 | 4030 | 4190 | 3940 | 4110 | 4280 | mV   |

| V <sub>IL</sub> | Input LOW Voltage (Single-Ended)                                                 | 3050 | 3285 | 3520 | 3050 | 3285 | 3520 | 3050 | 3302 | 3555 | mV   |

| $V_{BB}$        | Output Voltage Reference                                                         | 3.62 |      | 3.74 | 3.65 |      | 3.75 | 3.69 |      | 3.81 | V    |

| VIHCMR          | Input HIGH Voltage Common Mode<br>Range (Differential Configuration)<br>(Note 3) | 2.4  |      | 4.6  | 2.4  |      | 4.6  | 2.4  |      | 4.6  | V    |

| I <sub>IH</sub> | Input HIGH Current                                                               |      |      | 150  |      |      | 150  |      |      | 150  | μA   |

| Ι <sub>ΙL</sub> | Input LOW Current                                                                | 0.5  | 0.3  |      | 0.5  | 0.25 |      | 0.3  | 0.2  |      | μA   |

## Table 4. 10E SERIES PECL DC CHARACTERISTICS (V<sub>CCx</sub> = 5.0 V; V<sub>EE</sub> = 0.0 V (Note 1))

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

1. Input and output parameters vary 1:1 with V\_{CC}. V\_{EE} can vary –0.46 V / +0.06 V.

2. Outputs are terminated through a 50  $\Omega$  resistor to V\_{CC} – 2.0 V.

3.  $V_{IHCMR}$  min varies 1:1 with  $V_{EE}$ , max varies 1:1 with  $V_{CC}$ .

#### Table 5. 10E SERIES NECL DC CHARACTERISTICS (V<sub>CCx</sub> = 0.0 V; V<sub>E E</sub> = -5.0 V (Note 1))

|                 |                                                                                  |       | 0°C   |       | 25°C  |       |       |       |       |       |      |

|-----------------|----------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol          | Characteristic                                                                   | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EE</sub> | Power Supply Current                                                             |       | 119   | 160   |       | 119   | 160   |       | 119   | 160   | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 2)                                                     | -1020 | -930  | -840  | -980  | -895  | -810  | -910  | -815  | -720  | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 2)                                                      | -1950 | -1790 | -1630 | -1950 | -1790 | -1630 | -1950 | -1773 | -1595 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage (Single-Ended)                                                | -1170 | -1005 | -840  | -1130 | -970  | -810  | -1060 | -890  | -720  | mV   |

| V <sub>IL</sub> | Input LOW Voltage (Single-Ended)                                                 | -1950 | -1715 | -1480 | -1950 | -1715 | -1480 | -1950 | -1698 | -1445 | mV   |

| V <sub>BB</sub> | Output Voltage Reference                                                         | -1.38 |       | -1.27 | -1.35 |       | -1.25 | -1.31 |       | -1.19 | V    |

| VIHCMR          | Input HIGH Voltage Common Mode<br>Range (Differential Configuration)<br>(Note 3) | -2.6  |       | -0.4  | -2.6  |       | -0.4  | -2.6  |       | -0.4  | V    |

| I <sub>IH</sub> | Input HIGH Current                                                               |       |       | 150   |       |       | 150   |       |       | 150   | μA   |

| ۱ <sub>IL</sub> | Input LOW Current                                                                | 0.5   | 0.3   |       | 0.5   | 0.065 |       | 0.3   | 0.2   |       | μA   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

1. Input and output parameters vary 1:1 with V<sub>CC</sub>. V<sub>EE</sub> can vary –0.46 V / +0.06 V.

2. Outputs are terminated through a 50  $\Omega$  resistor to V<sub>CC</sub> – 2.0 V.

3.  $V_{IHCMR}$  min varies 1:1 with  $V_{EE}$ , max varies 1:1 with  $V_{CC}$ .

|                 |                                                                                  |      | 0°C  |      |      | 25°C |      |      | 85°C |      |      |

|-----------------|----------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|

| Symbol          | Characteristic                                                                   | Min  | Тур  | Max  | Min  | Тур  | Max  | Min  | Тур  | Max  | Unit |

| I <sub>EE</sub> | Power Supply Current                                                             |      | 119  | 160  |      | 119  | 160  |      | 137  | 164  | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 2)                                                     | 3975 | 4050 | 4120 | 3975 | 4050 | 4120 | 3975 | 4050 | 4120 | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 2)                                                      | 3190 | 3295 | 3380 | 3190 | 3255 | 3380 | 3190 | 3260 | 3380 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage (Single-Ended)                                                | 3835 | 3975 | 4120 | 3835 | 3975 | 4120 | 3835 | 3975 | 4120 | mV   |

| V <sub>IL</sub> | Input LOW Voltage (Single-Ended)                                                 | 3190 | 3355 | 3525 | 3190 | 3355 | 3525 | 3190 | 3355 | 3525 | mV   |

| $V_{BB}$        | Output Voltage Reference                                                         | 3.62 |      | 3.74 | 3.62 |      | 3.74 | 3.62 |      | 3.74 | V    |

| VIHCMR          | Input HIGH Voltage Common Mode<br>Range (Differential Configuration)<br>(Note 3) | 2.4  |      | 4.6  | 2.4  |      | 4.6  | 2.4  |      | 4.6  | V    |

| I <sub>IH</sub> | Input HIGH Current                                                               |      |      | 150  |      |      | 150  |      |      | 150  | μA   |

| Ι <sub>ΙL</sub> | Input LOW Current                                                                | 0.5  | 0.3  |      | 0.5  | 0.25 |      | 0.5  | 0.2  |      | μA   |

## Table 6. 100E SERIES PECL DC CHARACTERISTICS (V<sub>CCx</sub> = 5.0 V; V<sub>EE</sub> = 0.0 V (Note 1))

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

1. Input and output parameters vary 1:1 with V\_{CC}. V\_{EE} can vary –0.46 V / +0.8 V.

2. Outputs are terminated through a 50  $\Omega$  resistor to  $V_{CC}$  – 2.0 V.

3.  $V_{IHCMR}$  min varies 1:1 with  $V_{EE}$ , max varies 1:1 with  $V_{CC}$ .

#### Table 7. 100E SERIES NECL DC CHARACTERISTICS (V<sub>CCx</sub> = 0.0 V; V<sub>EE</sub> = -5.0 V (Note 1))

|                 |                                                                                  |       | 0°C   |       | 25°C  |       |       | 85°C  |       |       |      |

|-----------------|----------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol          | Characteristic                                                                   | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EE</sub> | Power Supply Current                                                             |       | 119   | 160   |       | 119   | 160   |       | 137   | 164   | mA   |

| V <sub>OH</sub> | Output HIGH Voltage (Note 2)                                                     | -1025 | -950  | -880  | -1025 | -950  | -880  | -1025 | -950  | -880  | mV   |

| V <sub>OL</sub> | Output LOW Voltage (Note 2)                                                      | -1810 | -1705 | -1620 | -1810 | -1745 | -1620 | -1810 | -1740 | -1620 | mV   |

| V <sub>IH</sub> | Input HIGH Voltage (Single-Ended)                                                | -1165 | -1025 | -880  | -1165 | -1025 | -880  | -1165 | -1025 | -880  | mV   |

| V <sub>IL</sub> | Input LOW Voltage (Single-Ended)                                                 | -1810 | -1645 | -1475 | -1810 | -1645 | -1475 | -1810 | -1645 | -1475 | mV   |

| V <sub>BB</sub> | Output Voltage Reference                                                         | -1.38 |       | -1.26 | -1.38 |       | -1.26 | -1.38 |       | -1.26 | V    |

| VIHCMR          | Input HIGH Voltage Common Mode<br>Range (Differential Configuration)<br>(Note 3) | -2.6  |       | -0.4  | -2.6  |       | -0.4  | -2.6  |       | -0.4  | V    |

| I <sub>IH</sub> | Input HIGH Current                                                               |       |       | 150   |       |       | 150   |       |       | 150   | μA   |

| ۱ <sub>IL</sub> | Input LOW Current                                                                | 0.5   | 0.3   |       | 0.5   | 0.25  |       | 0.5   | 0.2   |       | μA   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

1. Input and output parameters vary 1:1 with V<sub>CC</sub>. V<sub>EE</sub> can vary –0.46 V / +0.8 V.

2. Outputs are terminated through a 50  $\Omega$  resistor to  $V_{CC}$  – 2.0 V.

3.  $V_{IHCMR}$  min varies 1:1 with  $V_{EE}$ , max varies 1:1 with  $V_{CC}$ .

|                                      |                                                                                            |                          | 0°C                      |                              |                          | 25°C                     |                              |                          | 85°C                      |                              |      |

|--------------------------------------|--------------------------------------------------------------------------------------------|--------------------------|--------------------------|------------------------------|--------------------------|--------------------------|------------------------------|--------------------------|---------------------------|------------------------------|------|

| Symbol                               | Characteristic                                                                             | Min                      | Тур                      | Max                          | Min                      | Тур                      | Max                          | Min                      | Тур                       | Max                          | Unit |

| f <sub>MAX</sub>                     | Maximum Toggle Frequency                                                                   |                          | 700                      |                              |                          | 700                      |                              |                          | 700                       |                              | MHz  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay to Output<br>CLK to Q (Diff)<br>CLK to Q (SE)<br>SCLK to Q<br>SEL to Q   | 795<br>745<br>650<br>745 | 930<br>930<br>900<br>970 | 1065<br>1115<br>1085<br>1195 | 805<br>755<br>650<br>755 | 940<br>940<br>910<br>980 | 1075<br>1125<br>1095<br>1205 | 825<br>775<br>650<br>775 | 960<br>960<br>930<br>1000 | 1095<br>1145<br>1115<br>1225 | ps   |

| t <sub>PHL</sub>                     | Disable Time<br>CLK or SCLK to Q (Note 3)                                                  |                          | 600                      | 800                          |                          | 600                      | 800                          |                          | 600                       | 800                          | ps   |

| t <sub>skew</sub>                    | Part-to-Part Skew<br>CLK (Diff) to Q<br>CLK (SE), SCLK to Q<br>Within-Device Skew (Note 2) |                          | 50                       | 270<br>370<br>75             |                          | 50                       | 270<br>370<br>75             |                          |                           | 270<br>370<br>75             | ps   |

| t <sub>JITTER</sub>                  | Random Clock Jitter (RMS)                                                                  |                          | < 1                      |                              |                          | < 1                      |                              |                          | < 1                       |                              | ps   |

| t <sub>s</sub>                       | Setup Time<br>ENx to CLK<br>CEN to CLK (Note 3)                                            | 200<br>200               | -100<br>0                |                              | 200<br>200               | -100<br>0                |                              | 200<br>200               | -100<br>0                 |                              | ps   |

| t <sub>h</sub>                       | Hold Time<br>CLK to ENx, CEN (Note 3)                                                      | 900                      | 600                      |                              | 900                      | 160                      |                              | 900                      | 600                       |                              | ps   |

| V <sub>PP</sub>                      | Minimum Input Swing (CLK) (Note 4)                                                         | 0.25                     |                          | 1.0                          | 0.25                     |                          | 1.0                          | 0.25                     |                           | 1.0                          | V    |

| t <sub>r</sub><br>t <sub>f</sub>     | Rise/Fall Times<br>(20 – 80%)                                                              | 150                      |                          | 400                          | 150                      |                          | 400                          | 150                      |                           | 400                          | ps   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

1. 10 Series: V<sub>EE</sub> can vary -0.46 V / +0.06 V.

Series: V<sub>EE</sub> can vary -0.46 V / +0.8 V.

Within-Device skew is defined for identical transitions on similar paths through a device.

3. Setup, Hold and Disable times are all relative to a falling edge on CLK or SCLK.

4. Minimum input swing for which AC parameters are guaranteed. Full DC ECL output swings will be generated with only 50 mV input swings.

#### APPLICATIONS INFORMATION

#### **General Description**

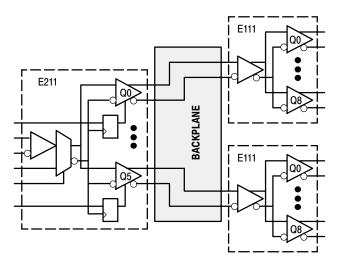

The MC10E/100E211 is a 1:6 fanout tree designed explicitly for low skew high speed clock distribution. The device was targeted to work in conjunction with the E111 device to provide another level of flexibility in the design and implementation of clock distribution trees. The individual synchronous enable controls and multiplexed clock inputs make the device ideal as the first level distribution unit in a distribution tree. The device provides the ability to distribute a lower speed scan or test clock along with the high speed system clock to ease the design of system diagnostics and self test procedures. The individual enables could be used to allow for the disabling of individual cards on a backplane in fault tolerant designs.

Because of lower fanout and larger skews the E211 will not likely be used as an alternative to the E111 for the bulk of the clock fanout generation. Figure 3 shows a typical application combining the two devices to take advantage of the strengths of each.

Figure 3. Standard E211 Application

#### Using the E211 in PECL Designs

The E211 device can be utilized very effectively in designs utilizing only a +5 V power supply. Since the internal switching reference levels are biased off of the  $V_{CC}$  supply the input thresholds for the single-ended inputs will vary with  $V_{CC}$ . As a result the single-ended inputs should be driven by a device on the same board as the E211. Driving these inputs across a backplane where significant differences between the  $V_{CC}$ 's of the transmitter and receiver can occur can lead to AC performance and/or significant noise margin degradations. Because the differential I/O does not use a switching reference, and due to the CMR range of the E211, even under worst case  $V_{CC}$

situations between cards there will be no AC performance or noise margin loss for the differential CLK inputs.

For situations where TTL clocks are required the E211 can be interfaced with the H641 or H643 ECL to TTL Clock Distribution Chips. The H641 is a single supply 1:9 PECL to TTL device while the H643 is a 1:8 dual supply standard ECL to TTL device. By combining the superior skew performance of the E211, or E111, with the low skew translating capabilities of the H641 and H643 very low skew TTL clock distribution networks can be realized.

#### Handling Open Inputs and Outputs

All of the input pins of the E211 have a 50 k $\Omega$  to 75 k $\Omega$ pulldown resistor to pull the input to V<sub>EE</sub> when left open. This feature can cause a problem if the differential clock inputs are left open as the input gate current source transistor will become saturated. Under these conditions the outputs of the CLK input buffer will go to an undefined state. It is recommended, if possible,that the SCLK input should be selected any time the differential CLK inputs are allowed to float. The SCLK buffer, under open input conditions, will maintain a defined output state and thus the Q outputs of the device will be in a defined state (Q = LOW). Note that if all of the inputs are left open the differential CLK input will be selected and the state of the Q outputs will be undefined.

With the simultaneous switching characteristics and the tight skew specifications of the E211 the handling of the unused outputs becomes critical. To minimize the noise generated on the die all outputs should be terminated in pairs, i.e. both the true and complement outputs should be terminated even if only one of the outputs will be used in the system. With both complementary pairs terminated the current in the V<sub>CC</sub> pins will remain essentially constant and thus inductance induced voltage glitches on V<sub>CC</sub> will not occur. V<sub>CC</sub> glitches will result in distorted output waveforms and degradations in the skew performance of the device.

The package parasitics of the PLCC-28 cause the signals on a given pin to be influenced by signals on adjacent pins. The E211 is characterized and tested with all of the outputs switching, therefore the numbers in the data book are guaranteed only for this situation. If all of the outputs of the E211 are not needed and there is a desire to save power the unused output pairs can be left unterminated. Unterminated outputs can influence the propagation delay on adjacent pins by 15 ps - 20 ps. Therefore under these conditions this 15 ps - 20 ps needs to be added to the overall skew of the device. Pins which are separated by a package corner are not considered adjacent pins in the context of propagation delay influence. Therefore as long as all of the outputs on a single side of the package are terminated the specification limits in the data sheet will apply.

## **APPLICATIONS INFORMATION**

### **Differential versus Single-Ended Use**

As can be seen from the data sheet, to minimize the skew of the E211 the device must be used in the differential mode. In the single-ended mode the propagation delays are dependent on the relative position of the  $V_{BB}$  switching reference. Any  $V_{BB}$  offset from the center of the input swing will add delay to either the  $T_{PLH}$  or  $T_{PHL}$  and subtract delay from the other. This increase and decrease in delay will lead to an increase in the duty cycle skew and thus part-to-part skew. The within-device skew will be independent of the  $V_{BB}$  and therefore will be the same regardless of whether the device is driven differentially or single-ended.

For applications where part-to-part skew or duty cycle skew are not important the advantages of single-ended clock distribution may lead to its use. Using single-ended interconnect will reduce the number of signal traces to be routed, but remember that all of the complementary outputs still need to be terminated therefore there will be no reduction in the termination components required. To use the E211 with a single-ended input the arrangement pictured in Figure 5 should be used. If the input to the differential CLK inputs are AC coupled as pictured in Figure 4 the dependence on a centered  $V_{BB}$  reference is removed. The situation pictured will ensure that the input is centered around the bias set by the VBB. As a result when AC coupled the AC specification limits for a differential input can be used. For more information on AC coupling please refer to the interfacing section of the design guide in the ECLinPS data book.

#### Using the Enable Pins

Both the common enable ( $\overline{\text{CEN}}$ ) and the individual enables ( $\overline{\text{ENx}}$ ) are synchronous to the CLK or SCLK input depending on which is selected. The active low signals are clocked into the enable flip flops on the negative edges of the E211 clock inputs. In this way the devices will only be disabled when the outputs are already in the LOW state. The internal propagation delays are such that the delay to the output through the distribution buffers is less than that through the enable flip flops. This will ensure that the disabling of the device will not slice any time off the clock pulse. On initial power up the enable flip flops will randomly attain a stable state, therefore precautions should be taken on initial power up to ensure the E211 is in the desired state.

Figure 4. AC Coupled Input

Figure 5. Single-Ended Input

Figure 6. Typical Termination for Output Driver and Device Evaluation (See Application Note <u>AND8020/D</u> – Termination of ECL Logic Devices.)

#### **Resource Reference of Application Notes**

| AN1405/D  | - | ECL Clock Distribution Techniques           |

|-----------|---|---------------------------------------------|

| AN1406/D  | - | Designing with PECL (ECL at +5.0 V)         |

| AN1503/D  | - | ECLinPS <sup>™</sup> I/O SPiCE Modeling Kit |

| AN1504/D  | - | Metastability and the ECLinPS Family        |

| AN1568/D  | - | Interfacing Between LVDS and ECL            |

| AN1672/D  | - | The ECL Translator Guide                    |

| AND8001/D | - | Odd Number Counters Design                  |

| AND8002/D | - | Marking and Date Codes                      |

| AND8020/D | - | Termination of ECL Logic Devices            |

| AND8066/D | - | Interfacing with ECLinPS                    |

| AND8090/D | - | AC Characteristics of ECL Devices           |

|           |   |                                             |

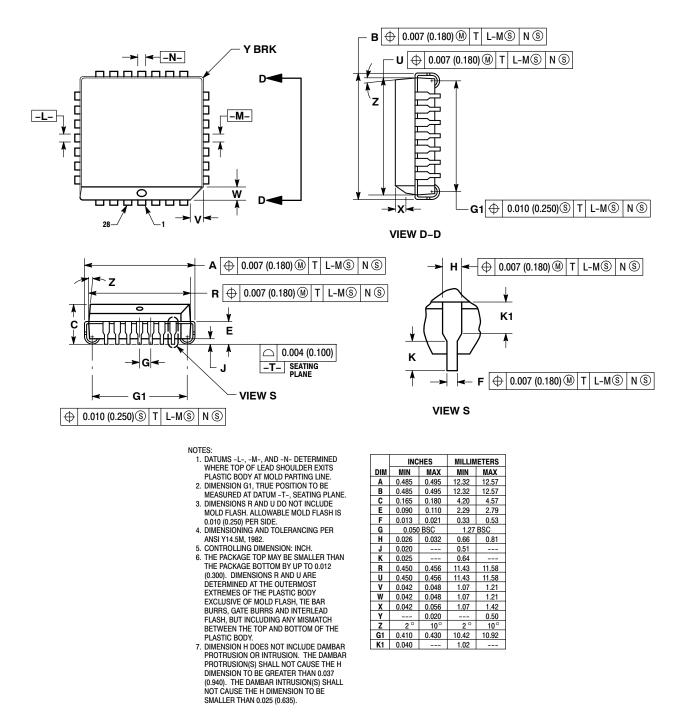

### PACKAGE DIMENSIONS

28 LEAD PLLC CASE 776-02 ISSUE F

#### ECLinPS is a registered trademark of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns me rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor roducts, "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights or the rights of others. ON Semiconductor and the support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly, any claim of personal injury or death associated with such unintended or unauthorized colaim alleges that ON Se

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative