## 32-bit Microcontroller

**CMOS**

## FR60 MB91460N Series

# MB91F463NA/F463NC/V460A

#### **■ DESCRIPTION**

MB91F463NA is a line of the general-purpose 32-bit RISC microcontrollers designed for embedded control applications which require high-speed real-time processing, such as consumer devices and on-board vehicle systems. MB91F463NA uses the FR60 CPU which is compatible with the FR\* CPUs.

MB91F463NA contains the LIN-USART and CAN controllers.

\*: FR, the abbreviation of FUJITSU RISC controller, is a line of products of Fujitsu Microelectronics Limited.

Note: MB91F463NC improved the features of MB91F463NA and updated the sector map for the flash memory. Please select MB91F463NC for the future development.

#### **■ FEATURES**

#### • FR60 CPU

- 32-bit RISC, load/store architecture, five-stage pipeline

- Maximum operating frequency: 80 MHz (oscillator frequency: 4 MHz; oscillator frequency multiplier: 20 (PLL clock multiplication method))

- 16-bit fixed-length instructions (basic instructions)

- Instruction execution speed: 1 instruction per cycle

- Instructions including memory-to-memory transfer, bit manipulation instructions, and barrel shift instructions: Instructions suitable for embedded applications

- Function entry/exit instructions and register data multi load store instructions: Instructions supporting C language

- Register interlock function: Facilitating assembly-language coding

(Continued)

For the information for microcontroller supports, see the following web site.

This web site includes the **"Customer Design Review Supplement"** which provides the latest cautions on system development and the minimal requirements to be checked to prevent problems before the system development.

http://edevice.fujitsu.com/micom/en-support/

• Built-in multiplier with instruction-level support

Signed 32-bit multiplication: 5 cycles Signed 16-bit multiplication: 3 cycles

- Interrupt (PC/PS saving): 6 cycles (16 priority levels)

- Harvard architecture allowing program access and data access to be executed simultaneously

- Instructions compatible with the FR family

- Internal peripheral resources

- Flash memory capacity: 288 Kbytes

- Internal RAM capacity: 8 Kbytes (Data RAM) + 2 Kbytes (Instruction/data RAM)

- General-purpose port: Maximum 48 ports

- DMAC (DMA Controller)

Maximum of 5 channels for able to operate simultaneously

2 transfer sources (internal peripheral/software)

Activation source can be selected by programs

Addressing mode specifies full 32-bit addresses (increment/decrement/fixed)

Transfer mode (burst transfer/step transfer/block transfer)

Transfer data size selectable from 8/16/32-bit

Multi-byte transfer capable (by programs)

DMAC descriptor in I/O areas (200<sub>H</sub> to 240<sub>H</sub>, 1000<sub>H</sub> to 1024<sub>H</sub>)

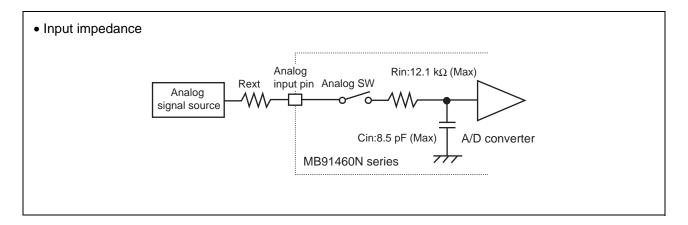

A/D converter (sequential comparison)

10-bit resolution: 8 channels

Conversion time: 1 µs (using at 5 V), 3 µs (using at 3.3 V)

- External interrupt inputs: 10 channels

- Bit search module (for REALOS)

Function to search from the MSB (most significant bit) for the position of the first "0", "1" or changed bit in a word

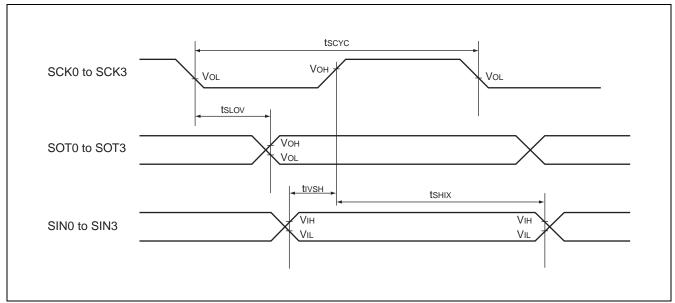

• LIN-USART (full duplex double buffer): 4 channels

Clock synchronous/asynchronous selectable

Sync-break detection

Internal dedicated baud rate generator

• I<sup>2</sup>C bus interface (Supports 400 kbps): 2 channels

Master/slave transmission and reception

Arbitration function, clock synchronization function

• CAN controller (C-CAN): 2 channels

Maximum transfer speed: 1 Mbps

32 transmission/reception message buffers

- 16-bit PPG timer: 8 channels

- 16-bit reload timer: 4 channels + 1 channel (exclusive A/D converter)

- 16-bit free-run timer: 4 channels

- Input capture: 4 channels

- Output compare: 4 channels

- 8/16-bit up/down counter: 2 channels (8-bit)/1channel (16-bit)

- · Watchdog timer

- Real-time clock

- Low-power consumption mode: Sleep/stop mode function

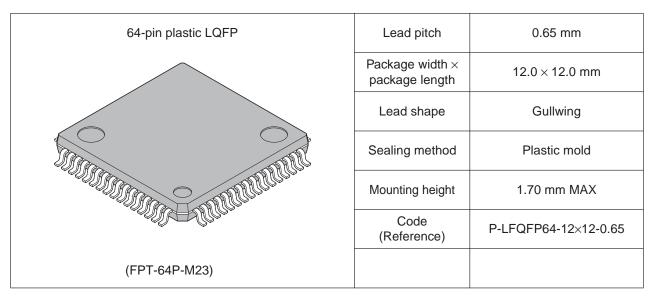

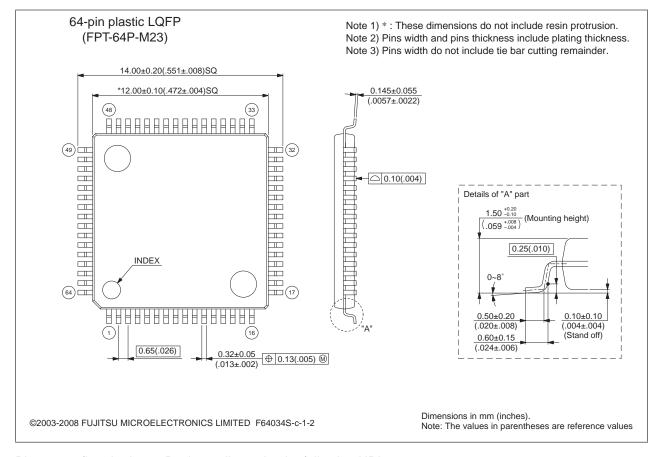

- Package: LQFP-64 (FPT-64P-M23)

- CMOS 0.18 μm technology

- 3.3 V only power supplies or 5 V only power supplies

- Operating temperature range: -40% to +85% (using at 5 V) -40% to +105% (using at 3.3 V)

## ■ PRODUCT LINEUP

| Part number Parameter             | MB91V460A                          | MB91F463NA<br>MB91F463NC |  |  |  |

|-----------------------------------|------------------------------------|--------------------------|--|--|--|

| Max core frequency<br>(CLKB)      | 80 MHz                             |                          |  |  |  |

| Max resource<br>frequency (CLKP)  | 40 MHz                             |                          |  |  |  |

| Max external bus frequency (CLKT) | 40 MHz                             | _                        |  |  |  |

| Max CAN frequency<br>(CLKCAN)     | 20 N                               | ЛНz                      |  |  |  |

| Technology                        | 0.35 μm                            | 0.18 μm                  |  |  |  |

| Watchdog Timer                    | Yes                                | No                       |  |  |  |

| Watchdog Timer<br>(CR oscillator) | Yes (disengageable)                | Yes                      |  |  |  |

| Bit search                        | Ye                                 | es                       |  |  |  |

| Reset input (INITX)               | Ye                                 | es                       |  |  |  |

| Hardware standby input (HSTX)     | Yes                                | No                       |  |  |  |

| Clock modulator                   | Yes                                |                          |  |  |  |

| Low-power mode                    | Yes                                |                          |  |  |  |

| DMAC                              | 5 channels                         |                          |  |  |  |

| MAC (μDSP)                        | No                                 |                          |  |  |  |

| MMU/MPU                           | MPU (16 channels)*                 | MPU (4 channels)*        |  |  |  |

| Flash memory                      | Emulation SRAM<br>32-bit read data | 288 Kbytes               |  |  |  |

| Flash protection                  | _                                  | Yes                      |  |  |  |

| Data RAM                          | 64 Kbytes                          | 8 Kbytes                 |  |  |  |

| Instruction/data RAM              | 64 Kbytes                          | 2 Kbytes                 |  |  |  |

| Flash-cache (instruction cache)   | 16 Kbytes                          | 4 Kbytes                 |  |  |  |

| Boot-ROM/BI-ROM                   | 4 Kbytes fixed                     | 4 Kbytes (BI-ROM)        |  |  |  |

| Real-time clock                   | 1 chai                             | nnels                    |  |  |  |

| Free-run timer                    | 8 channels                         | 4 channels               |  |  |  |

| ICU                               | 8 channels                         | 4 channels               |  |  |  |

| OCU                               | 8 channels                         | 4 channels               |  |  |  |

| 16-bit reload timer               | 8 channels                         | 4 channels + 1 channel   |  |  |  |

| 16-bit PPG                        | 16 channels                        | 8 channels               |  |  |  |

| Part number Parameter               | MB91V460A                                      | MB91F463NA<br>MB91F463NC                   |  |

|-------------------------------------|------------------------------------------------|--------------------------------------------|--|

| 16-bit PFM                          | 1 channel                                      | No                                         |  |

| Sound Generator                     | 1 channel                                      | No                                         |  |

| 8/16-bit<br>up/down counter         | 4 channels (8-bit) /<br>2 channels (16-bit)    | 2 channels (8-bit) /<br>1 channel (16-bit) |  |

| C_CAN                               | 6 channels (128 message buffers)               | 2 channels (32 message buffers)            |  |

| LIN-USART                           | 4 channels + 4 channels (FIFO) +<br>8 channels | 4 channels                                 |  |

| I <sup>2</sup> C (400 kbps)         | 4 channels                                     | 2 channels                                 |  |

| FR external bus                     | Yes (32-bit address, 32-bit data)              | No                                         |  |

| External interrupt                  | 16 channels                                    | 10 channels                                |  |

| NMI interrupts                      | Yes                                            | No                                         |  |

| Stepping motor controller (SMC)     | 6 channels                                     | No                                         |  |

| LCD controller (40 × 4)             | 1 channel                                      | No                                         |  |

| 10-bit A/D converter                | 32 channels                                    | 8 channels                                 |  |

| Alarm comparator                    | 2 channels                                     | No                                         |  |

| Clock supervisor                    | Yes                                            | No                                         |  |

| Main clock oscillator               | 4 Mi                                           | Hz                                         |  |

| Sub clock oscillator                | 32 kHz                                         | _                                          |  |

| CR oscillator                       | 100 kHz                                        | 100 kHz / 2 MHz                            |  |

| PLL                                 | ×2                                             | 20                                         |  |

| DSU4                                | Yes                                            | No                                         |  |

| EDSU                                | Yes (32 BP) *                                  | Yes (8 BP)*                                |  |

| Power supply voltage                | 3 V /                                          | 5 V                                        |  |

| Regulator                           | Ye                                             | s                                          |  |

| Power consumption                   | n.a.                                           | < 700 mW                                   |  |

| Temperature range (T <sub>A</sub> ) | 0 °C to +70 °C                                 | – 40 °C to + 105 °C                        |  |

| Package                             | BGA-660                                        | LQFP-64                                    |  |

<sup>\*:</sup> MPU channels use EDSU breakpoint registers (shared operation between MPU and EDSU).

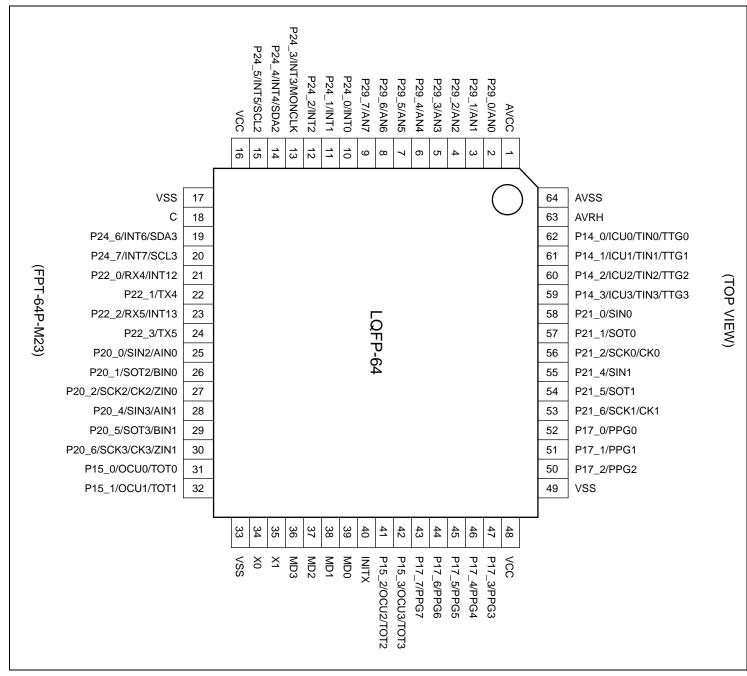

# PIN ASSIGNMENT

## **■ PIN DESCRIPTION**

| Pin no.  | Pin name       | I/O | I/O circuit<br>type* | Function                                    |

|----------|----------------|-----|----------------------|---------------------------------------------|

| 2 to 9   | P29_0 to P29_7 | I/O | В                    | General-purpose input/output ports          |

| 2 10 9   | AN0 to AN7     | 1/0 |                      | Analog input pins for A/D converter         |

| 10 to 12 | P24_0 to P24_2 | I/O | А                    | General-purpose input/output ports          |

| 10 10 12 | INT0 to INT2   | 1/0 | A                    | External interrupt input pins               |

|          | P24_3          |     |                      | General-purpose input/output port           |

| 13       | INT3           | I/O | Α                    | External interrupt input pins               |

|          | MONCLK         |     |                      | Clock monitor output pin                    |

|          | P24_4          |     |                      | General-purpose input/output port           |

| 14       | INT4           | I/O | С                    | External interrupt input pin                |

|          | SDA2           |     |                      | I <sup>2</sup> C bus data input/output pin  |

|          | P24_5          |     |                      | General-purpose input/output port           |

| 15       | INT5           | I/O | С                    | External interrupt input pin                |

|          | SCL2           |     |                      | I <sup>2</sup> C bus clock input/output pin |

|          | P24_6          |     |                      | General-purpose input/output port           |

| 19       | INT6           | I/O | С                    | External interrupt input pin                |

|          | SDA3           |     |                      | I <sup>2</sup> C bus data input/output pin  |

|          | P24_7          |     |                      | General-purpose input/output port           |

| 20       | INT7           | I/O | С                    | External interrupt input pin                |

|          | SCL3           |     |                      | I <sup>2</sup> C bus clock input/output pin |

|          | P22_0          |     |                      | General-purpose input/output port           |

| 21       | RX4            | I/O | Α                    | RX input pin of CAN4                        |

|          | INT12          |     |                      | External interrupt input pin                |

| 22       | P22_1          | I/O | А                    | General-purpose input/output port           |

| 22       | TX4            | 1/0 | A                    | TX output pin of CAN4                       |

|          | P22_2          |     |                      | General-purpose input/output port           |

| 23       | RX5            | I/O | Α                    | RX input pin of CAN5                        |

|          | INT13          |     |                      | External interrupt input pin                |

| 24       | P22_3          | I/O | А                    | General-purpose input/output port           |

| 24       | TX5            | 1/0 | A                    | TX output pin of CAN5                       |

|          | P20_0          |     |                      | General-purpose input/output port           |

| 25       | SIN2           | I/O | Α                    | Data input pin of LIN-USART2                |

|          | AIN0           |     |                      | Up/down counter input pin                   |

|          | P20_1          |     |                      | General-purpose input/output port           |

| 26       | SOT2           | I/O | А                    | Data output pin of LIN-USART2               |

|          | BIN0           |     |                      | Up/down counter input pin                   |

| Pin no.   | Pin name       | I/O | I/O circuit<br>type* | Function                             |

|-----------|----------------|-----|----------------------|--------------------------------------|

|           | P20_2          |     |                      | General-purpose input/output port    |

| 27        | SCK2           | I/O | А                    | Clock input/output pin of LIN-USART2 |

| 21        | CK2            | 1/0 |                      | Free-run timer input pin             |

|           | ZIN0           |     |                      | Up/down counter input pin            |

|           | P20_4          |     |                      | General-purpose input/output port    |

| 28        | SIN3           | I/O | Α                    | Data input pin of LIN-USART3         |

|           | AIN1           |     |                      | Up/down counter input pin            |

|           | P20_5          |     |                      | General-purpose input/output port    |

| 29        | SOT3           | I/O | Α                    | Data output pin of LIN-USART3        |

|           | BIN1           |     |                      | Up/down counter input pin            |

|           | P20_6          |     |                      | General-purpose input/output port    |

| 20        | SCK3           | 1/0 |                      | Clock input/output pin of LIN-USART3 |

| 30        | 30 CK3         | I/O | A                    | Free-run timer input pin             |

|           | ZIN1           |     |                      | Up/down counter input pin            |

|           | P15_0          |     |                      | General-purpose input/output port    |

| 31        | OCU0           | I/O | A                    | Output compare output pin            |

|           | ТОТ0           |     |                      | Reload timer output pin              |

|           | P15_1          |     |                      | General-purpose input/output port    |

| 32        | OCU1           | I/O | Α                    | Output compare output pin            |

| -         | TOT1           |     |                      | Reload timer output pin              |

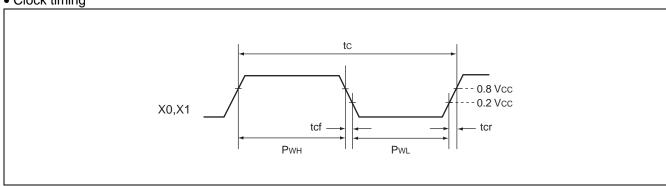

| 34        | X0             | _   | J                    | Clock (oscillation) input            |

| 35        | X1             | _   | J                    | Clock (oscillation) output           |

| 36        | MD3            | I   | I                    | Mode setting pin                     |

| 37        | MD2            | I   | G                    | Mode setting pin                     |

| 38        | MD1            | I   | G                    | Mode setting pin                     |

| 39        | MD0            | I   | G                    | Mode setting pin                     |

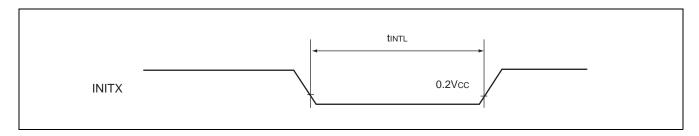

| 40        | INITX          | I   | Н                    | External reset input                 |

|           | P15_2          |     |                      | General-purpose input/output port    |

| 41        | OCU2           | I/O | Α                    | Output compare output pin            |

| -         | TOT2           |     |                      | Reload timer output pin              |

|           | P15_3          |     |                      | General-purpose input/output port    |

| 42        | OCU3           | I/O | Α                    | Output compare output pin            |

|           | ТОТ3           |     |                      | Reload timer output pin              |

| 43 to 47, | P17_7 to P17_0 | I/O | ۸                    | General-purpose input/output ports   |

| 50 to 52  | PPG7 to PPG0   | 1/0 | A                    | PPG timer output pins                |

| Pin no. | Pin name | 1/0 | I/O circuit<br>type*     | Function                                   |

|---------|----------|-----|--------------------------|--------------------------------------------|

|         | P21_6    |     |                          | General-purpose input/output port          |

| 53      | SCK1     | I/O | Α                        | Clock input/output pin of LIN-USART1       |

|         | CK1      |     |                          | Free-run timer input pin                   |

| 54      | P21_5    | I/O | А                        | General-purpose input/output port          |

| 34      | SOT1     | 1/0 | A                        | Data output pin of LIN-USART1              |

| 55 -    | P21_4    | I/O | А                        | General-purpose input/output port          |

| 55      | SIN1     | 1/0 | A                        | Data input pin of LIN-USART1               |

|         | P21_2    |     |                          | General-purpose input/output port          |

| 56      | SCK0     | I/O | А                        | Clock input/output pin of LIN-USART0       |

| CK0     |          |     | Free-run timer input pin |                                            |

| 57      | P21_1    | I/O | А                        | General-purpose input/output port          |

| 57      | SOT0     | 1/0 | A                        | Data output pin of LIN-USART0              |

| F0      | P21_0    | I/O | ۸                        | General-purpose input/output port          |

| 58      | SIN0     | 1/0 | A                        | Data input pin of LIN-USART0               |

|         | P14_3    |     |                          | General-purpose input/output port          |

| 59      | ICU3     | I/O | А                        | Input capture input pin                    |

| 59      | TIN3     | 1/0 | A                        | External trigger input pin of reload timer |

|         | TTG3     |     |                          | PPG timer input pin                        |

|         | P14_2    |     |                          | General-purpose input/output port          |

| 60      | ICU2     | I/O | А                        | Input capture input pin                    |

| 60      | TIN2     | 1/0 | A                        | External trigger input pin of reload timer |

|         | TTG2     |     |                          | PPG timer input pin                        |

|         | P14_1    |     |                          | General-purpose input/output port          |

| 61      | ICU1     | I/O | ٨                        | Input capture input pin                    |

| 61      | TIN1     | 1/0 | A                        | External trigger input pin of reload timer |

|         | TTG1     |     |                          | PPG timer input pin                        |

|         | P14_0    |     |                          | General-purpose input/output port          |

| 62      | ICU0     | I/O | ^                        | Input capture input pin                    |

| 02      | TIN0     | 1/0 | А                        | External trigger input pin of reload timer |

|         | TTG0     |     |                          | PPG timer input pin                        |

<sup>\* :</sup> For I/O circuit type, refer to "■ I/O CIRCUIT TYPE".

### [Power supply/GND pins]

| Pin no.    | Pin name | I/O | Function                                        |

|------------|----------|-----|-------------------------------------------------|

| 17, 33, 49 | VSS      | _   | GND pins                                        |

| 16, 48     | VCC      |     | 3.3 V/5 V power supply pins                     |

| 64         | AVSS     |     | Analog GND pin for A/D converter                |

| 1          | AVCC     |     | 3.3 V/5 V power supply pin for A/D converter    |

| 63         | AVRH     |     | Reference power supply pin for A/D converter    |

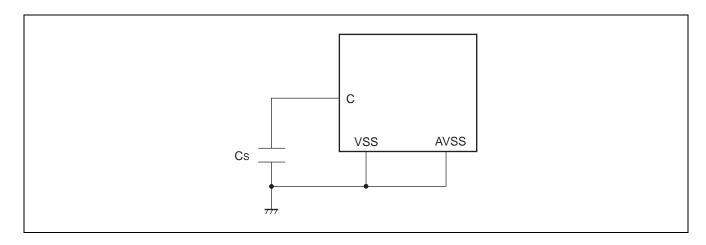

| 18         | С        | _   | Capacitor connection pin for internal regulator |

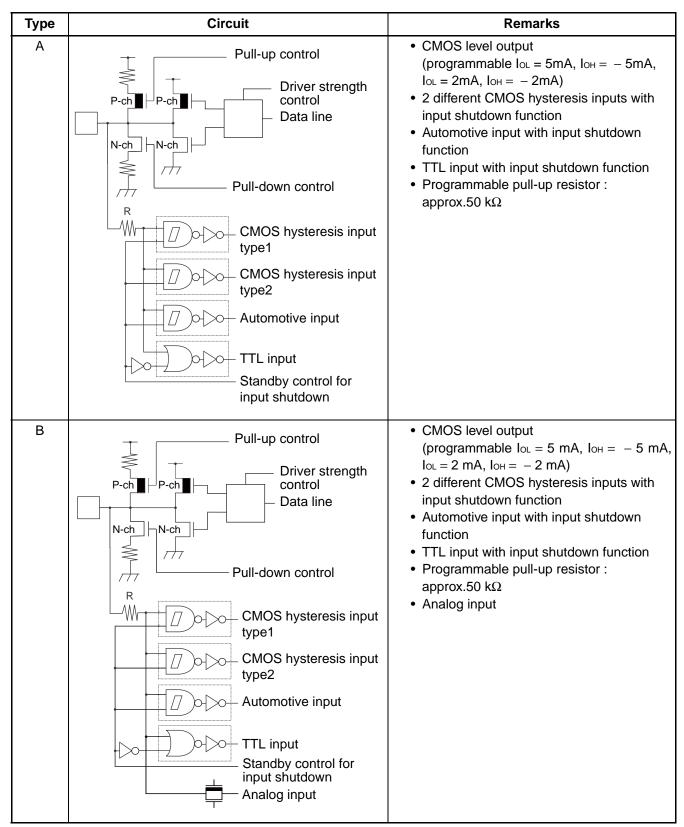

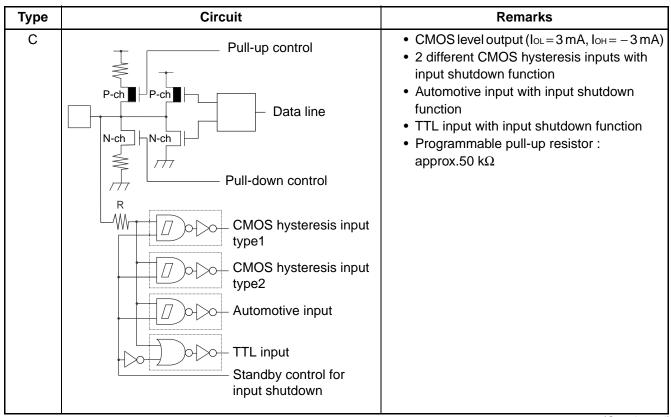

#### **■ I/O CIRCUIT TYPE**

| Туре | Circuit                       | Remarks                                                                                                                       |

|------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| G    | R CMOS level input            | MASK ROM and evaluation device:     CMOS level input     Flash device:     CMOS level input     12 V resistant (for MD [2:0]) |

| Н    | ₹ Pull-up resistor            | <ul> <li>CMOS hysteresis input</li> <li>Pull-up resistor value : approx.50 kΩ</li> </ul>                                      |

|      | R CMOS<br>Hysteresis<br>input |                                                                                                                               |

| I    | R CMOS Hysteresis input       | <ul> <li>CMOS hysteresis input</li> <li>Pull-down resistor value : approx.50 kΩ</li> </ul>                                    |

| J    | X1 Xout                       | Oscillation circuit                                                                                                           |

|      | X0 Standby control signal     |                                                                                                                               |

#### ■ PRECAUTIONS FOR HANDLING THE DEVICES

Any semiconductor devices have inherently a certain rate of failure. The possibility of failure is greatly affected by the conditions in which they are used (circuit conditions, environmental conditions, etc.). This page describes precautions that must be observed to minimize the chance of failure and to obtain higher reliability from your FUJITSU semiconductor devices.

#### 1. Precautions for Product Design

This section describes precautions when designing electronic equipment using semiconductor devices.

#### · Absolute Maximum Ratings

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### • Recommended Operating Conditions

The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

#### · Processing and Protection of Pins

These precautions must be followed when handling the pins which connect semiconductor devices to power supply and input/output functions.

#### (1) Preventing Over-Voltage and Over-Current Conditions

Exposure to voltage or current levels in excess of maximum ratings at any pin is likely to cause deterioration within the device, and in extreme cases leads to permanent damage of the device. Try to prevent such over voltage or over-current conditions at the design stage.

#### (2) Protection of Output Pins

Shorting of output pins to supply pins or other output pins, or connection to large capacitance can cause large current flows. Such conditions if present for extended periods of time can damage the device. Therefore, avoid this type of connection.

#### (3) Handling of Unused Input Pins

Unconnected input pins with very high impedance levels can adversely affect stability of operation. Such pins should be connected through an appropriate resistance to a power supply pin or ground pin.

#### • Latch-up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

Note: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

- (a) Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

- (b) Be sure that abnormal current flows do not occur during the power-on sequence.

#### • Observance of Safety Regulations and Standards

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### · Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

#### Precautions Related to Usage of Devices

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, submarine repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

#### 2. Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mounting type. In either case, quality assurance of heat resistance are applied for mounting under the Fujitsu's recommended conditions only at the soldering stage. For detailed information on mount conditions, contact the sales representative.

#### · Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder.

In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to FUJITSU recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

#### Surface Mount Type

Surface mount packaging has longer and thinner leads than lead-insertion packaging, and therefore leads are more easily deformed or bent. The use of packages with higher pin counts and narrower pin pitch results in increased susceptibility to open connections caused by deformed pins, or shorting due to solder bridges. You must use appropriate mounting techniques. FUJITSU recommends the solder reflow method, and has established a ranking of mounting conditions for each product. Users are advised to mount packages in accordance with FUJITSU ranking of recommended conditions.

#### Storage of Semiconductor Devices

Because plastic chip packages are formed from plastic resins, exposure to natural environmental conditions will cause absorption of moisture. During mounting, the application of heat to a package that has absorbed moisture can cause surfaces to peel, reducing moisture resistance and causing packages to crack. To prevent, do the following:

- (a) Avoid exposure to rapid temperature changes, which cause moisture to condense inside the product. Store products in locations where temperature changes are slight.

- (b) Use dry boxes for product storage. Products should be stored below 70% relative humidity, and at temperatures between +5 °C to +30 °C.

- (c) When necessary, FUJITSU packages semiconductor devices in highly moisture-resistant aluminum laminate bags, with a silica gel desiccant. Devices should be sealed in their aluminum laminate bags for storage.

- (d) Avoid storing packages where they are exposed to corrosive gases or high levels of dust.

#### Baking

Packages that have absorbed moisture may be de-moisturized by baking (heat drying). Follow the FUJITSU recommended conditions for baking.

#### · Static Electricity

Because semiconductor devices are particularly susceptible to damage by static electricity, you must take the following precautions:

- (a) Maintain relative humidity in the working environment between 40% and 70%. Use of an apparatus for ion generation may be needed to remove electricity.

- (b) Electrically ground all conveyors, solder vessels, soldering irons and peripheral equipment.

- (c) Eliminate static body electricity by the use of rings or bracelets connected to ground through high resistance (on the level of 1  $M\Omega$ ). Wearing of conductive clothing and shoes, use of conductive floor mats and other measures to minimize shock loads is recommended.

- (d) Ground all fixtures and instruments, or protect with anti-static measures.

- (e) Avoid the use of styrofoam or other highly static-prone materials for storage of completed board assemblies.

#### 3. Precautions for Use Environment

Reliability of semiconductor devices depends on ambient temperature and other conditions as described above. For reliable performance, do the following:

- (1) Humidity

- Prolonged use in high humidity can lead to leakage in devices as well as printed circuit boards. If high humidity levels are anticipated, consider anti-humidity processing.

- (2) Discharge of Static Electricity

When high-voltage charges exist close to semiconductor devices, discharges can cause abnormal operation.

In such cases, use anti-static measures or processing to prevent discharges.

- (3) Corrosive Gases, Dust, or Oil

Exposure to corrosive gases or contact with dust or oil may lead to chemical reactions that will adversely affect the device. If you use devices in such conditions, consider ways to prevent such exposure or to protect the devices.

- (4) Radiation, Including Cosmic Radiation

Most devices are not designed for environments involving exposure to radiation or cosmic radiation. Users should provide shielding as appropriate.

- (5) Smoke, Flame

Note: Plastic molded devices are flammable, and therefore should not be used near combustible substances. If devices begin to smoke or burn, there is danger of the release of toxic gases.

Customers considering the use of FUJITSU products in other special environmental conditions should consult with FUJITSU sales representatives.

#### **■ HANDLING DEVICES**

#### Power supply pins

Because there are multiple VCC and VSS pins, respective pins at the same potential are interconnected to prevent malfunctions such as latch-up. However, you must connect the pins externally to the power supply and ground lines to reduce the electro-magnetic emission levels, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating. Furthermore, the current supply source should be connected to the VCC and VSS pins of the device at a low impedance.

It is recommended to connect a ceramic bypass capacitor of approximately 0.1  $\mu$ F as a bypass capacitor between the Vcc and Vss near this device.

#### · Crystal oscillator circuit

Noise in proximity to the X0 and X1 pins can cause the device to malfunction. Printed circuit boards should be designed so that the X0 and X1 pins, crystal oscillator (or ceramic oscillator), and bypass capacitors connected to ground are located near the device and ground.

It is recommended that the printed circuit board artwork be designed such that the X0 and X1 pins are surrounded by ground plane for the stable operation.

Please request the oscillator manufacturer to evaluate the oscillational characteristics of the crystal and this device.

#### Mode pins (MD0 to MD3)

Connect them directly to VCC or VSS. To prevent the device from entering test mode accidentally due to noise, minimize the lengths of the patterns between each mode pin and VCC or VSS on the printed circuit board as much as possible and connect them at a low impedance. When used pulling down, design your circuit not to generate noises with a resistance 1  $k\Omega$  or less. Test your circuit and confirm that there is no problem.

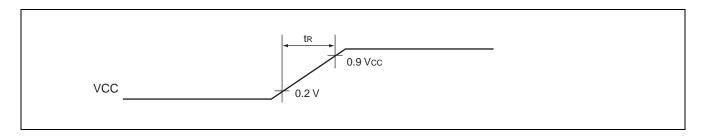

#### Operation at power-on

At power-on, it is necessary to make the terminal INITX "L" level.

Maintain the "L" level input to the INITX pin for the duration of the stabilization wait time immediately after the power on to ensure the stabilization wait time as required by the oscillator circuit.

#### Note on oscillator input at power-on

At power-on, ensure that the clock is input until the oscillator stabilization wait time has elapsed.

#### · Built-in regulator

As this series includes built-in step-down regulators, always connect a bypass capacitor of 4.7  $\mu$ F or more to the C pin for use by the regulator.

#### Notes on power on/off

Connect/disconnect the power supply pins when power on/off, or turn on/off in the following order.

Power on : VCC  $\rightarrow$  AVCC, AVRH Power off : AVCC, AVRH  $\rightarrow$  VCC

#### Precautions for the STOP mode

Set 1 to the bit 0 (OSCD1) of STCR register. When shifting to the STOP mode, a regulator switches to the standby regulator (for low-consumption current).

Due to the limited drive current, stop the (programming/erasing) access to the A/D converter and Flash before shifting to the STOP mode.

#### Serial communication

There is a possibility to receive wrong data due to the noise or other causes on the serial communication. Therefore, design a board so as to avoid noise.

Consider receiving of wrong data when designing the system. For example, apply a checksum to detect an error. If an error is detected, retransmit the data.

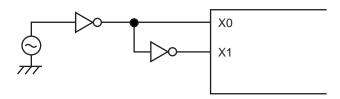

#### Notes on using external clock

When using the external clock, as a general rule you should simultaneously supply X0 and X1 pins. And also, the clock signal to X0 should be supplied a clock signal with the reverse phase to X1 pins. However, in this case the stop mode (oscillation stop mode) must not be used.

Example of using external clock (normal)

Note: Stop mode (oscillation stop mode) cannot be used.

#### • Notes on operating in PLL clock mode

If the oscillator is disconnected or the clock input stops when the PLL clock is selected, the microcontroller may continue to operate at the free-running frequency of the self-oscillating circuit of the PLL. However, this self-running operation cannot be guaranteed.

#### **■ NOTES ON DEBUGGER**

#### Execution of the RETI Command

If single-step execution is used in an environment where an interrupt occurs frequently, the corresponding interrupt handling routine will be executed repeatedly to the exclusion of other processing. This will prevent the main routine and the handlers for low priority level interrupts from being executed (For example, if the time-base timer interrupt is enabled, stepping over the RETI instruction will always break on the first line of the time-base timer interrupt handler).

Disable the corresponding interrupts when the corresponding interrupt handling routine no longer needs debugging.

#### Break function

If the range of addresses that cause a hardware break (including event breaks) is set to the address of the current system stack pointer or to an area that contains the stack pointer, execution will break after each instruction regardless of whether the user program actually contains data access instructions.

To prevent this, do not set (word) access to the area containing the address of the system stack pointer as the target of the hardware break (including an event breaks).

#### Operand break

It may cause malfunctions if a stack pointer exists in the area which is set as the DSU operand break. Do not set the access to the areas containing the address of system stack pointer as a target of data event break.

#### • Notes on PS register

As the PS register is processed in advance by some instructions, when the debugger is being used, the following exception handling may result in execution breaking in an interrupt handling routine or the displayed values of the flags in the PS register being updated.

As the microcontroller is designed to carry out reprocessing correctly upon returning from such an EIT event, the operation before and after the EIT always proceeds according to specification.

- 1) The following behavior may occur if any of the following occurs in the instruction immediately after a DIV0U/DIV0S instruction:

- (a) a user interrupt or NMI is accepted; (b) single-step execution is performed; or (c) execution breaks due to a data event or from the emulator menu.

- -D0 and D1 flags are updated in advance.

- -An EIT handling routine (user interrupt/NMI or emulator) is executed.

- -Upon returning from the EIT, the DIV0U/DIV0S instruction is executed and the D0 and D1 flags are updated to the same values as those in 1).

- 2) The following behavior occurs when an ORCCR, STILM, MOV Ri or PS instruction is executed to enable a user interrupt or NMI source while that interrupt is in the active state.

- -The PS register is updated in advance.

- -An EIT handling routine (user interrupt/NMI or emulator) is executed.

- -Upon returning from the EIT, the above instructions are executed and the PS register is updated to the same value as in 1).

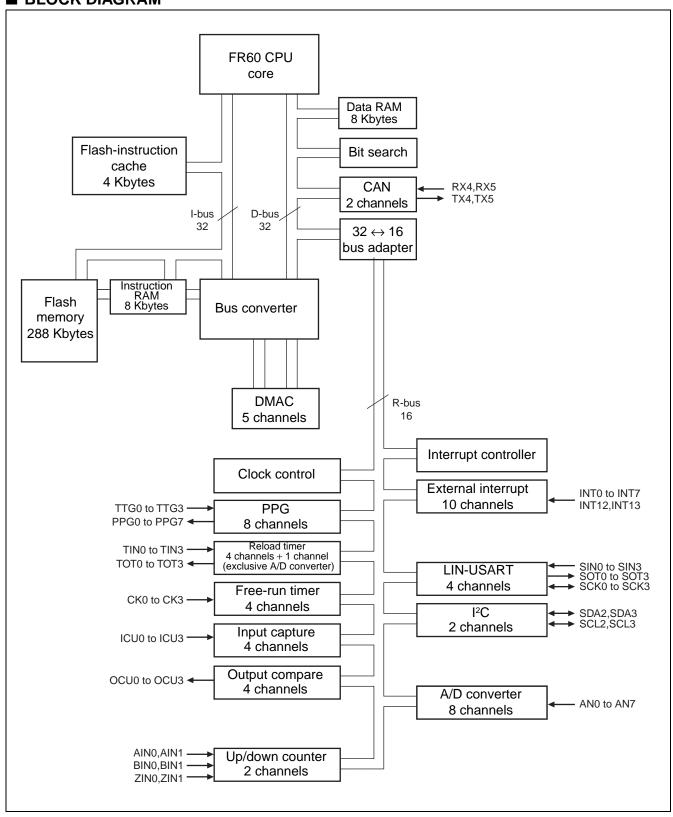

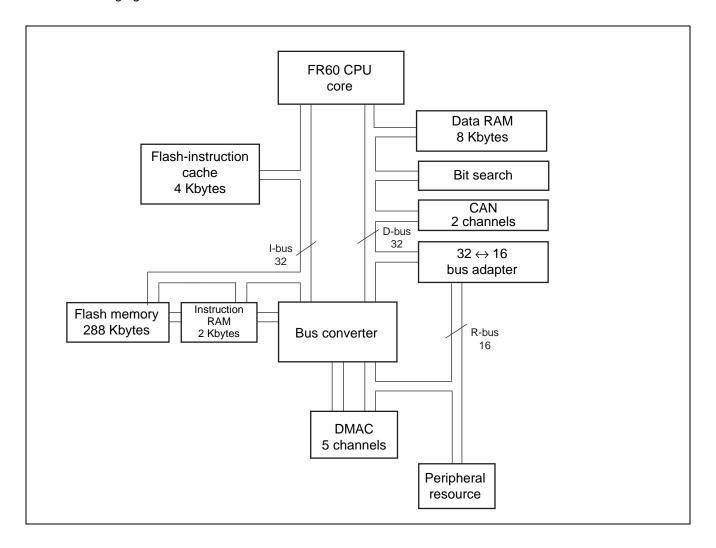

#### **■ BLOCK DIAGRAM**

#### **■ CPU AND CONTROL UNIT**

#### Internal architecture

The FR family CPU is a high performance core that is designed based on the RISC architecture with advanced instructions for embedded applications.

#### 1. Features

- Adoption of RISC architecture

Basic instruction: 1 instruction per cycle

- General-purpose registers: 32-bit x 16 registers

- 4 Gbytes linear memory space

- Multiplier installed

- 32-bit × 32-bit multiplication: 5 cycles 16-bit × 16-bit multiplication: 3 cycles

- Enhanced interrupt processing function Quick response speed (6 cycles)

Multiple-interrupt support Level mask function (16 levels)

- Enhanced instructions for I/O operation Memory-to-memory transfer instruction Bit processing instruction

- Basic instruction word length: 16 bits

- Low-power consumption SLEEP mode/STOP mode

#### 2. Internal architecture

The FR family CPU uses the Harvard architecture in which the instruction bus and data bus are independent of each other.

A 32-bit  $\leftrightarrow$  16-bit bus adapter is connected to the 32-bit bus (D-bus) to provide an interface between the CPU and peripheral resources.

A Harvard  $\leftrightarrow$  Princeton bus converter is connected to both the I-bus and D-bus to provide an interface between the CPU and the bus controller.

The following figure shows the internal architecture structure.

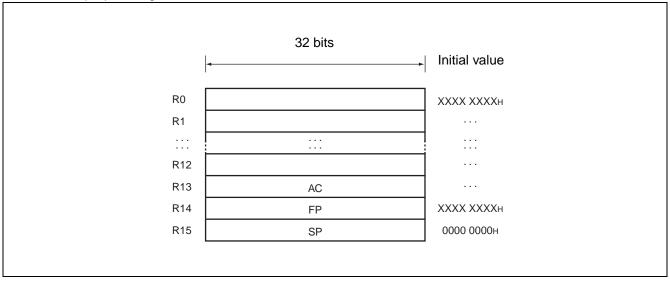

# 3. Programming model• Basic programming model

|                             |     | 32 bits           |               |

|-----------------------------|-----|-------------------|---------------|

|                             |     | <b> </b> →        | Initial value |

| (                           | R0  |                   | XXXX XXXXH    |

|                             | R1  |                   |               |

|                             | ::: | :::               | :::           |

| General-purpose registers < | R12 |                   |               |

|                             | R13 | AC                |               |

|                             | R14 | FP                | XXXX XXXXH    |

|                             | R15 | SP                | 0000 0000н    |

| Program status              |     |                   |               |

| Program counter             | PC  |                   |               |

|                             | RS  | ILM     SCR   CCR |               |

| Table base register         | TBR |                   |               |

| Return pointer              | RP  |                   |               |

| System stack pointer        | SSP |                   |               |

| User stack pointer          | USP |                   |               |

| Multiply and divide result  | MDH |                   |               |

| registers                   | MDL |                   |               |

#### 4. Registers

General-purpose register

Registers R0 to R15 are general-purpose registers. These registers can be used as accumulators for computation operations and as pointers for memory access.

Enhanced commands are provided for some of the 16 registers to enable their use for particular applications.

R13: Virtual accumulator

R14 : Frame pointer R15 : Stack pointer

Initial values at reset are undefined for R0 to R14. The value for R15 is 00000000H (SSP value).

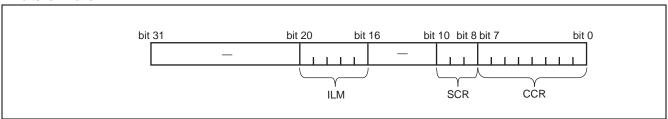

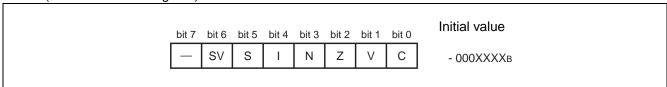

#### • PS (Program Status)

This register holds the program status, and is divided into three parts, ILM, SCR, and CCR.

All undefined bits (-) in the diagram are reserved bits. The values are always read "0". Write access to these bits is invalid.

#### • CCR (Condition Code Register)

SV : Supervisor S : Stack flag

I : Interrupt enable flagN : Negative enable flag

Z : Zero flagV : Overflow flagC : Carry flag

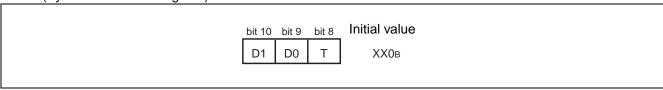

| <ul> <li>SCR (System Condition Registe</li> </ul> | • SCR | (System | Condition | Register |

|---------------------------------------------------|-------|---------|-----------|----------|

|---------------------------------------------------|-------|---------|-----------|----------|

Flag for step multiplication (D1, D0)

This flag stores interim data during execution of step multiplication.

Step trace trap flag (T)

This flag indicates whether the step trace trap is enabled or disabled.

The step trace trap function is used by emulators. When an emulator is in use, it cannot be used in execution of user programs.

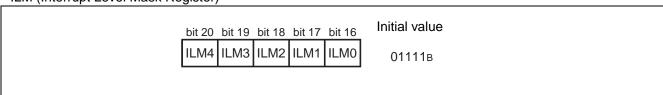

#### • ILM (Interrupt Level Mask Register)

This register stores interrupt level mask values, and the values stored in ILM4 to ILM0 are used for level masking. The register is initialized to value "01111<sub>B</sub>" at reset.

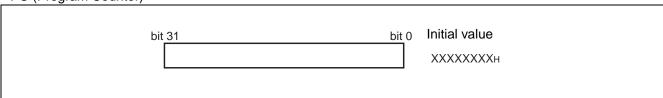

• PC (Program Counter)

The program counter indicates the address of the instruction that is being executed.

The initial value at reset is undefined.

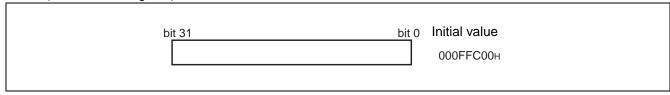

• TBR (Table Base Register)

The table base register stores the starting address of the vector table used in EIT processing.

The initial value at reset is 000FFC00<sub>H</sub>.

| • RP | (Return | Pointer) |

|------|---------|----------|

|------|---------|----------|

The return pointer stores the address to return from subroutines.

During execution of a CALL instruction, the PC value is transferred to this RP register.

During execution of a RET instruction, the contents of the RP register are transferred to PC.

The initial value at reset is undefined.

#### • USP (User Stack Pointer)

When the S flag is "1", the user stack pointer functions as the R15 register.

• The USP register can also be explicitly specified.

The initial value at reset is undefined.

• This register cannot be used with RETI instructions.

• Multiply & divide registers

These registers are for multiplication and division, and are each 32 bits in length.

The initial value at reset is undefined.

#### **■ MODE SETTING**

In the FR family, the mode pins (MD2, MD1, MD0) and the mode register (MODR) are used to set the operating mode.

#### 1. Mode pins

The three pins MD2, MD1, MD0 are used to specify the mode vector fetch.

Settings other than shown in the table are prohibited.

| M   | Mode pins* |     | Mode name                | Reset vector | Remarks     |  |

|-----|------------|-----|--------------------------|--------------|-------------|--|

| MD2 | MD1        | MD0 | Wiode Haine              | access area  | Remarks     |  |

| 0   | 0          | 0   | Internal ROM mode vector | Internal     |             |  |

| 0   | 0          | 1   | External ROM mode vector | External     | Not allowed |  |

<sup>\*:</sup> Always use MD3 with "0".

#### 2. Mode register (MODR)

The data written to the mode register using mode vector fetch is called mode data.

After the mode register (MODR) is set, the device operates according to the operation mode set in this register.

The mode register is set by all reset sources. User programs cannot write data to the mode register.

Rewriting is allowed in the emulator mode. In this case, use an 8-bit length data transfer instruction.

Data cannot be written by the transfer instruction of the 16/32-bit length.

Be sure to set these bits to "00000111<sub>B</sub>".

Operation is not guaranteed when any value other than "00000111<sub>B</sub>" is set.

Note: The mode data needs to be allocated in 000FFFF8<sub>H</sub> as byte data. The mode data (00000111<sub>B</sub>) must be allocated in bit 31 to bit 24, as the FR family uses the big endian architecture.

#### ■ RECOMMENDED SETTING

#### 1. Setting of PLL and clock gear

Recommended setting of PLL division and clock gear

| Clock input | PLL multiplied setting |      | Clock gear setting |      | PLL (vco) output (X) | Base clock |

|-------------|------------------------|------|--------------------|------|----------------------|------------|

| [MHz]       | DIVM                   | DIVN | DIVG               | MULG | [MHz]                | [MHz]      |

| 4           | 2                      | 20   | 16                 | 20   | 160                  | 80         |

| 4           | 2                      | 19   | 16                 | 20   | 152                  | 76         |

| 4           | 2                      | 18   | 16                 | 20   | 144                  | 72         |

| 4           | 2                      | 17   | 16                 | 16   | 136                  | 68         |

| 4           | 2                      | 16   | 16                 | 16   | 128                  | 64         |

| 4           | 2                      | 15   | 16                 | 16   | 120                  | 60         |

| 4           | 2                      | 14   | 16                 | 16   | 112                  | 56         |

| 4           | 2                      | 13   | 16                 | 12   | 104                  | 52         |

| 4           | 2                      | 12   | 16                 | 12   | 96                   | 48         |

| 4           | 2                      | 11   | 16                 | 12   | 88                   | 44         |

| 4           | 4                      | 10   | 16                 | 24   | 160                  | 40         |

| 4           | 4                      | 9    | 16                 | 24   | 144                  | 36         |

| 4           | 4                      | 8    | 16                 | 24   | 128                  | 32         |

| 4           | 4                      | 7    | 16                 | 24   | 112                  | 28         |

| 4           | 6                      | 6    | 16                 | 24   | 144                  | 24         |

| 4           | 8                      | 5    | 16                 | 28   | 160                  | 20         |

| 4           | 10                     | 4    | 16                 | 32   | 160                  | 16         |

| 4           | 12                     | 3    | 16                 | 32   | 144                  | 12         |

#### 2. Setting of Flash memory controller

· Setting of flash access timing

For executing programs with a Flash memory, follow the settings below according to the frequency of CPU clock (CLKB). This setting is the most suitable for a high-speed access to the Flash memory.

#### At Flash memory read operating

| CPU clock (CLKB) | ATD | ALEH | EQ | WEXH | WTC |

|------------------|-----|------|----|------|-----|

| To 24 MHz        | 0   | 0    | 0  | 0    | 1   |

| To 48 MHz        | 0   | 0    | 1  | 0    | 2   |

| To 80 MHz        | 1   | 1    | 3  | 0    | 4   |

#### At Flash memory write operating

| CPU clock (CLKB) | ATD | ALEH | EQ | WEXH | WTC |

|------------------|-----|------|----|------|-----|

| To 32 MHz        | 1   | 0    | 1  | 0    | 4   |

| To 48 MHz        | 1   | 0    | 3  | 0    | 5   |

| To 64 MHz        | 1   | 1    | 3  | 0    | 6   |

| To 80 MHz        | 1   | 1    | 3  | 0    | 7   |

#### 3. Setting of clock modulator

The setting values in the table are defined within the rages of base clock frequency; 32 MHz to 80 MHz. The Flash memory access needs to be configured according to the Fmax.

PLL and clock gear need to be configured according to the base clock.

Setting of clock modulator

| Modulation<br>(k) | Internal parameter (N) | CMPR<br>[hex] | Base clock<br>[MHz] | Fmin<br>[MHz] | Fmax<br>[MHz] |

|-------------------|------------------------|---------------|---------------------|---------------|---------------|

| 1                 | 3                      | 026F          | 80                  | 72.6          | 89.1          |

| 1                 | 3                      | 026F          | 76                  | 69.1          | 84.5          |

| 1                 | 5                      | 02AE          | 76                  | 65.3          | 90.8          |

| 2                 | 3                      | 046E          | 76                  | 65.3          | 90.8          |

| 1                 | 3                      | 026F          | 72                  | 65.5          | 79.9          |

| 1                 | 5                      | 02AE          | 72                  | 62            | 85.8          |

| 1                 | 7                      | 02ED          | 72                  | 58.8          | 92.7          |

| 2                 | 3                      | 046E          | 72                  | 62            | 85.8          |

| 1                 | 3                      | 026F          | 68                  | 62            | 75.3          |

| 1                 | 5                      | 02AE          | 68                  | 58.7          | 80.9          |

| 1                 | 7                      | 02ED          | 68                  | 55.7          | 87.3          |

| 1                 | 9                      | 032C          | 68                  | 53            | 95            |

| 2                 | 3                      | 046E          | 68                  | 58.7          | 80.9          |

| 2                 | 5                      | 04AC          | 68                  | 53            | 95            |

| 3                 | 3                      | 066D          | 68                  | 55.7          | 87.3          |

| 4                 | 3                      | 086C          | 68                  | 53            | 95            |

| 1                 | 3                      | 026F          | 64                  | 58.5          | 70.7          |

| 1                 | 5                      | 02AE          | 64                  | 55.3          | 75.9          |

| 1                 | 7                      | 02ED          | 64                  | 52.5          | 82            |

| 1                 | 9                      | 032C          | 64                  | 49.9          | 89.1          |

| 2                 | 3                      | 046E          | 64                  | 55.3          | 75.9          |

| 2                 | 5                      | 04AC          | 64                  | 49.9          | 89.1          |

| 3                 | 3                      | 066D          | 64                  | 52.5          | 82            |

| 4                 | 3                      | 086C          | 64                  | 49.9          | 89.1          |

| 1                 | 3                      | 026F          | 60                  | 54.9          | 66.1          |

| 1                 | 5                      | 02AE          | 60                  | 51.9          | 71            |

| 1                 | 7                      | 02ED          | 60                  | 49.3          | 76.7          |

| 1                 | 9                      | 032C          | 60                  | 46.9          | 83.3          |

| 2                 | 3                      | 046E          | 60                  | 51.9          | 71            |

| 2                 | 5                      | 04AC          | 60                  | 46.9          | 83.3          |

| 3                 | 3                      | 066D          | 60                  | 49.3          | 76.7          |

| Modulation<br>(k) | Internal parameter (N) | CMPR<br>[hex] | Base clock<br>[MHz] | Fmin<br>[MHz] | Fmax<br>[MHz] |

|-------------------|------------------------|---------------|---------------------|---------------|---------------|

| 4                 | 3                      | 086C          | 60                  | 46.9          | 83.3          |

| 5                 | 3                      | 0A6B          | 60                  | 44.7          | 91.3          |

| 1                 | 3                      | 026F          | 56                  | 51.4          | 61.6          |

| 1                 | 5                      | 02AE          | 56                  | 48.6          | 66.1          |

| 1                 | 7                      | 02ED          | 56                  | 46.1          | 71.4          |

| 1                 | 9                      | 032C          | 56                  | 43.8          | 77.6          |

| 1                 | 11                     | 036B          | 56                  | 41.8          | 84.9          |

| 1                 | 13                     | 03AA          | 56                  | 39.9          | 93.8          |

| 2                 | 3                      | 046E          | 56                  | 48.6          | 66.1          |

| 2                 | 5                      | 04AC          | 56                  | 43.8          | 77.6          |

| 2                 | 7                      | 04EA          | 56                  | 39.9          | 93.8          |

| 3                 | 3                      | 066D          | 56                  | 46.1          | 71.4          |

| 4                 | 3                      | 086C          | 56                  | 43.8          | 77.6          |

| 5                 | 3                      | 0A6B          | 56                  | 41.8          | 84.9          |

| 1                 | 3                      | 026F          | 52                  | 47.8          | 57            |

| 1                 | 5                      | 02AE          | 52                  | 45.2          | 61.2          |

| 1                 | 7                      | 02ED          | 52                  | 42.9          | 66.1          |

| 1                 | 9                      | 032C          | 52                  | 40.8          | 71.8          |

| 1                 | 11                     | 036B          | 52                  | 38.8          | 78.6          |

| 1                 | 13                     | 03AA          | 52                  | 37.1          | 86.8          |

| 2                 | 3                      | 046E          | 52                  | 45.2          | 61.2          |

| 2                 | 5                      | 04AC          | 52                  | 40.8          | 71.8          |

| 2                 | 7                      | 04EA          | 52                  | 37.1          | 86.8          |

| 3                 | 3                      | 066D          | 52                  | 42.9          | 66.1          |

| 3                 | 5                      | 06AA          | 52                  | 37.1          | 86.8          |

| 4                 | 3                      | 086C          | 52                  | 40.8          | 71.8          |

| 5                 | 3                      | 0A6B          | 52                  | 38.8          | 78.6          |

| 6                 | 3                      | 0C6A          | 52                  | 37.1          | 86.8          |

| 1                 | 3                      | 026F          | 48                  | 44.2          | 52.5          |

| 1                 | 5                      | 02AE          | 48                  | 41.8          | 56.4          |

| 1                 | 7                      | 02ED          | 48                  | 39.6          | 60.9          |

| 1                 | 9                      | 032C          | 48                  | 37.7          | 66.1          |

| 1                 | 11                     | 036B          | 48                  | 35.9          | 72.3          |

| 1                 | 13                     | 03AA          | 48                  | 34.3          | 79.9          |

| 1                 | 15                     | 03E9          | 48                  | 32.8          | 89.1          |

| Modulation<br>(k) | Internal parameter (N) | CMPR<br>[hex] | Base clock<br>[MHz] | Fmin<br>[MHz] | Fmax<br>[MHz] |

|-------------------|------------------------|---------------|---------------------|---------------|---------------|

| 2                 | 3                      | 046E          | 48                  | 41.8          | 56.4          |

| 2                 | 5                      | 04AC          | 48                  | 37.7          | 66.1          |

| 2                 | 7                      | 04EA          | 48                  | 34.3          | 79.9          |

| 3                 | 3                      | 066D          | 48                  | 39.6          | 60.9          |

| 3                 | 5                      | 06AA          | 48                  | 34.3          | 79.9          |

| 4                 | 3                      | 086C          | 48                  | 37.7          | 66.1          |

| 5                 | 3                      | 0A6B          | 48                  | 35.9          | 72.3          |

| 6                 | 3                      | 0C6A          | 48                  | 34.3          | 79.9          |

| 7                 | 3                      | 0E69          | 48                  | 32.8          | 89.1          |

| 1                 | 3                      | 026F          | 44                  | 40.6          | 48.1          |

| 1                 | 5                      | 02AE          | 44                  | 38.4          | 51.6          |

| 1                 | 7                      | 02ED          | 44                  | 36.4          | 55.7          |

| 1                 | 9                      | 032C          | 44                  | 34.6          | 60.4          |

| 1                 | 11                     | 036B          | 44                  | 33            | 66.1          |

| 1                 | 13                     | 03AA          | 44                  | 31.5          | 73            |

| 1                 | 15                     | 03E9          | 44                  | 30.1          | 81.4          |

| 2                 | 3                      | 046E          | 44                  | 38.4          | 51.6          |

| 2                 | 5                      | 04AC          | 44                  | 34.6          | 60.4          |

| 2                 | 7                      | 04EA          | 44                  | 31.5          | 73            |

| 3                 | 3                      | 066D          | 44                  | 36.4          | 55.7          |

| 3                 | 5                      | 06AA          | 44                  | 31.5          | 73            |

| 4                 | 3                      | 086C          | 44                  | 34.6          | 60.4          |

| 4                 | 5                      | 08A8          | 44                  | 28.9          | 92.1          |

| 5                 | 3                      | 0A6B          | 44                  | 33            | 66.1          |

| 6                 | 3                      | 0C6A          | 44                  | 31.5          | 73            |

| 7                 | 3                      | 0E69          | 44                  | 30.1          | 81.4          |

| 1                 | 3                      | 026F          | 40                  | 37            | 43.6          |

| 1                 | 5                      | 02AE          | 40                  | 34.9          | 46.8          |

| 1                 | 7                      | 02ED          | 40                  | 33.1          | 50.5          |

| 1                 | 9                      | 032C          | 40                  | 31.5          | 54.8          |

| 1                 | 11                     | 036B          | 40                  | 30            | 59.9          |

| 1                 | 13                     | 03AA          | 40                  | 28.7          | 66.1          |

| 1                 | 15                     | 03E9          | 40                  | 27.4          | 73.7          |

| 2                 | 3                      | 046E          | 40                  | 34.9          | 46.8          |

| 2                 | 5                      | 04AC          | 40                  | 31.5          | 54.8          |

(Continued)

DS07-16607-4E

| Modulation<br>(k) | Internal parameter (N) | CMPR<br>[hex] | Base clock<br>[MHz] | Fmin<br>[MHz] | Fmax<br>[MHz] |

|-------------------|------------------------|---------------|---------------------|---------------|---------------|

| 2                 | 7                      | 04EA          | 40                  | 28.7          | 66.1          |

| 2                 | 9                      | 0528          | 40                  | 26.3          | 83.3          |

| 3                 | 3                      | 066D          | 40                  | 33.1          | 50.5          |

| 3                 | 5                      | 06AA          | 40                  | 28.7          | 66.1          |

| 3                 | 7                      | 06E7          | 40                  | 25.3          | 95.8          |

| 4                 | 3                      | 086C          | 40                  | 31.5          | 54.8          |

| 4                 | 5                      | 08A8          | 40                  | 26.3          | 83.3          |

| 5                 | 3                      | 0A6B          | 40                  | 30            | 59.9          |

| 6                 | 3                      | 0C6A          | 40                  | 28.7          | 66.1          |

| 7                 | 3                      | 0E69          | 40                  | 27.4          | 73.7          |

| 8                 | 3                      | 1068          | 40                  | 26.3          | 83.3          |

| 1                 | 3                      | 026F          | 36                  | 33.3          | 39.2          |

| 1                 | 5                      | 02AE          | 36                  | 31.5          | 42            |

| 1                 | 7                      | 02ED          | 36                  | 29.9          | 45.3          |

| 1                 | 9                      | 032C          | 36                  | 28.4          | 49.2          |

| 1                 | 11                     | 036B          | 36                  | 27.1          | 53.8          |

| 1                 | 13                     | 03AA          | 36                  | 25.8          | 59.3          |

| 1                 | 15                     | 03E9          | 36                  | 24.7          | 66.1          |

| 2                 | 3                      | 046E          | 36                  | 31.5          | 42            |

| 2                 | 5                      | 04AC          | 36                  | 28.4          | 49.2          |

| 2                 | 7                      | 04EA          | 36                  | 25.8          | 59.3          |

| 2                 | 9                      | 0528          | 36                  | 23.7          | 74.7          |

| 3                 | 3                      | 066D          | 36                  | 29.9          | 45.3          |

| 3                 | 5                      | 06AA          | 36                  | 25.8          | 59.3          |

| 3                 | 7                      | 06E7          | 36                  | 22.8          | 85.8          |

| 4                 | 3                      | 086C          | 36                  | 28.4          | 49.2          |

| 4                 | 5                      | 08A8          | 36                  | 23.7          | 74.7          |

| 5                 | 3                      | 0A6B          | 36                  | 27.1          | 53.8          |

| 6                 | 3                      | 0C6A          | 36                  | 25.8          | 59.3          |

| 7                 | 3                      | 0E69          | 36                  | 24.7          | 66.1          |

| 8                 | 3                      | 1068          | 36                  | 23.7          | 74.7          |

| 9                 | 3                      | 1267          | 36                  | 22.8          | 85.8          |

| 1                 | 3                      | 026F          | 32                  | 29.7          | 34.7          |

| 1                 | 5                      | 02AE          | 32                  | 28            | 37.3          |

| 1                 | 7                      | 02ED          | 32                  | 26.6          | 40.2          |

| Modulation (k) | Internal parameter (N) | CMPR<br>[hex] | Base clock<br>[MHz] | Fmin<br>[MHz] | Fmax<br>[MHz] |

|----------------|------------------------|---------------|---------------------|---------------|---------------|

| 1              | 9                      | 032C          | 32                  | 25.3          | 43.6          |

| 1              | 11                     | 036B          | 32                  | 24.1          | 47.7          |

| 1              | 13                     | 03AA          | 32                  | 23            | 52.5          |

| 1              | 15                     | 03E9          | 32                  | 22            | 58.6          |

| 2              | 3                      | 046E          | 32                  | 28            | 37.3          |

| 2              | 5                      | 04AC          | 32                  | 25.3          | 43.6          |

| 2              | 7                      | 04EA          | 32                  | 23            | 52.5          |

| 2              | 9                      | 0528          | 32                  | 21.1          | 66.1          |

| 2              | 11                     | 0566          | 32                  | 19.5          | 89.1          |

| 3              | 3                      | 066D          | 32                  | 26.6          | 40.2          |

| 3              | 5                      | 06AA          | 32                  | 23            | 52.5          |

| 3              | 7                      | 06E7          | 32                  | 20.3          | 75.9          |

| 4              | 3                      | 086C          | 32                  | 25.3          | 43.6          |

| 4              | 5                      | 08A8          | 32                  | 21.1          | 66.1          |

| 5              | 3                      | 0A6B          | 32                  | 24.1          | 47.7          |

| 5              | 5                      | 0AA6          | 32                  | 19.5          | 89.1          |

| 6              | 3                      | 0C6A          | 32                  | 23            | 52.5          |

| 7              | 3                      | 0E69          | 32                  | 22            | 58.6          |

| 8              | 3                      | 1068          | 32                  | 21.1          | 66.1          |

| 9              | 3                      | 1267          | 32                  | 20.3          | 75.9          |

| 10             | 3                      | 1466          | 32                  | 19.5          | 89.1          |

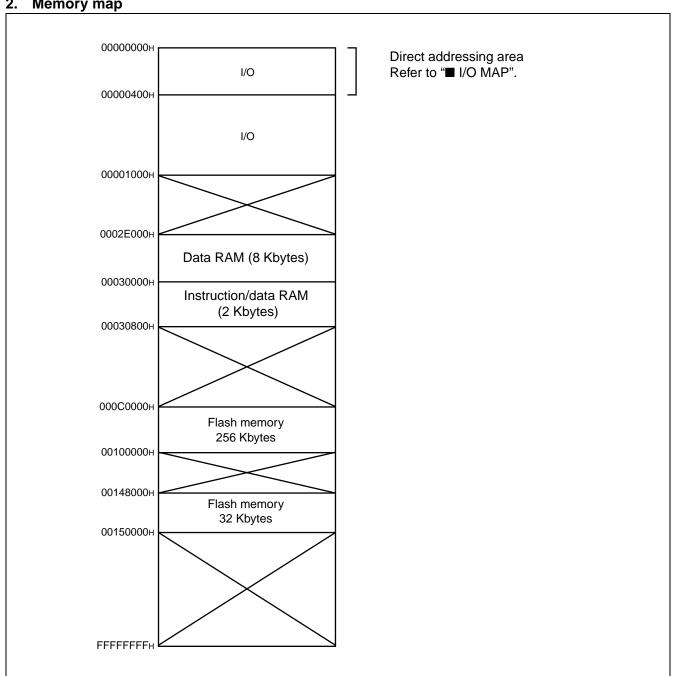

#### **■ MEMORY SPACE**

#### 1. Memory space

The FR family has 4 Gbytes of logical address space (2<sup>32</sup> addresses) available to the CPU by linear access.

• Direct addressing area

The following address space area is used for I/O.

This area is called direct addressing area, and the address of an operand can be specified directly in an instruction.

The size of directly addressable area depends on the length of the data to be accessed as shown below.

Byte data access : 000H to 0FFH Half word access : 000H to 1FFH Word data access : 000H to 3FFH

#### **Memory map**

#### 3. Flash memory sector configuration

|                          | MDOAFACONO                  |

|--------------------------|-----------------------------|

| addr                     | MB91F463NC                  |

| оот<br>0014:FFFFн        |                             |

| 0014:Е000н               | SA7(8 Kbytes)               |

| 0014:DFFFн               | 0.4.0(0.1(h.:.t)            |

| 0014:С000н               | SA6(8 Kbytes)               |

| 0014:BFFFн               | CAE(9 Khytoo)               |

| 0014:А000н               | SA5(8 Kbytes)               |

| 0014:9FFFн               | SA4(8 Kbytes)               |

| 0014:8000н               | e/(T(GT(B)(GG)              |

| 0014:7FFFн               | SA3(8 Kbytes)               |

| 0014:6000н<br>0014:5FFFн | ` , ,                       |

| 0014:35556               | SA2(8 Kbytes)               |

| 0014:3FFFн               |                             |

| 0014:2000н               | SA1(8 Kbytes)               |

| 0014:1FFFн               | 0.10(0.14)                  |

| 0014:0000н               | SA0(8 Kbytes)               |

| 0013:FFFFн               | CA22(64 Khytaa)             |

| 0013:0000н               | SA23(64 Kbytes)             |

| 0012:FFFFн               | SA22(64 Kbytes)             |

| 0012:0000н               | 6/122(04 Noytes)            |

| 0011:FFFFн               | SA21(64 Kbytes)             |

| 0011:0000н<br>0010:FFFFн |                             |

| 0010:РЕРЕН               | SA20(64 Kbytes)             |

| 0010.0000н<br>000F:FFFFн |                             |

| 000F:0000н               | SA19(64 Kbytes)             |

| 000E:FFFFн               | 0.4.0/0.4.1/1 / )           |

| 000Е:0000н               | SA18(64 Kbytes)             |

| 000D:FFFFн               | SA17(64 Kbytes)             |

| 000D:0000н               | OATT (04 Rbytes)            |

| 000С:FFFFн               | SA16(64 Kbytes)             |

| 000С:0000н               | (0.11.0)100)                |

| 000B:FFFFн<br>000B:0000н | SA15(64 Kbytes)             |

| 000Б.0000H<br>000А:FFFFн | , , ,                       |

| 000А:1111н               | SA14(64 Kbytes)             |

| 0009:FFFFн               | 0.1.0(0.1.1(1)              |

| 0009:0000н               | SA13(64 Kbytes)             |

| 0008:FFFFн               | SA12(64 Kbytes)             |

| 0008:0000н               | SA12(64 Rbyles)             |

| 0007:FFFFн               | SA11(64 Kbytes)             |

| 0007:0000н               | Critical Region)            |

| 0006:FFFFн               | SA10(64 Kbytes)             |

| 0006:0000н<br>0005:FFFFн |                             |

| 0005:ГЕГЕН               | SA9(64 Kbytes)              |

| 0003.0000н<br>0004:FFFFн |                             |

| 0004:11111н              | SA8(64 Kbytes)              |

| 223000                   | addr+0 addr+1 addr+2 addr+3 |

| 16-bit write mode        | dat[31:16] dat[15:0]        |

| 32-bit read mode         | dat[31:0]                   |

|                          | · · ·                       |

The shaded area is unusable.

Note: MB91F463NC has a different sector map for the flash memory to that of MB91F463NA. The sector map showed above is suited for MB91F463NC, not for MB91F463NA.

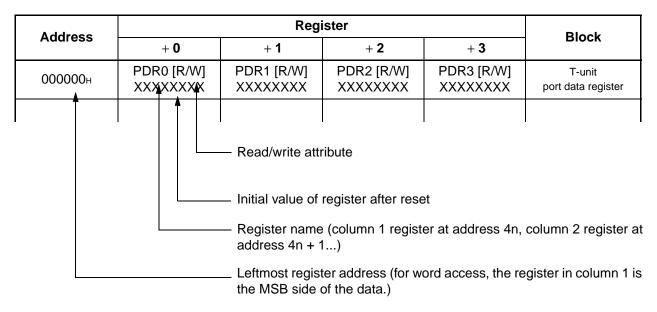

#### ■ I/O MAP

Note: Initial values of register bits are represented as follows:

- " 1 " : Initial value " 1 "

- " 0 " : Initial value " 0 "

- " X ": Initial value " undefined "

- " " : No physical register at this location