### 16-bit Proprietary Microcontroller

# F<sup>2</sup>MC-16FX MB96690 Series

# MB96F693R/A, MB96F695R/A, MB96F696R

### ■ DESCRIPTION

MB96690 series is based on FUJITSU's advanced  $F^2MC$ -16FX architecture (16-bit with instruction pipeline for RISC-like performance). The CPU uses the same instruction set as the established  $F^2MC$ -16LX family thus allowing for easy migration of  $F^2MC$ -16LX Software to the new  $F^2MC$ -16FX products.  $F^2MC$ -16FX product improvements compared to the previous generation include significantly improved performance - even at the same operation frequency, reduced power consumption and faster start-up time.

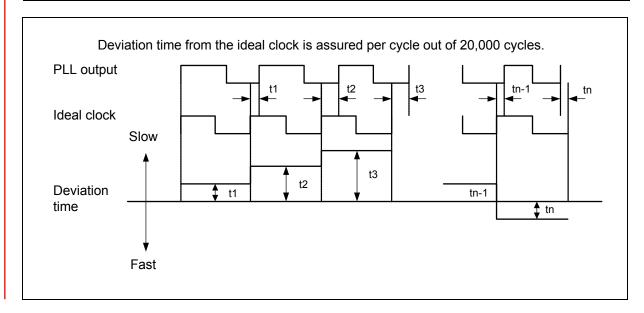

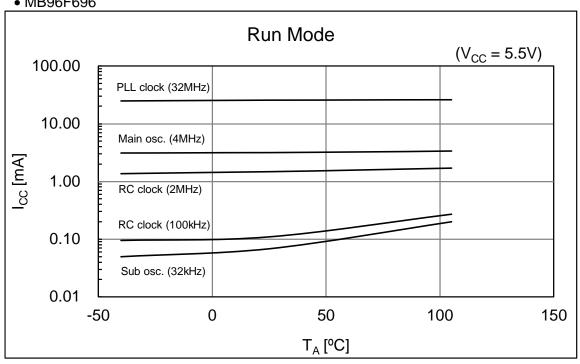

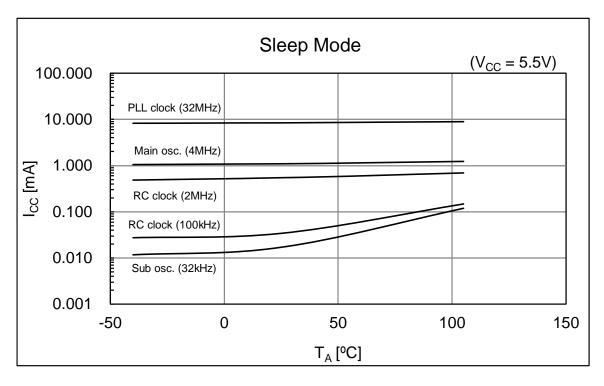

For high processing speed at optimized power consumption an internal PLL can be selected to supply the CPU with up to 32MHz operation frequency from an external 4MHz to 8MHz resonator. The result is a minimum instruction cycle time of 31.2ns going together with excellent EMI behavior. The emitted power is minimized by the on-chip voltage regulator that reduces the internal CPU voltage. A flexible clock tree allows selecting suitable operation frequencies for peripheral resources independent of the CPU speed.

Note: F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

FUJITSU SEMICONDUCTOR provides information facilitating product development via the following website. The website contains information useful for customers.

http://edevice.fujitsu.com/micom/en-support/

### **■ FEATURES**

### Technology

0.18µm CMOS

### • CPU

- F<sup>2</sup>MC-16FX CPU

- Optimized instruction set for controller applications (bit, byte, word and long-word data types, 23 different addressing modes, barrel shift, variety of pointers)

- 8-byte instruction queue

- $\bullet$  Signed multiply (16-bit × 16-bit) and divide (32-bit/16-bit) instructions available

### System clock

- On-chip PLL clock multiplier ( $\times 1$  to  $\times 8$ ,  $\times 1$  when PLL stop)

- 4MHz to 8MHz crystal oscillator (maximum frequency when using ceramic resonator depends on Q-factor)

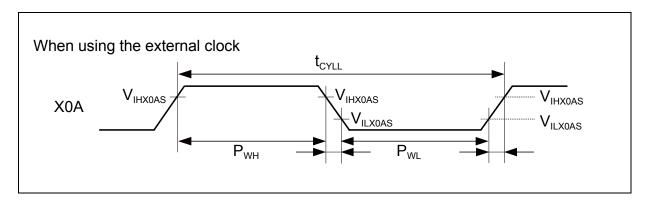

- Up to 8MHz external clock for devices with fast clock input feature

- 32.768kHz subsystem quartz clock

- 100kHz/2MHz internal RC clock for quick and safe startup, clock stop detection function, watchdog

- Clock source selectable from mainclock oscillator, subclock oscillator and on-chip RC oscillator, independently for CPU and 2 clock domains of peripherals

- The subclock oscillator is enabled by the Boot ROM program controlled by a configuration marker after a Power or External reset

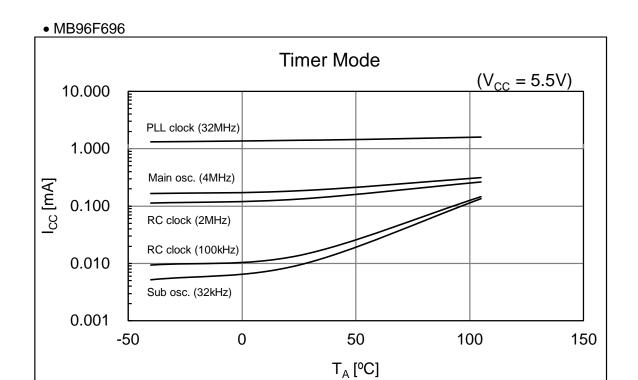

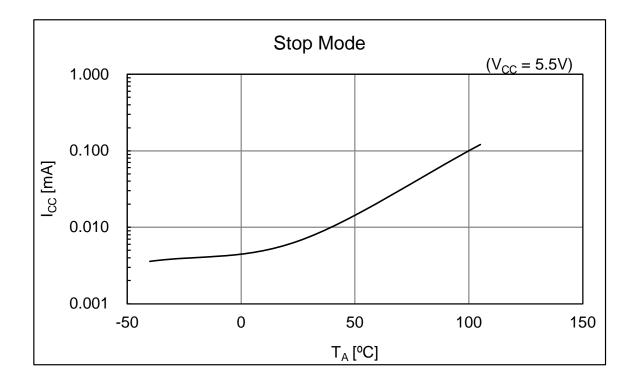

- Low Power Consumption 13 operating modes (different Run, Sleep, Timer, Stop modes)

### On-chip voltage regulator

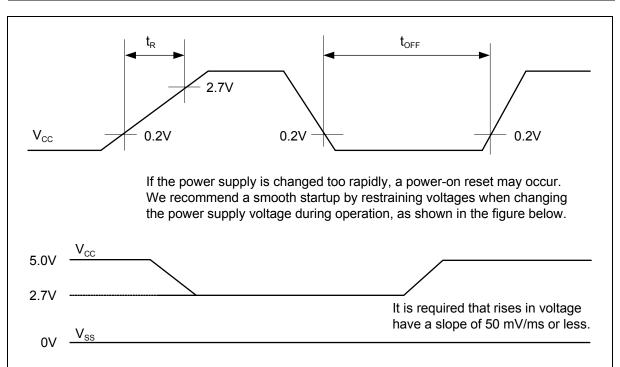

Internal voltage regulator supports a wide MCU supply voltage range (Min=2.7V), offering low power consumption

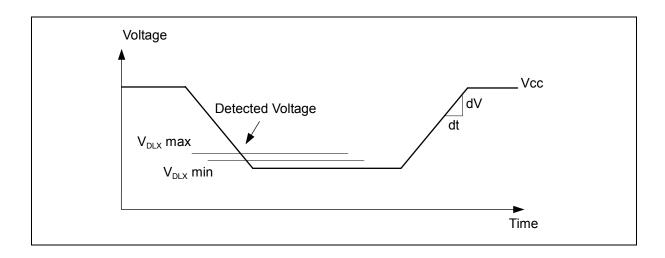

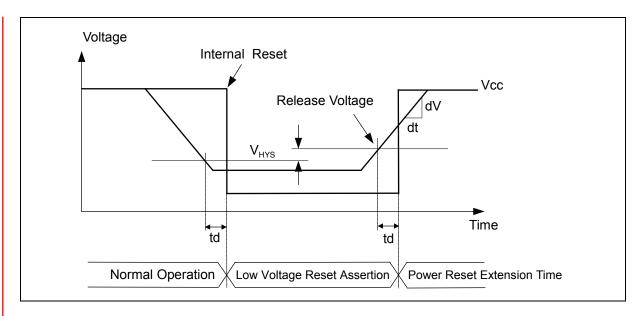

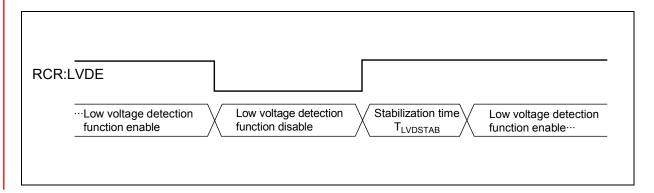

### • Low voltage detection function

Reset is generated when supply voltage falls below programmable reference voltage

### Code Security

Protects Flash Memory content from unintended read-out

### DMA

Automatic transfer function independent of CPU, can be assigned freely to resources

### Interrupts

- Fast Interrupt processing

- 8 programmable priority levels

- Non-Maskable Interrupt (NMI)

### CAN

- Supports CAN protocol version 2.0 part A and B

- ISO16845 certified

- Bit rates up to 1Mbps

- 32 message objects

- Each message object has its own identifier mask

- Programmable FIFO mode (concatenation of message objects)

- Maskable interrupt

- Disabled Automatic Retransmission mode for Time Triggered CAN applications

- Programmable loop-back mode for self-test operation

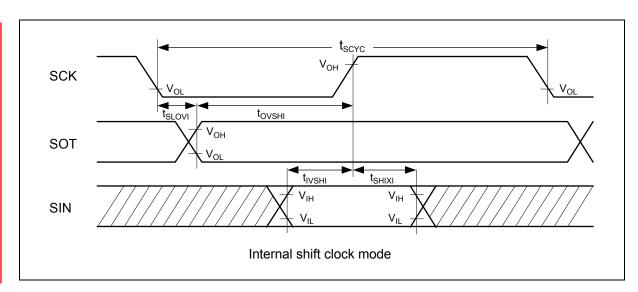

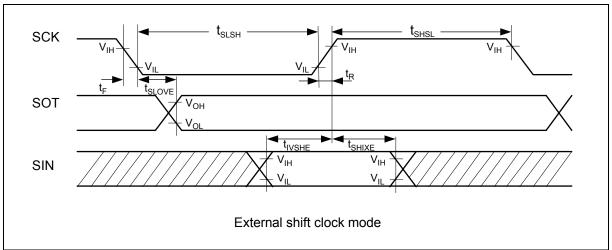

#### USART

- Full duplex USARTs (SCI/LIN)

- Wide range of baud rate settings using a dedicated reload timer

- Special synchronous options for adapting to different synchronous serial protocols

- LIN functionality working either as master or slave LIN device

- Extended support for LIN-Protocol with 16-byte FIFO for selected channels to reduce interrupt load

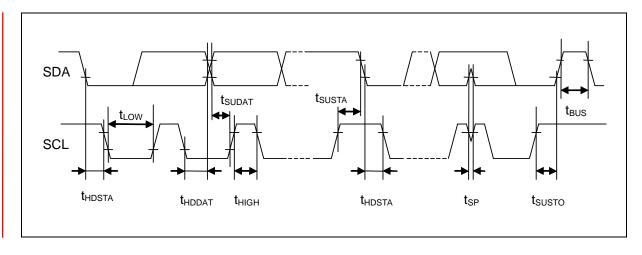

### • I<sup>2</sup>C

- Up to 400kbps

- Master and Slave functionality, 7-bit and 10-bit addressing

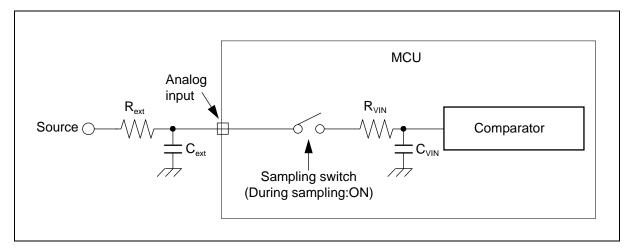

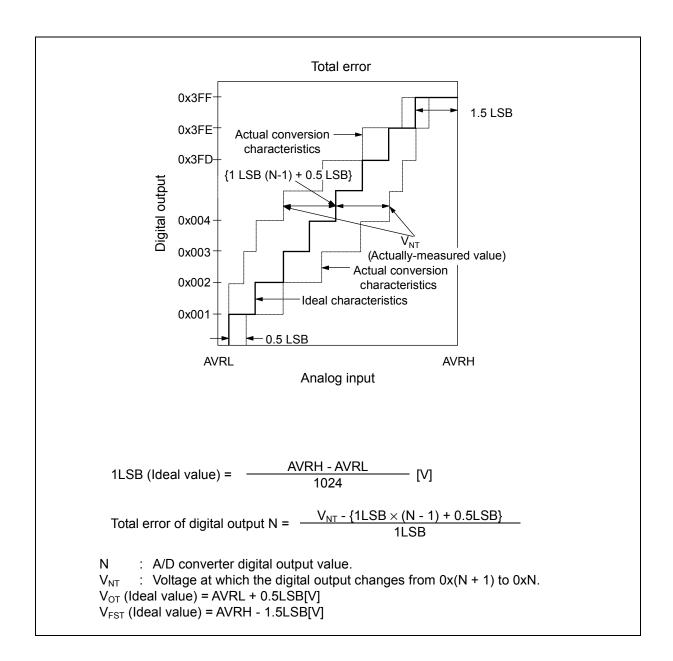

### A/D converter

- SAR-type

- 8/10-bit resolution

- Signals interrupt on conversion end, single conversion mode, continuous conversion mode, stop conversion mode, activation by software, external trigger, reload timers and PPGs

- Range Comparator Function

- Scan Disable Function

- ADC Pulse Detection Function

### Source Clock Timers

Three independent clock timers (23-bit RC clock timer, 23-bit Main clock timer, 17-bit Sub clock timer)

### • Hardware Watchdog Timer

- Hardware watchdog timer is active after reset

- Window function of Watchdog Timer is used to select the lower window limit of the watchdog interval

### Reload Timers

- 16-bit wide

- Prescaler with  $1/2^1$ ,  $1/2^2$ ,  $1/2^3$ ,  $1/2^4$ ,  $1/2^5$ ,  $1/2^6$  of peripheral clock frequency

- Event count function

### • Free-Running Timers

- Signals an interrupt on overflow, supports timer clear upon match with Output Compare (0, 4)

- Prescaler with 1,  $1/2^1$ ,  $1/2^2$ ,  $1/2^3$ ,  $1/2^4$ ,  $1/2^5$ ,  $1/2^6$ ,  $1/2^7$ ,  $1/2^8$  of peripheral clock frequency

### Input Capture Units

- 16-bit wide

- Signals an interrupt upon external event

- Rising edge, Falling edge or Both (rising & falling) edges sensitive

### Output Compare Units

- 16-bit wide

- Signals an interrupt when a match with Free-running Timer occurs

- A pair of compare registers can be used to generate an output signal

### Programmable Pulse Generator

- 16-bit down counter, cycle and duty setting registers

- Can be used as  $2 \times 8$ -bit PPG

- Interrupt at trigger, counter borrow and/or duty match

- PWM operation and one-shot operation

- Internal prescaler allows 1, 1/4, 1/16, 1/64 of peripheral clock as counter clock or of selected Reload timer underflow as clock input

- Can be triggered by software or reload timer

- Can trigger ADC conversion

- Timing point capture

- Start delay

### • Stepping Motor Controller

- Stepping Motor Controller with integrated high current output drivers

- Four high current outputs for each channel

- Two synchronized 8/10-bit PWMs per channel

- Internal prescaling for PWM clock: 1, 1/4, 1/5, 1/6, 1/8, 1/10, 1/12, 1/16 of peripheral clock

- Dedicated power supply for high current output drivers

### LCD Controller

- LCD controller with up to 4COM × 36SEG

- Internal or external voltage generation

- Duty cycle: Selectable from options: 1/2, 1/3 and 1/4

- Fixed 1/3 bias

- Programmable frame period

- Clock source selectable from four options (main clock, peripheral clock, subclock or RC oscillator clock)

- Internal divider resistors or external divider resistors

- On-chip data memory for display

- LCD display can be operated in Timer Mode

- Blank display: selectable

- All SEG, COM and V pins can be switched between general and specialized purposes

#### Sound Generator

- 8-bit PWM signal is mixed with tone frequency from 16-bit reload counter

- PWM clock by internal prescaler: 1, 1/2, 1/4, 1/8 of peripheral clock

### Real Time Clock

- Operational on main oscillation (4MHz), sub oscillation (32kHz) or RC oscillation (100kHz/2MHz)

- Capable to correct oscillation deviation of Sub clock or RC oscillator clock (clock calibration)

- Read/write accessible second/minute/hour registers

- Can signal interrupts every half second/second/minute/hour/day

- Internal clock divider and prescaler provide exact 1s clock

### External Interrupts

- Edge or Level sensitive

- Interrupt mask bit per channel

- Each available CAN channel RX has an external interrupt for wake-up

- Selected USART channels SIN have an external interrupt for wake-up

### Non Maskable Interrupt

- Disabled after reset, can be enabled by Boot-ROM depending on ROM configuration block

- Once enabled, can not be disabled other than by reset

- High or Low level sensitive

- Pin shared with external interrupt 0

### • I/O Ports

- Most of the external pins can be used as general purpose I/O

- All push-pull outputs (except when used as I<sup>2</sup>C SDA/SCL line)

- Bit-wise programmable as input/output or peripheral signal

- Bit-wise programmable input enable

- One input level per GPIO-pin (either Automotive or CMOS hysteresis)

- Bit-wise programmable pull-up resistor

### • Built-in On Chip Debugger (OCD)

- One-wire debug tool interface

- Break function:

- Hardware break: 6 points (shared with code event)

- Software break: 4096 points

- Event function

- Code event: 6 points (shared with hardware break)

- Data event: 6 points

- Event sequencer: 2 levels + reset

- Execution time measurement function

- Trace function: 42 branches

- Security function

### • Flash Memory

- Dual operation flash allowing reading of one Flash bank while programming or erasing the other bank

- Command sequencer for automatic execution of programming algorithm and for supporting DMA for programming of the Flash Memory

- Supports automatic programming, Embedded Algorithm

- Write/Erase/Erase-Suspend/Resume commands

- A flag indicating completion of the automatic algorithm

- Erase can be performed on each sector individually

- Sector protection

- Flash Security feature to protect the content of the Flash

- Low voltage detection during Flash erase or write

### ■ PRODUCT LINEUP

6

|                                 | Features                              |                                 | MB96690                                 | Remark                                                           |

|---------------------------------|---------------------------------------|---------------------------------|-----------------------------------------|------------------------------------------------------------------|

| Product Type                    |                                       | Flash Memory Product            | Remark                                  |                                                                  |

| Subclock                        |                                       | Subclock can be set by software |                                         |                                                                  |

| Dual Operation Flash Memory RAM |                                       | -                               |                                         |                                                                  |

| 64.5KB + 32KB 8KB               |                                       | MB96F693R, MB96F693A            | Product Options                         |                                                                  |

|                                 | 8.5KB + 32KB                          | 8KB                             | MB96F695R, MB96F695A                    | R: MCU with CAN                                                  |

|                                 | 6.5KB + 32KB                          | 16KB                            | MB96F696R                               | A: MCU without CAN                                               |

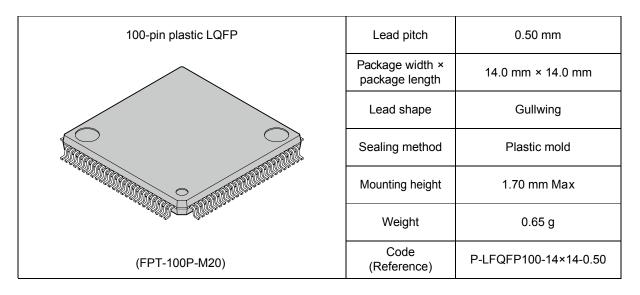

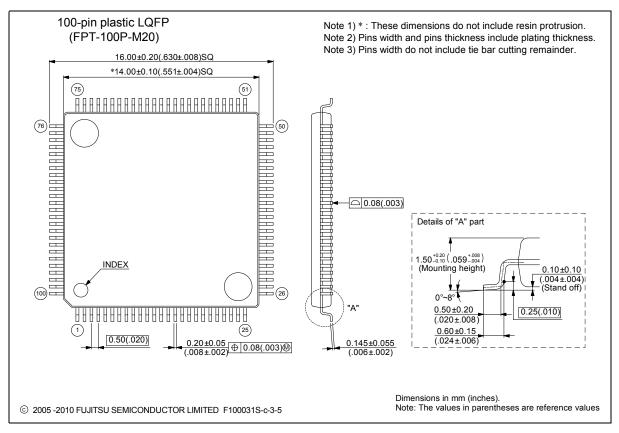

|                                 |                                       |                                 | LQFP-100                                |                                                                  |

| Package                         |                                       |                                 | FPT-100P-M20                            |                                                                  |

| DMA                             |                                       |                                 | 4ch                                     |                                                                  |

| USART                           |                                       |                                 | 5ch                                     | LIN-USART 0 to 2/4/5                                             |

|                                 | with automatic LIN-H                  | Header                          |                                         |                                                                  |

|                                 | transmission/receptio                 | n                               |                                         | I DI LIGADE O /I                                                 |

|                                 | with 16 byte RX- and                  |                                 | 2ch                                     | LIN-USART 0/1                                                    |

|                                 | TX-FIFO                               | •                               |                                         |                                                                  |

| I <sup>2</sup> C                | 1111110                               |                                 | 1ch                                     | $I^2C$ 0                                                         |

| 0/10.1:                         | 1 /D G                                |                                 |                                         | AN 2 to 4/6 to 8/10 to 12/                                       |

| 8/10-bit A                      | A/D Converter                         |                                 | 27ch                                    | 14 to 31                                                         |

|                                 | with Data Buffer                      |                                 | No                                      |                                                                  |

|                                 | with Range Compara                    | tor                             | Yes                                     |                                                                  |

|                                 | with Scan Disable                     |                                 | Yes                                     |                                                                  |

|                                 | with ADC Pulse Dete                   | ction                           | Yes                                     |                                                                  |

| 16-bit Re                       | load Timer (RLT)                      |                                 | 5ch                                     | RLT 0 to 3/6                                                     |

|                                 | ee-Running Timer (FRT                 | <u> </u>                        | 2ch                                     | FRT 0/1                                                          |

|                                 | C                                     | /                               |                                         | ICU 0/1/4 to 7                                                   |

| 16-bit Inı                      | out Capture Unit (ICU)                |                                 | 6ch                                     | (ICU 0/1/4 to 6                                                  |

|                                 | , c (- c c )                          |                                 | (5 channels for LIN-USART)              | for LIN-USART)                                                   |

| 16-bit Oı                       | 16-bit Output Compare Unit (OCU)      |                                 | 4ch                                     | OCU 0 to 3                                                       |

| 8/16-bit I<br>(PPG)             | 8/16-bit Programmable Pulse Generator |                                 | 10ch (16-bit) / 14ch (8-bit)            | PPG 0 to 7/14/15                                                 |

| ,                               | with Timing point cap                 | oture                           | Yes                                     |                                                                  |

|                                 | with Start delay                      |                                 | Yes                                     |                                                                  |

|                                 | with Ramp                             |                                 | No                                      |                                                                  |

| CANIL                           | C                                     |                                 | 1 1                                     | CAN 0                                                            |

| CAN Inte                        | erface                                |                                 | 1ch                                     | 32 Message Buffers                                               |

| Stepping                        | Motor Controller (SMC                 | C)                              | 4ch                                     | SMC 0 to 2/4                                                     |

|                                 | Interrupts (INT)                      |                                 | 16ch                                    | INT 0 to 15                                                      |

| Non-Mas                         | skable Interrupt (NMI)                |                                 | 1ch                                     |                                                                  |

|                                 | Sound Generator (SG)                  |                                 | 2ch                                     | SG 0/1                                                           |

|                                 |                                       |                                 |                                         | COM 0 to 3                                                       |

| LCD Cor                         | ntroller                              |                                 | 4COM × 36SEG                            | SEG 0 to 4/7/                                                    |

|                                 |                                       |                                 |                                         | 11 to 28/30/33/36 to 45                                          |

| Real Tim                        | e Clock (RTC)                         |                                 | 1ch                                     |                                                                  |

|                                 |                                       |                                 | 75 (Dual clock mode)                    |                                                                  |

| I/O Ports                       |                                       |                                 | 77 (Single clock mode)                  |                                                                  |

| Clock Calibration Unit (CAL)    |                                       | 1ch                             |                                         |                                                                  |

| Clock Output Function           |                                       | 2ch                             |                                         |                                                                  |

|                                 | age Detection Function                |                                 | Yes                                     | Low voltage detection<br>function can be<br>disabled by software |

|                                 | e Watchdog Timer                      |                                 | Yes                                     |                                                                  |

|                                 | RC-oscillator                         |                                 | Yes                                     |                                                                  |

|                                 | Debugger                              |                                 | Yes                                     |                                                                  |

| Note: A                         | Il signals of the nerinhe             | ral function                    | n in each product cannot be allocated b | by limiting the pins of package                                  |

Note: All signals of the peripheral function in each product cannot be allocated by limiting the pins of package. It is necessary to use the port relocate function of the general I/O port according to your function use.

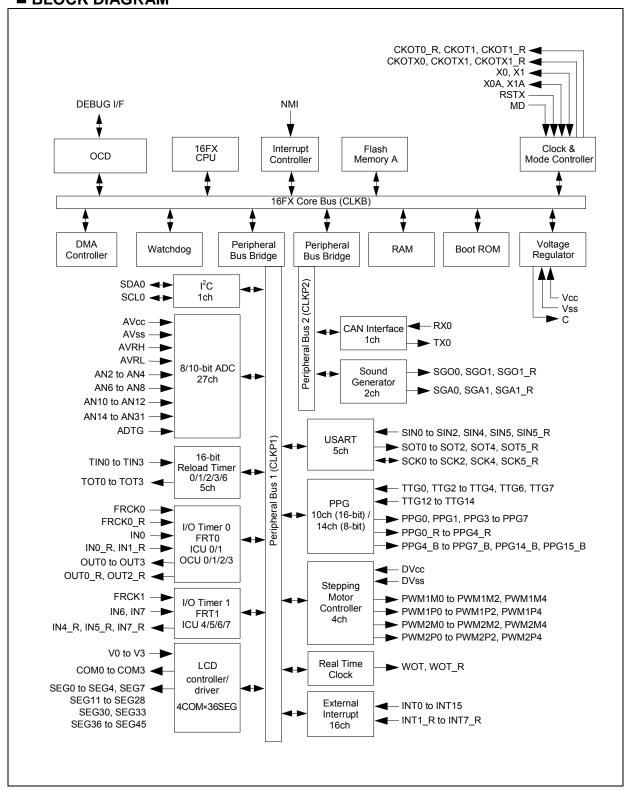

### **■ BLOCK DIAGRAM**

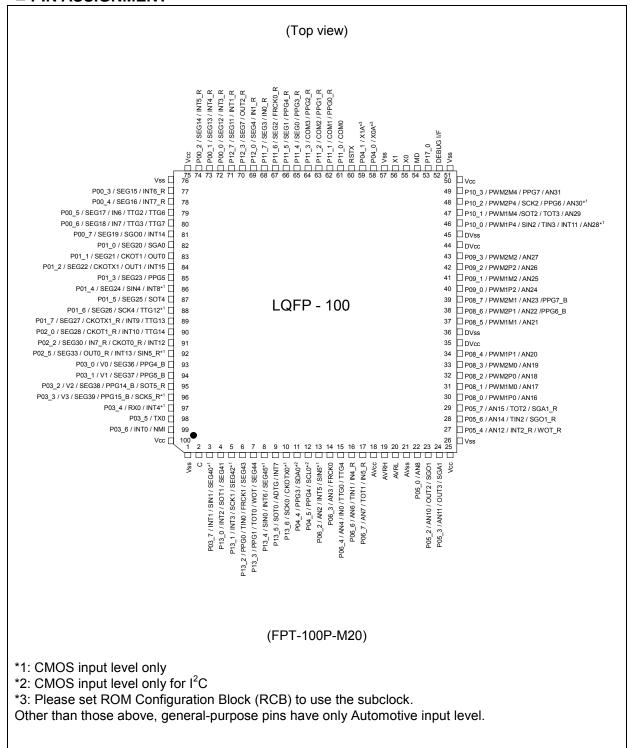

### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| ■ PIN DESCR | RIPTION               |                                                                  |  |

|-------------|-----------------------|------------------------------------------------------------------|--|

| Pin name    | Feature               | Description                                                      |  |

| ADTG        | ADC                   | A/D converter trigger input pin                                  |  |

| ANn         | ADC                   | A/D converter channel n input pin                                |  |

| AVcc        | Supply                | Analog circuits power supply pin                                 |  |

| AVRH        | ADC                   | A/D converter high reference voltage input pin                   |  |

| AVRL        | ADC                   | A/D converter low reference voltage input pin                    |  |

| AVss        | Supply                | Analog circuits power supply pin                                 |  |

| C           | Voltage regulator     | Internally regulated power supply stabilization capacitor pin    |  |

| CKOTn       | Clock Output function | Clock Output function n output pin                               |  |

| CKOTn_R     | Clock Output function | Relocated Clock Output function n output pin                     |  |

| CKOTXn      | Clock Output function | Clock Output function n inverted output pin                      |  |

| CKOTXn_R    | Clock Output function | Relocated Clock Output function n inverted output pin            |  |

| COMn        | LCD                   | LCD Common driver pin                                            |  |

| DEBUG I/F   | OCD                   | On Chip Debugger input/output pin                                |  |

| DVcc        | Supply                | SMC pins power supply                                            |  |

| DVss        | Supply                | SMC pins power supply                                            |  |

| FRCKn       | Free-Running Timer    | Free-Running Timer n input pin                                   |  |

| FRCKn_R     | Free-Running Timer    | Relocated Free-Running Timer n input pin                         |  |

| INn         | ICU                   | Input Capture Unit n input pin                                   |  |

| INn_R       | ICU                   | Relocated Input Capture Unit n input pin                         |  |

| INTn        | External Interrupt    | External Interrupt n input pin                                   |  |

| INTn_R      | External Interrupt    | Relocated External Interrupt n input pin                         |  |

| MD          | Core                  | Input pin for specifying the operating mode                      |  |

| NMI         | External Interrupt    | Non-Maskable Interrupt input pin                                 |  |

| OUTn        | OCU                   | Output Compare Unit n waveform output pin                        |  |

| OUTn_R      | OCU                   | Relocated Output Compare Unit n waveform output pin              |  |

| Pnn_m       | GPIO                  | General purpose I/O pin                                          |  |

| PPGn        | PPG                   | Programmable Pulse Generator n output pin (16bit/8bit)           |  |

| PPGn_R      | PPG                   | Relocated Programmable Pulse Generator n output pin (16bit/8bit) |  |

| PPGn_B      | PPG                   | Programmable Pulse Generator n output pin (16bit/8bit)           |  |

| PWMn        | SMC                   | SMC PWM high current output pin                                  |  |

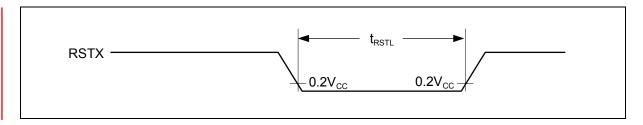

| RSTX        | Core                  | Reset input pin                                                  |  |

| RXn         | CAN                   | CAN interface n RX input pin                                     |  |

| SCKn        | USART                 | USART n serial clock input/output pin                            |  |

| SCKn_R      | USART                 | Relocated USART n serial clock input/output pin                  |  |

| SCLn        | I <sup>2</sup> C      | I <sup>2</sup> C interface n clock I/O input/output pin          |  |

| SDAn        | I <sup>2</sup> C      | I <sup>2</sup> C interface n serial data I/O input/output pin    |  |

| SEGn        | LCD                   | LCD Segment driver pin                                           |  |

| SGAn        | Sound Generator       | Sound Generator amplitude output pin                             |  |

| SGAn_R      | Sound Generator       | Relocated Sound Generator amplitude output pin                   |  |

| SGOn        | Sound Generator       | Sound Generator sound/tone output pin                            |  |

| SGOn_R      | Sound Generator       | Relocated Sound Generator sound/tone output pin                  |  |

| SINn        | USART                 | USART n serial data input pin                                    |  |

| SINn_R      | USART                 | Relocated USART n serial data input pin                          |  |

| SOTn        | USART                 | USART n serial data output pin                                   |  |

|             |                       |                                                                  |  |

10

| Pin name | Feature      | Description                                      |

|----------|--------------|--------------------------------------------------|

| SOTn_R   | USART        | Relocated USART n serial data output pin         |

| TINn     | Reload Timer | Reload Timer n event input pin                   |

| TOTn     | Reload Timer | Reload Timer n output pin                        |

| TTGn     | PPG          | Programmable Pulse Generator n trigger input pin |

| TXn      | CAN          | CAN interface n TX output pin                    |

| Vn       | LCD          | LCD voltage reference pin                        |

| Vcc      | Supply       | Power supply pin                                 |

| Vss      | Supply       | Power supply pin                                 |

| WOT      | RTC          | Real Time clock output pin                       |

| WOT_R    | RTC          | Relocated Real Time clock output pin             |

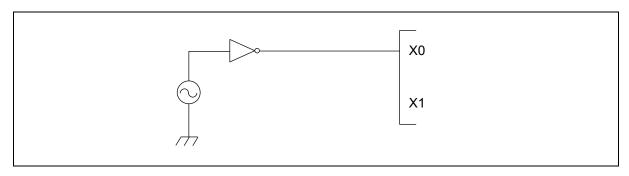

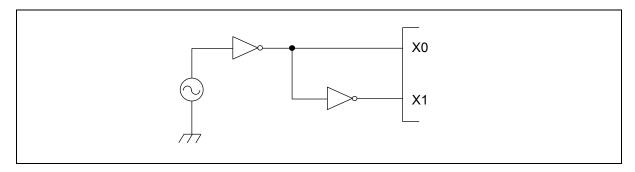

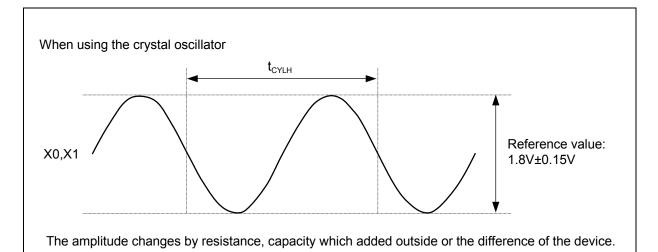

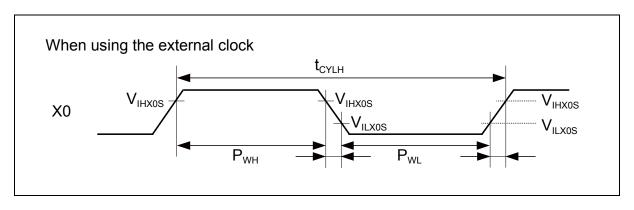

| X0       | Clock        | Oscillator input pin                             |

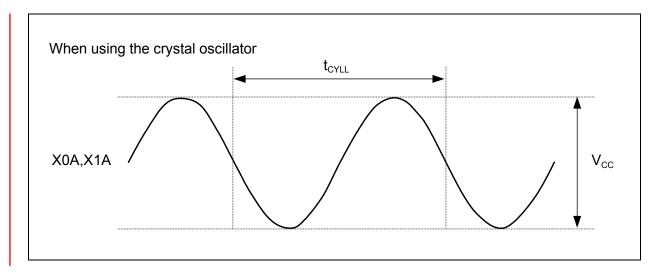

| X0A      | Clock        | Subclock Oscillator input pin                    |

| X1       | Clock        | Oscillator output pin                            |

| X1A      | Clock        | Subclock Oscillator output pin                   |

### ■ PIN CIRCUIT TYPE

| Pin no. | I/O circuit type* | Pin name                            |  |

|---------|-------------------|-------------------------------------|--|

| 1       | Supply            | Vss                                 |  |

| 2       | F                 | C                                   |  |

| 3       | P                 | P03_7 / INT1 / SIN1 / SEG40         |  |

| 4       | J                 | P13_0 / INT2 / SOT1 / SEG41         |  |

| 5       | P                 | P13_1 / INT3 / SCK1 / SEG42         |  |

| 6       | J                 | P13_2 / PPG0 / TIN0 / FRCK1 / SEG43 |  |

| 7       | J                 | P13_3 / PPG1 / TOT0 / WOT / SEG44   |  |

| 8       | P                 | P13_4 / SIN0 / INT6 / SEG45         |  |

| 9       | Н                 | P13_5 / SOT0 / ADTG / INT7          |  |

| 10      | M                 | P13_6 / SCK0 / CKOTX0               |  |

| 11      | N                 | P04_4 / PPG3 / SDA0                 |  |

| 12      | N                 | P04_5 / PPG4 / SCL0                 |  |

| 13      | I                 | P06_2 / AN2 / INT5 / SIN5           |  |

| 14      | K                 | P06_3 / AN3 / FRCK0                 |  |

| 15      | K                 | P06_4 / AN4 / IN0 / TTG0 / TTG4     |  |

| 16      | K                 | P06_6 / AN6 / TIN1 / IN4_R          |  |

| 17      | K                 | P06_7 / AN7 / TOT1 / IN5_R          |  |

| 18      | Supply            | AVcc                                |  |

| 19      | G                 | AVRH                                |  |

| 20      | G                 | AVRL                                |  |

| 21      | Supply            | AVss                                |  |

| 22      | K                 | P05_0 / AN8                         |  |

| 23      | K                 | P05_2 / AN10 / OUT2 / SGO1          |  |

| 24      | K                 | P05_3 / AN11 / OUT3 / SGA1          |  |

| 25      | Supply            | Vcc                                 |  |

| 26      | Supply            | Vss                                 |  |

| 27      | K                 | P05_4 / AN12 / INT2_R / WOT_R       |  |

| 28      | K                 | P05_6 / AN14 / TIN2 / SGO1_R        |  |

| 29      | K                 | P05_7 / AN15 / TOT2 / SGA1_R        |  |

| 30      | R                 | P08_0 / PWM1P0 / AN16               |  |

| 31      | R                 | P08_1 / PWM1M0 / AN17               |  |

| 32      | R                 | P08_2 / PWM2P0 / AN18               |  |

| 33      | R                 | P08_3 / PWM2M0 / AN19               |  |

| 34      | R                 | P08_4 / PWM1P1 / AN20               |  |

| 35      | Supply            | DVcc                                |  |

| 36      | Supply            | DVss                                |  |

| 37      | R                 | P08_5 / PWM1M1 / AN21               |  |

| 38      | R                 | P08_6 / PWM2P1 / AN22 / PPG6_B      |  |

| 39      | R                 | P08_7 / PWM2M1 / AN23 / PPG7_B      |  |

| 40      | R                 | P09_0 / PWM1P2 / AN24               |  |

12

| Pin no. | I/O circuit type* | Pin name                                    |  |

|---------|-------------------|---------------------------------------------|--|

| 41      | R                 | P09_1 / PWM1M2 / AN25                       |  |

| 42      | R                 | P09_2 / PWM2P2 / AN26                       |  |

| 43      | R                 | P09_3 / PWM2M2 / AN27                       |  |

| 44      | Supply            | DVcc                                        |  |

| 45      | Supply            | DVss                                        |  |

| 46      | S                 | P10_0 / PWM1P4 / SIN2 / TIN3 / INT11 / AN28 |  |

| 47      | R                 | P10_1 / PWM1M4 / SOT2 / TOT3 / AN29         |  |

| 48      | S                 | P10_2 / PWM2P4 / SCK2 / PPG6 / AN30         |  |

| 49      | R                 | P10_3 / PWM2M4 / PPG7 / AN31                |  |

| 50      | Supply            | Vcc                                         |  |

| 51      | Supply            | Vss                                         |  |

| 52      | 0                 | DEBUG I/F                                   |  |

| 53      | Н                 | P17_0                                       |  |

| 54      | C                 | MD                                          |  |

| 55      | A                 | X0                                          |  |

| 56      | A                 | X1                                          |  |

| 57      | Supply            | Vss                                         |  |

| 58      | В                 | P04_0 / X0A                                 |  |

| 59      | В                 | P04_1 / X1A                                 |  |

| 60      | C                 | RSTX                                        |  |

| 61      | J                 | P11_0 / COM0                                |  |

| 62      | J                 | P11_1 / COM1 / PPG0_R                       |  |

| 63      | J                 | P11_2 / COM2 / PPG1_R                       |  |

| 64      | J                 | P11_3 / COM3 / PPG2_R                       |  |

| 65      | J                 | P11_4 / SEG0 / PPG3_R                       |  |

| 66      | J                 | P11_5 / SEG1 / PPG4_R                       |  |

| 67      | J                 | P11_6 / SEG2 / FRCK0_R                      |  |

| 68      | J                 | P11_7 / SEG3 / IN0_R                        |  |

| 69      | J                 | P12_0 / SEG4 / IN1_R                        |  |

| 70      | J                 | P12_3 / SEG7 / OUT2_R                       |  |

| 71      | J                 | P12_7 / SEG11 / INT1_R                      |  |

| 72      | J                 | P00_0 / SEG12 / INT3_R                      |  |

| 73      | J                 | P00_1 / SEG13 / INT4_R                      |  |

| 74      | J                 | P00_2 / SEG14 / INT5_R                      |  |

| 75      | Supply            | Vcc                                         |  |

| 76      | Supply            | Vss                                         |  |

| 77      | J                 | P00_3 / SEG15 / INT6_R                      |  |

| 78      | J                 | P00_4 / SEG16 / INT7_R                      |  |

| 79      | J                 | P00_5 / SEG17 / IN6 / TTG2 / TTG6           |  |

| 80      | J                 | P00_6 / SEG18 / IN7 / TTG3 / TTG7           |  |

| Pin no. | I/O circuit type* | Pin name                                |  |

|---------|-------------------|-----------------------------------------|--|

| 81      | J                 | P00_7 / SEG19 / SGO0 / INT14            |  |

| 82      | J                 | P01_0 / SEG20 / SGA0                    |  |

| 83      | J                 | P01_1 / SEG21 / CKOT1 / OUT0            |  |

| 84      | J                 | P01_2 / SEG22 / CKOTX1 / OUT1 / INT15   |  |

| 85      | J                 | P01_3 / SEG23 / PPG5                    |  |

| 86      | P                 | P01_4 / SEG24 / SIN4 / INT8             |  |

| 87      | J                 | P01_5 / SEG25 / SOT4                    |  |

| 88      | P                 | P01_6 / SEG26 / SCK4 / TTG12            |  |

| 89      | J                 | P01_7 / SEG27 / CKOTX1_R / INT9 / TTG13 |  |

| 90      | J                 | P02_0 / SEG28 / CKOT1_R / INT10 / TTG14 |  |

| 91      | J                 | P02_2 / SEG30 / IN7_R / CKOT0_R / INT12 |  |

| 92      | P                 | P02_5 / SEG33 / OUT0_R / INT13 / SIN5_R |  |

| 93      | L                 | P03_0 / V0 / SEG36 / PPG4_B             |  |

| 94      | L                 | P03_1 / V1 / SEG37 / PPG5_B             |  |

| 95      | L                 | P03_2 / V2 / SEG38 / PPG14_B / SOT5_R   |  |

| 96      | Q                 | P03_3 / V3 / SEG39 / PPG15_B / SCK5_R   |  |

| 97      | M                 | P03_4 / RX0 / INT4                      |  |

| 98      | Н                 | P03_5 / TX0                             |  |

| 99      | Н                 | P03_6 / INT0 / NMI                      |  |

| 100     | Supply            | Vcc                                     |  |

<sup>\*:</sup> See "■ I/O CIRCUIT TYPE" for details on the I/O circuit types.

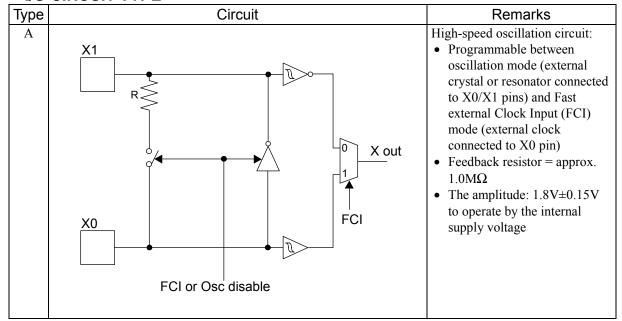

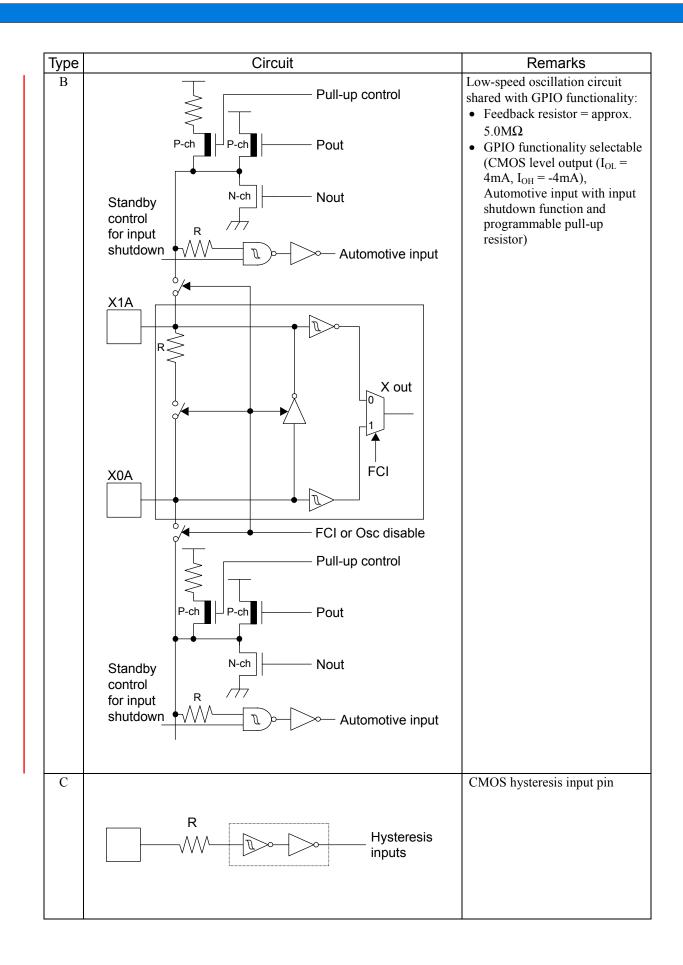

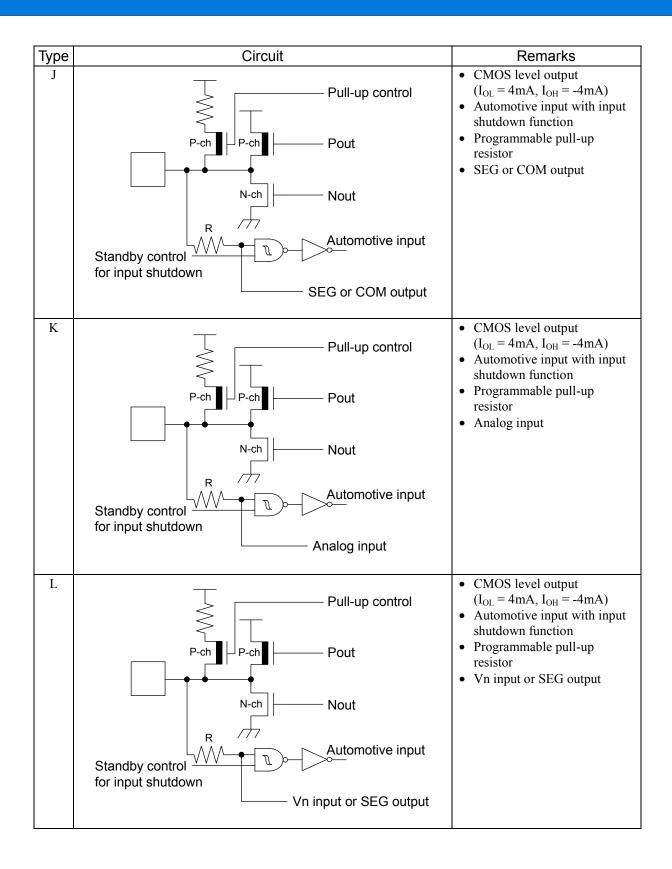

### ■ I/O CIRCUIT TYPE

| Туре | Circuit                                                                      | Remarks                                                                                                                                                                                 |

|------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F    | P-ch N-ch                                                                    | Power supply input protection circuit                                                                                                                                                   |

| G    | P-ch N-ch                                                                    | <ul> <li>A/D converter ref+ (AVRH), ref- (AVRL) power supply input pin with protection circuit</li> <li>Without protection circuit against V<sub>CC</sub> for pins AVRH/AVRL</li> </ul> |

| Н    | Pull-up control P-ch P-ch Pout N-ch Nout Automotive input for input shutdown | CMOS level output (I <sub>OL</sub> = 4mA, I <sub>OH</sub> = -4mA) Automotive input with input shutdown function Programmable pull-up resistor                                           |

| I    | P-ch P-ch Pout  N-ch Nout  Hysteresis input                                  | CMOS level output (I <sub>OL</sub> = 4mA, I <sub>OH</sub> = -4mA) CMOS hysteresis input with input shutdown function Programmable pull-up resistor Analog input                         |

|      | Standby control VVV Analog input  Analog input                               |                                                                                                                                                                                         |

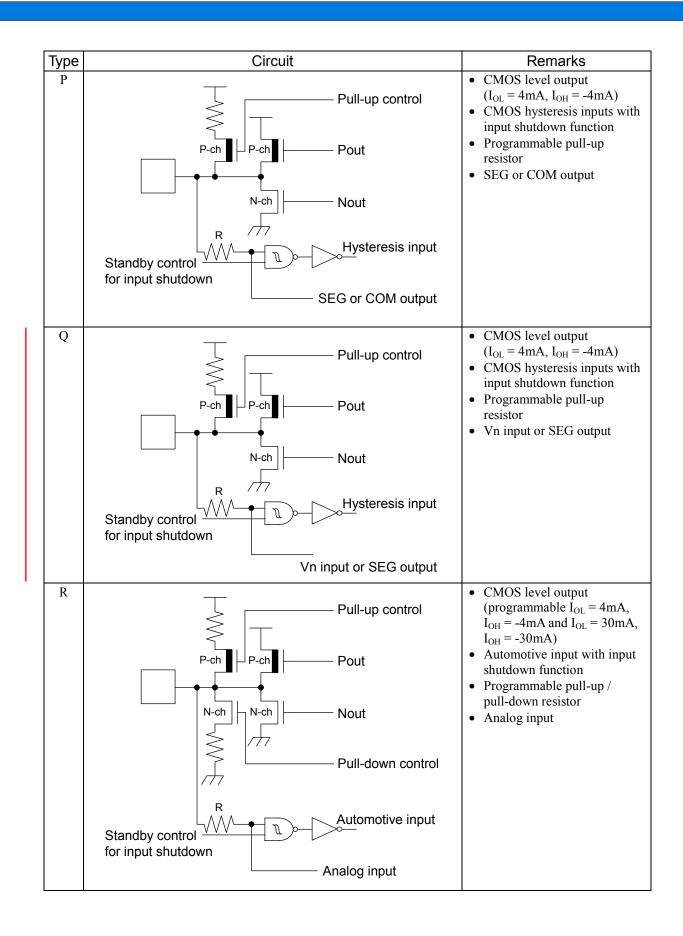

| Туре | Circuit                                                                                      | Remarks                                                                                                                                                                                                                                                                                                        |

|------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M    | Pull-up control P-ch P-ch Pout N-ch Nout Hysteresis input Standby control for input shutdown | <ul> <li>CMOS level output         (I<sub>OL</sub> = 4mA, I<sub>OH</sub> = -4mA)</li> <li>CMOS hysteresis input with input shutdown function</li> <li>Programmable pull-up resistor</li> </ul>                                                                                                                 |

| N    | Pull-up control P-ch P-ch Pout N-ch Nout* Hysteresis input for input shutdown                | <ul> <li>CMOS level output         (I<sub>OL</sub> = 3mA, I<sub>OH</sub> = -3mA)</li> <li>CMOS hysteresis input with input shutdown function</li> <li>Programmable pull-up resistor</li> <li>*: N-channel transistor has slew rate control according to I<sup>2</sup>C spec, irrespective of usage.</li> </ul> |

| O    | Standby control TTL input                                                                    | <ul> <li>Open-drain I/O</li> <li>Output 25mA, Vcc = 2.7V</li> <li>TTL input</li> </ul>                                                                                                                                                                                                                         |

| Type | Circuit                                                  | Remarks                                                                                                              |

|------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| S    | Pull-up control                                          | • CMOS level output<br>(programmable $I_{OL} = 4mA$ ,<br>$I_{OH} = -4mA$ and $I_{OL} = 30mA$ ,<br>$I_{OH} = -30mA$ ) |

|      | P-ch P-ch Pout                                           | <ul> <li>CMOS hysteresis input with<br/>input shutdown function</li> <li>Programmable pull-up /</li> </ul>           |

|      | N-ch N-ch Nout                                           | <ul><li>pull-down resistor</li><li>Analog input</li></ul>                                                            |

|      | Pull-down control                                        |                                                                                                                      |

|      | Standby control  R  Hysteresis input  for input shutdown |                                                                                                                      |

|      | Analog input                                             |                                                                                                                      |

### **■ MEMORY MAP**

| FF:FFFF <sub>H</sub> DE:0000 <sub>H</sub> | USER ROM*1         |

|-------------------------------------------|--------------------|

| DD:FFFF <sub>H</sub>                      | Reserved           |

| 10:0000 <sub>H</sub>                      |                    |

| 0F:C000 <sub>H</sub>                      | Boot-ROM           |

| 0E:9000 <sub>H</sub>                      | Peripheral         |

| 01:0000 <sub>H</sub>                      | Reserved           |

| 00:8000 <sub>H</sub>                      | ROM/RAM<br>MIRROR  |

| RAMSTART0*2                               | Internal RAM bank0 |

| 00:0C00 <sub>H</sub>                      | Reserved           |

| 00:0380 <sub>H</sub>                      | Peripheral         |

| 00:0180 <sub>H</sub>                      | GPR*3              |

| 00:0100 <sub>H</sub>                      | DMA                |

| 00:00F0 <sub>H</sub>                      | Reserved           |

| 00:0000 <sub>H</sub>                      | Peripheral         |

<sup>\*1:</sup> For details about USER ROM area, see "■USER ROM MEMORY MAP FOR FLASH DEVICES" on the following pages.

The DMA area is only available if the device contains the corresponding resource.

The available RAM and ROM area depends on the device.

<sup>\*2:</sup> For RAMSTART addresses, see the table on the next page.

<sup>\*3:</sup> Unused GPR banks can be used as RAM area. GPR: General-Purpose Register

### ■ RAMSTART ADDRESSES

| Devices              | Bank 0<br>RAM size | RAMSTART0            |

|----------------------|--------------------|----------------------|

| MB96F693<br>MB96F695 | 8KB                | 00:6200 <sub>H</sub> |

| MB96F696             | 16KB               | $00:4200_{\rm H}$    |

### ■ USER ROM MEMORY MAP FOR FLASH DEVICES

|                                              |                                              | MB96F693                    | MB96F695    | MB96F696                     |                   |

|----------------------------------------------|----------------------------------------------|-----------------------------|-------------|------------------------------|-------------------|

| CPU mode address                             | Flash memory mode address                    | Flash size<br>64.5KB + 32KB | Flash size  | Flash size<br>256.5KB + 32KB |                   |

| FF:FFFF <sub>H</sub><br>FF:0000 <sub>H</sub> | 3F:FFFF <sub>H</sub><br>3F:0000 <sub>H</sub> | SA39 - 64KB                 | SA39 - 64KB | SA39 - 64KB                  |                   |

| FE:FFFF <sub>H</sub>                         | 3E:FFFF <sub>H</sub>                         |                             | SA38 - 64KB | SA38 - 64KB                  |                   |

| FE:0000 <sub>H</sub><br>FD:FFFF <sub>H</sub> | 3E:0000 <sub>H</sub><br>3D:FFFF <sub>H</sub> |                             |             | SA37 - 64KB                  | Bank A of Flash   |

| FD:0000 <sub>H</sub><br>FC:FFFF <sub>H</sub> | 3D:0000 <sub>H</sub><br>3C:FFFF <sub>H</sub> | _                           |             |                              |                   |

| FC:0000 <sub>H</sub>                         | 3C:0000 <sub>H</sub>                         |                             |             | SA36 - 64KB                  |                   |

| DF:A000 <sub>H</sub><br>DF:9FFF <sub>H</sub> | 1F:9FFF <sub>H</sub>                         | Reserved                    | Reserved    | Reserved                     |                   |

| DF:8000 <sub>H</sub>                         | 1F:8000 <sub>H</sub>                         | SA4 - 8KB                   | SA4 - 8KB   | SA4 - 8KB                    |                   |

| DF:7FFF <sub>H</sub><br>DF:6000 <sub>H</sub> | 1F:7FFF <sub>H</sub><br>1F:6000 <sub>H</sub> | SA3 - 8KB                   | SA3 - 8KB   | SA3 - 8KB                    | Bank B of Flash   |

| DF:5FFF <sub>H</sub><br>DF:4000 <sub>H</sub> | 1F:5FFF <sub>H</sub><br>1F:4000 <sub>H</sub> | SA2 - 8KB                   | SA2 - 8KB   | SA2 - 8KB                    | Dalik D OI Flasii |

| ы .4000н                                     | 1F:3FFF <sub>H</sub><br>1F:2000 <sub>H</sub> | SA1 - 8KB                   | SA1 - 8KB   | SA1 - 8KB                    |                   |

| DF:3FFF <sub>H</sub> DF:2000 <sub>H</sub>    |                                              |                             |             |                              |                   |

| DF:3FFF <sub>H</sub>                         | 1F:1FFF <sub>H</sub><br>1F:0000 <sub>H</sub> | SAS - 512B*                 | SAS - 512B* | SAS - 512B*                  | Bank A of Flash   |

<sup>\*:</sup> Physical address area of SAS-512B is from DF:0000 $_{\rm H}$  to DF:01FF $_{\rm H}$ . Others (from DF:0200 $_{\rm H}$  to DF:1FFF $_{\rm H}$ ) is mirror area of SAS-512B. Sector SAS contains the ROM configuration block RCBA at CPU address DF:0000 $_{\rm H}$ -DF:01FF $_{\rm H}$ . SAS can not be used for E<sup>2</sup>PROM emulation.

### ■ SERIAL PROGRAMMING COMMUNICATION INTERFACE

USART pins for Flash serial programming (MD = 0, DEBUG I/F = 0, Serial Communication mode)

| MB96690    |                 |      |  |  |  |  |

|------------|-----------------|------|--|--|--|--|

| Pin Number | Normal Function |      |  |  |  |  |

| 8          |                 | SIN0 |  |  |  |  |

| 9          | USART0          | SOT0 |  |  |  |  |

| 10         |                 | SCK0 |  |  |  |  |

| 3          |                 | SIN1 |  |  |  |  |

| 4          | USART1          | SOT1 |  |  |  |  |

| 5          |                 | SCK1 |  |  |  |  |

| 46         |                 | SIN2 |  |  |  |  |

| 47         | USART2          | SOT2 |  |  |  |  |

| 48         |                 | SCK2 |  |  |  |  |

| 86         |                 | SIN4 |  |  |  |  |

| 87         | USART4          | SOT4 |  |  |  |  |

| 88         |                 | SCK4 |  |  |  |  |

### ■ INTERRUPT VECTOR TABLE

| Vector<br>number | Offset in vector table    | Vector name | Cleared by<br>DMA | Index in ICR to program | Description                     |  |

|------------------|---------------------------|-------------|-------------------|-------------------------|---------------------------------|--|

| 0                | 3FC <sub>H</sub>          | CALLV0      | No                | 1                       | CALLV instruction               |  |

| 1                | $3F8_{H}$                 | CALLV1      | No                | -                       | CALLV instruction               |  |

| 2                | $3F4_{H}$                 | CALLV2      | No                | -                       | CALLV instruction               |  |

| 3                | $3F0_{H}$                 | CALLV3      | No                | -                       | CALLV instruction               |  |

| 4                | 3EC <sub>H</sub>          | CALLV4      | No                | -                       | CALLV instruction               |  |

| 5                | 3E8 <sub>H</sub>          | CALLV5      | No                | -                       | CALLV instruction               |  |

| 6                | 3E4 <sub>H</sub>          | CALLV6      | No                | -                       | CALLV instruction               |  |

| 7                | $3E0_{H}$                 | CALLV7      | No                | -                       | CALLV instruction               |  |

| 8                | $3DC_H$                   | RESET       | No                | -                       | Reset vector                    |  |

| 9                | $3D8_{H}$                 | INT9        | No                | -                       | INT9 instruction                |  |

| 10               | $3D4_{H}$                 | EXCEPTION   | No                | -                       | Undefined instruction execution |  |

| 11               | $3D0_{H}$                 | NMI         | No                | -                       | Non-Maskable Interrupt          |  |

| 12               | 3CC <sub>H</sub>          | DLY         | No                | 12                      | Delayed Interrupt               |  |

| 13               | 3C8 <sub>H</sub>          | RC TIMER    | No                | 13                      | RC Clock Timer                  |  |

| 14               | 3C4 <sub>H</sub>          | MC TIMER    | No                | 14                      | Main Clock Timer                |  |

| 15               | $3C0_{H}$                 | SC TIMER    | No                | 15                      | Sub Clock Timer                 |  |

| 16               | $3BC_{H}$                 | LVDI        | No                | 16                      | Low Voltage Detector            |  |

| 17               | $3B8_{\mathrm{H}}$        | EXTINT0     | Yes               | 17                      | External Interrupt 0            |  |

| 18               | $3\mathrm{B4}_\mathrm{H}$ | EXTINT1     | Yes               | 18                      | External Interrupt 1            |  |

| 19               | $3\mathrm{B0_{H}}$        | EXTINT2     | Yes               | 19                      | External Interrupt 2            |  |

| 20               | $3AC_{H}$                 | EXTINT3     | Yes               | 20                      | External Interrupt 3            |  |

| 21               | $3A8_{\rm H}$             | EXTINT4     | Yes               | 21                      | External Interrupt 4            |  |

| 22               | $3A4_{H}$                 | EXTINT5     | Yes               | 22                      | External Interrupt 5            |  |

| 23               | $3A0_{H}$                 | EXTINT6     | Yes               | 23                      | External Interrupt 6            |  |

| 24               | 39C <sub>H</sub>          | EXTINT7     | Yes               | 24                      | External Interrupt 7            |  |

| 25               | 398 <sub>H</sub>          | EXTINT8     | Yes               | 25                      | External Interrupt 8            |  |

| 26               | 394 <sub>H</sub>          | EXTINT9     | Yes               | 26                      | External Interrupt 9            |  |

| 27               | $390_{\mathrm{H}}$        | EXTINT10    | Yes               | 27                      | External Interrupt 10           |  |

| 28               | 38C <sub>H</sub>          | EXTINT11    | Yes               | 28                      | External Interrupt 11           |  |

| 29               | $388_{ m H}$              | EXTINT12    | Yes               | 29                      | External Interrupt 12           |  |

| 30               | 384 <sub>H</sub>          | EXTINT13    | Yes               | 30                      | External Interrupt 13           |  |

| 31               | 380 <sub>H</sub>          | EXTINT14    | Yes               | 31                      | External Interrupt 14           |  |

| 32               | 37C <sub>H</sub>          | EXTINT15    | Yes               | 32                      | External Interrupt 15           |  |

| 33               | 378 <sub>H</sub>          | CAN0        | No                | 33                      | CAN Controller 0                |  |

| 34               | 374 <sub>H</sub>          | -           | -                 | 34                      | Reserved                        |  |

| 35               | 370 <sub>H</sub>          | -           | -                 | 35                      | Reserved                        |  |

| 36               | 36C <sub>H</sub>          | -           | -                 | 36                      | Reserved                        |  |

| 37               | 368 <sub>H</sub>          | -           | -                 | 37                      | Reserved                        |  |

| 38               | 364 <sub>H</sub>          | PPG0        | Yes               | 38                      | Programmable Pulse Generator 0  |  |

| 39               | 360 <sub>H</sub>          | PPG1        | Yes               | 39                      | Programmable Pulse Generator 1  |  |

| 40               | 35C <sub>H</sub>          | PPG2        | Yes               | 40                      | Programmable Pulse Generator 2  |  |

| Vector<br>number | Offset in vector table | Vector name | Cleared by DMA | Index in ICR to program | Description                     |  |

|------------------|------------------------|-------------|----------------|-------------------------|---------------------------------|--|

| 41               | 358 <sub>H</sub>       | PPG3        | Yes            | 41                      | Programmable Pulse Generator 3  |  |

| 42               | 354 <sub>H</sub>       | PPG4        | Yes            | 42                      | Programmable Pulse Generator 4  |  |

| 43               | $350_{\mathrm{H}}$     | PPG5        | Yes            | 43                      | Programmable Pulse Generator 5  |  |

| 44               | 34C <sub>H</sub>       | PPG6        | Yes            | 44                      | Programmable Pulse Generator 6  |  |

| 45               | $348_{\rm H}$          | PPG7        | Yes            | 45                      | Programmable Pulse Generator 7  |  |

| 46               | 344 <sub>H</sub>       | -           | -              | 46                      | Reserved                        |  |

| 47               | $340_{\rm H}$          | -           | -              | 47                      | Reserved                        |  |

| 48               | 33C <sub>H</sub>       | -           | -              | 48                      | Reserved                        |  |

| 49               | $338_{\rm H}$          | -           | -              | 49                      | Reserved                        |  |

| 50               | $334_{\rm H}$          | -           | -              | 50                      | Reserved                        |  |

| 51               | $330_{\mathrm{H}}$     | -           | -              | 51                      | Reserved                        |  |

| 52               | 32C <sub>H</sub>       | PPG14       | Yes            | 52                      | Programmable Pulse Generator 14 |  |

| 53               | $328_{\mathrm{H}}$     | PPG15       | Yes            | 53                      | Programmable Pulse Generator 15 |  |

| 54               | $324_{\rm H}$          | -           | -              | 54                      | Reserved                        |  |

| 55               | $320_{\mathrm{H}}$     | -           | -              | 55                      | Reserved                        |  |

| 56               | 31C <sub>H</sub>       | -           | -              | 56                      | Reserved                        |  |

| 57               | 318 <sub>H</sub>       | -           | -              | 57                      | Reserved                        |  |

| 58               | $314_{\rm H}$          | RLT0        | Yes            | 58                      | Reload Timer 0                  |  |

| 59               | $310_{\rm H}$          | RLT1        | Yes            | 59                      | Reload Timer 1                  |  |

| 60               | 30C <sub>H</sub>       | RLT2        | Yes            | 60                      | Reload Timer 2                  |  |

| 61               | $308_{\mathrm{H}}$     | RLT3        | Yes            | 61                      | Reload Timer 3                  |  |

| 62               | 304 <sub>H</sub>       | -           | -              | 62                      | Reserved                        |  |

| 63               | $300_{\mathrm{H}}$     | -           | -              | 63                      | Reserved                        |  |

| 64               | 2FC <sub>H</sub>       | RLT6        | Yes            | 64                      | Reload Timer 6                  |  |

| 65               | 2F8 <sub>H</sub>       | ICU0        | Yes            | 65                      | Input Capture Unit 0            |  |

| 66               | $2F4_{H}$              | ICU1        | Yes            | 66                      | Input Capture Unit 1            |  |

| 67               | $2F0_{H}$              | -           | -              | 67                      | Reserved                        |  |

| 68               | 2EC <sub>H</sub>       | -           | -              | 68                      | Reserved                        |  |

| 69               | 2E8 <sub>H</sub>       | ICU4        | Yes            | 69                      | Input Capture Unit 4            |  |

| 70               | 2E4 <sub>H</sub>       | ICU5        | Yes            | 70                      | Input Capture Unit 5            |  |

| 71               | $2E0_{H}$              | ICU6        | Yes            | 71                      | Input Capture Unit 6            |  |

| 72               | $2DC_{H}$              | ICU7        | Yes            | 72                      | Input Capture Unit 7            |  |

| 73               | $2D8_{H}$              | -           | -              | 73                      | Reserved                        |  |

| 74               | $2D4_{H}$              | -           | -              | 74                      | Reserved                        |  |

| 75               | $2D0_{H}$              | -           | -              | 75                      | Reserved                        |  |

| 76               | 2CC <sub>H</sub>       | -           | -              | 76                      | Reserved                        |  |

| 77               | 2C8 <sub>H</sub>       | OCU0        | Yes            | 77                      | Output Compare Unit 0           |  |

| 78               | 2C4 <sub>H</sub>       | OCU1        | Yes            | 78                      | Output Compare Unit 1           |  |

| 79               | 2C0 <sub>H</sub>       | OCU2        | Yes            | 79                      | Output Compare Unit 2           |  |

| 80               | 2BC <sub>H</sub>       | OCU3        | Yes            | 80                      | Output Compare Unit 3           |  |

| Vector<br>number | Offset in vector table    | Vector name | Cleared by DMA | Index in ICR to program | Description                  |  |

|------------------|---------------------------|-------------|----------------|-------------------------|------------------------------|--|

| 81               | $2B8_{H}$                 | -           | -              | 81                      | Reserved                     |  |

| 82               | $2B4_{H}$                 | -           | -              | 82                      | Reserved                     |  |

| 83               | $2\mathrm{B0}_\mathrm{H}$ | -           | -              | 83                      | Reserved                     |  |

| 84               | 2AC <sub>H</sub>          | -           | -              | 84                      | Reserved                     |  |

| 85               | $2A8_{H}$                 | -           | -              | 85                      | Reserved                     |  |

| 86               | $2A4_{H}$                 | -           | -              | 86                      | Reserved                     |  |

| 87               | $2A0_{H}$                 | -           | -              | 87                      | Reserved                     |  |

| 88               | 29C <sub>H</sub>          | -           | -              | 88                      | Reserved                     |  |

| 89               | 298 <sub>H</sub>          | FRT0        | Yes            | 89                      | Free-Running Timer 0         |  |

| 90               | 294 <sub>H</sub>          | FRT1        | Yes            | 90                      | Free-Running Timer 1         |  |

| 91               | $290_{\mathrm{H}}$        | -           | -              | 91                      | Reserved                     |  |

| 92               | 28C <sub>H</sub>          | -           | -              | 92                      | Reserved                     |  |

| 93               | $288_{\mathrm{H}}$        | RTC0        | No             | 93                      | Real Time Clock              |  |

| 94               | $284_{\rm H}$             | CAL0        | No             | 94                      | Clock Calibration Unit       |  |

| 95               | $280_{\mathrm{H}}$        | SG0         | No             | 95                      | Sound Generator 0            |  |

| 96               | 27C <sub>H</sub>          | IIC0        | Yes            | 96                      | I <sup>2</sup> C interface 0 |  |

| 97               | 278 <sub>H</sub>          | -           | -              | 97                      | Reserved                     |  |

| 98               | 274 <sub>H</sub>          | ADC0        | Yes            | 98                      | A/D Converter 0              |  |

| 99               | $270_{\mathrm{H}}$        | -           | -              | 99                      | Reserved                     |  |

| 100              | 26C <sub>H</sub>          | -           | -              | 100                     | Reserved                     |  |

| 101              | $268_{\mathrm{H}}$        | LINR0       | Yes            | 101                     | LIN USART 0 RX               |  |

| 102              | $264_{\mathrm{H}}$        | LINT0       | Yes            | 102                     | LIN USART 0 TX               |  |

| 103              | $260_{\mathrm{H}}$        | LINR1       | Yes            | 103                     | LIN USART 1 RX               |  |

| 104              | 25C <sub>H</sub>          | LINT1       | Yes            | 104                     | LIN USART 1 TX               |  |

| 105              | 258 <sub>H</sub>          | LINR2       | Yes            | 105                     | LIN USART 2 RX               |  |

| 106              | 254 <sub>H</sub>          | LINT2       | Yes            | 106                     | LIN USART 2 TX               |  |

| 107              | $250_{\mathrm{H}}$        | -           | -              | 107                     | Reserved                     |  |

| 108              | 24C <sub>H</sub>          | -           | -              | 108                     | Reserved                     |  |

| 109              | 248 <sub>H</sub>          | LINR4       | Yes            | 109                     | LIN USART 4 RX               |  |

| 110              | 244 <sub>H</sub>          | LINT4       | Yes            | 110                     | LIN USART 4 TX               |  |

| 111              | $240_{\mathrm{H}}$        | LINR5       | Yes            | 111                     | LIN USART 5 RX               |  |

| 112              | 23C <sub>H</sub>          | LINT5       | Yes            | 112                     | LIN USART 5 TX               |  |

| 113              | $238_{\mathrm{H}}$        | -           | -              | 113                     | Reserved                     |  |

| 114              | $234_{\rm H}$             | -           | -              | 114                     | Reserved                     |  |

| 115              | 230 <sub>H</sub>          | -           | -              | 115                     | Reserved                     |  |

| 116              | 22C <sub>H</sub>          | -           | -              | 116                     | Reserved                     |  |

| 117              | 228 <sub>H</sub>          | -           | -              | 117                     | Reserved                     |  |

| 118              | 224 <sub>H</sub>          | -           | -              | 118                     | Reserved                     |  |

| 119              | 220 <sub>H</sub>          | _           | _              | 119                     | Reserved                     |  |

| 120              | 21C <sub>H</sub>          | _           | _              | 120                     | Reserved                     |  |

| Vector<br>number | Offset in vector table | Vector name | Cleared by DMA | Index in ICR to program | Description                        |  |

|------------------|------------------------|-------------|----------------|-------------------------|------------------------------------|--|

| 121              | $218_{\mathrm{H}}$     | SG1         | No             | 121                     | Sound Generator 1                  |  |

| 122              | $214_{\rm H}$          | -           | -              | 122                     | Reserved                           |  |

| 123              | $210_{\mathrm{H}}$     | -           | -              | 123                     | Reserved                           |  |

| 124              | 20C <sub>H</sub>       | -           | -              | 124                     | Reserved                           |  |

| 125              | $208_{\mathrm{H}}$     | -           | -              | 125                     | Reserved                           |  |

| 126              | $204_{\mathrm{H}}$     | -           | -              | 126                     | Reserved                           |  |

| 127              | $200_{\mathrm{H}}$     | -           | -              | 127                     | Reserved                           |  |

| 128              | 1FC <sub>H</sub>       | -           | -              | 128                     | Reserved                           |  |

| 129              | 1F8 <sub>H</sub>       | -           | -              | 129                     | Reserved                           |  |

| 130              | 1F4 <sub>H</sub>       | -           | -              | 130                     | Reserved                           |  |

| 131              | 1F0 <sub>H</sub>       | -           | -              | 131                     | Reserved                           |  |

| 132              | 1EC <sub>H</sub>       | -           | -              | 132                     | Reserved                           |  |

| 133              | 1E8 <sub>H</sub>       | FLASHA      | Yes            | 133                     | Flash memory A interrupt           |  |

| 134              | 1E4 <sub>H</sub>       | -           | -              | 134                     | Reserved                           |  |

| 135              | 1E0 <sub>H</sub>       | -           | -              | 135                     | Reserved                           |  |

| 136              | 1DC <sub>H</sub>       | -           | -              | 136                     | Reserved                           |  |

| 137              | 1D8 <sub>H</sub>       | -           | -              | 137                     | Reserved                           |  |

| 138              | $1D4_{H}$              | -           | -              | 138                     | Reserved                           |  |

| 139              | $1D0_{H}$              | ADCRC0      | No             | 139                     | A/D Converter 0 - Range Comparator |  |

| 140              | 1CC <sub>H</sub>       | ADCPD0      | No             | 140                     | A/D Converter 0 - Pulse detection  |  |

| 141              | 1C8 <sub>H</sub>       | -           | -              | 141                     | Reserved                           |  |

| 142              | 1C4 <sub>H</sub>       | -           | -              | 142                     | Reserved                           |  |

| 143              | 1C0 <sub>H</sub>       | -           | -              | 143                     | Reserved                           |  |

Code: DS00-00004-1Ea

### **■ HANDLING PRECAUTIONS**

Any semiconductor devices have inherently a certain rate of failure. The possibility of failure is greatly affected by the conditions in which they are used (circuit conditions, environmental conditions, etc.). This page describes precautions that must be observed to minimize the chance of failure and to obtain higher reliability from your FUJITSU SEMICONDUCTOR semiconductor devices.

### 1. Precautions for Product Design

This section describes precautions when designing electronic equipment using semiconductor devices.

### Absolute Maximum Ratings

Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of certain established limits, called absolute maximum ratings. Do not exceed these ratings.

### Recommended Operating Conditions

Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their sales representative beforehand.

### Processing and Protection of Pins

These precautions must be followed when handling the pins which connect semiconductor devices to power supply and input/output functions.

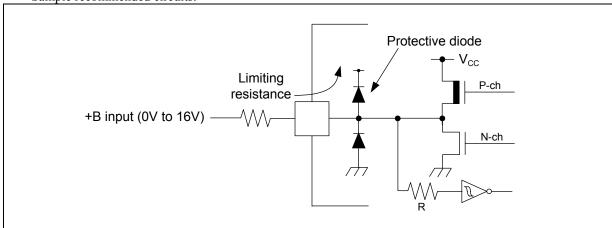

### (1) Preventing Over-Voltage and Over-Current Conditions

Exposure to voltage or current levels in excess of maximum ratings at any pin is likely to cause deterioration within the device, and in extreme cases leads to permanent damage of the device. Try to prevent such overvoltage or over-current conditions at the design stage.

### (2) Protection of Output Pins

Shorting of output pins to supply pins or other output pins, or connection to large capacitance can cause large current flows. Such conditions if present for extended periods of time can damage the device.

Therefore, avoid this type of connection.

### (3) Handling of Unused Input Pins

Unconnected input pins with very high impedance levels can adversely affect stability of operation. Such pins should be connected through an appropriate resistance to a power supply pin or ground pin.

#### · Latch-up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

- (1) Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

- (2) Be sure that abnormal current flows do not occur during the power-on sequence.

### · Observance of Safety Regulations and Standards

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### · Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

### Precautions Related to Usage of Devices

FUJITSU SEMICONDUCTOR semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

### 2. Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mount type. In either case, for heat resistance during soldering, you should only mount under FUJITSU SEMICONDUCTOR's recommended conditions. For detailed information about mount conditions, contact your sales representative.

### · Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder. In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to FUJITSU SEMICONDUCTOR recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

### Surface Mount Type

Surface mount packaging has longer and thinner leads than lead-insertion packaging, and therefore leads are more easily deformed or bent. The use of packages with higher pin counts and narrower pin pitch results in increased susceptibility to open connections caused by deformed pins, or shorting due to solder bridges.

You must use appropriate mounting techniques. FUJITSU SEMICONDUCTOR recommends the solder reflow method, and has established a ranking of mounting conditions for each product. Users are advised to mount packages in accordance with FUJITSU SEMICONDUCTOR ranking of recommended conditions.

### Lead-Free Packaging

CAUTION: When ball grid array (BGA) packages with Sn-Ag-Cu balls are mounted using Sn-Pb eutectic soldering, junction strength may be reduced under some conditions of use.

### · Storage of Semiconductor Devices

Because plastic chip packages are formed from plastic resins, exposure to natural environmental conditions will cause absorption of moisture. During mounting, the application of heat to a package that has absorbed moisture can cause surfaces to peel, reducing moisture resistance and causing packages to crack. To prevent, do the following:

- (1) Avoid exposure to rapid temperature changes, which cause moisture to condense inside the product. Store products in locations where temperature changes are slight.