#### **1 FEATURES**

- rfi elimination triac drive circuit

- Low external component count

- Low supply current required

- Variable ON and OFF cycle times

- External ON/OFF triac control available

- No DC component in the AC mains supply

- The ON period always has an odd number of half cycles, and the OFF period an even number

- · Gate pulse width may be externally set

- Negative triac gate drive (avoids insensitive quadrant operation)

- Versions available with slower cycle times to meet EMC flicker regulations

#### 2 GENERAL DESCRIPTION

The OM1895 is a precision low power simmerstat control IC for triggering a triac in applications where variable ON and OFF cycle time is required. It is suitable for a broad

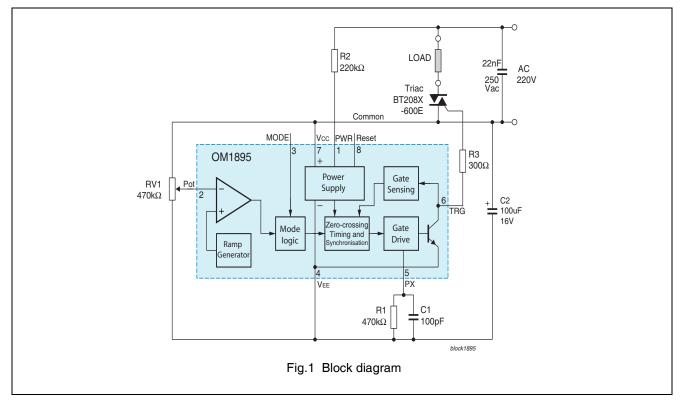

#### **3 BLOCK DIAGRAM**

range of applications, extending from the zero-crossing control of a heating element, a fan motor and other complex loads.

Because the operation of the OM1895 uses characteristics of triacs which are common to typical triacs, but may show some variation in triacs designed to emphasise specific uncommon features, it is preferable to use triacs which have been characterized and specified as suitable for use in this application.

The triac firing circuit uses a unique circuit arrangement by which load current zero crossing is detected, and a widened gate pulse applied during the critical current zero crossing period. Triac conduction is therefore maintained throughout the zero crossing time, ensuring that rfi transients are not generated during this time. With inductive loads only the final half cycle that ends an ON period (made up of an odd number of mains half cycles), will finish with a voltage transient. This may still need a snubber network to limit dv/dt, although it will not be required for the consecutive conducting half cycles during the ON time.

Contents are subject to the Disclaimer

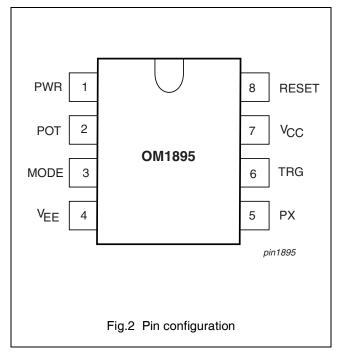

#### 4 PINNING INFORMATION

#### 4.1 Pinning layout

#### 4.2 Pin description

| SYMBOL | PIN | DESCRIPTION                   |  |

|--------|-----|-------------------------------|--|

| PWR    | 1   | AC line sense and power input |  |

| POT    | 2   | Control input, triac ON/OFF   |  |

| MODE   | 3   | Triac ON/OFF & function       |  |

| VEE    | 4   | Negative supply               |  |

| PX     | 5   | Gate pulse extender           |  |

| TRG    | 6   | Triac gate drive              |  |

| VCC    | 7   | Positive Common               |  |

| RESET  | 8   | Reset input/output            |  |

#### **5 FUNCTIONAL DESCRIPTION**

## 5.1 V<sub>CC</sub> – Common, positive DC supply

The positive DC supply rail for the control IC type OM1895 is used as the common reference. This is always connected to the T1 terminal of the triac, and being the positive supply rail allows negative gate drive to the triac in both positive and negative supply half cycles on T2. By driving the triac in this way the insensitive quadrant (negative T2 voltage, and positive gate triggering signal) of triacs is avoided.

### 5.2 V<sub>EE</sub> – Negative DC supply, substrate

This pin connects to the substrate and the internally generated and regulated negative DC supply, and should be bypassed to  $V_{CC}$  (common) by a capacitor of typically 100  $\mu$ F. The

capacitor needs to be sufficiently large to maintain the operating voltage during the half cycle when it is not being charged, as well as to provide the energy to drive the triac gate during the gate pulse.

Internal supply sensing prevents the commencement of an ON cycle while the voltage is too low for reliable circuit operation. If during an ON cycle the supply voltage falls below this level the ON cycle will terminate at the first opportunity consistent with the logic cycle algorithm.

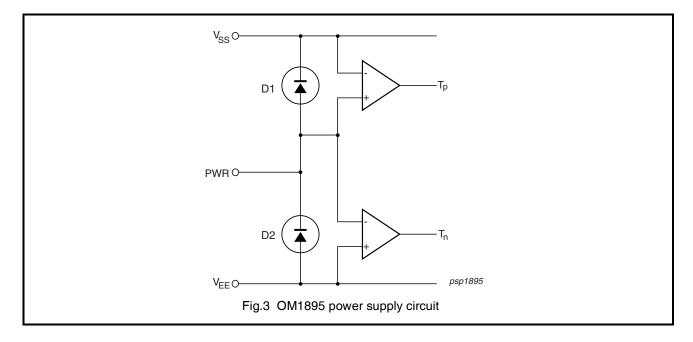

#### 5.3 PWR – Power supply and synchronisation from the mains supply line

The PWR input provides both a synchronisation signal for the logic functions of the OM1895, as well as the DC current used to provide the power supply from which the OM1895 is powered. Signals are derived which

indicate the phase and magnitude of the signal on the AC supply. Three states, positive, zero and negative, of this signal is recognised for synchronisation of the triggering times to the mains.

See Figure 3, OM1895 Power Supply Circuit.

The PWR pin is driven by a current limiting resistor from the mains supply. During the positive half cycle current flows through the upper diode D1 to the positive common rail, while on a negative half cycle the current flows through the lower diode D2, and charges the  $V_{EE}$  power supply capacitor.

The zero crossing is signalled by the two comparators, the output signals of which indicate whether the mains voltage is above the common rail voltage, or below the negative  $V_{EE}$ . There may be additional resistors in a simple network from the AC supply and  $V_{EE}$  to adjust these zero-crossing signals to provide a symmetrical response in the positive as well as the negative going direction.

As the AC signal passes through zero, comparators provide control signals Tp (when  $V_{PWR} > V_{CC}$ ) and Tn (when  $V_{PWR} < V_{EE}$ ) indicating whether the voltage on PWR pin is greater or less than  $V_{CC}$  or  $V_{EE}$ respectively. A resistor network ensures that these switching points correspond to equal positive or negative thresholds about the AC zero thus giving symmetrical zero-crossing information to the synchronisation and logic circuit.

Synchronisation is obtained from the threshold comparators at the levels of  $V_{CC}$  and  $V_{EE}$  on the chip.

Adjustment of the initial switching point, and hence the time of initiation of the first firing pulse, and its symmetry about the zero crossing point, is possible by varying the values of the resistors connected between PWR and the active supply, a resistor to  $V_{EE}$ , and a resistor to  $V_{CC}$ .

When the triac has switched on, the zero-crossing synchronisation information is derived from the voltage on the triac gate while it is conducting, although the polarity information provided by the PWR input signal continues to provide phase information to enable the ON and OFF transitions at the start and finish of an ON burst of conducting half cycles, to be synchronised to prevent repeated firing in the same polarity half cycle, and a resultant net DC load current.

#### 5.4 RESET /Ext\_Reset status and control

As the power supply rises towards its operating voltage, a reset signal is generated which holds the logic in an initial state until the voltage has risen to a sufficient value to sustain full operation.

The reset signal is active high to preserve a predictable voltage relationship with the Common supply rail (V<sub>CC</sub>) rather than V<sub>EE</sub>. The RESET pin is pulled high by  $50\mu$ A when the internal reset signal is active. When the power supply voltage reaches its normal regulated level, the RESET pin is pulled low ( $6\mu$ A), and the controller then begins normal operation.

This reset signal can be used to reset counters and other electronic logic circuits which need to begin operation in a known state.

Furthermore, when OM1895s are used in parallel, or with other control circuits, an external reset signal can be applied which will override these internally generated signals.

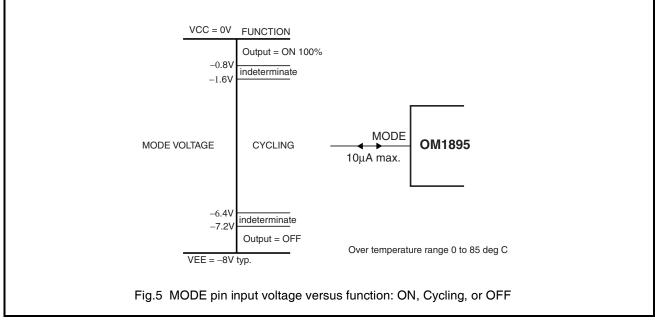

#### 5.5 MODE – external triac ON/OFF, or function

The mode pin is an external triac ON/OFF control input, and has three active states.

When MODE pin is connected to either  $V_{CC}$  (held high) or  $V_{EE}$  (held low), then the triac is turned ON and OFF respectively. Irrespective of the control input on POT pin. Figure 5 shows the MODE functions against voltage graphically.

When MODE pin is not connected, the OM1895 uses the control input (POT) to turn the triac ON/OFF.

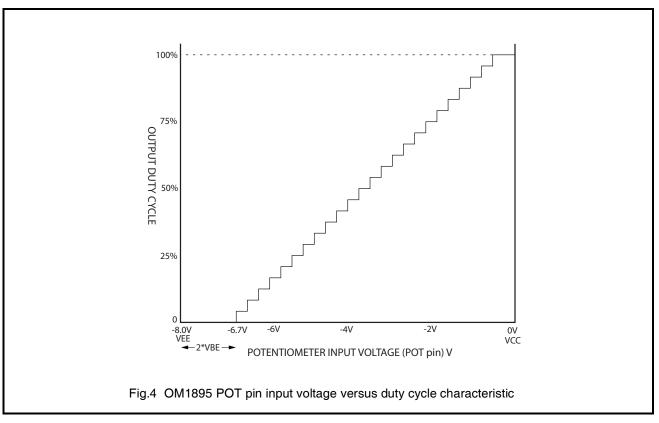

#### 5.6 POT – Triac drive control input

When POT pin is connected to  $V_{CC}$ , then the triac is turned ON 100%. When POT pin is left unconnected or is connected to 1.2V with respect to  $V_{EE}$ , then the triac is fully OFF. Figure 4 shows the characteristic of duty cycle against POT voltage.

The OM1895 generates an internal reference voltage signal which consists of 32 voltage levels, ranging from typically 7.79V down to 1.3V (2Vbe) with respect to  $V_{EE}$ . The OM1895 compares the generated reference voltage signal with the voltage signal set on the POT pin, which turns the triac ON when the voltage set on POT pin is greater than the reference voltage, and OFF when the voltage set on POT pin is less

than or is equal to the reference voltage.

Additional cycling period can be achieved to extend the triac ON/OFF period by grounding the appropriate ZAP1 and ZAP2 internal pins to V<sub>FF</sub>. ZAP1 and ZAP2 internal pins are permanently wired during pretest. When ZAP1, ZAP2 pins are not connected, cycling time is 0.64 seconds. If ZAP1 pin not connected and ZAP2 pin is connected to V<sub>FF</sub>, cycling time is 5.12 seconds. While if ZAP1 pin is connected to V<sub>FF</sub> and ZAP2 pin not connected, cycling time is 40.96 seconds. Finally, if ZAP1 and ZAP2 pins are both connected to V<sub>FF</sub> cycling time is 327.68 seconds or 5.46 minutes.

The voltage signals on POT and MODE pins will switch the triac ON or OFF in a manner which is synchronised to the mains zero crossings. These signals may change at any time, but the triac will only be switched ON or permitted to turn OFF, at a time that is consistent with controlling it at the first available opportunity consistent with the cycling algorithm which triggers the triac for an odd number cycles in each ON period, and lets it remain OFF for and even number of half cycles. In this way there is no DC current present in the mains supply when it is averaged over a large number of ON cycles and at the same time for inductive loads, a new ON period begins on a half wave of the opposite polarity to the start and finish half wave of the previous run cycle.

#### 5.7 TRG – Triac gate drive

The triac gate output drives the gate through an external current setting resistor. It has in-built protection to withstand transient voltage signals which may be induced on the gate of the triac by mains transients during firing. The gate drive current should be set to a value suited to the gate sensitivity of the triac used. The firing pulse width will need to be of such a width that the specified latching current of the triac when used with the design load has been reached before the gate pulse ends.

In the OM1895 the gate drive is first applied at the start of an ON period at the zero crossing of the mains supply. The leading edge of this obtained from the signal derived from the PWR resistor network before the falling mains voltage reaches zero.

On this first half cycle current is flowing in the triac, and subsequent zero crossings of the triac can be determined in another way. While a resistive load may have the zero crossing determined from the mains supply, this is not possible when the load is inductive (for example, when it is a motor). The current is no longer in phase with the supply voltage, and can reach zero at a time significantly lagging the supply voltage phase.

In the OM1895, the voltage of the triac gate has been found to provide an indicator of imminent zero crossing, and with an appropriate threshold circuit, the gate drive can be re-applied before the triac turns fully off. Again the gate pulse is determined by the length of the internal delay circuit, plus any additional delay from the application of external resistor and capacitors applied in parallel from the pin PX to  $V_{EE}$

#### 5.8 PX – triac gate pulse width external setting

The gate pulse must be wide enough to be applied from the time the triac is about to turn off until the increasing current in the triac in the opposite direction has reached the latching current of the triac being used.

While there is a time delay circuit within the OM1895 to provide a minimum gate pulse width of typically  $100\mu$ s, for lower powered loads, where it takes longer for the load current to reach the triac latching current, then it may be necessary to extend the gate pulse.

A parallel resistor and capacitor are connected from pin PX (pulse extender) to  $V_{EE}$  giving a pulse extension time of:

$t_{pw} \approx 1.4 \cdot R \cdot C$  (s)

The gate pulse is applied for a time determined by either the internal delay time of typically 100µs or the

### OM1895 Simmerstat control IC

extended time, set by the RC network on the PX pin, whichever is greater.

#### 6 IMPORTANT: ELECTRICAL SAFETY WARNING

OM1895 circuits are connected to the mains electrical supply and operate at voltages which need to be protected by proper enclosure and protective covering. Application circuits for OM1895 should be designed to conform to relevant standards (such as IEC-60335 {Safety} and IEC-61000 {EMC compatibility}, or equivalent). The OM1895 should only be used in a manner that ensures the appliance in which it is used complies with all relevant national safety and other Standards.

It is recommended that a printed circuit board using this integrated circuit be mounted with non-conductive clips, and positioned such that the minimum creepage distances from the assembly to accessible metal parts, and between high voltage points cannot be transgressed. It should be noted that as there are Mains Voltages on the circuit board adequate labelling should be attached to warn service personnel, and others, that this danger exists.

A control board assembly should be mounted, preferably vertically, with sufficient free air flow across its surface to prevent the heat dissipated in various components from causing an unacceptable rise in the ambient temperature. The triac also needs to have an adequate heatsink, as exceeding its rated maximum junction temperature can result in loss of control, unpredictable behaviour, and possible dangerous conditions.

The board should be mounted in a place that is clean and dry at all times, not subject to condensation or the accumulation of dust and other contaminants.

#### 7 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 134). All voltage measured with respect to  $V_{CC},\,Common.$

| SYMBOL                                                   | PARAMETER                          | CONDITIONS                  | MIN.                | MAX. | UNIT |

|----------------------------------------------------------|------------------------------------|-----------------------------|---------------------|------|------|

| I                                                        | DC current (any pin except 4 & 6)  |                             | -                   | 20   | mA   |

| Ι                                                        | DC current (pins 4 & 6)            |                             | -                   | 70   | mA   |

| V <sub>TRG</sub>                                         | Voltage range TRG, pin6, transient | V <sub>6-7</sub>            | V <sub>4</sub> -30  | +50  | V    |

| V <sub>PWR</sub>                                         | Voltage range PWR                  | V <sub>1-7</sub>            | V <sub>4</sub> -0.8 | +0.8 | V    |

| V <sub>MODE</sub> , V <sub>PX</sub> , V <sub>RESET</sub> | Voltage range MODE, PX, RESET      | $V_{3-7}, V_{5-7}, V_{8-7}$ | V <sub>4</sub> -0.8 | +0.8 | V    |

| P <sub>tot</sub>                                         | total power dissipation            |                             | -                   | 300  | mW   |

| T <sub>stg</sub>                                         | storage temperature                |                             | -40                 | +150 | °C   |

| T <sub>amb</sub>                                         | operating ambient temperature      |                             | 0                   | +85  | °C   |

#### 8 CHARACTERISTICS

At  $T_{amb} = 25^{\circ}C$ ; Voltages are specified with respect to V<sub>CC</sub>.

| SYMBOL             | PARAMETER                            | CONDITIONS                                                   | MIN  | ТҮР                  | MAX        | UNIT |

|--------------------|--------------------------------------|--------------------------------------------------------------|------|----------------------|------------|------|

| Power supp         | ly                                   |                                                              | •    | 1                    |            |      |

| -VEE               | supply voltage (operating)           | I <sub>CC</sub> = 1 mA                                       | 7.4  | 8.0                  | 8.6        | V    |

| –IEE               | quiescent current                    | TRG pin open circuit                                         | _    | 300                  | 350        | μA   |

| Power and s        | ensing input, pin PWR                |                                                              |      |                      |            |      |

| V <sub>ut</sub>    | upper threshold                      |                                                              | -    | 0                    | _          | V    |

| V <sub>lt</sub>    | lower threshold                      |                                                              | _    | V <sub>EE</sub>      | _          | V    |

| Reset outpu        | t/input, pin RESET                   |                                                              |      |                      |            |      |

| V <sub>reset</sub> | internally generated reset signal    | active until power up                                        | -    | 0                    | _          | V    |

| I <sub>high</sub>  | reset active pull-up current         | V <sub>reset</sub> = -0.5 V                                  | _    | 50                   | _          | μA   |

| Ilow               | reset off pull-down current          | V <sub>reset</sub> = V <sub>EE</sub>                         | _    | 6                    | -          | μA   |

| V <sub>reset</sub> | external reset threshold             |                                                              | -    | -2                   | -          | V    |

| Gate drive, p      | bin TRG                              | •                                                            | -    |                      | - <u>-</u> |      |

| l <sub>G</sub>     | gate current (triac T1 to $V_{CC}$ ) | set by R <sub>G</sub> connected from TRG to gate             | _    | -                    | 50         | mA   |

| V <sub>G</sub> th- | gate sensing thresholds (triac G     | gate voltage sensing of                                      | -120 | -150                 | -180       | mV   |

| V <sub>G</sub> th+ | to $V_{CC}$ , positive and negative) | current zero crossing                                        | +120 | +150                 | +180       | mV   |

| Pulse stretc       | hing, pin PX                         | I                                                            | I    |                      |            |      |

| t <sub>pulse</sub> | gate pulse width                     | 390K $\Omega$ from PX to V <sub>EE</sub>                     | _    | 100                  | _          | μs   |

| t <sub>pulse</sub> | stretched gate pulse width           | 390K $\Omega$ & 220pF in parallel from PX to V <sub>EE</sub> | -    | 120                  | -          | μs   |

| Triac drive n      | node, pin MODE                       |                                                              |      | 1                    | •          | 1    |

| V <sub>ut</sub>    | upper mode threshold                 | hold ON threshold                                            | _    | -1.2                 | _          | V    |

| V <sub>lt</sub>    | lower mode threshold                 | hold OFF threshold                                           | -    | V <sub>EE</sub> +1.2 | _          | V    |

| l <sub>in</sub>    | mode control input current           | $V_{mode} = V_{CC} \text{ or } V_{EE}$                       | _    | -                    | 10         | μA   |

| Triac drive n      | node, pin POT                        |                                                              |      |                      |            | •    |

| V <sub>ut</sub>    | upper pot threshold                  | Output ON 100%                                               | -    | 0                    | -          | V    |

| V <sub>lt</sub>    | lower pot threshold                  | Output OFF                                                   | -    | V <sub>EE</sub> +1.2 | _          | V    |

|                    | POT pin open circuit                 | Output OFF                                                   | -    | -                    | -          | -    |

| l <sub>in</sub>    | pot control input current            | $V_{pot} = V_{CC} \text{ or } V_{EE}$                        | -    | -                    | 1          | μA   |

| Cycle timing       |                                      |                                                              | •    | - •                  | •          | •    |

| t <sub>P(A)</sub>  | Cycle period (mains divided)         | OM1895A - 50Hz supply                                        | _    | 0.64                 | _          | S    |

| · /                |                                      | OM1895A - 60Hz supply                                        | -    | 0.53                 |            | s    |

# OM1895

### Simmerstat control IC

| SYMBOL            | PARAMETER                    | CONDITIONS                                     | MIN    | ТҮР          | МАХ | UNIT   |

|-------------------|------------------------------|------------------------------------------------|--------|--------------|-----|--------|

| t <sub>P(B)</sub> | Cycle period (mains divided) | OM1895B - 50Hz supply<br>OM1895B - 60Hz supply | _<br>_ | 5.1<br>4.3   | -   | s<br>s |

| t <sub>P(C)</sub> | Cycle period (mains divided) | OM1895C - 50Hz supply<br>OM1895C - 60Hz supply | -<br>- | 41.0<br>34.1 | -   | s<br>s |

| t <sub>P(D)</sub> | Cycle period (mains divided) | OM1895D - 50Hz supply<br>OM1895D - 60Hz supply | _<br>_ | 328<br>273   | -   | s<br>s |

#### 9 APPLICATION INFORMATION

#### 9.1 Design considerations

Resistors connected directly to the AC supply rail should be specified to withstand the voltage. It is recommended that (Philips BC Components) VR37 (or VR25) high-ohmic / high-voltage resistors be used. These resistors meet the safety requirements of a number of international standards on high voltage applications.

#### 9.2 MODE function

Figure 5 shows graphically the functions obtained by applying a voltage to the mode pin. Open circuit the MODE pin floats in the Cycling part of its characteristic, but a current of less than  $10\mu$ A flows into or out of

MODE when it is held HIGH or LOW to override the cycling function.

The thresholds are set to be 2 x VBE away form the VCC and VEE supply rails, and therefore these are temperature sensitive (-4 mV/deg C). Therefore to guarantee functionality over the temperature range an indeterminate region is shown where the actual observed function will be temperature dependent.

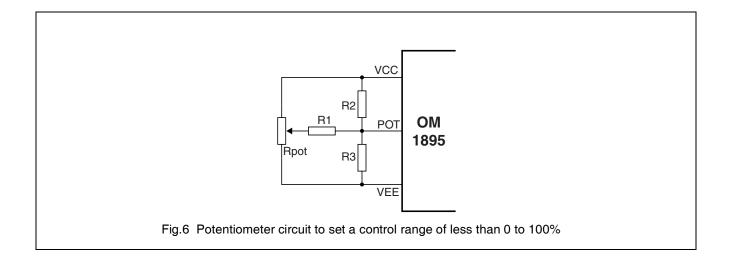

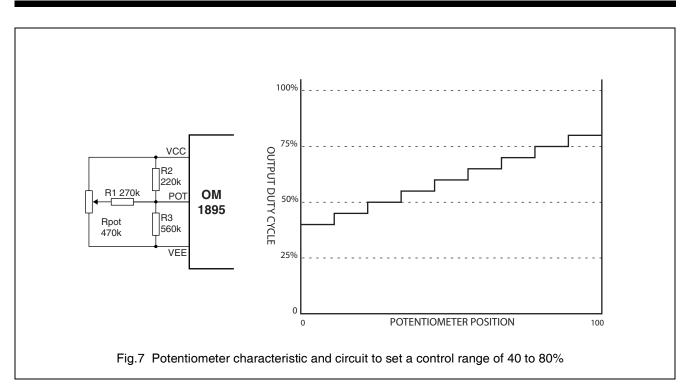

#### 9.3 Potentiometer circuits for limiting the power range

In figure 6 a circuit is shown in which resistors can be added to the simple voltage divider between VCC and VEE to limit the range of the input voltage to the POT pin), and in this way limit the control range covered by the potentiometer to a range that does not cover the full zero to 100% range capability of the OM1895.

If there is no significant impedance, or current input loading on the wiper tap on the potentiometer, then by using the potentiometer as a voltage divider between VCC and VEE the resistance tolerance of the

potentiometer does not influence the divided voltage. For the OM1895 the POT pin presents very little loading to the potentiometer divider. But even if they did present a load impedance at the IC input pin, it would not effect the duty cycle at each end of the

potentiometer travel. Such a load impedance would result in curvature of the potentiometer control characteristic, and any spread from the tolerance of the potentiometer resistance would apply only to the curvature the IC loading presented. Adding the extra resistors R1, R2 and/or R3 adapts the range covered by the voltage applied to POT to a range that corresponds to the required reduced duty cycle span.

From the graph in figure 7 the required upper and lower (minimum and maximum) duty cycle readings can be read off the horizontal scale in terms of voltage. The input resistor network can then be analysed to find resistor values which provide these voltages when the potentiometer is at the extremes of its range.

The choice of potentiometer resistance is limited by the loading which can be applied to the -VEE power supply. Choice of 470k will load the 8 V power supply with a current of 17  $\mu$ A. The current in the resistor network loads the wiper tap on the potentiometer, the current flowing in R1 needing to be small compared to the current in the potentiometer.

As an example, a circuits is shown in figure 12 using a 470k potentiometer, and values of resistors R1, R2 and R3 chosen to give control over the range of 40% to 80%.

This has been calculated on a spreadsheet, which also calculates the error in the linearity caused by the resistor loading on the potentiometer. (Note that the maximum error may be near the mid point on the potentiometer if only R2 or R3 are used alone, while if both R2 and R3 are used the error curve is S shaped with an accurate point around the mid-range of the pot. The equivalent circuit load of the potentiometer at its mid point is one quarter of the total resistance Rpot, or 117.5 k $\Omega$ . At each end of its travel the potentiometer impedance is zero ohms.

Because the accuracy of the voltage on Vpot depends on the divided voltage on the potentiometer wiper, and accurate resistors chosen to set the required range, then potentiometer and resistor tolerances and spreads will have negligible effect on the actual duty cycles achieved.

The Excel spreadsheet potcalc.xls automatically calculates the control range for different resistor values in the input network. It shows graphically the duty cycle stepped characteristic that will be provided by the OM1895 controller.

In addition another graph in the spreadsheet shows the ideal characteristic (by ignoring the resistance of the potentiometer and giving a straight line) and the real curve which deviates from the straight line depending on the loading offered by the resistor network R1 to R3. This error may be curved above or below the ideal line or S shaped, depending on whether the R2 or R3 resistors are used, or both.

The final spreadsheet graph shows the error as a deviation from the ideal curve in percentage terms, ignoring the stepped characteristic of the input circuit of the OM1895. It needs to be recognised that one step is about 4%, and that an error of less than 4% can be ignored, especially considering that it is accurate anyway when the pot is fully clockwise or anti-clockwise. As can be shown in the calculated spreadsheet values, changing the pot resistance only changes the error, the end points are not dependent on pot tolerance.

#### 9.4 Gate drive

The  $300\Omega$  gate resistor shown in the application circuits gives a little over 10 mA gate drive. Thus for the circuit shown a triac would need to be specified that is suitable for 10 mA triggering with negative triggering signal for both positive and negative voltage on T2. From the threshold levels determined from the resistive

network on PWR, and the AC supply, the timing of the first gate pulse in a conduction cycle can be calculated (assuming a sine wave supply). The specification of the triac will indicate the latching current for switch-on, and knowing the minimum load with which the circuit is to operate, then proper design will ensure that the gate pulse will be long enough, and will not be removed before the triac current reaches this figure.

In addition to the triac gate current, the circuit also uses about 3mA to operate the output gate drive circuit when a triac gate pulse is required.

#### 9.5 Pulse width extension

When the gate pulse is extended by adding a parallel resistor and capacitor from the pulse width extension pin PX to  $V_{EE}$ , the power supply current used in driving the gate is a major portion of the available DC power supply needed

in the circuit. This has therefore to be included in the calculation of the total power supply requirements.

In particular allowance must be made for the changes in triac characteristics below normal room temperature.

### 9.6 Power supply requirements

The DC power supply current available for the operation of the circuit is derived from the resistor connected to the PWR pin. On the negative half cycle of the AC signal applied to this resistor, the current into the OM1895 charges the power supply capacitor (typically  $100 \ \mu F$ ) connected between V<sub>CC</sub> and V<sub>EE</sub>.

Apart from the current required by the chip, the triac gate drive presents the major DC current requirement of the circuit. As the gate pulse must be wide enough for the load current to reach the triac's specified holding current, this may be a significant

load on the DC supply (especially with small resistive & inductive triac loads)

#### 9.7 Startup reset

While the reset pin provides an output of the reset condition within the OM1895, and provides a suitable reset signal to reset timers, and external logic circuits which might be used it can also be driven from an external reset source, or connected to another OM1895 reset pin.

It is active HIGH with 50  $\mu$ A pull up current, and once the power supply reaches its regulated voltage level, falls to a 6  $\mu$ A pull down condition.

An externally applied reset signal will override these currents, and reset the internal circuitry of the OM1895 in accordance with the state of the externally applied signal.

When two or more OM1895 have reset interconnected, the reset will only be freed when the first of the OM1895 device reaches the shunt operating level. This hysteresis feature on reset pin is to ensure that full operating voltage is reached before reset to internal logic is release during start up.

#### 9.8 Zero-crossing detection

The two thresholds at which the zero-crossing of the input voltage on PWR is sensed are the two supply

rails,  $V_{CC}$  and  $V_{EE}$ . This is set by the resistor from the mains active to PWR and an equal resistor connected between PWR and  $V_{EE}$ . The positive threshold will therefore be an equal voltage above  $V_{CC}$  due to the divider action of the resistors, while the negative threshold is still equal to  $V_{EE}$ , at which point no current is flowing in the second resistor. If a third resistor with suitable values is added from PWR to  $V_{CC}$ , then the positive and negative threshold can be made larger than the DC supply voltage of  $V_{CC} - V_{EE}$ .

The symmetry about the zero crossing set by the external resistor network described above only applies to the initial switching point of the first firing pulse. Once the triac has switched on, zero-crossing is derived from the voltage on the triac gate while it is conducting. It is thought that no great benefit is gained from the information provided by the external resistor network. Therefore the resistors connected from PWR to  $V_{EE}$  and from PWR to  $V_{CC}$  are not included in the application circuit.

#### 9.9 Inductive loads

Because of the triac control method used in the OM1895, both resistive and inductive loads can be controlled without changing the controller circuit.

### OM1895 Simmerstat control IC

In the application circuits shown in this data sheet, snubber networks are not shown connected across the triac, nor is an rfi filtering capacitor shown between active and neutral.

The OM1895 provides zero crossing firing of both inductive and resistive loads, and rfi suppression may only be needed to filter residual transient behaviour of the triac which would be present even if the gate was DC fired. For example with high current resistive loads.

However with inductive loads, while the OM1895 provides zero crossing firing during the run cycle at every current zero crossing through this period, when the last half cycle finishes at zero current (not in phase with the mains voltage supply) a single voltage transient will occur which may exceed the dv/dt rating of the triac, and need a snubbing circuit to bring it within the triac ratings. Also that last transient may generate rfi which exceeds the limits published in the standards. However it will no longer be at 100Hz and higher harmonics, as is the case with interference generated in phase with the supply frequency; it will only be a single transient coming at the end of the ON cycle, and therefore occurring a lot less frequently, and falling under other clauses of the standard.

#### **10 APPLICATION CIRCUITS**

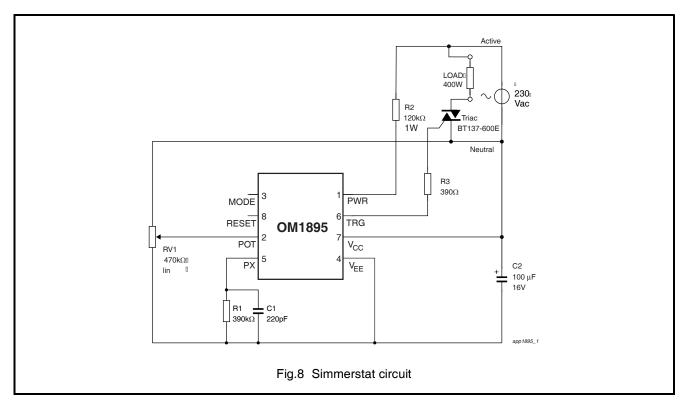

Two application circuits are included in this data sheet. The first shown in Figure 8 is the basic simmerstat circuit, with potentiometer control of the duty cycle from OFF (zero duty cycle) to fully ON (a duty cycle of 100% ON).

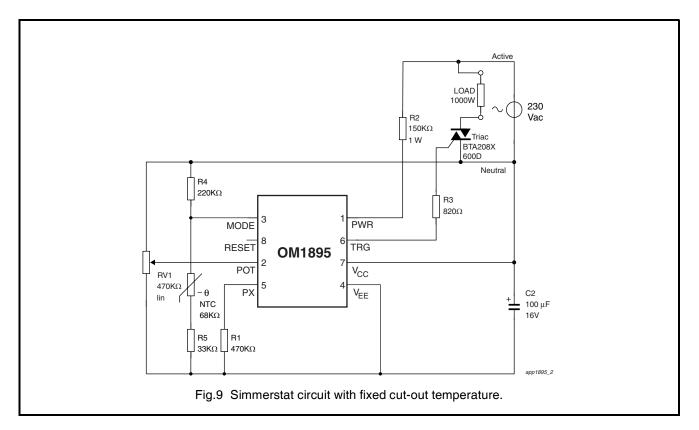

The second circuit in Figure 9 uses the MODE input to give over-riding control of the operation to a thermistor divider, so that if the thermistor detects over-temperature the OM1895 is switched OFF.

To assist in carrying out circuit designs using the OM1895 design spread sheets are available. For figure 8 the file "OM1895 fig 8 app cct.xls" is provided, and for figure 9 the file name is "OM1895 fig 9app cct.xls". These can greatly assist in selecting appropriate values for the external components around the OM1895. The design process involved in applications using the spreadsheet is as follows:

Enter the nominal, maximum and minimum mains supply voltages and the frequency. (The numbers in BLUE are for the designer to enter). The design needs to ensure that sufficient power supply current is available to maintain operation at the minimum voltage, and yet not dissipate excessive power in the power supply resistor (R2) when the supply voltage is at its maximum.

Next provide the intended load figures (in Watts). Usually the load is fixed (for the example in Figure 9, 1000W), but a circuit may be intended to cover a range of possible loads. The gate pulse needs to be sufficiently wide to cover the zero crossing behaviour of the triac used on minimum load, and at the same time have a sufficient current rating to carry the load current. Choose a suitable triac. Current rating, gate sensitivity, latching and holding current figures need to be inserted into the table.

It is then necessary to enter the various component values into the spreadsheet, and to check that the results of the calculations give figures that indicate proper operation of the circuit.

The following are the important points, with key results from the calculations shown on the spreadsheet in RED alongside the component values being used:

The heat dissipation in R2, the power supply resistor is important. The resistor must be chosen such that it can handle the mains voltage applied across it (including good transient handling capability), as well as being able to dissipate the power.

R4 sets the gate current. The gate current sensitivity in the data sheet is given for a triac at 25 deg. A margin is desirable for initial operation below 25 deg, and the temperature sensitivity figures are found in the data sheet.

The next important figure is the required gate pulse width. That is the minimum pulse width to be applied to the gate so that the gate drive begins as the triac load current falls below the triac holding current (and the triac turns OFF, and continues until the increasing load current in the other polarity has reached the holding current.

The resistor R1 and capacitor C1 are then chosen to give a gate pulse that is at least a wide as the calculated required pulse width (allowing a margin for component tolerances). If the required pulse width is less than  $100\mu$ s, then the minimum pulse width of  $100\mu$ s is used and only the resistor is needed from pin PX to VEE (This is the case in the circuit of figure 9 where the higher power load does not need wide gate pulse).

Finally it is necessary to ensure that there is sufficient power supply available. All of the loads presented to the VEE-VCC DC supply are added up to give a figure indicating the total power supply needed, and this figure is compared to the calculated DC current available through the power supply resistor R2. The available current should exceed that needed by a margin to allow for tolerances, and errors.

The power supply load if first of all the current needed by the OM1895, followed by the average gate current consumed while the gate is driving the triac. Finally any other circuit connected between VEE and VCC requires an estimate of its current load to be included in the spreadsheet.

In these example spread sheets it should be evident how in Figure 9 the extra load presented by the NTC divider has been covered by an addition line in the spreadsheet (cells B83 & B84).

These spread sheets are presented as an aid to support the circuit design, and as other circuit ideas are suggested they are intended to be freely modified by the designer to cover a customer's specific application. Some of the mathematical concepts used are discussed in Application Notes AN001, and AN002. Although these Application Notes were written for other control ICs the discussion of the mathematical concepts used apply equally well to the OM1895.

#### **11 ORDERING INFORMATION**

| ТҮРЕ     |                  | PACKAGE                                                   |                     |

|----------|------------------|-----------------------------------------------------------|---------------------|

| NUMBER   | NAME DESCRIPTION |                                                           | VERSION             |

| OM1895P  | DIP8             | plastic dual in-line package; 8 leads (300 mil)           | SOT97-1             |

| OM1895T  | SO8              | plastic small outline package; 8 leads; body width 3.9 mm | SOT96-1             |

| OM1895 A |                  | ZAP1 & ZAP2 open circuit                                  | cycling time 0.64s  |

| OM1895 B |                  | ZAP1 open circuit & ZAP2 connected to V <sub>EE</sub>     | cycling time 5.12s  |

| OM1895 C |                  | ZAP1 connected to V <sub>EE</sub> & ZAP2 open circuit     | cycling time 40.96s |

| OM1895 D |                  | ZAP1 & ZAP2 connected to V <sub>EE</sub>                  | cycling time 327.6s |

Other package options are available - contact Hendon Semiconductors for details. For more information on packages, please refer to the document "Integrated Circuit Packaging and Soldering Information" on the Hendon Semiconductors web site.

#### **12 ESD CAUTION**

Electrostatic Discharge (ESD) sensitive device. ESD can cause permanent damage or degradation in the performance of this device. This device contains ESD protection structures aimed at minimising the impact of ESD. However, it is the users responsibility to ensure that proper ESD precautions are observed during the handling, placement and operation of this device.

#### **13 DOCUMENT HISTORY**

| REVISION | DATE     | DESCRIPTION                         |  |

|----------|----------|-------------------------------------|--|

| 1.0      | 20030509 | Released version                    |  |

| 2.0      | 20070116 | HS formatting, standard ESD caution |  |

|          |          |                                     |  |

|          |          |                                     |  |

#### 14 DEFINITIONS

| Data sheet status                                        |                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Engineering sample information                           | This contains draft information describing an engineering sample provided to demonstrate possible function and feasibility. Engineering samples have no guarantee that they will perform as described in all details.                                                                                                                            |

| Objective specification                                  | This data sheet contains target or goal specifications for product development.<br>Engineering samples have no guarantee that they will function as described in all details.                                                                                                                                                                    |

| Preliminary specification                                | This data sheet contains preliminary data; supplementary data may be published later.<br>Products to this data may not yet have been fully tested, and their performance fully documented.                                                                                                                                                       |

| Product specification                                    | This data sheet contains final product specifications.                                                                                                                                                                                                                                                                                           |

| Limiting values                                          |                                                                                                                                                                                                                                                                                                                                                  |

| more of the limiting values of the device at these or at | accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or<br>may cause permanent damage to the device. These are stress ratings only and operation<br>any other conditions above those given in the Characteristics sections of the specification<br>limiting values for extended periods may affect device reliability. |

#### **Application information**

Where application information is given, it is advisory and does not form part of the specification.

#### **15 COMPANY INFORMATION**

HENDON SEMICONDUCTORS a trading name of INTEGRATED ELECTRONIC SOLUTIONS PTY. LTD. ABN 17 080 879 616

Postal address:

Hendon Semiconductors PO Box 2226 Port Adelaide SA 5015 AUSTRALIA Street Address:

Hendon Semiconductors 1 Butler Drive Hendon SA 5014 AUSTRALIA

Telephone:+61 8 8348 5200Facsimile:+61 8 8243 1048World Wide Web:www.hendonsemiconductors.com

www.bus-buffer.com Email: ies@ies-sa.com.au

#### 16 DISCLAIMER

Integrated Electronic Solutions Pty. Ltd. ABN 17 080 879 616 trading as Hendon Semiconductors ("Hendon") reserves the right to make changes to both its products and product data without notice.

Hendon makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Hendon assume any liability arising out of the use or application of any Hendon product. Hendon specifically disclaims any and all liability, including without limitation incidental or consequential damages. It is the responsibility of the customer to ensure that in all respects the application in which Hendon goods are used is suited to the purpose of the end user.

Typical performance figures, where quoted may depend on the application and therefore must be validated by the customer in each particular application. It is the responsibility of customers to ensure that any designs using Hendon products comply with good practice, applicable standards and approvals. Hendon accepts no responsibility for incorrect or non-compliant use of its products, failure to meet appropriate standards and approvals in the application of Hendon products, or for the correct engineering choice of other connected components, layout and operation of Hendon products.

Any customer purchasing or using Hendon product(s) for an unintended or unauthorised application shall indemnify and hold Hendon and its officers, employees, related companies, affiliates and distributors harmless against all claims, costs, damages, expenses, and reasonable legal fees arising out of, directly or indirectly, any claim of loss, personal injury or death associated with such unintended or unauthorised use, even if such claim alleges that Hendon was negligent regarding the design or manufacture of the relevant product(s).

#### Life Support Applications

Products of Hendon Semiconductors (Hendon) are not designed for use in life support appliances, devices or systems, where malfunction can result in personal injury. Customers using or selling Hendon products for use in such applications do so at their own risk and agree to fully indemnify Hendon for any damages resulting from such improper use or sale.