# SONY

### **Dual SPDT Low Power Switch**

# CXG1404XR

### **Description**

The CXG1404XR is a low power dual SPDT switch for Rx applications. It can be used as a differential signal switch. The CXG1404XR has on-chip logic with single control reduces component counts and simplifies PCB layout by allowing direct connection of the switch to digital base band control lines with the CMOS logic levels.

The Sony GaAs junction gate pHEMT (JPHEMT) MMIC process is used for low insertion loss and high linearity.

(Applications: CDMA/GSM/UMTS handsets, Differential signal switch)

#### **Features**

♦ Low insertion loss: 0.30 dB (Typ.) Rx (746 to 960 MHz)

0.35 dB (Typ.) Rx (1710 to 2170 MHz) 0.40 dB (Typ.) Rx (2500 to 2690 MHz)

◆ Low voltage operation: VDD = 2.5 V

♦ On chip logic with single control

◆ Small package size: XQFN-12P (2.0 mm x 2.0 mm x 0.4 mm Max.)

◆ Lead-free and RoHS compliant

#### **Structure**

GaAs Junction Gate pHEMT (JPHEMT) MMIC Switch

#### **Absolute Maximum Ratings**

(Ta = 25 °C)

Bias voltage VDD 4 V

Control voltage VCTL 4 V

Input power max. 18 dBm

Operating temperature -35 to +85 °C

Storage temperature -65 to +150 °C

GaAs MMIC's are ESD sensitive device. Special handling precautions are required.

1

E11906-PS

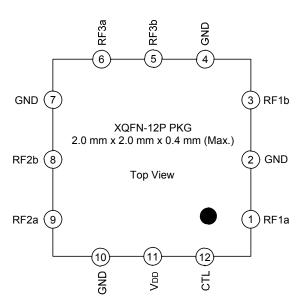

# **Pin Configuration**

SONY

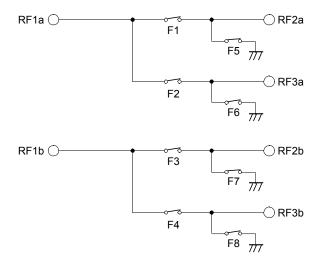

# **Block Diagram**

## **Truth Table**

| State | Active path              | CTL state | Switch state |     |     |     |     |     |     |     |

|-------|--------------------------|-----------|--------------|-----|-----|-----|-----|-----|-----|-----|

|       |                          |           | F1           | F2  | F3  | F4  | F5  | F6  | F7  | F8  |

| 1     | RF1a – RF2a, RF1b – RF2b | L         | ON           | OFF | ON  | OFF | OFF | ON  | OFF | ON  |

| 2     | RF1a – RF3a, RF1b – RF3b | Н         | OFF          | ON  | OFF | ON  | ON  | OFF | ON  | OFF |

# **DC Bias Condition**

| Parameter | Min. | Тур. | Max. | Unit |

|-----------|------|------|------|------|

| VDD       | 2.5  | 2.6  | 3.3  | V    |

| VCTL(H)   | 1.5  | 1.8  | 3.3  | V    |

| VCTL(L)   | 0    | _    | 0.3  | V    |

# **Target Specification**

(VDD = 2.6 V, Ta = 25 °C)

| Item            | Symbol | Path                                   | Condition           | Min. | Тур. | Max. | Unit |

|-----------------|--------|----------------------------------------|---------------------|------|------|------|------|

|                 | IL     | RF1a – RF2a, RF3a<br>RF1b – RF2b, RF3b | *1                  | _    | 0.30 | 0.45 |      |

| Insertion loss  |        |                                        | *2                  | 1    | 0.35 | 0.50 | dB   |

|                 |        |                                        | *3                  | 1    | 0.40 | 0.60 |      |

|                 | ISO    | RF1a – RF2a, RF3a<br>RF1b – RF2b, RF3b | 746 to 960 MHz      | 25   | 28   |      |      |

| Isolation       |        |                                        | 1710 to 2170 MHz    | 21   | 24   | _    | dB   |

|                 |        |                                        | 2500 to 2690 MHz    | 19   | 22   | _    |      |

| VSWR            | VSWR   | All ports in active paths              | 746 to 2690 MHz     | _    | _    | 1.40 | _    |

| Switching time  | Ts     |                                        | 50 % Ctl to 90 % RF | 1    | 3    | 5    | μs   |

| Control current | ICTL   |                                        | VCTL = 1.80 V       | 1    | 7    | 20   | μΑ   |

| Supply current  | IDD    |                                        | VDD = 2.60 V        | _    | 30   | 50   | μA   |

Electrical Characteristics are measured with all RF ports terminated in 50  $\boldsymbol{\Omega}$

- \*1 Pin = 10 dBm, 746 to 960 MHz

- \*2 Pin = 10 dBm, 1710 to 2170 MHz

- \*3 Pin = 10 dBm, 2500 to 2690 MHz

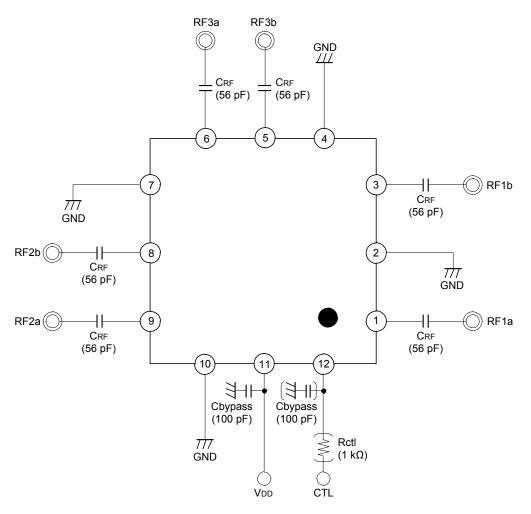

### **Recommended Circuit**

When using this IC, the following external components should be used:

Rctl: This resistor is used to improved ESD performance. 1 k $\Omega$  is recommended. CRF: This capacitor is used for RF De-coupling and must be used all application. Cbypass: This capacitor is used for DC line filtering. 100 pF is recommended.

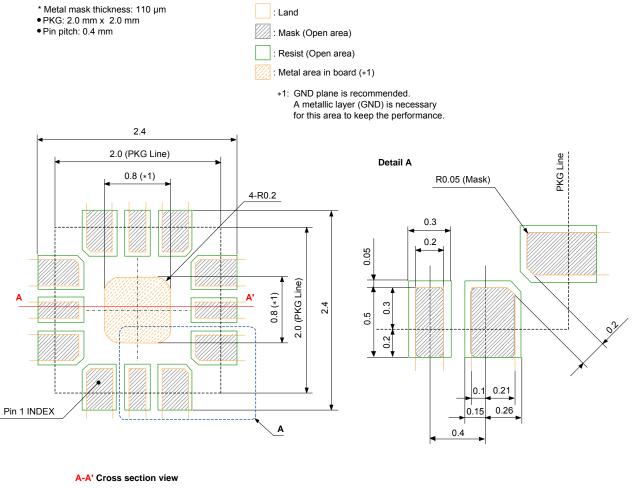

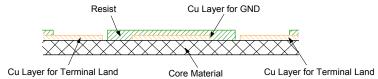

## **PCB Layout Template**

#### XQFN-12P-02 Macro drawing (Reference)

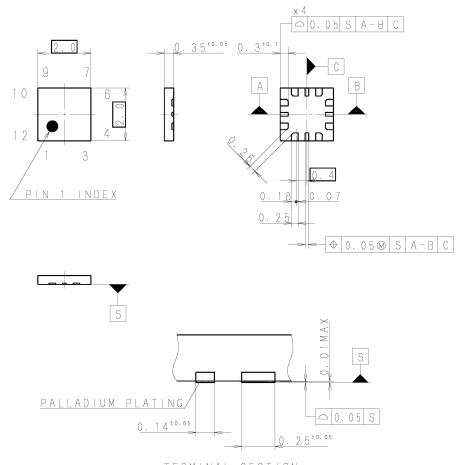

## **Package Outline**

(Unit: mm)

## 12PIN XQFN (PLASTIC)

TERMINAL SECTION

## Note:Terminal burr height 0.05mm MAX.

|   | SONY | CODE | X Q F N - 1 2 P - 0 2 |

|---|------|------|-----------------------|

| J | EITA | CODE |                       |

| J | EDEC | CODE |                       |

| PACKAGE MATERIAL | EPOXY RESIN       |

|------------------|-------------------|

| LEAD TREATMENT   | PALLADIUM PLATING |

| LEAD MATERIAL    | COPPER ALLOY      |

| PACKAGE MASS     | 0.0049            |

PACKAGE STRUCTURE

| PART No. A P - 4 0 0 0 - 1 2 0 1 3 | 3 S                                     | Rev. () |  |  |  |

|------------------------------------|-----------------------------------------|---------|--|--|--|

| ' 11.08.30                         | REVISED                                 |         |  |  |  |

| PRODUCTION LINE                    | COMPILING DIV. SDT ENGINEERING DIVISION |         |  |  |  |

| REMARKS PKG CODE: XR-012-D         |                                         |         |  |  |  |

DETAIL B

## Marking

# MARKING C: GC

注1) B部はロット番号(Max3文字で通し記号)を配置する。

| (規定文字数未満につき省略は省略規定に従う。                                                          |              |

|---------------------------------------------------------------------------------|--------------|

| 製造年は下記2進法ビット方式により表示する。)                                                         |              |

| a 部年コード(2進法ビット方式の1ビット目を表示)を配置する。                                                |              |

| b部年コード(2進法ビット方式の2ビット目を表示)を配置する。                                                 |              |

| c 部年コード(2進法ビット方式の3ビット目を表示)を配置する。                                                |              |

| d 部年コード(2進法ビット方式の4ビット目を表示)を配置する。                                                |              |

| 注2) C部は製品名(Max2文字)を配置する。                                                        |              |

| (2文字を超える場合は製品名省略標示規定に従う。)                                                       |              |

| 注3) マーク深さは、MaxO.05mmの事。                                                         |              |

| < INSTRUCTIONS >                                                                |              |

| 1) LOT NO. ( MAX 3 CHARACTERS : SERIAL CODE ) IN SECTION 8.                     |              |

| ( FOLLOW RULES FOR ABBREVIATIONS.                                               |              |

| MANUFACTURING YEAR IS DISPLAYED BY FOLLOWING BYNARY BIT SYSTEM. )               |              |

| A YEAR CODE ( THE 1ST BIT OF A BINARY SYSTEM BIT SYSTEM IS DISPLAYED IN 1 DOT ) | IN SECTION a |

| A YEAR CODE ( THE 2ND BIT OF A BINARY SYSTEM BIT SYSTEM IS DISPLAYED IN 1 DOT ) | IN SECTION b |

| A YEAR CODE ( THE 3RD BIT OF A BINARY SYSTEM BIT SYSTEM IS DISPLAYED IN 1 DOT ) | IN SECTION c |

| A YEAR CODE ( THE 4TH BIT OF A BINARY SYSTEM BIT SYSTEM IS DISPLAYED IN 1 DOT ) | IN SECTION d |

| 2) TYPE NO. ( MAX 2 CHARACTERS ) IN SECTION C.                                  |              |

| ( FOR MORE THAN 2 CHARACTERS FOLLOW RULES FOR ABBREVIATIONS. )                  |              |

| 3) MARK DEPTH MAX 0.05 mm.                                                      |              |

| AL THURS AND THE HIGH AS AN HIM.                                                |              |

**SONY** CXG1404XR

### Note

Sony reserves the right to change products and specifications without prior notice.

This information does not convey any license by any implication or otherwise under any patents or other right.

Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.