Datasheet | Rev. 1.1 | 2012

# 512Mbit Single-Data-Rate (SDR) SDRAM

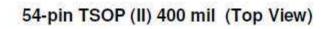

AS4C64M8S-7TCN 64Mx8 (16M x 8 x 4 Banks) AS4C32M16S-7TCN 32Mx16 (8M x 16 x 4 Banks)

# **Revision History**

### Rev. 1.1 April 2012

Revised Operating-; Standby- and Refresh Currents

### Rev. 1.0 March 2012

initial version

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document.

### 1 | Overview

This chapter gives an overview of the 512Mbit SDRAM product and describes its main characteristics.

### 1.1 Features

- Single 3.3 V ± 0.3 V Power Supply

- LVTTL compatible I/O

- DRAM organizations with 8, 16 Data In/Outputs

- Single Pulsed RAS interface

- Fully synchronous to Positive Clock Edge

- Four Banks controlled by BA0/BA1 (Bank Select)

- Programmable CAS Latency: 2, 3

- Programmable Burst Length: 1,2,4,8 or full page

- Programmable Wrap: Sequential or Interleave

- Multiple Burst Read with Single Write Option

- Automatic and Controlled Precharge Command

- Data Mask for Read/Write Control (x8)

- Dual Data Mask for byte control (x16)

- Suspend Mode and Power Down Mode

- Standard Power Operation

- Random Column Address every CK (1-N Rule)

- Operating Temperature range 0°C to 70°C. Industrial Temperature devices (Ordering code ending with "I") allow an operating temperature range of -40°C to 85°C 1

- Auto Refresh(CBR) and Self Refresh

- 8192 Refresh Cycles/64ms

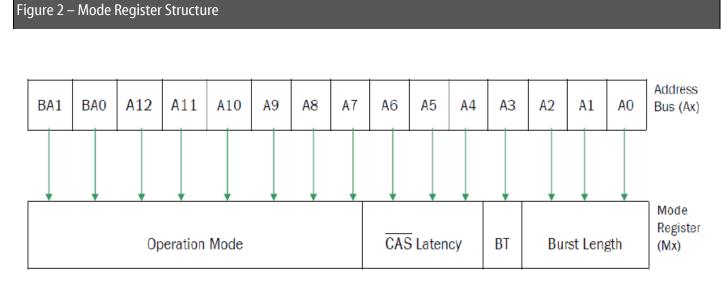

- 54-pin TSOP II (400 mil) Package

- RoHS Compliant Product <sup>2</sup>

- Electrically and mechanically JEDEC compliant

<sup>1</sup> ambient Temperature

<sup>2</sup> RoHS Compliant Product: Restriction of the use of certain hazardous substances (RoHS) in electrical and electronic equipment as defined in the directive 2002/95/EC issued by the European Parliament and of the Council of 27 January 2003. These substances include mercury, lead, cadmium, hexavalent chromium, polybrominated biphenyls and polybrominated biphenyl ethers. For more information please visit <u>http://www.alliancememory.com</u>

| Table 1 - Performance Table             |     |                  |        |                       |      |      |  |  |

|-----------------------------------------|-----|------------------|--------|-----------------------|------|------|--|--|

|                                         |     |                  |        |                       | Unit | Note |  |  |

| Speed Code                              |     |                  | -7/-71 | -7A/-7AI <sup>1</sup> |      |      |  |  |

| Max. Data Rate SDR                      |     | SDR              | 133    | 133                   | MHz  |      |  |  |

| CAS-RCD-RP Latencies                    |     |                  | 3-3-3  | 2-2-2                 | tCK  | 1    |  |  |

| Max. Clock Frequency                    | CL3 | f <sub>CK3</sub> | 133    | 133                   | MHz  |      |  |  |

|                                         | CL2 | f <sub>CK2</sub> | 100    | 133                   | MHz  |      |  |  |

| Min. RAS-CAS-Delay t <sub>RCD</sub>     |     | t <sub>RCD</sub> | 20     | 15                    | ns   |      |  |  |

| Min. Row Precharge Time t <sub>RP</sub> |     | 20               | 15     | ns                    |      |      |  |  |

| Min. Row Active Time t <sub>RAS</sub>   |     |                  | 45     | 42                    | ns   |      |  |  |

| Min. Row Cycle Time                     |     | t <sub>RC</sub>  | 67.5   | 60                    | ns   |      |  |  |

Versions marked -7A(I) support both: 2-2-2 and 3-3-3 at 133MHz (CAS-RCD-RP)

#### 1.2 Description

The 512Mbit SDRAM is a high-speed CMOS, dynamic random-access memory containing 536,870,912 bits internally configured as a quad-bank DRAM with a synchronous interface.

The x8 device is organized as  $16M \times 8 I/O \times 4$  banks, the x16 device is organized as  $8M \times 16 I/O \times 4$  banks. These synchronous devices achieve data transfer rates of up to 133 Mb/sec/pin for general applications.

See Table 1 for performance figures.

The device is designed in compliance with JEDEC standards for SDRAM memory components both electrically and mechanically.

The control signals  $\overline{RA\xi}$ -  $\overline{CA\xi}$ ,  $\overline{WE}$ -and- $\overline{CS}$  are pulsed signals which are sampled at the positive edge of each externally applied clock (CK).

A thirteen bit address bus A[12:0] together with 2 Bank select lines BA[1:0] accept address data in a  $\overrightarrow{RAS}/\overrightarrow{CAS}$  multiplexing style.

Operating the four memory banks in an interleave fashion allows random access operation to occur at a higher rate than is possible with standard DRAMs. A sequential and gapless data rate of up to 133 MHz is

possible depending on Burst Length and CASLatency. Auto Refresh (CBR) and Self Refresh operation, both are supported. The 512Mb SDRAM is available in 54-pin TSOP-Type II package.

|                                                            |                                                |                                        |                  | 100        |      |  |  |  |

|------------------------------------------------------------|------------------------------------------------|----------------------------------------|------------------|------------|------|--|--|--|

|                                                            |                                                |                                        |                  |            |      |  |  |  |

| Table 2 - Ordering Information for RoHS Compliant Products |                                                |                                        |                  |            |      |  |  |  |

| Product Part Number <sup>1</sup>                           | Org.                                           | CAS-RCD-RP<br>Latencies <sup>234</sup> | Max. Clock (MHz) | Package    | Note |  |  |  |

| Standard Temperature Range (0°C to 70°C) 6                 |                                                |                                        |                  |            |      |  |  |  |

| AS4C64M8S-7TCN                                             | ×8                                             | 3-3-3                                  | 133              | 54 TSOP II | 5    |  |  |  |

| AS4C32M16S-7TCN                                            | ×16                                            | 3-3-3                                  | 133              | 54 TSOP II | 5    |  |  |  |

| AS4C64M8S-7A                                               | ×8                                             | 2-2-2                                  | 133              | 54 TSOP II | 57   |  |  |  |

| AS4C32M16S-7A                                              | ×16                                            | 2-2-2                                  | 133              | 54 TSOP II | 5 7  |  |  |  |

| Industrial Temperature Rang                                | Industrial Temperature Range (-40°C to 85°C) 6 |                                        |                  |            |      |  |  |  |

| AS4C64M8S-7TIN                                             | ×8                                             | 3-3-3                                  | 133              | 54 TSOP II | 5    |  |  |  |

| AS4C32M16S-7TIN                                            | ×16                                            | 3-3-3                                  | 133              | 54 TSOP II | 5    |  |  |  |

| AS4C64M8S-7AI                                              | ×8                                             | 2-2-2                                  | 133              | 54 TSOP II | 5 7  |  |  |  |

| AS4C32M16S-7AI                                             | ×16                                            | 2-2-2                                  | 133              | 54 TSOP II | 57   |  |  |  |

For detailed information regarding the part numbering of Alliance Memory products, please contact Alliance Memory for a separated "Part No. Decoder".

2 CAS: Column Address Strobe

3 RCD: Row Column Delay

4 **RP: Row Precharge**

5 RoHS Compliant Product: Restriction of the use of certain hazardous substances (RoHS) in electrical and electronic equipment as defined in the directive 2002/95/EC issued by the European Parliament and of the Council of 27 January 2003. These substances include mercury, lead, cadmium, hexavalent chromium, polybrominated biphenyls and polybrominated biphenyl ethers. For more information please visit http://www.alliancememory.com

6 Operating ambient temperature surrounding the package

Versions marked -7A support both: 2-2-2 and 3-3-3 (CAS-RCD-RP) 7

#### 1.3 Addressing

| Table 3 - Addressing |                        |                        |      |  |  |  |  |

|----------------------|------------------------|------------------------|------|--|--|--|--|

| Configuration        | 64 Mb x 8 <sup>1</sup> | 32 Mb x16 <sup>1</sup> | Note |  |  |  |  |

| Bank Address         | BA[1:0]                | BA[1:0]                |      |  |  |  |  |

| Number of Banks      | 4                      | 4                      |      |  |  |  |  |

| Auto Precharge       | A10 / AP               | A10 / AP               |      |  |  |  |  |

| Auto Refresh Cycles  | 8192                   | 8192                   |      |  |  |  |  |

| Row Address          | A[12:0]                | A[12:0]                |      |  |  |  |  |

| Column Address       | A[9:0] A11             | A[9:0]                 |      |  |  |  |  |

| Number of I/Os       | 8                      | 16                     |      |  |  |  |  |

Notes:

Referred to as 'org' 1

## 2 | Configuration

This chapter contains the chip configuration.

2.1 Configuration for 54-pin TSOP II Package

The chip configuration of the SDRAM is listed by function in Table 3. The abbreviations used in the Pin# and Buffer Type column are explained in <u>Table 4</u> and <u>Table 5</u> respectively.

| Table 4 - PIN Description for 54-pin TSOP II Package |                         |                          |          |             |                                                                                            |  |  |

|------------------------------------------------------|-------------------------|--------------------------|----------|-------------|--------------------------------------------------------------------------------------------|--|--|

| Pin#                                                 | Name<br>x8 <sup>1</sup> | Name<br>x16 <sup>1</sup> | Pin Type | Buffer Type | Function                                                                                   |  |  |

| Clock Signals                                        |                         |                          |          |             |                                                                                            |  |  |

| 38                                                   | CLK                     | CLK                      | I        | LVTTL       | Clock Signal, all SDRAM Inputs are sampled on the rising edge<br>of the clock              |  |  |

| 37                                                   | CKE                     | CKE                      | I        | LVTTL       | Clock Enable activates (HIGH) and deactivates (LOW)<br>the CLK Signal                      |  |  |

| Control Signals                                      |                         |                          |          |             |                                                                                            |  |  |

| 18                                                   | RAS                     | RAS                      | I        | LVTTL       | Row Address Strobe (RAS), Column Address Strobe (CAS),<br>Write Enable (WE)                |  |  |

| 17                                                   | CAS                     | CAS                      | I        | LVTTL       |                                                                                            |  |  |

| 16                                                   | WE                      | WE                       | I        | LVTTL       |                                                                                            |  |  |

| 19                                                   | CS                      | CS                       | I        | LVTTL       | Chip Select enables (registered LOW) and disables<br>(registered HIGH) the command decoder |  |  |

| Address Signals                                      |                         |                          |          |             |                                                                                            |  |  |

| 20                                                   | BA0                     | BA0                      | Ι        | LVTTL       | Bank Address Bus BA[1:0]                                                                   |  |  |

| 21                                                   | BA1                     | BA1                      | Ι        | LVTTL       |                                                                                            |  |  |

| 23                                                   | A0                      | A0                       | Ι        | LVTTL       | Address Inputs A[12:0]                                                                     |  |  |

| 24                                                   | A1                      | A1                       | Ι        | LVTTL       |                                                                                            |  |  |

| 25                                                   | A2                      | A2                       | I        | LVTTL       |                                                                                            |  |  |

| 26                                                   | A3                      | A3                       | I        | LVTTL       |                                                                                            |  |  |

| 29                                                   | A4                      | A4                       | I        | LVTTL       |                                                                                            |  |  |

| 30                                                   | A5                      | A5                       | I        | LVTTL       |                                                                                            |  |  |

| 31                                                   | A6                      | A6                       | I        | LVTTL       |                                                                                            |  |  |

| 32                                                   | A7                      | A7                       | I        | LVTTL       |                                                                                            |  |  |

| 33                                                   | A8                      | A8                       | I        | LVTTL       |                                                                                            |  |  |

| 34                                                   | A9                      | A9                       | I        | LVTTL       |                                                                                            |  |  |

| 22                                                   | A10                     | A10                      | I        | LVTTL       |                                                                                            |  |  |

| 35                                                   | A11                     | A11                      | I        | LVTTL       |                                                                                            |  |  |

| 36                                                   | A12                     | A12                      | 1        | LVTTL       |                                                                                            |  |  |

- continued next page -

Notes:

<sup>1</sup> Referred to as 'org'

| Continued Table 4 - PIN Description for 54-pin TSOP II Package |                  |                  |          |             |                                                                                                   |  |

|----------------------------------------------------------------|------------------|------------------|----------|-------------|---------------------------------------------------------------------------------------------------|--|

| PIN#                                                           | Name<br>x8       | Name<br>x16      | PIN Type | Buffer Type | Function                                                                                          |  |

| Data Signals                                                   |                  |                  |          |             |                                                                                                   |  |

| 2                                                              | DQ0              | DQ0              | I/O      | LVTTL       | Data Signal DQ[7:0] for x8                                                                        |  |

| 4                                                              | NC               | DQ1              | I/O      | LVTTL       | Data Signal DQ[15:0] for x16                                                                      |  |

| 5                                                              | DQ1              | DQ2              | I/O      | LVTTL       |                                                                                                   |  |

| 7                                                              | NC               | DQ3              | I/O      | LVTTL       |                                                                                                   |  |

| 8                                                              | DQ2              | DQ4              | I/O      | LVTTL       |                                                                                                   |  |

| 10                                                             | NC               | DQ5              | I/O      | LVTTL       |                                                                                                   |  |

| 11                                                             | DQ3              | DQ6              | I/O      | LVTTL       |                                                                                                   |  |

| 42                                                             | NC               | DQ8              | I/O      | LVTTL       |                                                                                                   |  |

| 44                                                             | DQ4              | DQ9              | I/O      | LVTTL       |                                                                                                   |  |

| 45                                                             | NC               | DQ10             | I/O      | LVTTL       |                                                                                                   |  |

| 47                                                             | DQ5              | DQ11             | I/O      | LVTTL       |                                                                                                   |  |

| 48                                                             | NC               | DQ12             | I/O      | LVTTL       |                                                                                                   |  |

| 50                                                             | DQ6              | DQ13             | I/O      | LVTTL       |                                                                                                   |  |

| 51                                                             | NC               | DQ14             | I/O      | LVTTL       |                                                                                                   |  |

| 53                                                             | DQ7              | DQ15             | I/O      | LVTTL       |                                                                                                   |  |

| 13                                                             | NC               | DQ7              | I/O      | LVTTL       |                                                                                                   |  |

| Data Mask                                                      |                  |                  |          |             |                                                                                                   |  |

| 15                                                             | NC               | DQML             |          | LVTTL       | Data Mask                                                                                         |  |

| 39                                                             | DQM              | DQMH             |          | LVTTL       | Data Mask                                                                                         |  |

| Power Supplies                                                 |                  |                  |          | 1           |                                                                                                   |  |

| 3, 9, 43, 49                                                   | V <sub>DDQ</sub> | V <sub>DDQ</sub> | PWR      | -           | DQ Power: DQ Power to the die for improved noise immunity                                         |  |

| 1, 14, 27                                                      | V <sub>DD</sub>  | V <sub>DD</sub>  | PWR      | -           | Power Supply $+3.3V \pm 0.3V$                                                                     |  |

| 6, 12, 46, 52                                                  | V <sub>SSQ</sub> | V <sub>SSQ</sub> | PWR      | -           | DQ Ground: isolated power supply and ground for the<br>output buffers for improved noise immunity |  |

| 28, 41, 54                                                     | Vss              | Vss              | PWR      | -           | Power Supply Ground                                                                               |  |

| Not Connected                                                  |                  |                  |          |             |                                                                                                   |  |

| 40                                                             | NC               | NC               | NC       | -           | Not Connected                                                                                     |  |

| Table 5 - Abbreviations for Pin Type |                                             |  |  |  |  |

|--------------------------------------|---------------------------------------------|--|--|--|--|

| Abbreviation                         | eviation Description                        |  |  |  |  |

| I                                    | Standard input-only ball. Digital levels.   |  |  |  |  |

| 0                                    | Output. Digital levels.                     |  |  |  |  |

| I/O                                  | I/O is a bidirectional Input/Output signal. |  |  |  |  |

| PWR                                  | Power                                       |  |  |  |  |

| GND                                  | Ground                                      |  |  |  |  |

| NC                                   | Not Connected                               |  |  |  |  |

| Table 6 - Abbreviations for Buffer Type |                                                                                                                                                                                        |  |  |  |  |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Abbreviation                            | Description                                                                                                                                                                            |  |  |  |  |  |

| SSTL                                    | Serial Stub Terminated Logic (SSTL_18)                                                                                                                                                 |  |  |  |  |  |

| LVTTL                                   | Low Voltage TTL                                                                                                                                                                        |  |  |  |  |  |

| CMOS                                    | CMOS Levels                                                                                                                                                                            |  |  |  |  |  |

| OD                                      | Open Drain. The corresponding ball has 2 operational states, active low and tristate, and allows multiple devices to share as a wire-OR allows multiple devices to share as a wire-OR. |  |  |  |  |  |

# DATASHEET

Figure 1 - Ball Assignment for ×8 and ×16 Components, TSOP-54 (II)

# 3 | Functional Description

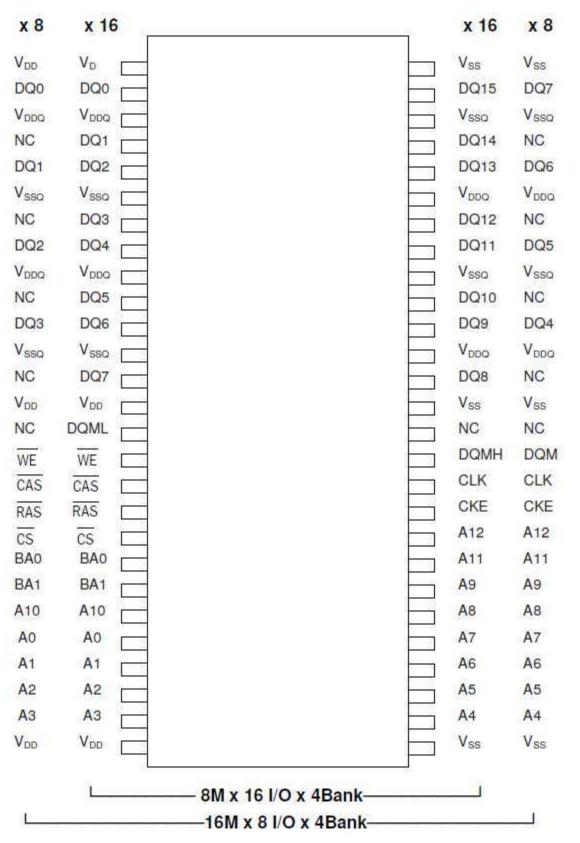

#### 3.1 Mode Register Set (MRS)

The Mode Register <sup>1</sup> stores data defining the specific mode of operation including Burst Length (BL), Burst Type, CAS Latency (CL)<sup>2</sup>, Operating Mode and write Burst Mode of the SDRAM. Since power on state of the register is not defined it must be initialized in order to avoid unpredictable start-up modes.

The Mode Register content can be altered by re-executing the Mode Register Set Command if needed. In such a case however all 4 variables must be redefined when the Mode Register Set Command is issued.

<sup>1</sup> Operation Mode, CAS Latency, Burst Type and Burst Length are user defined variables and must be programmed into the Mode Register before Read or Write Cycles may begin. The Mode Register is programmed using the Mode Register Set Command. It retains the data until it is reprogrammed or power is switched off the SDRAM.

<sup>2</sup> CAS Latency defines the delay from when a Read Command is registered on a rising Clock Edge to when the data from that Read Command becomes available at the Data I/O's.

| 人 | A |   | Π |   | C | E |

|---|---|---|---|---|---|---|

|   | M | E | M | 0 | R | Y |

### Table 7 - Mode Register (MR) Definition

| Field          | Bits   | Type <sup>1</sup> | Description                                                                                                                                                                                        |  |  |  |

|----------------|--------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Operation Mode | [14:7] | w                 | 0000000B Normal Mode<br>00000100B Multiple Burst with Single Write<br>All other states reserved.*                                                                                                  |  |  |  |

| CL             | [6:4]  | w                 | CAS Latency<br>Note: All other bit combinations are reserved.<br>010 <sub>B</sub> CL 2<br>011 <sub>B</sub> CL 3                                                                                    |  |  |  |

| BT             | 3      | w                 | Burst Type<br>OB BT Sequential<br>1B BT Interleaved                                                                                                                                                |  |  |  |

| BL             | [2:0]  | w                 | Burst LengthNote: All other bit combinations are reserved.<br>BT (Bit3=0)000BSequential BL: 1001BSequential BL: 2010BSequential BL: 4011BSequential BL: 8111BSequential: Full PageInterleave BL: 8 |  |  |  |

$^{1}$  w = write only register bits

\* BA1 and BA0 must be set to "0" when programming Mode Register MR

Burst Mode): 0 -> Normal Mode (read and write with programmed Burst Length)

M9 (Write

1 -> Multiple Burst & Single Write location access

### 3.2 Burst Mode Operation

Read and Write Operations to the device are burst oriented.

The Burst Type defines the sequence in which the data is Output and Input to the device. The Burst Types supported are sequential and interleaved. Please refer to the below table.

The Bust Length (BL) is programmable in the Mode Register Bits [2:0] and controls the number of bits that will be Output after a Read Command or being Input after a Write Command.

The Burst Operation Mode can be normal (Read and Write Cycles both are operated until the selected Burst Length is worked through) or Multiple Burst with Single Write Operation.

| Table 8 - Burst Length and Sequence (Burst Type) |                                |                                    |                                    |  |  |  |  |  |

|--------------------------------------------------|--------------------------------|------------------------------------|------------------------------------|--|--|--|--|--|

| Burst Length                                     | Starting Address<br>(A2 A1 A0) | Sequential Addressing<br>(decimal) | Interleave Addressing<br>(decimal) |  |  |  |  |  |

| 2                                                | X X 0                          | 0, 1                               | 0, 1                               |  |  |  |  |  |

|                                                  | X X 1                          | 1,0                                | 1,0                                |  |  |  |  |  |

| 4                                                | X 0 0                          | 0, 1, 2, 3                         | 0, 1, 2, 3                         |  |  |  |  |  |

|                                                  | X 0 1                          | 1, 2, 3, 0                         | 1, 0, 3, 2                         |  |  |  |  |  |

|                                                  | X 1 0                          | 2, 3, 0, 1                         | 2, 3, 0, 1                         |  |  |  |  |  |

|                                                  | X11                            | 3, 0, 1, 2                         | 3, 2, 1, 0                         |  |  |  |  |  |

| 8                                                | 000                            | 0, 1, 2, 3, 4, 5, 6, 7             | 0, 1, 2, 3, 4, 5, 6, 7             |  |  |  |  |  |

|                                                  | 001                            | 1, 2, 3, 4, 5, 6, 7, 0             | 1, 0, 3, 2, 5, 4, 7, 6             |  |  |  |  |  |

|                                                  | 010                            | 2, 3, 4, 5, 6, 7, 0, 1             | 2, 3, 0, 1, 6, 7, 4, 5             |  |  |  |  |  |

|                                                  | 011                            | 3, 4, 5, 6, 7, 0, 1, 2             | 3, 2, 1, 0, 7, 6, 5, 4             |  |  |  |  |  |

|                                                  | 100                            | 4, 5, 6, 7, 0, 1, 2, 3             | 4, 5, 6, 7, 0, 1, 2, 3             |  |  |  |  |  |

|                                                  | 101                            | 5, 6, 7, 0, 1, 2, 3, 4             | 5, 4, 7, 6, 1, 0, 3, 2             |  |  |  |  |  |

|                                                  | 110                            | 6, 7, 0, 1, 2, 3, 4, 5             | 6, 7, 4, 5, 2, 3, 0, 1             |  |  |  |  |  |

|                                                  | 111                            | 7, 0, 1, 2, 3, 4, 5, 6             | 7, 6, 5, 4, 3, 2, 1, 0             |  |  |  |  |  |

| 256 (Full Page)                                  | n                              | Cn, Cn+1, Cn+2                     | 1, 0, 3, 2                         |  |  |  |  |  |

# 4 | Truth Tables

The truth tables in this chapter summarize the commands and the signal coding to control the SDRAM.

| Table 9 - Command Truth Table |                            |                        |                        |        |        |        |        |     |            |        |                      |                     |

|-------------------------------|----------------------------|------------------------|------------------------|--------|--------|--------|--------|-----|------------|--------|----------------------|---------------------|

| Function                      | Device State               | C<br>Previous<br>Cycle | KE<br>Current<br>Cycle | CS     | RAS    | CAS    | WE     | DQM | BA0<br>BA1 | A10    | A12<br>A11<br>A[9:0] | Note <sup>123</sup> |

| Mode Register Set             | Idle                       | Н                      | Х                      | L      | L      | L      | L      | Х   | 0          | P Code | e                    |                     |

| Auto (CBR) Refresh            | Idle                       | Н                      | Н                      | L      | L      | L      | Н      | Х   | Х          | Х      | Х                    |                     |

| Self-Refresh Entry            | Idle                       | Н                      | L                      | L      | L      | L      | Н      | Х   | Х          | Х      | Х                    |                     |

| Self-Refresh Exit             | ldle (Self-<br>Refresh)    | L                      | Н                      | H<br>L | X<br>H | X<br>H | X<br>H | х   | Х          | Х      | Х                    |                     |

| Single Bank Precharge         | Re. Current<br>State Table | Η                      | Х                      | L      | L      | Η      | L      | Х   | BS         | L      | х                    | 4                   |

| Precharge all Banks           | Re. Current<br>State Table | Н                      | Х                      | L      | L      | Н      | L      | Х   | Х          | Н      | Х                    |                     |

| Bank Activate                 | Idle                       | Η                      | Х                      | L      | L      | Н      | Н      | Х   | BS         | Row    | Address              |                     |

| Write                         | Active                     | Н                      | Х                      | L      | Н      | L      | L      | Х   | BS         | L      | Column               | 4                   |

| Write with Auto-<br>Precharge | Active                     | Η                      | Х                      | L      | Н      | L      | L      | Х   | BS         | Н      | Column               | 4                   |

| Read                          | Active                     | Н                      | Х                      | L      | Н      | L      | Η      | Х   | BS         | L      | Column               | 4                   |

| Read with Auto-<br>Precharge  | Active                     | Н                      | Х                      | L      | Н      | L      | Η      | Х   | BS         | Н      | Column               | 4                   |

| Burst Stop                    | Active                     | Н                      | Х                      | L      | Н      | Н      | L      | Х   | Х          | Х      | Х                    |                     |

| No Operation                  | Any                        | Н                      | Х                      | L      | Н      | Н      | Н      | Х   | Х          | Х      | Х                    |                     |

| Device Deselect               | Any                        | Н                      | Х                      | Н      | Х      | Х      | Х      | Х   | Х          | Х      | Х                    |                     |

| Clock Suspend Mode<br>Entry   | Active                     | Η                      | L                      | Х      | Х      | Х      | Х      | х   | Х          | Х      | х                    | 5                   |

| Clock Suspend Mode<br>Exit    | Active                     | L                      | Η                      | Х      | Х      | Х      | Х      | Х   | Х          | Х      | х                    | 5                   |

| Data Write/Output<br>Enable   | Active                     | Н                      | Х                      | Х      | Х      | Х      | Х      | L   | Х          | Х      | х                    | 6                   |

| Data Write/Output<br>Disable  | Active                     | Η                      | Х                      | Х      | Х      | Х      | Х      | Н   | Х          | Х      | Х                    | 6                   |

| Power Down Entry              | Idle/Active                | Η                      | L                      | H<br>L | X<br>H | X<br>H | X<br>H | Х   | Х          | Х      | х                    | 7, 8                |

| Power Down Exit               | Any(Power<br>Down)         | L                      | Η                      | H<br>L | X<br>H | X<br>H | X<br>H | Х   | Х          | х      | Х                    | 7, 8                |

<sup>1</sup> All SDRAM Operations are defined by states of CS, WE, RAS, CAS, and CKE at the rising edge of the clock.

<sup>2</sup> "X" means H or L (but a defined logic level).

<sup>3</sup> Operation that is not specified is illegal and after such an event, in order to guarantee proper operation, the DRAM must be powered down and then restarted through the specified initialization sequence before normal operation can continue.

<sup>4</sup> Bank addresses BA[1:0] determine which bank is to be operated upon

<sup>5</sup> In normal access mode, CKE is held high and CK is enabled. When CKE is low it freezes the internal clock and extends data Read and Write operations. One clock delay is required for mode entry and exit.

- <sup>6</sup> DQM has two functions for the data DQ Read and Write operations. During a Read Cycle when DQM goes high during a clock timing the data outputs are disabled and become high impedance after a two-clock delay. During Write Cycles when activated the Write operation at the clock cycle is prohibited (zero clock latency).

- All banks must be precharged before entering Power Down Mode. If this command is issued during a Burst operation, the device state will be Clock Suspend Mode. The Powerd Down Mode does not perform any Refresh operations therefore the device can not remain in this mode longer than the Refresh period (t<sub>REF</sub>) duration. One clock delay is required for mode entry and exit.

- <sup>8</sup> A No Operation or Device Deselect Command is required on the next clock edge following CKE going high.

#### Table 10 – Bank Selection Bits (BS) Truth Table

| BA0 | BA1 | Bank   |

|-----|-----|--------|

| L   | L   | Bank 0 |

| Н   | L   | Bank 1 |

| L   | Н   | Bank 2 |

| Н   | Н   | Bank 3 |

| Table 11 - Clock | cEnable (C        | KE) Truth T      | able    |      |    |    |             |             |                                                                     |       |

|------------------|-------------------|------------------|---------|------|----|----|-------------|-------------|---------------------------------------------------------------------|-------|

| Current State    | C                 | KE               | Com     | mand |    |    |             |             | Action                                                              | Notes |

|                  | Previous<br>Cycle | Current<br>Cycle | -<br>CS | RAS  | CA | WE | BAO,<br>BA1 | A12<br>- A0 |                                                                     |       |

| Self Refresh     | Н                 | Х                | Х       | Х    | Х  | Х  | Х           | Х           | INVALID                                                             | 1     |

|                  | L                 | Н                | Н       | Х    | Х  | Х  | Х           | Х           | Exit Self Refresh with Device Deselect                              | 2     |

|                  | L                 | Н                | L       | Н    | Н  | Н  | Х           | Х           | Exit Self Refresh with No Operation                                 | 2     |

|                  | L                 | L                | Х       | Х    | Х  | Х  | Х           | Х           | Maintain Self Refresh                                               |       |

| Power Down       | Н                 | Х                | Х       | Х    | Х  | Х  | Х           | Х           | INVALID                                                             | 1     |

|                  | L                 | Н                | Н       | Х    | Х  | Х  | Х           | Х           | Power Down Mode exit, all Banks Idle                                | 2     |

|                  | L                 | L                | Х       | Х    | Х  | Х  | Х           | Х           | Maintain Power Down Mode                                            |       |

| All Banks Idle   | Н                 | Н                | Н       | Х    | Х  | Х  |             |             |                                                                     | 3     |

|                  | Н                 | Н                | L       | Н    | Х  | Х  |             |             | Refer to the Idle State section of the<br>Current State Truth Table | 3     |

|                  | Н                 | Н                | L       | L    | Н  | Х  |             |             |                                                                     | 3     |

|                  | Н                 | Н                | L       | L    | L  | Н  | Х           | Х           | CBR Refresh                                                         |       |

|                  | Н                 | Н                | L       | L    | L  | L  | OP          | Code        | Mode Register Set                                                   | 4     |

|                  | Н                 | L                | Н       | Х    | Х  | Х  |             |             |                                                                     | 3     |

|                  | Н                 | L                | L       | Н    | Х  | Х  |             |             | Refer to the Idle State section of the<br>Current State Truth Table | 3     |

|                  | Н                 | L                | L       | L    | Н  | Х  |             |             |                                                                     | 3     |

|                  | Н                 | L                | L       | L    | L  | Н  | Х           | Х           | Entry Self Refresh                                                  | 4     |

|                  | Н                 | L                | L       | L    | L  | L  | OP          | Code        | Mode Register Set                                                   |       |

|                  | L                 | Х                | Х       | Х    | Х  | Х  | Х           | Х           | Power Down                                                          | 4     |

| Any State        | Н                 | Н                | х       | х    | х  | х  | х           | х           | Refer to operations in the Current State<br>Truth Table             |       |

| other than       | Н                 | L                | Х       | Х    | Х  | Х  | Х           | Х           | Begin Clock Suspend next Cycle                                      | 5     |

| listed above     | L                 | Н                | Х       | Х    | Х  | Х  | Х           | Х           | Exit Clock Suspend next Cycle                                       |       |

|                  | L                 | L                | Х       | Х    | Х  | Х  | Х           | Х           | Maintain Clock Suspend                                              |       |

1. For the given Current State CKE must be low in the previous Cycle.

2. When CKE has a low to high transition, the Clock and other Inputs are re-enabled asynchronously. The minimum setup time for CKE (t<sub>CES</sub>) must be satisfied. When exiting power down mode, a NOP command (or Device Deselected Command) is required on the first rising clock after CKE goes high (see page 26).

3. The address inputs depend on the command that is issued. See the Idle State section of the current State Truth Table for more information.

4. The Precharge Power Down Mode, the Self Refresh Mode, and the Mode Register Set can only entered from the all banks idle state.

5. Must be a legal command as defined in the Current State Truth Table.

Γ

| Current State |        |         |   |    | Comma    | nd          |                      | Action                                      | Notes |

|---------------|--------|---------|---|----|----------|-------------|----------------------|---------------------------------------------|-------|

|               | <br>CS | <br>RA§ |   | WE | BAO, BA1 | A12- A0     | Description          |                                             |       |

| Idle          | L      | L       | L | L  | 0        | P Code      | Mode Register Set    | Set the Mode Register                       | 2     |

|               | L      | L       | L | Н  | Х        | Х           | Auto or Self Refresh | Start Auto or Self Refresh                  | 2, 3  |

|               | L      | L       | Н | L  | BS       | Х           | Precharge            | No Operation                                |       |

|               | L      | L       | Н | Н  | BS       | Row Address | Bank Activate        | Activate the specified bank and row         |       |

|               | L      | Н       | L | L  | BS       | Column      | Write w/o Prechage   | ILLEGAL                                     | 4     |

|               | L      | Н       | L | Н  | BS       | Column      | Read w/o Prechage    | ILLEGAL                                     | 4     |

|               | L      | Н       | Н | L  | Х        | Х           | Burst Stop           | ILLEGAL                                     |       |

|               | L      | Н       | Н | Н  | Х        | Х           | No Operation         | No Operation                                |       |

|               | Н      | Х       | Х | Х  | Х        | Х           | Device Deselect      | No Operation or Power Down                  | 5     |

| Row Active    | L      | L       | L | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                     |       |

|               | L      | L       | L | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                     |       |

|               | L      | L       | Н | L  | BS       | Х           | Precharge            | Precharge                                   | 6     |

|               | L      | L       | Н | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                     | 4     |

|               | L      | Н       | L | L  | BS       | Column      | Write                | Start Write; Determine if<br>Auto Precharge | 7,8   |

|               | L      | Н       | L | Н  | BS       | Column      | Read                 | Start Read; Determine if<br>Auto Precharge  | 7,8   |

|               | L      | Н       | Н | L  | Х        | Х           | Burst Stop           | ILLEGAL                                     |       |

|               | L      | Н       | Н | Н  | Х        | Х           | No Operation         | No Operation                                |       |

|               | Н      | Х       | Х | Х  | Х        | Х           | Device Deselect      | No Operation                                |       |

| Read          | L      | L       | L | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                     |       |

|               | L      | L       | L | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                     |       |

|               | L      | L       | Н | L  | BS       | Х           | Precharge            | Terminate Burst; Start Precharge            |       |

|               | L      | L       | Н | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                     | 4     |

|               | L      | Н       | L | L  | BS       | Column      | Write                | Terminate Burst; Start Write Cycle          | 8, 9  |

|               | L      | Н       | L | Н  | BS       | Column      | Read                 | Terminate Burst; Start a new<br>Read Cycle  | 8, 9  |

|               | L      | Н       | Н | L  | Х        | Х           | Burst Stop           | Burst Stop                                  |       |

|               | L      | Н       | Н | Н  | Х        | Х           | No Operation         | Continue the Burst                          |       |

|               | Н      | Х       | Х | Х  | Х        | Х           | Device Deselect      | Continue the Burst                          |       |

| Write         | L      | L       | L | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                     |       |

|               | L      | L       | L | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                     |       |

|               | L      | L       | Н | L  | BS       | Х           | Precharge            | Terminate Burst; Start the Precharge        |       |

|               | L      | L       | Н | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                     | 4     |

|               | L      | Н       | L | L  | BS       | Column      | Write                | Terminate Burst; Start a new<br>Write Cycle | 8, 9  |

|               | L      | Н       | L | Н  | BS       | Column      | Read                 | Terminate Burst; Start the Read Cycle       | 8, 9  |

|               | L      | Н       | Н | L  | Х        | Х           | Burst Stop           | Burst Stop                                  |       |

|               | L      | Н       | Н | Н  | Х        | Х           | No Operation         | Continue the Burst                          |       |

|               | Н      | Х       | Х | Х  | Х        | Х           | Device Deselect      | Continue the Burst                          |       |

| Table 12 – Curr | ent Sta | ate Tru | th Tab | le | Part 2/  | 3           |                      |                                                              |       |

|-----------------|---------|---------|--------|----|----------|-------------|----------------------|--------------------------------------------------------------|-------|

| Current State   |         |         |        |    | Comma    | nd          |                      | Action                                                       | Notes |

|                 | <br>CS  | <br>RA§ | CA     | WE | BAO, BA1 | A12- A0     | Description          |                                                              |       |

| Read with Auto  | L       | L       | L      | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                                      |       |

| Precharge       | L       | L       | L      | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                                      |       |

|                 | L       | L       | Н      | L  | BS       | Х           | Precharge            | ILLEGAL                                                      | 4     |

|                 | L       | L       | Н      | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                                      | 4     |

|                 | L       | Н       | L      | L  | BS       | Column      | Write                | ILLEGAL                                                      | 4     |

|                 | L       | Н       | L      | Н  | BS       | Column      | Read                 | ILLEGAL                                                      | 4     |

|                 | L       | Н       | Н      | L  | Х        | Х           | Burst Stop           | ILLEGAL                                                      |       |

|                 | L       | Н       | Н      | Н  | Х        | Х           | No Operation         | Continue the Burst                                           |       |

|                 | Н       | Х       | Х      | Х  | Х        | Х           | Device Deselect      | Continue the Burst                                           |       |

| Write with Auto | L       | L       | L      | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                                      |       |

| Precharge       | L       | L       | L      | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                                      |       |

|                 | L       | L       | Н      | L  | BS       | Х           | Precharge            | ILLEGAL                                                      | 4     |

|                 | L       | L       | Н      | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                                      | 4     |

|                 | L       | Н       | L      | L  | BS       | Column      | Write                | ILLEGAL                                                      | 4     |

|                 | L       | Н       | L      | Н  | BS       | Column      | Read                 | ILLEGAL                                                      | 4     |

|                 | L       | Н       | Н      | L  | Х        | Х           | Burst Stop           | ILLEGAL                                                      |       |

|                 | L       | Н       | Н      | Н  | Х        | Х           | No Operation         | Continue the Burst                                           |       |

|                 | Н       | Х       | Х      | Х  | Х        | Х           | Device Deselect      | Continue the Burst                                           |       |

| Precharging     | L       | L       | L      | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                                      |       |

|                 | L       | L       | L      | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                                      |       |

|                 | L       | L       | Н      | L  | BS       | Х           | Precharge            | No Operation; Bank(s) idle after $t_{\mbox{\scriptsize RP}}$ |       |

|                 | L       | L       | Н      | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                                      | 4     |

|                 | L       | Н       | L      | L  | BS       | Column      | Write                | ILLEGAL                                                      | 4     |

|                 | L       | Н       | L      | Н  | BS       | Column      | Read                 | ILLEGAL                                                      | 4     |

|                 | L       | Н       | Н      | L  | Х        | Х           | Burst Stop           | ILLEGAL                                                      |       |

|                 | L       | Н       | Н      | Н  | Х        | Х           | No Operation         | No Operation; Bank(s) idle after $t_{\text{RP}}$             |       |

|                 | Н       | Х       | Х      | Х  | Х        | Х           | Device Deselect      | No Operation; Bank(s) idle after $\mathbf{t}_{\text{RP}}$    |       |

| Row Activating  | L       | L       | L      | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                                      |       |

|                 | L       | L       | L      | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                                      |       |

|                 | L       | L       | Н      | L  | BS       | Х           | Precharge            | ILLEGAL                                                      | 4     |

|                 | L       | L       | Н      | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                                      | 4, 10 |

|                 | L       | Н       | L      | L  | BS       | Column      | Write                | ILLEGAL                                                      | 4     |

|                 | L       | Н       | L      | Н  | BS       | Column      | Read                 | ILLEGAL                                                      | 4     |

|                 | L       | Н       | Н      | L  | Х        | Х           | Burst Stop           | ILLEGAL                                                      |       |

|                 | L       | Н       | Н      | Н  | х        | Х           | No Operation         | No Operation; Row Active after $t_{\text{RCD}}$              |       |

|                 | Н       | Х       | Х      | Х  | Х        | Х           | Device Deselect      | No Operation; Row Active after $\mathbf{t}_{RCD}$            |       |

| Table 12 – Curr  | ent Sta | ate Tru | th Tab | le | Part 3/  | '3          |                      |                                              |       |

|------------------|---------|---------|--------|----|----------|-------------|----------------------|----------------------------------------------|-------|

| Current State    |         |         |        |    | Comma    | nd          |                      | Action                                       | Notes |

|                  | CS      | RAS     | CA     | WE | BAO, BA1 | A12- A0     | Description          |                                              |       |

| Write Recovering | L       | L       | L      | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                      |       |

|                  | L       | L       | L      | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                      |       |

|                  | L       | L       | Н      | L  | BS       | Х           | Precharge            | ILLEGAL                                      | 4     |

|                  | L       | L       | Н      | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                      | 4     |

|                  | L       | Н       | L      | L  | BS       | Column      | Write                | Start Write; Determine if Auto<br>Precharge  | 9     |

|                  | L       | Н       | L      | н  | BS       | Column      | Read                 | Start Read; Determine if Auto<br>Precharge   | 9     |

|                  | L       | Н       | Н      | Н  | Х        | Х           | No Operation         | No Operation; Row Active after $t_{DPL}$     |       |

|                  | Н       | Х       | Х      | Х  | Х        | Х           | Device Deselect      | No Operation; Row Active after $t_{DPL}$     |       |

| Write Recovering | L       | L       | L      | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                      |       |

| with Auto        | L       | L       | L      | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                      |       |

| Precharge        | L       | L       | Н      | L  | BS       | Х           | Precharge            | ILLEGAL                                      | 4     |

|                  | L       | L       | Н      | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                      | 4     |

|                  | L       | Н       | L      | L  | BS       | Column      | Write                | ILLEGAL                                      | 4, 9  |

|                  | L       | Н       | L      | Н  | BS       | Column      | Read                 | ILLEGAL                                      | 4, 9  |

|                  | L       | Н       | Н      | Н  | Х        | Х           | No Operation         | No Operation; Precharge after $t_{DPL}$      |       |

|                  | Н       | Х       | Х      | Х  | Х        | Х           | Device Deselect      | No Operation; Precharge after $t_{DPL}$      |       |

| Refreshing       | L       | L       | L      | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                      |       |

|                  | L       | L       | L      | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                      |       |

|                  | L       | L       | Н      | L  | BS       | Х           | Precharge            | ILLEGAL                                      |       |

|                  | L       | L       | Н      | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                      |       |

|                  | L       | Н       | L      | L  | BS       | Column      | Write                | ILLEGAL                                      |       |

|                  | L       | Н       | L      | Н  | BS       | Column      | Read                 | ILLEGAL                                      |       |

|                  | L       | Н       | Н      | Н  | Х        | х           | No Operation         | No Operation; Idle after $t_{\text{RC}}$     |       |

|                  | Н       | Х       | Х      | Х  | Х        | Х           | Device Deselect      | No Operation; Idle after $t_{RC}$            |       |

| Mode Register    | L       | L       | L      | L  | 0        | P Code      | Mode Register Set    | ILLEGAL                                      |       |

| Accessing        | L       | L       | L      | Н  | Х        | Х           | Auto or Self Refresh | ILLEGAL                                      |       |

|                  | L       | L       | Н      | L  | BS       | Х           | Precharge            | ILLEGAL                                      |       |

|                  | L       | L       | Н      | Н  | BS       | Row Address | Bank Activate        | ILLEGAL                                      |       |

|                  | L       | Н       | L      | L  | BS       | Column      | Write                | ILLEGAL                                      |       |

|                  | L       | Н       | L      | Н  | BS       | Column      | Read                 | ILLEGAL                                      |       |

|                  | L       | Н       | Н      | Н  | Х        | Х           | No Operation         | No Operation; Idle after two<br>clock cycles |       |

|                  | Н       | х       | х      | х  | Х        | Х           | Device Deselect      | No Operation; Idle after two<br>clock cycles |       |

#### Legend of the Current State Truth Table (Part 1 to 3)

- 1. CKE is assumed to be active (high) in the previous cycle for all entries. The Current State is the state of the bank that the Command is being applied to.

- 2. All Banks must be idle; otherwise, it is an illegal action.

- 3. If CKE is active (high) the SDRAM will start the Auto (CBR) Refresh Operation, if CKE is inactive (low) than the Self Refresh mode is entered.

- 4. The Current State refers to only one of the banks. If BS selects this bank then the action is illegal. If BS selects the bank not being referenced by the Current State then the action may be legal depending on the state of that bank.

- 5. If CKE is inactive (low) then the Power Down mode is entered; otherwise there is a No Operation.

- 6. The minimum and maximum Active time ( $t_{RAS}$ ) must be satisfied.

- 7. The RA(to CA(Delay ( $t_{RCD}$ ) must occur before the command is given.

- 8. Column address A10 is used to determine if the Auto Precharge function is activated.

- 9. The command must satisfy any bus contention, bus turn around, and/or write recovery requirements.

- 10. The command is illegal if the minimum bank to bank delay time ( $t_{RRD}$ ) is not satisfied

### 5 | Electrical Characteristics

This chapter describes the Electrical Characteristics.

#### 5.1 Absolute Maximum Ratings

Caution is needed not to exceed absolute maximum ratings of the DRAM device at any time.

| Table 13 - Absolute Maximum Ratings |                                                             |      |                      |      |      |  |  |  |  |

|-------------------------------------|-------------------------------------------------------------|------|----------------------|------|------|--|--|--|--|

| Symbol                              | Parameter                                                   | Ra   | ating                | Unit | Note |  |  |  |  |

|                                     |                                                             | Min. | Max.                 |      |      |  |  |  |  |

| V <sub>DD</sub>                     | Voltage on $V_{DD}$ pin relative to $V_{SS}$                | -0.3 | +4.6                 | V    |      |  |  |  |  |

| V <sub>DDQ</sub>                    | Voltage on V <sub>DDQ</sub> pin relative to V <sub>ss</sub> | -0.3 | +4.6                 | V    |      |  |  |  |  |

| V <sub>IN</sub> V <sub>OUT</sub>    | Voltage on any pin relative to V <sub>ss</sub>              | -0.3 | V <sub>DD</sub> +0.3 | ۷    |      |  |  |  |  |

| P <sub>D</sub>                      | Power Dissipation                                           | -    | +1.0                 | W    |      |  |  |  |  |

| T <sub>STG</sub>                    | Storage Temperature                                         | -55  | +125                 | °C   | 1    |  |  |  |  |

Storage Temperature is the ambient (case surface) temperature (on the center/top side) of the DRAM

#### Attention:

1

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

| Table 14 - DRAM Component Operating Temperature Range |                                                          |      |       |      |      |  |  |  |

|-------------------------------------------------------|----------------------------------------------------------|------|-------|------|------|--|--|--|

| Symbol                                                | Parameter                                                | Ra   | ating | Unit | Note |  |  |  |

|                                                       |                                                          | Min. | Max.  |      |      |  |  |  |

| T <sub>A</sub>                                        | Operating Temperature for standard product               | 0    | +70   | °C   | 123  |  |  |  |

| T <sub>A</sub>                                        | Operating Temperature for Industrial Temperature product | -40  | +85   | °C   | 123  |  |  |  |

<sup>1</sup> Operating Temperature is the ambient temperature around the DRAM.

<sup>2</sup> The Operating Temperature ranges are the temperatures where all DRAM specification will be supported.

<sup>3</sup> During operation, the temperature must be maintained under all other specification parameters.

### 5.2 DC Characteristics

| Table 15 - Recommended DC Operating Conditions |                           |       |      |                       |   |    |  |  |  |  |

|------------------------------------------------|---------------------------|-------|------|-----------------------|---|----|--|--|--|--|

| Symbol                                         | ParameterRatingUnitNote   |       |      |                       |   |    |  |  |  |  |

|                                                |                           | Min.  | Тур. | Max.                  |   |    |  |  |  |  |

| V <sub>DD</sub>                                | Supply Voltage            | 3.0   | 3.3  | 3.6                   | V | 1  |  |  |  |  |

| V <sub>DDQ</sub>                               | Supply Voltage for Output | 3.0   | 3.3  | 3.6                   | V | 1  |  |  |  |  |

| V <sub>IH</sub>                                | Input High Voltage        | 2.0   |      | V <sub>DD</sub> + 0.3 | V | 12 |  |  |  |  |

| V <sub>TT</sub>                                | Termination Voltage       | - 0.3 |      | 0.8                   | V | 13 |  |  |  |  |

1 2

All Voltages are referenced to V<sub>SS</sub> and V<sub>SSQ</sub> V<sub>IH</sub> (max) = V<sub>DD</sub> + 1.2V for pulse width  $\leq$  5ns V<sub>IL</sub> (min) = V<sub>SS</sub> + 1.2V for pulse width  $\leq$  5ns 3

| Table 16 - Input and Output Leakage Currents |                                                              |      |      |      |      |  |  |  |

|----------------------------------------------|--------------------------------------------------------------|------|------|------|------|--|--|--|

| Symbol                                       | Parameter / Condition                                        | Min. | Max. | Unit | Note |  |  |  |

| ١ <sub>IL</sub>                              | Input Leakage Current; any input 0 V < VIN < V <sub>DD</sub> | -2   | +2   | μA   | 1, 2 |  |  |  |

| IOL                                          | Output Leakage Current; 0 V < VOUT < V <sub>DDQ</sub>        | -2   | +2   | μA   | 2    |  |  |  |

| <sup>1</sup> All other pins                  | not under test = 0 V                                         |      |      |      |      |  |  |  |

2  $V_{DD} = 3.3V \pm 0.3V$

| Table 17 – Do   | C Logic Output Levels                          |      |      |      |      |

|-----------------|------------------------------------------------|------|------|------|------|

| Symbol          | Parameter / Condition                          | Min. | Max. | Unit | Note |

| V <sub>OH</sub> | Output Level (LVTTL); Output "H" Voltage Level | 2.4  | _    | V    | 1    |

| VOL             | Output Level (LVTTL); Output "L" Voltage Level | -    | 0.4  | V    | 2    |

1  $I_{out} = -2.0 \text{mA}$

2  $I_{out} = +2.0 \text{mA}$

### 5.3 Operating-, Standby- and Refresh Currents

| Table 18          | – Operating-, Standby- and                          | Refresh Currents                                                                               |                         |      |      |

|-------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------|------|------|

| Symbol            | Parameter                                           | Test Condition                                                                                 | -7/-7A (133MHz)<br>Max. | Unit | Note |

| ICC1              | Operating Current                                   | 1 bank operation <sup>1</sup><br>$t_{RC} = t_{RC(min)}, t_{CK} = min$                          | 130                     | mA   | 23   |

| I <sub>CC2P</sub> | Precharge Standby Current                           | $CKE \le V_{IL(max)}, ^{t}CK = min, CS = V_{IH(min)}$                                          | 7                       | mA   |      |

| ICC2PS            | in Power Down Mode                                  | $CKE \le V_{IL(max)}, t_{CK} = \infty, CS = V_{IH(min)}$                                       | 5                       | mA   |      |

| ICC2N             | Precharge Standby Current<br>in Non-Power Down Mode | $CKE \ge V_{IH(min)}, ^{t}CK = min, CS = V_{IH(min)}$                                          | 58                      | mA   | 4    |

| ICC3N             | No Operation Comment                                | $\frac{-}{CKE \ge V_{IH(min)}, t_{CK} = min, CS = V_{IH(min)}}$                                | 75                      | mA   | 4    |

| ICC3P             | No Operating Current<br>(Active State 4bank)        | $CKE \leq V_{IL(max)}, ^{t}CK = min$                                                           | 10                      | mA   | 5    |

| ICC3NS            | (Active State Isanky                                | $CKE \ge V_{IL(min)}, t_{CK} = \infty$                                                         | 49                      | mA   | 7    |

| ICC4              | Operating Current (Burst<br>Mode)                   | t <sub>CK =min</sub> , Rea/Write command cycling,<br>Multiple banks active, gapless data, BL=4 | 120                     | mA   | 36   |

| ICC5              | Auto (CBR) Refresh Current                          | $t_{CK=min}$ , $t_{RC} = t_{RC(min)}$ , CBR command Cycling                                    | 270                     | mA   |      |

| ICC6N             | Self Refresh Current                                | CKE ≤ 0.2V                                                                                     | 5                       | mA   |      |

<sup>1</sup> Active-Precharge command cycling without Burst Operation.

<sup>2</sup> These parameters depend on the cycle rate and are measured with the cycle determined by the minimum value of <sup>t</sup>CK and <sup>t</sup>RC. Input signals are changed up to three times during <sup>t</sup>RC(min).

The specified values are obtained with the output open.

Input signals are changed once during three clock cycles.

Input signals are changed once during three clock cycles.

Active Standby Current will be higher if Clock Suspend is entered during a Burst Read Cycle (add 1mA per DQ).

- 6 Input signals are changed once during  $t_{CK} = min$

- 7 Input signals are stable

### 5.4 Input/Output Capacitance

This chapter contains the Input and the Output Capacitance.

| Table 19 - Input/Output Capacitance |                                                |      |     |     |      |       |  |  |

|-------------------------------------|------------------------------------------------|------|-----|-----|------|-------|--|--|

| Symbol                              | Parameter                                      | Min. | Тур | Max | Unit | Notes |  |  |

| ССК                                 | Input Capacitance, CK                          | 2.5  | 2.8 | 3.5 | рF   |       |  |  |

| CI                                  | Input Capacitance, all other Input - only pins | 2.5  | 3.0 | 3.8 | pF   |       |  |  |

| CIO                                 | Input/Output Capacitance, DQn                  | 4.0  | 4.5 | 6.5 | рF   |       |  |  |

#### 5.5 Clock- and Clock Enable Parameters

This chapter describes the Clock- and Clock Enable Parameters.

| Speed G          | rade                               | -7 / -71 |      | -7A / -7AI |      |      |      |

|------------------|------------------------------------|----------|------|------------|------|------|------|

| Symbol           | Parameter                          | Min.     | Max. | Min.       | Max. | Unit | Note |

| t <sub>CK3</sub> | Clock Cycle Time, CAS Latency = 3  | 7.5      | 1000 | 7          | 1000 | ns   |      |

| t <sub>CK2</sub> | Clock Cycle Time, CAS Latency = 2  | 10       | 1000 | 7.5        | 1000 | ns   |      |

| t <sub>AC3</sub> | Clock Access Time, CAS Latency = 3 |          | 5.4  | —          | 5.4  | ns   | 1    |

| t <sub>AC2</sub> | Clock Access Time, CAS Latency = 2 | _        | 6    |            | 5.4  | ns   | 1    |

| <sup>t</sup> CKH | Clock High Pulse Width             | 2.5      | _    | 2.5        | —    | ns   |      |

| tckl             | Clock Low Pulse Width              | 2.5      | _    | 2.5        | _    | ns   |      |

| tCES             | Clock Enable Set-up Time           | 1.5      | _    | 1.5        | _    | ns   |      |