# SANYO Semiconductors DATA SHEET

An ON Semiconductor Company

# LC822973 — TV Image Viewer LSI

# **Overview**

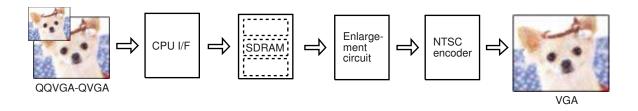

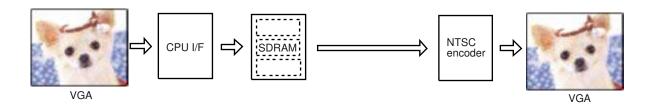

This LSI is TV image viewer. A 16Mbit SDRAM is built-in as image frame buffers, on which an external CPU is able to draw the images, then another part of this LSI displays the SDRAM images on TV in NTSC/PAL after video data encoding. This LSI equips H/V scaling circuit to scale up QVGA size image to VGA to display on the TV screen, for instance.

The main features of this LSI are specified as below.

#### **Features**

• NTSC/PAL video encoder is integrated.

Various format support

ITU-R601 (13.5MHz/NTSC&PAL) SQ (12.27MHz/NTSC, 14.75MHz/PAL)

NTSC-J, M/PAL-B, D, G, H, I/PAL-M, N

Various image adjustment

Y signal: brightness and contrast adjustment

C signal:U gain, V gain, HUE and Burst amplitude adjustment

Trap filter

Trap filters locate on the Y signal pass to reduce cross color interference. The trap strength is adjustable by register setup.

Built-in color bar

This is for system test and level adjustment.

10 bit DAC with  $75\Omega$  driver

A high accuracy video DAC of 10bit is built-in. Its DAC output is able to be connected to TV input or any image devices, thanks for its  $75\Omega$  driver built-in.

• It mounts 16Mbit SDRAM to store multiple VGA size images. Since it has the arbitration function built-in, the access timing from CPU for drawing can be used without any care of real-time access condition for TV display. VGA 30fps performance can be achieved with appropriate setting of system clock, the burst size of SDRAM, scaling ratio etc.

\* I<sup>2</sup>C Bus is a trademark of Philips Corporation.

Continued to the next page.

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment. The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for new introduction or other application different from current conditions on the usage of automotive device, communication device, office equipment, industrial equipment etc., please consult with us about usage condition (temperature, operation time etc.) prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

#### SANYO Semiconductor Co., Ltd.

Continued from the previous page.

- The OSD function is installed. OSD images consist of binary pixel data to display over the original image. The Alfa-blend display is also available.

- Scaling from ×1 up to ×4 in two independent directions, horizontally and vertically, is available.

256 step arbitrary enlargement is given by register settings. The image rotation is available when writing as well.

- The high-speed clock for SDRAM is generated internally by built-in PLL.

- CPU-IF with 8/9/16/18/24 bit width data transfer is available.

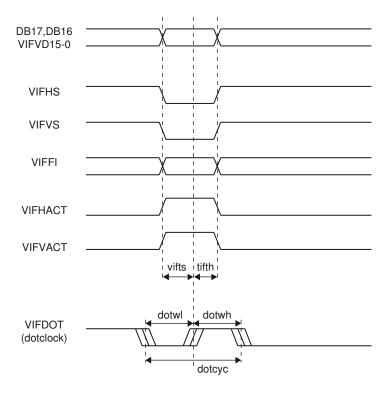

- Built-in VIDEO-IF supports receiving video rate image input with Hsync/Vsync/Dotclcok signals. It accepts various digital image formats of 18bit-RGB666, 16bit-RGB565, 16bit-YUV422, 8bit-YUV422, 8bit-YUV422 (BT656) and so on. In addition, it accepts both interlace and non-interlace format.

- The Autoview function executes automatic writing/reading sequence. Once all the relevant commands are set, then this function properly updates the image banks to write and to read. This bank arbitration avoids well the tearing image (reading outruns writing).

- The FilckerFreeFilter effectively decreases the line flicker, a substantial phenomena of the interlace method.

- High performance C-signal band-limit filter is built-in. The thorny 'dot crawl' is thus decreased.

- CGMS-A/WSS data multiple functions are built-in.

- The I/O voltage of the CPU/Video interface is 1.6V-3.4V.

- Macrovision<sup>TM</sup> Encoding (Revision 7.1.L1 in NTSC and PAL standards for Composite video output applications) are built-in. (LC822973-04VM-E only)\*

- \* This device is Protected by U.S. patents 5, 583, 936; 6, 516, 132; 6, 836, 549; and 7, 050, 698; and other intellectual property rights. The use of Macrovision's copy protection technology in the device must be authorized by Macrovision and is intended for home and other limited pay-per-view uses only, unless otherwise authorized in writing by Macrovision. Reverse engineering or disassembly is prohibited. This Device can only be sold or distributed to Authorized Buyers.

# DC characteristics/AC characteristics

Absolute Maximum Ratings at  $DV_{SS} = 0V$

| Parame                            | eter           | Symbol                               | Conditions     | Ratings                         | unit |

|-----------------------------------|----------------|--------------------------------------|----------------|---------------------------------|------|

| Supply voltage                    |                | DV <sub>DD</sub> 15 max              |                | -0.3 to 1.8                     | V    |

|                                   |                | DV <sub>DD</sub> IO max              |                | -0.3 to 3.96                    | V    |

| Input voltage                     |                | V <sub>I</sub> IO                    |                | -0.3 to 3.96 *1                 | V    |

| Output voltage                    |                | V <sub>O</sub> IO                    |                | -0.3 to DV <sub>DD</sub> IO+0.3 | V    |

| Operation surrounding temperature |                | Topg                                 |                | -30 to 85                       | °C   |

| Storage temperat                  | ture           | Tstg                                 |                | -55 to 125                      | °C   |

| Soldering temperature             | Hand soldering |                                      | For 3 seconds  | 350                             | °C   |

|                                   | Reflow         |                                      | For 10 seconds | 255                             | °C   |

| In/Out current                    | •              | I <sub>I</sub> 15, I <sub>O</sub> 15 |                | ±20 *2                          | mA   |

|                                   |                | I <sub>I</sub> IO, I <sub>O</sub> IO |                |                                 |      |

<sup>\*1</sup> Input voltage of I/O basic cell in case of without P-ch protection diode.

# **Permissible Operation Range** at Ta = -30 to 85°C, $DV_{SS} = 0V$

| Parameter      | Symbol                 | Conditions | min  | typ | max                 | unit |

|----------------|------------------------|------------|------|-----|---------------------|------|

| Supply voltage | DV <sub>DD</sub> 15    |            | 1.35 | 1.5 | 1.65                | V    |

|                | DV <sub>DD</sub> IO *3 |            | 2.5  | 3.0 | 3.4                 | V    |

|                | DV <sub>DD</sub> IO *4 |            | 1.6  | 1.8 | 2.0                 | V    |

|                | DV <sub>DD</sub> 3     |            | 2.7  | 3.0 | 3.4                 | V    |

|                | AV <sub>DD</sub> 3     |            | 2.7  | 3.0 | 3.4                 | V    |

|                | AV <sub>DD</sub> 15    |            | 1.35 | 1.5 | 1.65                | V    |

| Input range    | V <sub>IN</sub> IO     |            | 0    |     | DV <sub>DD</sub> IO | V    |

<sup>\*3</sup> at supply = 3.0V (Typical)

<sup>\*2</sup> per 1 cell of I/O basic cell

<sup>\*4</sup> at supply = 1.8V (Typical)

# I/O pin capacity at $V_{DD}3 = DV_{DD}IO = V_{I}15 = V_{I}IO = DV_{SS} = 0V$ , Ta = -30 to $85^{\circ}C$

| Parameter  | Symbol           | Conditions | min | typ | max | unit |

|------------|------------------|------------|-----|-----|-----|------|

| Input pin  | C <sub>IN</sub>  | f = 1MHz   |     |     | 10  | pF   |

| Output pin | C <sub>OUT</sub> |            |     |     | 10  | pF   |

| I/O pin    | C <sub>I/O</sub> |            |     |     | 10  | pF   |

#### **DC** characteristics

I/O level /  $V_{SS} = 0V$ ,  $DV_{DD}IO = 2.5$  to 3.4V,  $T_{a} = -30$  to  $85^{\circ}C$

| Parameter          |   | Symbol             | Conditions                   | Applied pin *5 | min                     | typ | max                    | unit |

|--------------------|---|--------------------|------------------------------|----------------|-------------------------|-----|------------------------|------|

| Input level        | Н | V <sub>IH</sub> IO | CMOS                         | (4) (0)        | 2.0                     |     |                        | ٧    |

|                    | L | V <sub>IL</sub> IO |                              | (1) (2)        |                         |     | 0.3DV <sub>DD</sub> IO | ٧    |

|                    | Н | V <sub>IH</sub> IO | CMOS schmit                  | (0)            | 2.0                     |     |                        | ٧    |

|                    | L | V <sub>IL</sub> IO |                              | (3)            |                         |     | 0.3DV <sub>DD</sub> IO | ٧    |

| Output level       | Н | V <sub>OH</sub> IO | I <sub>OH</sub> = -4mA       | (0) (4)        | DV <sub>DD</sub> IO-0.4 |     |                        | ٧    |

|                    | L | V <sub>OL</sub> IO | I <sub>OL</sub> = 4mA        | (2) (4)        |                         |     | 0.4                    | ٧    |

|                    | Н |                    |                              |                |                         |     |                        | ٧    |

|                    | L | V <sub>OL</sub> IO | I <sub>OL</sub> = 4mA        | (5)            |                         |     | 0.4                    | ٧    |

| Input leak current |   | կլ                 | $V_I = DV_{DD}3$ , $DV_{SS}$ | (1) (2) (3)    | -10                     |     | +10                    | μА   |

| Output leak curren | t | loz                | High impedance               | (4) (5)        | -10                     |     | +10                    | μΑ   |

<sup>\*5</sup> The applied pins correspond to the following names.

# I/O level / $V_{SS} = 0V$ , $DV_{DD}IO = 1.6$ to 2.0V, Ta = -30 to $85^{\circ}C$

| Parameter          |   | Symbol             | Conditions                   | Applied pin *6 | min                     | typ | max                     | unit |

|--------------------|---|--------------------|------------------------------|----------------|-------------------------|-----|-------------------------|------|

| Input level        | Н | V <sub>IH</sub> IO | CMOS                         | (4) (0)        | 0.7DV <sub>DD</sub> IO  |     |                         | V    |

|                    | L | V <sub>IL</sub> IO |                              | (1) (2)        |                         |     | 0.25DV <sub>DD</sub> IO | V    |

|                    | Н | V <sub>IH</sub> IO | CMOS schmit                  | (0)            | 0.75DV <sub>DD</sub> IO |     |                         | V    |

|                    | L | V <sub>IL</sub> IO |                              | (3)            |                         |     | 0.2DV <sub>DD</sub> IO  | V    |

| Output level       | Н | V <sub>OH</sub> IO | I <sub>OH</sub> = -4mA       | (0) (4)        | DV <sub>DD</sub> IO-0.4 |     |                         | V    |

|                    | L | V <sub>OL</sub> IO | I <sub>OL</sub> = 4mA        | (2) (4)        |                         |     | 0.4                     | V    |

|                    | Н |                    |                              | (5)            |                         |     |                         | V    |

|                    | L | V <sub>OL</sub> IO | I <sub>OL</sub> = 4mA        | (5)            |                         |     | 0.4                     | V    |

| Input leak current |   | կլ                 | $V_I = DV_{DD}3$ , $DV_{SS}$ | (1) (2) (3)    | -10                     |     | +10                     | μΑ   |

| Output leak curren | t | loz                | High impedance               | (4) (5)        | -10                     |     | +10                     | μΑ   |

<sup>\*6</sup> The applied pins correspond to the following names.

(INPUT)

(1) ... CKI, A0, CS, CONF3-CONF0, MODE2-MODE0

(2) ... D15-D0, DB17, DB16

(3) ... XRST, CS, RD, WR, SCL, SDA

(OUTPUT)

(2) ... D15-D0

(4) ... INT, MON

(5) ... SDA (Open Drain)

# **DAC** characteristics

The characteristics of DAC (10bitDAC) for video that features this LSI are illustrated.

Zero scale output voltage within 0V±15mV Full scale output voltage within 1.00V±80mV

Maximum conversion speed 30MHz

Linear line error within±4LSB (VQFN84 [-10B] : within±4.5LSB)

Differential linear line error within±1LSB Voltage reference level 1.20±20mV

$(Ta = +25^{\circ}C)$

# **Current consumption**

\*at the time of DVDD3 = DVDDIO = 3V and DVDD15 = 1.5V and AVDD3 = 3V and AVDD15 = 1.5V and MCLK50MHz

\* at the time of still picture (640×480) + OSD1 All screens + OSD2 All screens

| Parameter                                            | min | typ | max | unit |

|------------------------------------------------------|-----|-----|-----|------|

| AV <sub>DD</sub> 15 (PLL operation current)          |     | 0.5 | 1   | mA   |

| DV <sub>DD</sub> 15 (core operation current)         |     | 10  | 15  | mA   |

| AV <sub>DD</sub> 3 (DAC operation current)*          |     | 35  | 35  | mA   |

| DV <sub>DD</sub> IO (IO operation current)           |     | 2   | 5   | mA   |

| DV <sub>DD</sub> 3 (SDRAM operation current)         |     | 8   | 13  | mA   |

| Standby current (clock input on)                     |     |     | 300 | μΑ   |

| Standby current (input clock off)**                  |     |     | 100 | μΑ   |

| Standby current (input clock off + SDRAM/SRAM off)** |     | 6   | 18  | μΑ   |

<sup>\* &#</sup>x27;typ' here implies only that DACOUT always outputs its maximum current.

Standby current is at the condition of room temperature (+25°C)

<sup>\*\*</sup> Under the condition of tying input pin levels to H or L.

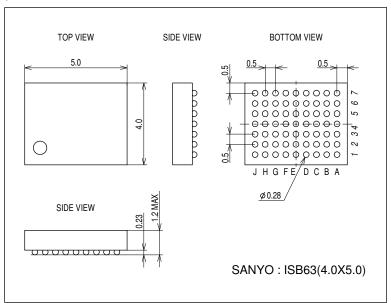

# **Package Dimensions**

unit: mm (typ)

3442

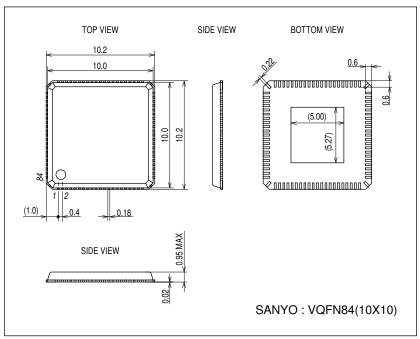

# **Package Dimensions**

unit: mm (typ)

3443

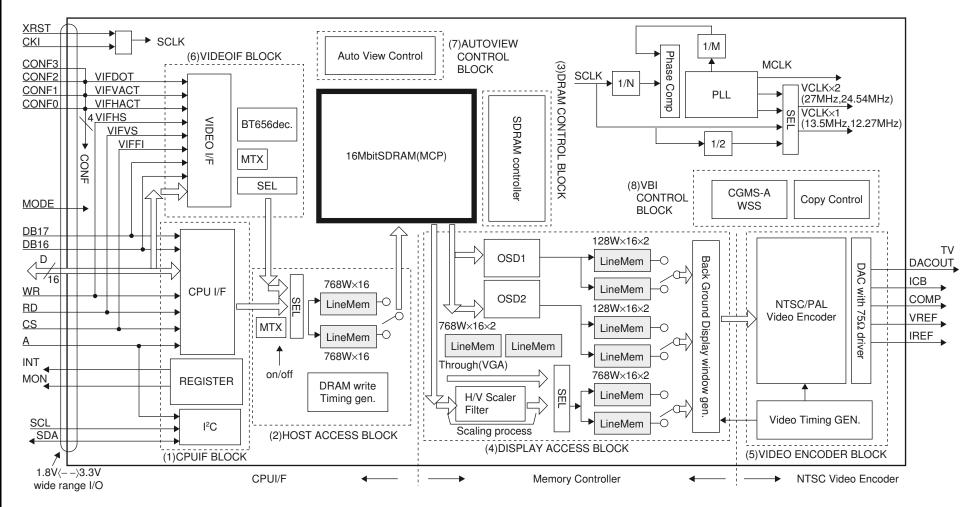

# Structure

# **Outline Specification**

| Item                   | Outline                                                                                                   |

|------------------------|-----------------------------------------------------------------------------------------------------------|

| NTSC/PAL video encoder | Multi rate and multi format video encoder that supports NTSC/PAL and ITU-601/SQ (square pixel).           |

| DAC                    | 10bit-1chD/A converter that integrates $7\Omega$ driver.                                                  |

|                        | Can be connected to TV directly without OP-amp or buffer.                                                 |

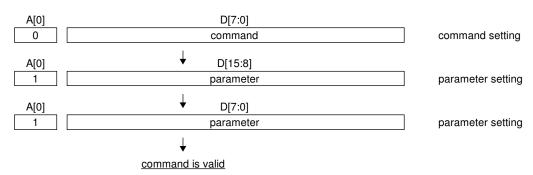

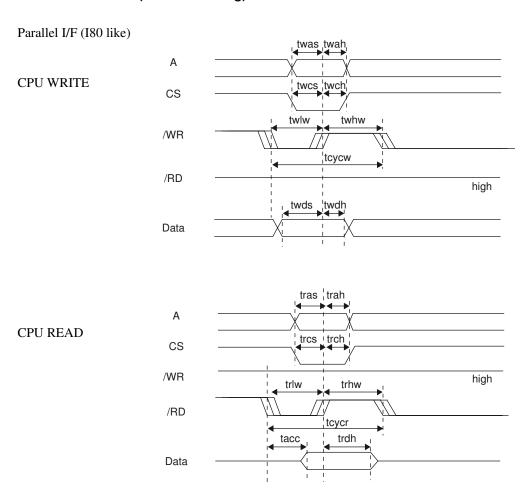

| CPU I/F                | Support 8/9/16/18/24bit bus (D, WR, RD, CS, A0) of I80 type.                                              |

| Video I/F              | It corresponds to 5 format of RGB565, RGB666, YUV422 (8bit), YUV422 (8bit_BT656mode), and YUV422          |

|                        | (16bit). The writing operation is executed based on Sync signals.                                         |

| Memory controller      | Controls built-in (MCP) 16MbitSDRAM. Owns arbitration function and CPU access (drawing) is possible       |

|                        | as needed.                                                                                                |

| Matrix (CPU I/F)       | Performs RGB $\rightarrow$ YUV conversion at the time of CPU $\rightarrow$ memory writing.                |

| Matrix (Video I/F)     | Performs RGB $\rightarrow$ YUV conversion at the time of video port $\rightarrow$ memory writing.         |

| PLL                    | Generates high-speed clock for SDRAM.                                                                     |

| OSD                    | A reading binary image from SDRAM is displayed in TV. Because the Alfa blend function is installed, it is |

|                        | possible to select four stages by blend register.                                                         |

| Scaling function       | ×4 scaling processing at maximum is executed for reading image from SDRAM.                                |

|                        | Can be set to H and V direction independently.                                                            |

| Autoview function      | The issue of the command of each screen is unnecessary. Writing/reading control in the image area (two    |

|                        | bank or3 bank) set beforehand is executed automatically.                                                  |

| V-blanking period.     | Can insert CGMS-A/WSS code into V-blanking period.                                                        |

| I/O                    | CMOS interface                                                                                            |

| Operation temperature  | -30°C to 85°C                                                                                             |

| Package                | ISB63 4mm×5mm                                                                                             |

|                        | VQFN84 10mm × 10mm                                                                                        |

| Power voltage (IO)     | DV <sub>DD</sub> IO (1.6V - 3.4V)                                                                         |

|                        | for ex. : 1.8V (1.6V - 2.0V), 3.0V (2.5V - 3.4V)                                                          |

| Power voltage          | 1.5V (1.35V - 1.65V)                                                                                      |

| (digital core)         |                                                                                                           |

| Power voltage (PLL)    | 1.5V (1.35V - 1.65V)                                                                                      |

| Power voltage          | 3.0V (2.7V - 3.4V)                                                                                        |

| (for stacked SDRAM)    |                                                                                                           |

| Power voltage          | 3.0V (2.7V - 3.4V)                                                                                        |

| (DAC analog part)      |                                                                                                           |

This LSI consists of 9 function blocks in the structure block above.

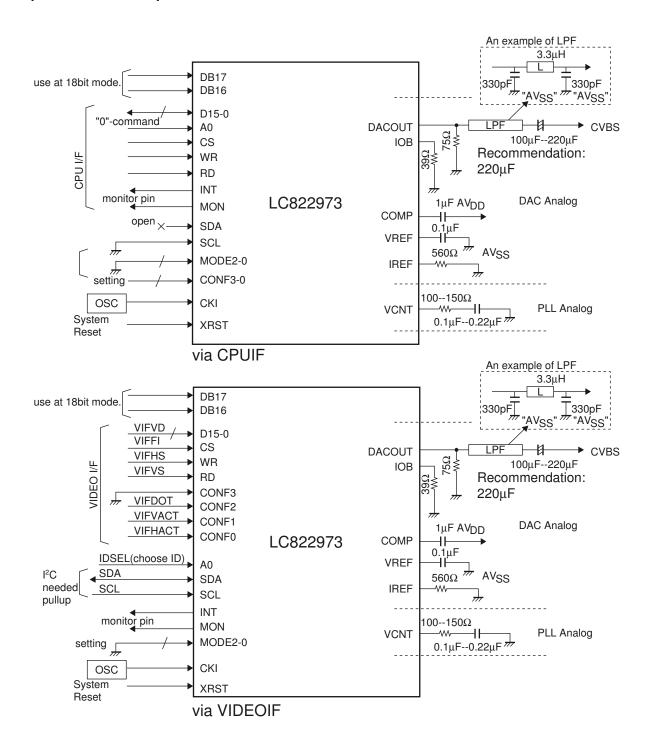

#### (1) CPU interface (CPUIF BLOCK)

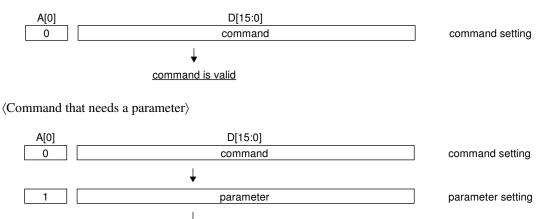

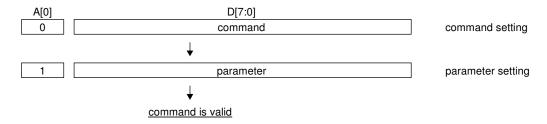

The parameter setup such as mode setup/image area setup/video encoder characteristic of this LSI is possible via bus from CPU. The image data writing to SDRAM achieves image port writing command that is in the same command class as regular register and the same command class and keep writing continuously. This is a double bank buffer structure and is able to write drawing data for 1 line without WAIT control.

#### (2) Host access (HOST ACCESS BLOCK)

The image writing is fulfilled from CPU interface for SDRAM.

This obtains line buffer in double bank buffer and the writing is carried out to SDRAM as accessing from CPU. It also mounts 90, 180, 270 degrees rotation writing and writing function with matrix conversion processing besides regular writing.

#### (3) SDRAM control (DRAM CONTROL BLOCK)

This LSI is MCP (multi chip) structure and has 16Mbit SDRAM built-in. This is the memory controller that controls writing from CPU, reading for real-time display to video encoder and refresh processing for this memory.

#### (4) Reading control for display (DISPLAY ACCESS BLOCK)

This is the SDRAM reading processing part that controls transferring real-time image data to NTSC/PAL video encoder.

This consists of scaling part that performs enlargement processing for image data that was read from SDRAM and the buffer controlling part that provides video signal continuously to video encoder. The background processing circuit that inserts fixed level is mounted in the buffer control part besides display window (image from SDRAM).

#### (5) Video encoder (VIDEO ENCODER BLOCK)

This supports both NTSC/PAL methods. All timing signals that are necessary for video signal are generated in this block. This operates as a sync master and generates transfer request of real-time image data for DISPLAY ACCESS BLOCK.

#### (6) Video interface (VIDEOIF BLOCK)

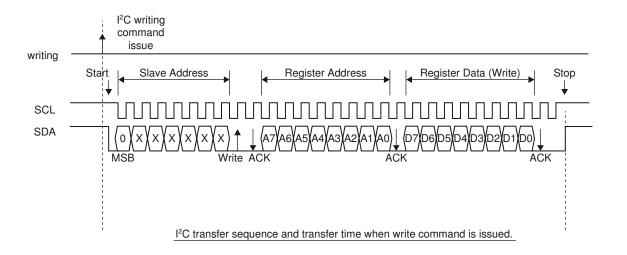

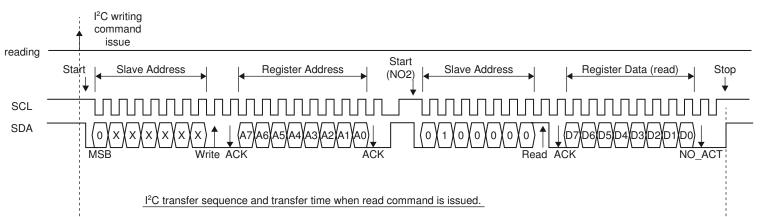

It is an interface part for the video rate writing. It writes based on a video sync signal and the dot clock. In case of RGB format (RGB565, RGB666 etc.), the image is input to the host access part by processing the matrix at valid period. The BT656 decoding is done if necessary at the YUV format. it supports both non-interlace and interlace format. When the video interface is used, the data bus (D15 - D0) is treated as a dedicated image bus. The command issue and the register access are executed with the I<sup>2</sup>C bus. It has the I<sup>2</sup>C bus control part in CPU interface part.

# (7) Automatic image viewing (AUTOVIEW CONTROL BLOCK)

Automatic writing/reading sequence is executed by alternating the pre-defined image banks. Thus clean images without the scan passing (tearing image) are displayed. Consecutive image data transfer follows after one time command and parameter setting.

# (8) VBI control (VBI CONTROL BLOCK)

The CGMS-A/WSS data is inserted. It has AUX function for the copy protect control etc.

#### (9) Others

To combine drawing from CPU and real-time request (continuous video signal is provided to NTSC/PAL video encoder), SDRAM needs to be operated with high-speed clock. The high-speed master clock (MCLK) is created and supported by using PLL for input clock (CKI).

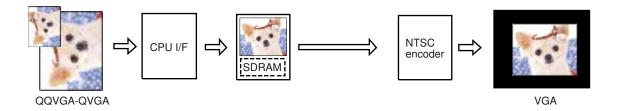

# **General Operation**

#### [Operation 1.]

The rotation processing is performed at the time of SDRAM writing. As a result, a vertically long image of small size such as QQVGA, QVGA, etc. is rotated 90 degrees and it is possible to display on TV (VGA size image).

# [Operation 2.]

The enlargement processing can be realized by filter processing that utilized line memory for reading data from SDRAM. The small size image such as QQVGA and QVGA can be displayed on TV screen fully (VGA size). An enlargement ratio can be set optionally  $(2\times(n+1)/256, n: 128 \text{ to } 255)$ . If the displayed image after enlargement is smaller than VGA size, other than target image can be set to background level (brightness/color setup possible). This operation can be combined with the above rotation function.

#### [Operation 3.]

The enlargement processing can be bypassed if writing image size from CPU fits VGA image size exactly. Degradation of broad area level due to filter processing can be prevented.

# [Moving image processing]

This LSI is the system that supports moving image that made writing from CPU and competitive operation of TV display (real-time reading from SDRAM) possible by using high-speed clock operation.

The moving image performance (supportable frame rate) improves by raising SDRAM clock frequency through PLL setup. However, the current consumption increases significantly.

# **Corresponding video format**

The video format that NTSC/PAL video encoder corresponds is described in the following tables.

# ((NTSC))

| Mode                     | ITU-601                                  | SQ         |  |

|--------------------------|------------------------------------------|------------|--|

| Dot clock                | 13.500MHz                                | 12.2727MHz |  |

| Dot/line                 | 858                                      | 780        |  |

| Horizontal valid period  | 720                                      | 640        |  |

| Vertical cycle           | 525 lines/frames                         |            |  |

| Vertical frequency       | 59.94Hz (field)                          |            |  |

| Vertical blanking period | 21 lines (line1-line21, line263-line284) |            |  |

| Burst mask period        | 9 lines (line1-line9, line264-line272)   |            |  |

# ((PAL))

| Mode                     | ITU-601                                    | SQ        |  |

|--------------------------|--------------------------------------------|-----------|--|

| Dot clock                | 13.500MHz                                  | 14.750MHz |  |

| Dot/ line                | 864                                        | 944       |  |

| Horizontal valid period  | 720                                        | 768       |  |

| Vertical cycle           | 625 lines/frames                           |           |  |

| Vertical frequency       | (field)                                    |           |  |

| Vertical blanking period | 25 lines (line623-line22, line311-line335) |           |  |

| Burst mask period        | 9 lines (line623-line6, line310-line318)   |           |  |

<sup>\*</sup>The video encoder is the component signal processing for Y and C of 8 bit each as an internal processing. The dot clock in the table above corresponds to the sampling clock at the time of 16bit processing of Y+C. To simplify post filter, the video encoder processing performs ×2 oversampling. Therefore, the operation clock in video encoder part is double of dot clock (27MHz, 24.54MHz, 29.5MHz, etc.).

# **Pin Description**

analog DAC

analog PLL

| Pin name             | Pol. | Dir | Description of function                                                      | at<br>reset    | Pin     |

|----------------------|------|-----|------------------------------------------------------------------------------|----------------|---------|

| CKI                  | -    | I   | Master clock                                                                 | Master clock - |         |

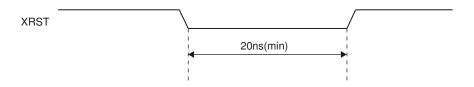

| XRST                 | L    | I   | Master reset, Low active                                                     | -              | 1       |

| DB17                 | -    | I   | (bit17) extended bit. use at 18bit mode.                                     | -              | 1       |

| DB16                 | -    | I   | (bit16) extended bit. use at 18bit mode                                      | -              | 1       |

| D[15:0]/             |      |     | Data bus, needs pull-up resistance externally                                |                |         |

| VIFVD[15:0]          | -    | I/O | (unnecessary if either device always drives bus).                            | -              | 16      |

|                      |      |     | This bus is sharing for the VIDEOIF.                                         |                |         |

| A0/ (IDSEL)          | -    | I   | Address/ (IDSEL at VIDEOIF).                                                 | -              | 1       |

| RD/ (VIFVS)          | L    | ı   | Read pulse/ (Vsync in at VIDEOIF).                                           |                | 1       |

| WR/ (VIFHS)          | L    | ı   | Write pulse/ (Hsync in at VIDEOIF).                                          | -              | 1       |

| CS/ (VIFFI)          | L    | I   | Chip select/ (Field index in at VIDEOIF).                                    | -              | 1       |

| INT                  | L    | 0   | Interrupt                                                                    | "0"            | 1       |

| MON                  | Н    | 0   | Monitor                                                                      | "0"            | 1       |

| USEVIF               | Н    | ı   | Set "H" in case of VIDEOIF mode.                                             | -              | 1       |

| 00.4                 |      | 1/0 | The command issue is via I <sup>2</sup> C bus.                               |                |         |

| SDA                  | -    | I/O | SDA for I <sup>2</sup> C bus.                                                | -              | 1       |

| SCL                  | -    | I   | SCL for I <sup>2</sup> C bus.                                                |                | 1       |

| DACOUT               | Ana  | 0   | DAC output -                                                                 |                | 1       |

| IOB                  | Ana  | 0   | DAC_IOB pin -                                                                |                | 1       |

| COMP                 | Ana  | 0   | DAC_COMP pin                                                                 | -              | 1       |

| VREF                 | Ana  | 0   | DAC_VREF pin                                                                 | -              | 1       |

| IREF                 | Ana  | 0   | DAC_IREF pin                                                                 | -              | 1       |

| VCNT                 | Ana  | I   | VCNT pin                                                                     | -              | 1       |

| MODE[2:0]            | -    | I   | For test *                                                                   | -              | 3       |

| CONF3                | -    | I   | To decide input format                                                       | -              | 1       |

| CONF2                | -    | ı   | To decide input format                                                       | -              | 1       |

| / (VIFDOT)           |      |     | / (Dotclock in at VIDEOIF)                                                   |                |         |

| CONF1<br>/ (VIFVACT) | -    | I   | To decide input format / (V-valid period flag in at VIDEOIF)                 | -              | 1       |

| CONF0                |      |     | To decide input format                                                       |                |         |

| / (VIFHACT)          | -    | I   | / (H-valid period flag in at VIDEOIF)                                        | -              | 1       |

| DV <sub>DD</sub> 15  | Pow  | -   | DV <sub>DD</sub> for digital core (1.5V part)                                | -              | 4 (6)   |

| DV <sub>DD</sub> IO  | Pow  | -   | DV <sub>DD</sub> for digital I/O part                                        | -              | 4 (7)   |

| DV <sub>DD</sub> 3   | Pow  | -   | DV <sub>DD</sub> for stacked SDRAM (it's controlled by internal switch cell) |                | 3 (4)   |

| AV <sub>DD</sub> 3   | Pow  | -   | AV <sub>DD</sub> for DAC analog (analog 3V)                                  | -              | 1       |

| AV <sub>DD</sub> 15  | Pow  | -   | AV <sub>DD</sub> for PLL analog (analog 1.5V)                                | -              | 1       |

| DV <sub>SS</sub>     | Pow  | -   | GND for digital part                                                         | -              | 6 (13)  |

| AVSS                 | Pow  | -   | GND for analog part                                                          | -              | 2       |

|                      |      |     | Total                                                                        |                | 63 (76) |

<sup>\*</sup> MODE pins are for testing.

They should be fixed to "L" normally.

# Pin assignment (ISB63/VQFN84/[SQFP100])

| 1 NC 2 NC 2 NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | cPUIF mode.  t3). connect to GND at  t2) t1). de. t0). de. eration) |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| H5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | cPUIF mode.  t3). connect to GND at  t2) t1). de. t0). de. eration) |

| G6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | cPUIF mode.  t3). connect to GND at  t2) t1). de. t0). de. eration) |

| H7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | cPUIF mode.  t3). connect to GND at  t2) t1). de. t0). de. eration) |

| F4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t3). connect to GND at t2) t1). de. t0). de. eration)               |

| F6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | t2) t1). de. t0). de. eration)                                      |

| VIDEOIF mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | t2) t1). de. t0). de. eration)                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . t1). de. t0). de. eration)                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | de. tt0). de. eration)                                              |

| H-valid flag in at VIDEOIF mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | de.                                                                 |

| H5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     |

| E7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     |

| E7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     |

| E4       13       15       XRST       I       System reset ("L"==reset)         D7       14       16       INT       O       INT signal ("L"==interrupt gene         E5       15       17       MON       O       Monitor pin.         H5       16       18       DVSS       P       Digital GND         C7       17       19       A0/ (IDSEL)       I       Address/ID address select at V (0 : 8'b0100_000_r, 1 : 8'b010         D6       18       20       CS/ (VIFFI)       I       /CS signal/field index at VIDEO         B7       19       21       DVDD15       P       VDD (digital core)         H5       20       22       DVSS       P       Digital GND         -       -       23       NC       -         -       -       I       I       -         -       -       27       NC       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |

| D7         14         16         INT         O         INT signal ("L"==interrupt gene           E5         15         17         MON         O         Monitor pin.           H5         16         18         DVSS         P         Digital GND           C7         17         19         A0/ (IDSEL)         I         Address/ID address select at V (0 : 8'b0100_000_r, 1 : 8'b010           D6         18         20         CS/ (VIFFI)         I         /CS signal/field index at VIDEO           B7         19         21         DVDD15         P         VDD (digital core)           H5         20         22         DVSS         P         Digital GND           -         -         23         NC         -           -         -         1         -           -         -         27         NC         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                     |

| E5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     |

| H5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IDEOIF mode.                                                        |

| C7         17         19         A0/ (IDSEL)         I         Address/ID address select at V (0 : 8'b0100_000_r, 1 : 8'b010           D6         18         20         CS/ (VIFFI)         I         /CS signal/field index at VIDEO           B7         19         21         DVDD15         P         VDD (digital core)           H5         20         22         DVSS         P         Digital GND           -         -         23         NC         -           -         -         I         -           -         -         I         -           -         -         27         NC         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IDEOIF mode.                                                        |

| C7         17         19         A0/ (IDSEL)         I         Address/ID address select at V (0 : 8'b0100_000_r, 1 | IDEOIF mode.                                                        |

| D6         18         20         CS/ (VIFFI)         I         /CS signal/field index at VIDEO           B7         19         21         DV <sub>DD</sub> 15         P         V <sub>DD</sub> (digital core)           H5         20         22         DV <sub>SS</sub> P         Digital GND           -         -         -         -         -           -         -         I         I         -           -         -         -         I         -         -           -         -         -         I         -         -           -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                     |

| H5         20         22         DV <sub>SS</sub> P         Digital GND           -         -         -         -         -           -         -                   -         -           -         -                   -         -           -         -         27         NC         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                     |

| 23 NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |