# SANYO Semiconductors

DATA SHEET

An ON Semiconductor Company

# LC74763 LC74763M

On-Screen Display LSI

# Overview

The LC74763 and LC74763M are on-screen display CMOS LSIs that superimpose text and low-level graphics onto a TV screen (video signal) under the control of a microcontroller. The display characters have a 12 by 18 dots structure, and 128 characters are provided.

# Features

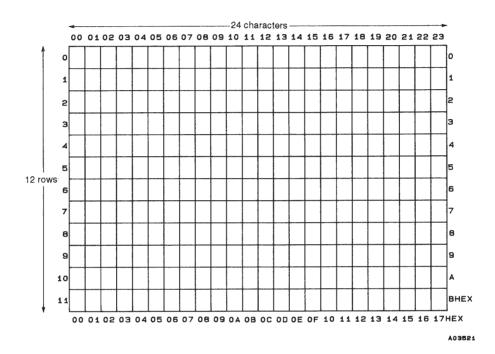

- Display structure: 12 lines by 24 characters (up to 288 characters)

- Maximum character display: Up to 288 characters

- Character configuration: 12 (W) by 18 (H) dots structure

- Number of characters: 128 characters (128 plus space 2 fonts)

- Character sizes: Three sizes (normal, double, and triple sizes)

- Display starting positions: 64 horizontal and 64 vertical locations

- Reverse video function: Characters can be inverted on a per character basis.

- Flashing types: Two types with periods of 0.5 and 1.0 second on a per character basis (duty fixed at 50%)

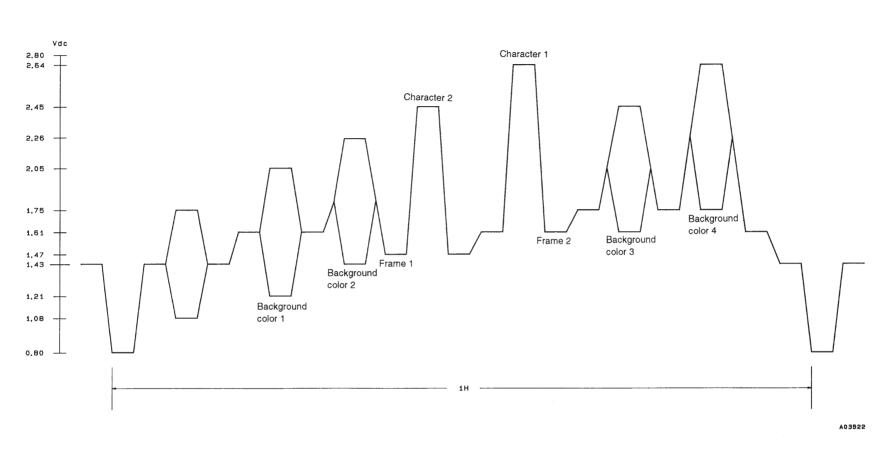

- Background color: One of eight colors (when internal synchronization used)

- External control input: Serial data input in 8-bit units

- · Built-in horizontal/vertical sync separation circuit, AFC circuit, and synchronization detector

- Video output: Composite video signal output in NTSC, PAL, PAL-M, PAL-N, PAL60, NTSC4.43, or SECAM format

Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment. The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for new introduction or other application different from current conditions on the usage of automotive device, communication device, office equipment, industrial equipment etc. , please consult with us about usage condition (temperature, operation time etc.) prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

> SANYO Semiconductor Co., Ltd. http://semicon.sanyo.com/en/network

# Specifications Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol               | Conditions                                                                | Ratings                                        | Unit |

|-----------------------------|----------------------|---------------------------------------------------------------------------|------------------------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max  | V <sub>DD1</sub> , V <sub>DD2</sub> pins                                  | V <sub>SS</sub> – 0.3 to V <sub>SS</sub> + 7.0 | V    |

| Maximum input voltage       | V <sub>IN</sub> max  | All input pins                                                            | V <sub>SS</sub> – 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Maximum output voltage      | V <sub>OUT</sub> max | HSYNC <sub>OUT</sub> , VSYNC <sub>OUT</sub> ,<br>SYNC <sub>DET</sub> pins | V <sub>SS</sub> – 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Allowable power dissipation | Pd max               |                                                                           | 300                                            | mW   |

| Operating temperature       | Topr                 |                                                                           | -30 to +70                                     | C    |

| Storage temperature         | Tstg                 |                                                                           | -40 to +125                                    | C    |

# Allowable Operating Ranges at Ta = -30 to $+70^{\circ}C$

| Deveryorten                          | Oursels al        | Que dition o                                                       |                       |                       | Ratings              |                        | Linit |  |

|--------------------------------------|-------------------|--------------------------------------------------------------------|-----------------------|-----------------------|----------------------|------------------------|-------|--|

| Parameter                            | Symbol            | Conditions                                                         | Conditions            |                       |                      | max                    | Unit  |  |

| Supply voltage                       | V <sub>DD1</sub>  | V <sub>DD1</sub> pin                                               |                       | 4.5                   | 5.0                  | 5.5                    | V     |  |

| Supply voltage                       | V <sub>DD2</sub>  | V <sub>DD2</sub> pin                                               |                       | 4.5                   | 5.0                  | 1.27 V <sub>DD1</sub>  | V     |  |

|                                      | V <sub>IH1</sub>  | RST, CS, SIN, SCLK pins                                            |                       | 0.8 V <sub>DD1</sub>  |                      | V <sub>DD1</sub> + 0.3 | V     |  |

| Input high level voltage             | $V_{\text{IH2}}$  | SECAM, 525/625,<br>NTSC/PAL, 3.58/4.43 pins                        |                       |                       |                      | V <sub>DD1</sub> + 0.3 | V     |  |

|                                      | V <sub>IL1</sub>  | RST, CS, SIN, SCLK                                                 |                       | V <sub>SS</sub> - 0.3 |                      | 0.2 V <sub>DD1</sub>   | V     |  |

| Input low level voltage              | V <sub>IL2</sub>  | SECAM, 525/625,<br>NTSC/PAL, 3.58/4.43 pins                        | V <sub>SS</sub> – 0.3 |                       | 0.3 V <sub>DD1</sub> | V                      |       |  |

| Input voltage                        | V <sub>IN</sub>   | FC, AMP <sub>IN</sub> pins                                         |                       | V <sub>SS</sub> - 0.3 |                      | V <sub>DD1</sub> + 0.3 | V     |  |

|                                      | V <sub>IN1</sub>  | CVIN pins                                                          |                       |                       | 2 V <sub>PP</sub>    |                        | V     |  |

| Composite video signal input voltage | V <sub>IN2</sub>  | CV <sub>CR</sub> pins                                              |                       |                       | 2 V <sub>PP</sub>    |                        | V     |  |

|                                      | V <sub>IN3</sub>  | SYNC <sub>IN</sub> pins                                            |                       |                       | 2 V <sub>PP</sub>    | 2.5 V <sub>PP</sub>    | V     |  |

|                                      |                   |                                                                    | NTSC                  |                       | 14.318               |                        | MHz   |  |

| Oscillator frequency                 | Fass              | Xtal <sub>IN1</sub> , Xtal <sub>OUT1</sub> , Xtal <sub>IN2</sub> , | PAL                   |                       | 17.734               |                        | MHz   |  |

|                                      | F <sub>OSC1</sub> | Xtal <sub>OUT2</sub> pins; 4fsc                                    | PAL-M                 |                       | 14.302               |                        | MHz   |  |

|                                      |                   |                                                                    | PAL-N                 |                       | 14.328               |                        | MHz   |  |

# Electrical Characteristics at Ta = -30 to $+70^{\circ}$ C, with $V_{DD1} = V_{DD2} = 5$ V unless otherwise specified

| Parameter                     | Symbol             | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | Ratings |     | Unit |

|-------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|------|

| Falameter                     | Symbol             | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | min | typ     | max | Unit |

| Output off leakage current    | I <sub>leak1</sub> | CV <sub>OUT</sub> pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |         | 10  | μA   |

| Input off leakage current     | I <sub>leak2</sub> | CV <sub>IN</sub> , CV <sub>CR</sub> pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |         | 10  | μA   |

| Output high level voltage     | V <sub>OH</sub>    | $\begin{array}{l} HSYNC_{OUT},  VSYNC_{\underline{OUT}}, \\ \underline{SYNC}_{DET},  \underline{SECAM},  \underline{525}/625, \\ \overline{NTSC}/PAL,  \underline{3.58}/4.43,  AMP_{OUT}, \\ PD_{OUT}  pins;  V_{DD1} = 4.5   V,  I_{OH} = -1.0   mA \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3.5 |         |     | V    |

| Output low level voltage      | V <sub>OL</sub>    | $\begin{array}{l} \mbox{HSYNC}_{OUT}, \mbox{VSYNC}_{OUT}, \\ \mbox{SYNC}_{DET}, \mbox{SECAM}, \mbox{525}/625, \\ \mbox{NTSC}/PAL, \mbox{3.58}/4.43, \mbox{AMP}_{OUT}, \\ \mbox{PD}_{OUT} \mbox{pins}; \mbox{V}_{DD1} = 4.5 \mbox{ V}, \mbox{I}_{OL} = 1.0 \mbox{ mA} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |         | 1.0 | V    |

| Input current                 | IIH                | $eq:rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_rescaled_$ |     |         | 1   | μA   |

| input current                 | IIL                | $\frac{\text{SECAM, }\overline{525}/625, \overline{\text{NTSC}}/\text{PAL},}{\overline{3.58}/4.43 \text{ pin}; \text{V}_{\text{IN}} = \text{V}_{\text{SS1}}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -1  |         |     | μΑ   |

| Oscillator frequency          | F <sub>OSC3</sub>  | $VCO_{IN}$ , $VCO_{OUT}$ pins; $FC = 1/2 V_{DD1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 14.12   |     | MHz  |

| Operating current dissipation | I <sub>DD1</sub>   | V <sub>DD1</sub> pin; All outputs open, Xtal: 4fsc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |         | 15  | mA   |

|                               | I <sub>DD2</sub>   | $V_{DD2}$ pin; $V_{DD2}$ = 5.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |         | 20  | mA   |

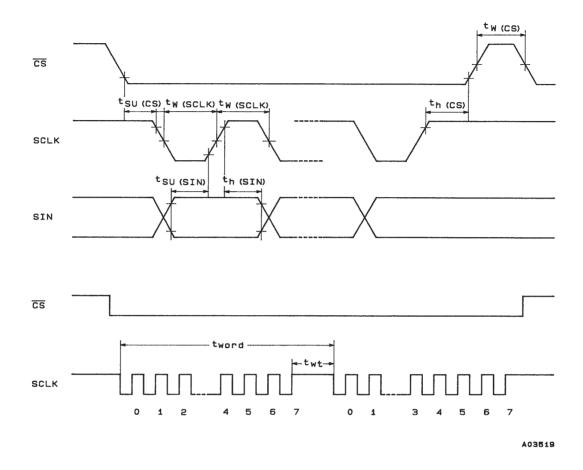

# Timing Characteristics at Ta = –30 to +70°C, $V_{DD}$ = 5 $\pm 0.5~V$

| Parameter                 | Cumhal               | Conditions                                                                      |     | Unit |     |      |  |

|---------------------------|----------------------|---------------------------------------------------------------------------------|-----|------|-----|------|--|

| Parameter                 | Symbol               | Symbol Conditions                                                               |     | typ  | max | Unit |  |

| Minimum input pulse width | t <sub>W(SCLK)</sub> | SCLK pin                                                                        | 200 |      |     | ns   |  |

|                           | t <sub>W(CS)</sub>   | $\overline{\text{CS}}$ pin (during periods when $\overline{\text{CS}}$ is high) | 1   |      |     | μs   |  |

| Data setup time           | t <sub>SU(CS)</sub>  | CS pin                                                                          | 200 |      |     | ns   |  |

|                           | t <sub>SU(SIN)</sub> | SIN pin                                                                         | 200 |      |     | ns   |  |

| Data hold time            | t <sub>h(CS)</sub>   | CS pin                                                                          | 2   |      |     | μs   |  |

|                           | t <sub>h(SIN)</sub>  | SIN pin                                                                         | 200 |      |     | ns   |  |

| One word write time       | tword                | Write time for 8 bits of data                                                   | 4.2 |      |     | μs   |  |

|                           | t <sub>wt</sub>      | RAM data write time                                                             | 1   |      |     | μs   |  |

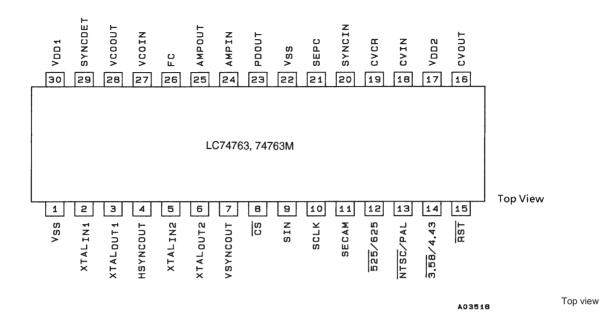

# **Pin Functions**

| Pin No.  | Symbol               | Function                                            | Description                                                                                                                                                                                                      |

|----------|----------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | V <sub>SS</sub>      | Ground                                              | Ground connection                                                                                                                                                                                                |

| 2        | Xtal <sub>IN1</sub>  | Crystal oscillator connection                       | Connection for the crystal and capacitor used to form the crystal oscillator that generates                                                                                                                      |

| 3        | Xtal <sub>OUT1</sub> |                                                     | the internal synchronization signal. The oscillator can be selected with a command switch.                                                                                                                       |

| 4        | HSYNCOUT             | Horizontal synchronization output                   | Outputs the horizontal synchronization signal (AFC). The output polarity can be selected (metal option). Also functions as general output port (command switch).                                                 |

| 5        | Xtal <sub>IN2</sub>  | Crystal oscillator connection                       | Connection for the crystal and capacitor used to form the crystal oscillator that generates                                                                                                                      |

| 6        | Xtal <sub>OUT2</sub> |                                                     | the internal synchronization signal.                                                                                                                                                                             |

| 7        | VSYNC <sub>OUT</sub> | Vertical synchronization output                     | Outputs the vertical synchronization signal. The output polarity can be selected (metal option). Also functions as general output port (command switch).                                                         |

| 8        | CS                   | Enable input                                        | Enables/disables serial data input. Serial data is enabled when this pin is low (hysteresis input). Pull-up resistor built in (metal option).                                                                    |

| 9        | SIN                  | Data input                                          | Serial data input (hysteresis input). Pull-up resistor built in (metal option).                                                                                                                                  |

| 10       | SCLK                 | Clock input                                         | Clock input for serial data input (hysteresis input). Pull-up resistor built in (metal option).                                                                                                                  |

| 11       | SECAM                | SECAM mode switch input/<br>output (command switch) | During input, switches between SECAM and other modes.<br>During output, functions as general output port or internal V output (command switch).<br>Low = other modes, high = SECAM mode                          |

| 12       | 525/625              | 525/625 switch input/output<br>(command switch)     | During input, switches between 525 scan lines and 625 scan lines.<br>During output, functions as general output port or character data output (command switch).<br>Low = 525 lines, high = 625 lines             |

| 13       | NTSC/PAL             | NTSC/PAL switch input/output<br>(command switch)    | Switches the color mode between NTSC and PAL.<br>During output, functions as general output port or frame data output (command switch).<br>Low = NTSC, high = PAL                                                |

| 14       | 3.58/4.43            | 3.58/4.43 switch input/output<br>(command switch)   | Switch FSC between 3.58 MHz and 4.43 MHz.<br>During output, functions as general output port or halftone output (command switch).<br>Low = 3.58, high = 4.43                                                     |

| 15       | RST                  | Reset input                                         | System reset input pin, low is active (hysteresis input).<br>Pull-up resistor built in (metal option).                                                                                                           |

| 16       | CV <sub>OUT</sub>    | Video signal output                                 | Composite video output                                                                                                                                                                                           |

| 17       | V <sub>DD2</sub>     | Power supply connection                             | Power supply connection for composite video signal level generation                                                                                                                                              |

| 18       | CVIN                 | Video signal input                                  | Composite video input                                                                                                                                                                                            |

| 19       | CV <sub>CR</sub>     | Video signal input                                  | SECAM chroma signal input                                                                                                                                                                                        |

| 20       | SYNCIN               | Sync separator circuit input                        | Built-in sync separator circuit video signal input                                                                                                                                                               |

| 21       | SEPC                 | Sync separator circuit                              | Built-in sync separator circuit                                                                                                                                                                                  |

| 22       | V <sub>SS</sub>      | Ground                                              | Ground connection                                                                                                                                                                                                |

| 23       | PD <sub>OUT</sub>    | Control voltage output                              | AFC control voltage output                                                                                                                                                                                       |

| 24       | AMP <sub>IN</sub>    | AFC filter connection                               | Filter connection                                                                                                                                                                                                |

| 25       | AMPOUT               |                                                     |                                                                                                                                                                                                                  |

| 26       | FC                   | Control voltage input                               | AFC control voltage input                                                                                                                                                                                        |

| 27<br>28 | VCO <sub>IN</sub>    | LC oscillator connection                            | VCO LC oscillator circuit coil and capacitor connection                                                                                                                                                          |

| 28       | VCO <sub>OUT</sub>   |                                                     | Outputs the evolution NOD of the horizontal are characterized in a local (AEO) and OO(ALO (                                                                                                                      |

| 29       | SYNC <sub>DET</sub>  | External synchronization signal detection output    | Outputs the exclusive NOR of the horizontal synchronization signal (AFC) and CSYNC (sync separator). The output polarity can be selected (metal option). Also functions as general output port (command switch). |

| 30       | V <sub>DD1</sub>     | Power supply connection                             | Power supply connection (+5 V: digital system power supply)                                                                                                                                                      |

# **Serial Data Input Timing**

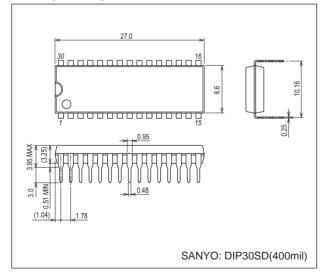

# **Package Dimensions**

unit : mm (typ) 3196A [LC74763]

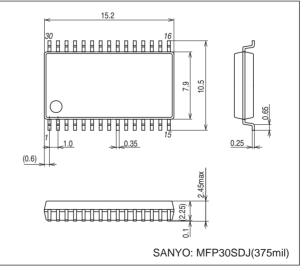

# **Package Dimensions**

unit : mm (typ) 3312 [LC74763M]

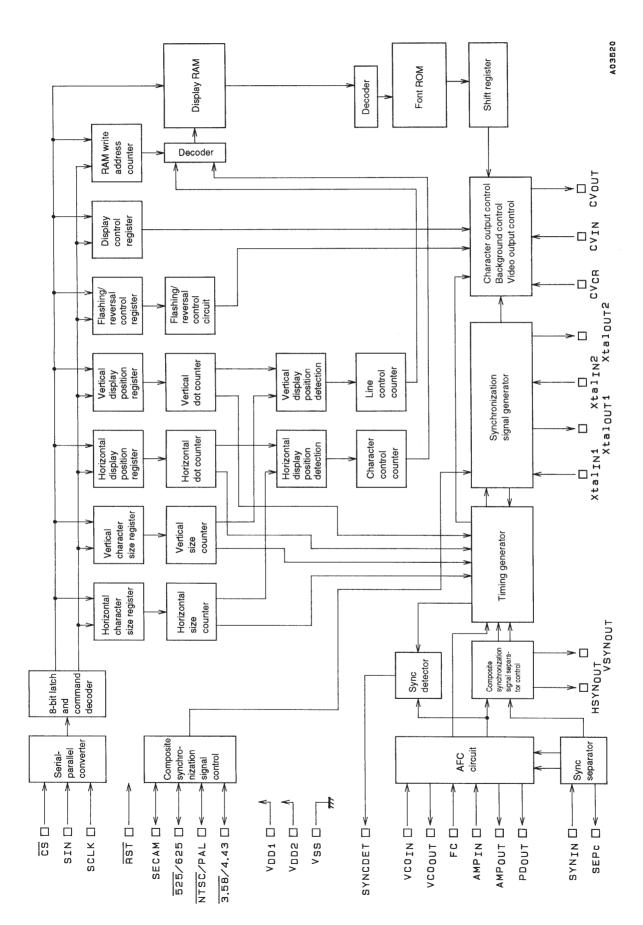

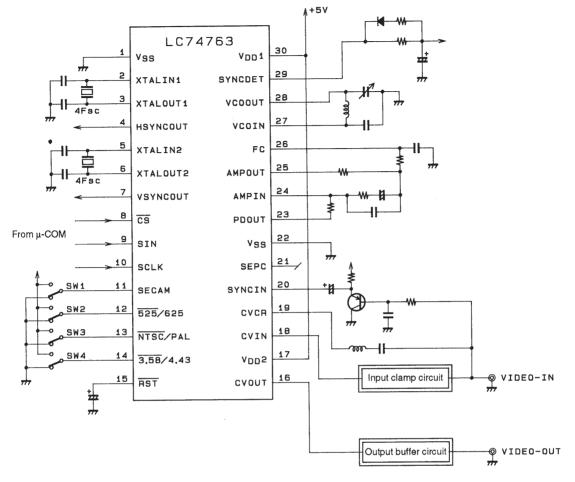

# System Block Diagram

# **Display Control Commands**

Display control commands are input in an 8-bit serial format. Commands consist of a command identification code in the first byte and data in the second and following bytes. The following commands are supported.

- ① COMMAND0: Display memory (VRAM) write address setting command

- 2 COMMAND1: Display character data write command

- ③ COMMAND2: Vertical display start position and character size (lines 1 and 2) setting command

- (4) COMMAND3: Horizontal display start position and character size (lines 9 and 11) setting command

- ⑤ COMMAND4: Display control setting command 1

- © COMMAND5: Display control setting command 2

- ⑦ COMMAND6: Display control setting command 3

- COMMAND7: Display control setting command 4

# **Display Control Command Table**

|                                               |      |          |            | First   | byte     |          |          |          |    |           |          | Secor    | nd byte   |          |          |          |

|-----------------------------------------------|------|----------|------------|---------|----------|----------|----------|----------|----|-----------|----------|----------|-----------|----------|----------|----------|

| Command                                       | Comm | nand ide | ntificatio | on code |          | Da       | ata      |          |    |           |          | Da       | ata       |          |          |          |

|                                               | 7    | 6        | 5          | 4       | 3        | 2        | 1        | 0        | 7  | 6         | 5        | 4        | 3         | 2        | 1        | 0        |

| COMMAND0<br>Write address                     | 1    | 0        | 0          | 0       | V3       | V2       | V1       | V0       | 0  | 0         | 0        | H4       | H3        | H2       | H1       | H0       |

| COMMAND1<br>Character write                   | 1    | 0        | 0          | 1       | 0        | 0        | at2      | at1      | c7 | c6        | c5       | c4       | c3        | c2       | c1       | c0       |

| COMMAND2<br>Vertical display start position   | 1    | 0        | 1          | 0       | SZ<br>21 | SZ<br>20 | SZ<br>11 | SZ<br>10 | 0  | 0         | VP<br>5  | VP<br>4  | VP<br>3   | VP<br>2  | VP<br>1  | VP<br>0  |

| COMMAND3<br>Horizontal display start position | 1    | 0        | 1          | 1       | SZ<br>B1 | SZ<br>B0 | SZ<br>91 | SZ<br>90 | 0  | 0         | HP<br>5  | HP<br>4  | HP<br>3   | HP<br>2  | HP<br>1  | HP<br>0  |

| COMMAND4<br>Display control 1                 | 1    | 1        | 0          | 0       | RST      | RAM      | OSC      | RND      | 0  | I/N       | BLK<br>1 | BLK<br>0 | BK<br>1   | ATS      | 0        | DSP      |

| COMMAND5<br>Display control 2                 | 1    | 1        | 0          | 1       | PH<br>2  | PH<br>1  | PH<br>0  | I/E      | 0  | TST       | CHAL     | BKL      | RSL<br>1  | RSL<br>0 | CVM      | XTS      |

| COMMAND6<br>Display control 3                 | 1    | 1        | 1          | 0       | MOD<br>3 | MOD<br>2 | MOD<br>1 | MOD<br>0 | 0  | HFI       | M30S     | SMS      | IOS       | BCL<br>1 | BCL<br>0 | СВ       |

| COMMAND70<br>Display control 4                | 1    | 1        | 1          | 1       | 0        | 0        | 0        | LINS     | 0  | VCOS<br>1 | LIN<br>5 | LIN<br>4 | LIN<br>3  | LIN<br>2 | LIN<br>1 | LIN<br>0 |

| COMMAND71<br>Display control 5                | 1    | 1        | 1          | 1       | 0        | 1        | 0        | LINS     | 0  | EG<br>2   | PS<br>2  | PS<br>1  | VMN       | SVIS     | VNS      | VSS      |

| COMMAND72<br>Display control 6                | 1    | 1        | 1          | 1       | 1        | 0        | 0        | LINS     | 0  | 0         | 0        | 0        | MOD<br>3  | MOD<br>2 | MOD<br>1 | MOD<br>0 |

| COMMAND73<br>Display control 7                | 1    | 1        | 1          | 1       | 1        | 1        | 0        | LINS     | 0  | 0         | 0        | 0        | VCOS<br>2 | SOUT     | VOUT     | HOUT     |

Once the command identification code in the first bite is written, it is stored internally until the first byte of the following command is written. However, when the display character data write command (COMMAND1) is written, the system becomes locked in display character data write mode, and the first byte cannot be overwritten.

When the  $\overline{\text{CS}}$  pin is set high the command state is set to COMMANDO, i.e., display memory write address setting mode.

# ① COMMAND0: Display Memory Write Address Setting Command

#### First data byte

|            | Desister                 |    | Register content                                        | NI-4- |  |

|------------|--------------------------|----|---------------------------------------------------------|-------|--|

| DA0 to DA7 | DA0 to DA7 Register name |    | Function                                                | Note  |  |

| 7          | —                        | 1  |                                                         |       |  |

| 6          | —                        | 0  | The command 0 identification code:                      |       |  |

| 5          | —                        | 0  | sets the display memory write address.                  |       |  |

| 4          | —                        | 0  |                                                         |       |  |

| 3          | 3 V3                     | 0  |                                                         |       |  |

| 3          | V3                       | 1  | 1                                                       |       |  |

| 0          | 2/0                      | V2 | 0                                                       |       |  |

| 2          | V2                       | 1  | Display memory line address (from 0 to D (howsdesimal)) |       |  |

| 4          |                          | 0  | Display memory line address (from 0 to B (hexadecimal)) |       |  |

| I          | V1                       | 1  |                                                         |       |  |

| 0          | 0                        | 0  |                                                         |       |  |

| 0          | V0                       | 1  |                                                         |       |  |

# Second byte

|            |                          |   | Register content                                              |      |

|------------|--------------------------|---|---------------------------------------------------------------|------|

| DAU to DA7 | DA0 to DA7 Register name |   | Function                                                      | Note |

| 7          | —                        | 0 | Second byte identification code                               |      |

| 6          | —                        | 0 |                                                               |      |

| 5          | —                        | 0 |                                                               |      |

| 4          | H4                       | 0 |                                                               | 1    |

| 4          | 114                      | 1 |                                                               |      |

| 3          | H3                       | 0 |                                                               |      |

| 5          | 115                      | 1 |                                                               |      |

| 2          | H2                       | 0 | Display memory character address (from 0 to 17 (hexadecimal)) |      |

| 2          | 112                      | 1 |                                                               |      |

| 1          | 1 H1<br>0 H0             | 0 |                                                               |      |

| I          |                          | 1 |                                                               |      |

| 0          |                          | 0 |                                                               |      |

| 0 110      |                          | 1 |                                                               |      |

Note: When the chip is reset by the RST pin, the register states (bits) are all cleared to 0.

# ② COMMAND1: Display Character Data Write Setting Command

|            | Desistant     |       | Register content                       | N                                                                          |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

|------------|---------------|-------|----------------------------------------|----------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|----------------------------------|----------------------------------|

| DA0 to DA7 | Register name | State | Function                               | Note                                                                       |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

| 7          | —             | 1     |                                        |                                                                            |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

| 6          | —             | 0     | The command 1 identification code:     | When this command is entered, the<br>chip locks in display character write |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

| 5          | —             | 0     | sets the display memory write address. | mode until the $\overline{CS}$ pin is set high.                            |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

| 4          | —             | 1     |                                        |                                                                            |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

| 3          | —             | 0     |                                        |                                                                            |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

| 2          | —             | 0     |                                        |                                                                            |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

| 1          | ot?           | at2   | at2                                    | at2                                                                        | at? | ot? | at2 | at2 | at2 | at2 | at2 | at? | at2 | at2 | 0 | Turns character attribute 2 off. | Specifies highlight or flashing. |

|            | aiz           | 1     | Turns character attribute 2 on.        | opeones nightight of hashing.                                              |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

| 0          | 0 at1         |       | Turns character attribute 1 off.       | Specifies reverse video.                                                   |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

| 0          |               | 1     | Turns character attribute 1 on.        |                                                                            |     |     |     |     |     |     |     |     |     |     |   |                                  |                                  |

# LC74763, LC74763M

# Second byte

|            | <b>D</b>      |       | Register content                       |      |  |

|------------|---------------|-------|----------------------------------------|------|--|

| DA0 to DA7 | Register name | State | Function                               | Note |  |

| 7          | c7            | 0     |                                        |      |  |

| 7          | 67            | 1     |                                        |      |  |

| 6          | c6            | 0     |                                        |      |  |

| 0          | 60            | 1     |                                        |      |  |

| 5          | 5 c5 -        | 5     | 0                                      |      |  |

| 5          |               | 1     |                                        |      |  |

| 4          | c4            | 0     |                                        |      |  |

|            | 64            | 1     | Character code (from 00 to 7F, FE, FF) |      |  |

| 3          | c3            | 0     |                                        |      |  |

|            |               | 1     |                                        |      |  |

| 2          | c2            | 0     |                                        |      |  |

| 2          |               | 1     |                                        |      |  |

| 1          |               | 0     |                                        |      |  |

|            | 51            | 1     |                                        |      |  |

| 0          | c0 0          | 0     |                                        |      |  |

| 5          | 00            | 1     |                                        |      |  |

Note: When the chip is reset by the RST pin, the register states (bits) are all cleared to 0.

# ③ COMMAND2: Vertical Display Position Setting Command

# First byte

|            | <b>D</b>      |       |                     | Register content    |             |                                    |

|------------|---------------|-------|---------------------|---------------------|-------------|------------------------------------|

| DA0 to DA7 | Register name | State |                     | Function            |             | Note                               |

| 7          | —             | 1     |                     |                     |             |                                    |

| 6          | —             | 0     | The command 2 i     | dentification code: |             |                                    |

| 5          | —             | 1     | sets the vertical d | isplay position.    |             |                                    |

| 4          | —             | 0     |                     |                     |             |                                    |

| 3          | SZ21          | 0     | SZ20                | -                   |             | 1                                  |

| 5          | 5221          | 1     | SZ21                | 0                   | 1           | Character size for the second line |

| 0          | 0700          | 0     | 0                   | Normal size         | Double size | Character size for the second line |

| 2          | SZ20          | 1     | 1                   | Triple size         | Normal size |                                    |

| 1          | SZ11          | 0     | SZ10                |                     |             | 1                                  |

| 1          | 3211          | 1     | SZ11                | 0                   | 1           | Character size for the first line  |

| 0          | 0710          | 0     | 0                   | Normal size         | Double size | Character size for the first line  |

| 0          | SZ10          | 1     | 1                   | Triple size         | Normal size |                                    |

# Second byte

|            | Desister      |       | Register content                                        | Nete                                                                 |  |

|------------|---------------|-------|---------------------------------------------------------|----------------------------------------------------------------------|--|

| DA0 to DA7 | Register name | State | Function                                                | Note                                                                 |  |

| 7          | _             | 0     | Second byte identification code                         |                                                                      |  |

| 6          | _             | 0     |                                                         |                                                                      |  |

| -          | VP5           | 0     | The vertical display start position is given by         |                                                                      |  |

| 5          | (MSB)         | 1     | 5                                                       |                                                                      |  |

| 4          |               | 0     | $VS = H \times (\sum_{n=0}^{5} 2^{n} VPn)$              |                                                                      |  |

| 4          | VP4           | 1     | where H is the horizontal synchronization pulse period. |                                                                      |  |

| 0          | 1/20          | 0     | HSYNC                                                   |                                                                      |  |

| 3          | VP3           | 1     |                                                         | The six bits VP0 to VP5 specify the vertical display start position. |  |

| 0          | ) (DO         | 0     |                                                         | The weight of the lsb is $1 \times H$ .                              |  |

| 2          | VP2           | 1     | vs                                                      |                                                                      |  |

| 4          | N/D4          | 0     | V5                                                      |                                                                      |  |

| 1          | VP1           | 1     | Character                                               |                                                                      |  |

| 0          | VP0           | 0     | HS display area                                         |                                                                      |  |

| 0          | (LSB)         | 1     |                                                         |                                                                      |  |

Note: When the chip is reset by the  $\overline{\text{RST}}$  pin, the register states (bits) are all cleared to 0.

# COMMAND3: Horizontal Display Position Setting Command

#### First byte

|            | Deviator      |       |                    | Register content     | NI-4-       |                                           |

|------------|---------------|-------|--------------------|----------------------|-------------|-------------------------------------------|

| DA0 to DA7 | Register name | State |                    | Function             |             | Note                                      |

| 7          | —             | 1     |                    |                      |             |                                           |

| 6          | —             | 0     | The command 3      | identification code: |             |                                           |

| 5          | —             | 1     | sets the horizonta | al display position. |             |                                           |

| 4          | —             | 1     |                    |                      |             |                                           |

| 3          | SZB1          | 0     | SZB0               |                      |             |                                           |

| 3          | 3201          | 1     | SZB1               | 0                    | 1           | The character size for the elements line  |

|            | 0750          | 0     | 0                  | Normal size          | Double size | The character size for the eleventh line. |

| 2          | SZB0          | 1     | 1                  | Triple size          | Normal size |                                           |

| 4          | 0704          | 0     | SZ90               |                      |             |                                           |

| 1          | SZ91          | 1     | SZ91               | 0                    | 1           |                                           |

| _          |               | 0     | 0                  | Normal size          | Double size | The character size for the ninth line.    |

| 0          | SZ90          | 1     | 1                  | Triple size          | Normal size |                                           |

# Second byte

|            |               |       | Register content                                             |                                  |                                     |

|------------|---------------|-------|--------------------------------------------------------------|----------------------------------|-------------------------------------|

| DA0 to DA7 | Register name | State | Function                                                     | Note                             |                                     |

| 7          | _             | 0     | Second byte identification code                              |                                  |                                     |

| 6          | _             | 0     |                                                              |                                  |                                     |

| _          | HP5           | 0     |                                                              |                                  |                                     |

| 5          | (MSB)         | 1     |                                                              |                                  |                                     |

|            |               | 0     |                                                              |                                  |                                     |

| 4          | HP4           | 1     | The horizontal display start position is given by            |                                  |                                     |

|            | 1100          | 0     | $HS = Tc \times (\sum_{n=0}^{5} 2^{n}HPn)$                   | The six hits HP0 to HP           | The six bits HP0 to HP5 specify the |

| 3          | HP3           | 1     |                                                              | vertical display start position. |                                     |

|            | 1100          | 0     |                                                              | The weight of the lsb is 1 x Tc. |                                     |

| 2          | HP2           | 1     | where Tc is the period of the OSCIN and OSCOUT oscillator in |                                  |                                     |

|            |               | 0     | operating mode.                                              |                                  |                                     |

| 1          | HP1           | 1     |                                                              |                                  |                                     |

|            | HP0           | 0     |                                                              |                                  |                                     |

| 0          | (LSB)         | 1     |                                                              |                                  |                                     |

Note: When the chip is reset by the  $\overline{\text{RST}}$  pin, the register states (bits) are all cleared to 0.

# © COMMAND4: Display Control Setting Command 1

|            | Deviator                    |   | Register content                                            | Nete                                                                                      |  |

|------------|-----------------------------|---|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| DA0 to DA7 | DA0 to DA7 Register name Si |   | Function                                                    | Note                                                                                      |  |

| 7          | —                           | 1 |                                                             |                                                                                           |  |

| 6          | —                           | 1 | The command 4 identification code:                          |                                                                                           |  |

| 5          | —                           | 0 | sets display control parameters.                            |                                                                                           |  |

| 4          | —                           | 0 |                                                             |                                                                                           |  |

|            | DOT                         | 0 |                                                             | This reset occurs when the $\overline{CS}$ pin goes low, and the reset state cleared when |  |

| 3          | RST <sub>SYS</sub>          | 1 | Resets all registers. (Clears all registers to 0.)          | the $\overline{CS}$ pin goes high.                                                        |  |

|            | DAM                         | 0 |                                                             | The RAM erase function requires at least 500 µs.                                          |  |

| 2          | RAM <sub>ERS</sub>          | 1 | Erases display RAM. (Sets display RAM to FF (hexadecimal).) | It is executed on DSPOFF.                                                                 |  |

| 1          | OSC <sub>STP</sub>          | 0 | Continues crystal oscillator operation.                     | Only valid with character display off if                                                  |  |

|            |                             |   | Stops the crystal oscillator.                               | external synchronization is used.                                                         |  |

| 0          | 0 RND <sub>SEL</sub> 0<br>1 |   | Turns off rounding.                                         | Only valid for double and triple size                                                     |  |

|            |                             |   | Turns on rounding.                                          | characters.                                                                               |  |

|            |                         |       |                    | Register content    |                                    |                                 |

|------------|-------------------------|-------|--------------------|---------------------|------------------------------------|---------------------------------|

| DA0 to DA7 | Register name           | State |                    | Function            |                                    | Note                            |

| 7          | —                       | 0     | Second byte ide    | entification code   |                                    |                                 |

| 6          | INT/NON                 | 0     | Interlaced         |                     |                                    | Switches between interlaced and |

| 0          | IN I/NON                | 1     | Non-interlaced     |                     |                                    | non-interlaced display.         |

| 5          | BLK1                    | 0     | BLK0               |                     |                                    |                                 |

| Э          | DLNI                    | 1     | BLK1               | 0                   | 1                                  | Changes the blanking size       |

| 4          | DLKO                    | 0     | 0                  | Blanking off        | Character size blanking            | Changes the blanking size.      |

| 4          | BLK0                    | 1     | 1                  | Frame size blanking | Total area blanking                |                                 |

| 3          | BK1                     | 0     | Flashing period    | about 0.5 s         |                                    |                                 |

| 3          | DNI                     | 1     | Flashing period    | about 1 s           |                                    | Sets the flashing period.       |

| 2          | ATO                     | 0     | Highlight function | on                  |                                    | Salasta et2                     |

| 2          | ATS                     | 1     | Flashing function  | n                   | Selects at2.                       |                                 |

| 1          | —                       | 0     |                    |                     |                                    |                                 |

| 0          | 0 Character display off |       |                    |                     |                                    |                                 |

| 0 DSPON 1  |                         |       | Character displa   | ay on               | Turns character output on and off. |                                 |

Note: When the chip is reset by the  $\overline{RST}$  pin, the register states (bits) are all cleared to 0.

# © COMMAND5: Display Control Setting Command 2

|            | Denistana     |       |                               | Regist          | er content   |          |              | Nete                                   |       |        |   |   |       |              |  |

|------------|---------------|-------|-------------------------------|-----------------|--------------|----------|--------------|----------------------------------------|-------|--------|---|---|-------|--------------|--|

| DA0 to DA7 | Register name | State |                               |                 | Function     |          |              | Note                                   |       |        |   |   |       |              |  |

| 7          | —             | 1     |                               |                 |              |          |              |                                        |       |        |   |   |       |              |  |

| 6          | —             | 1     | The comma                     | and 5 identific | cation code: |          |              |                                        |       |        |   |   |       |              |  |

| 5          | —             | 0     | sets display                  | / control para  | meters.      |          |              |                                        |       |        |   |   |       |              |  |

| 4          | —             | 1     |                               |                 |              |          |              |                                        |       |        |   |   |       |              |  |