# S1D15G00 Series

"Seiko Epson is neither licensed nor authorized to license its customers under one or more patents held by Motif Corporation to use this integrated circuit in the manufacture of liquid crystal display modules. Such license, however, may be obtained directly from MOTIF by writing to: Motif, Inc., c/o In Focus Systems, Inc., 27700A SW Parkway Avenue, Wilsonville, OR 97070-9215, Attention: Vice President Corporate Development."

$\ensuremath{\mathbb C}$  Seiko Epson Corporation 2001, All rights reserved.

### Contents

| 1.  | DESCRIPTION                                  | 1              |

|-----|----------------------------------------------|----------------|

| 2.  | FEATURES                                     | 1              |

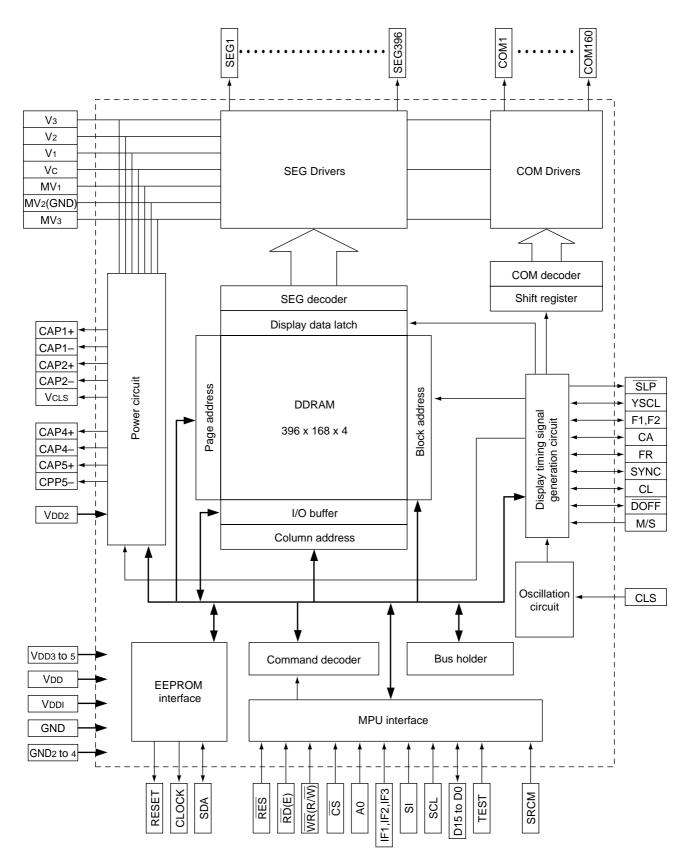

| 3.  | BLOCK DIAGRAM                                | 2              |

| 4.  | PIN LAYOUT                                   | 3              |

| 5.  | LIST OF DEVICE MODELS                        | 3              |

| 6.  | PIN COORDINATE                               | 4              |

| 7.  | PIN DESCRIPTION                              | 6              |

| 8.  | FUNCTIONAL DESCRIPTION 1                     | 1              |

| 9.  | COMMANDS                                     | 30             |

| 10. | ABSOLUTE MAXIMUM RATING                      | <del>1</del> 2 |

| 11. | ELECTRIC CHARACTERISTICS                     | 13             |

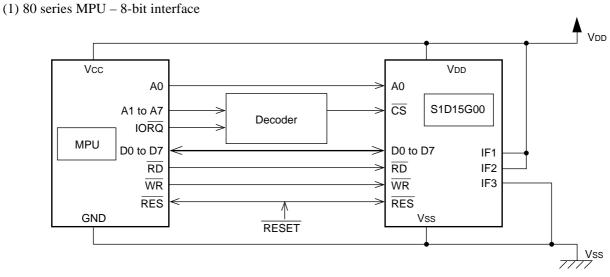

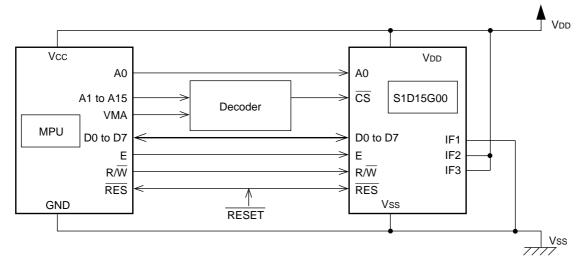

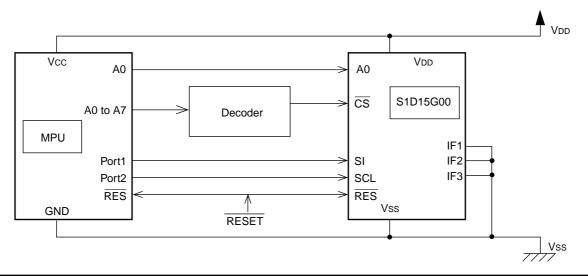

| 12. | MPU INTERFACES (EXAMPLES FOR YOUR REFERENCE) | 53             |

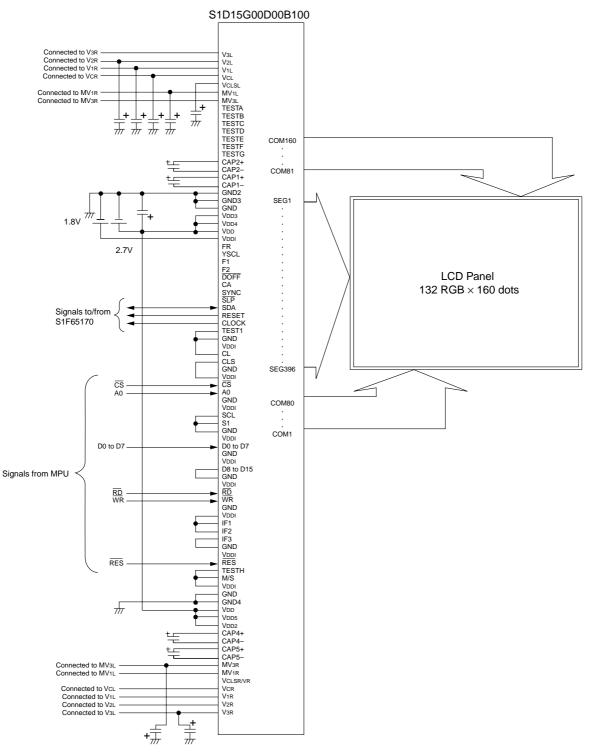

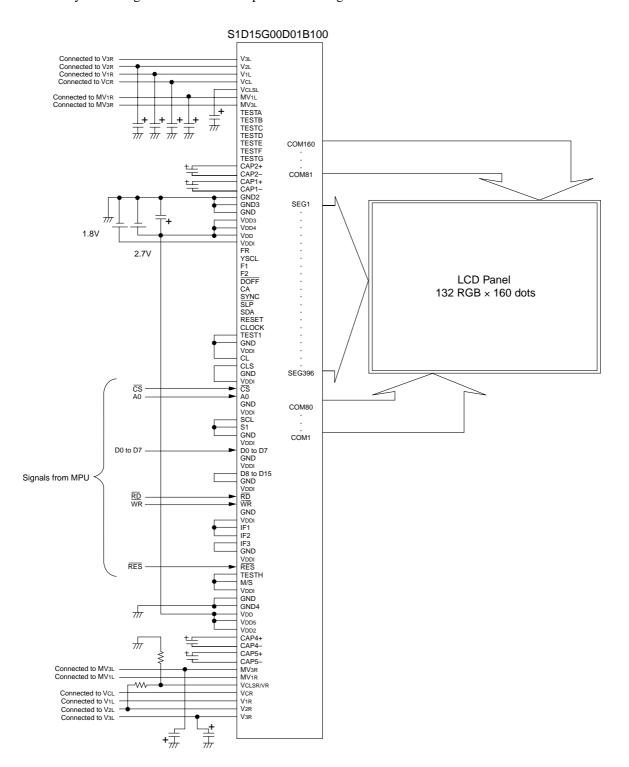

| 13. | PERIPHERAL CONNECTION EXAMPLES               | 58             |

| 14. |                                              | 30             |

| 15. | CAUTIONS                                     | 51             |

### 1. DESCRIPTION

S1D15G00 series are the LCD drivers equipped with the liquid crystal drive power circuit to realize color display with one chip.

S1D15G00 can be directly connected to the MPU bus to store parallel or serial gray-scale display data from MPU on the built-in RAM and to generate liquid crystal drive signals independent from MPU. S1D15G00 generates 396 segment outputs and  $160^{*1}$  common outputs for driving liquid crystal. It incorporates the display RAM with capacity of  $396 \times 168 \times 4$  (16 grayscale). A single dot of pixel on the liquid crystal panel corresponds to 4 bits of the built-in RAM, enabling to display 132 (RGB) × 160 pixels with one chip.

Read or write operations from MPU to the display RAM can be performed without resorting to external actuating clock signals. S1D15G00 allows you to run the display system of high performance and handy equipment at the minimum power consumption thanks to its low-power liquid crystal drive power circuit and oscillation circuit.

\*1: The S1D15G00D10\*100 generates 300 segment outputs and 120 common outputs. It incorporates the display RAM with 300 × 168 × 4 capacity and displays 100 (RGB) × 120 pixels.

### 2. FEATURES

- Number of liquid crystal-drive outputs: 396 segment outputs and 160 common outputs.

- Low cross talk by frame rate modulation.

- 256 color from 4096-color display or full 4096-color display.

When 256 color from 4096-color display is selected: 8 gray-scale for red and green and 4 gray-scale for blue (intermediate tone is selected with the command). When 4096-color display is selected: 16 gray-scale for red, green and blue.

• Direct data display with display RAM (When the LCD is set to normally black) RAM bit Data "0000" ... OFF (Black) "1111" ...ON (Maximum RGB display)

(Normally black LCD, using "inverse display" command)

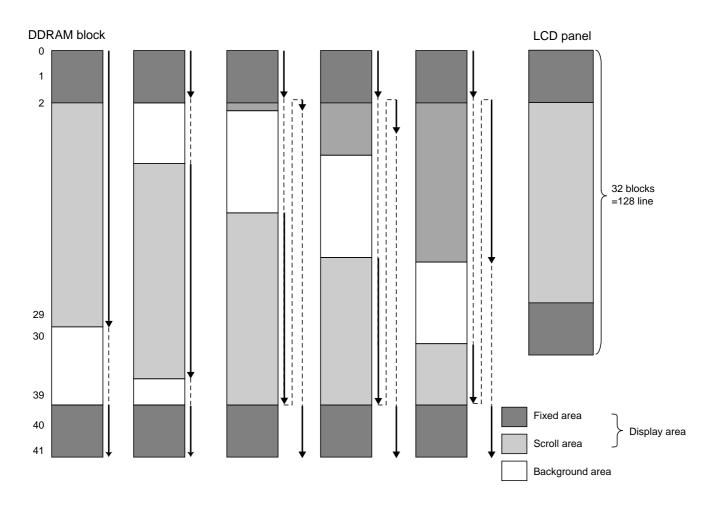

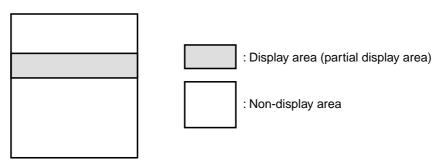

- Partial display function: You can save power by limiting the display space. This function is most suited for handy equipment in the standby mode.

- Display RAM :  $396 \times 168 \times 4 = 266,112$  bits.\*1

- \*1: The S1D15G00D10\*000 has RAM of  $300 \times 120 \times 4 = 144,000$  bits.

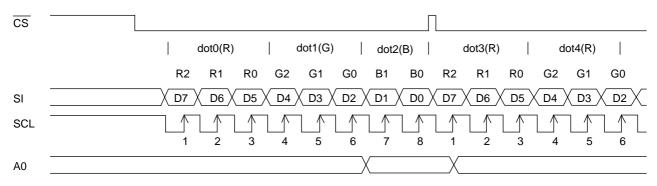

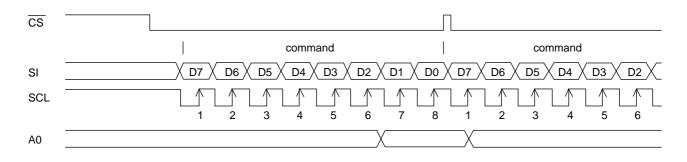

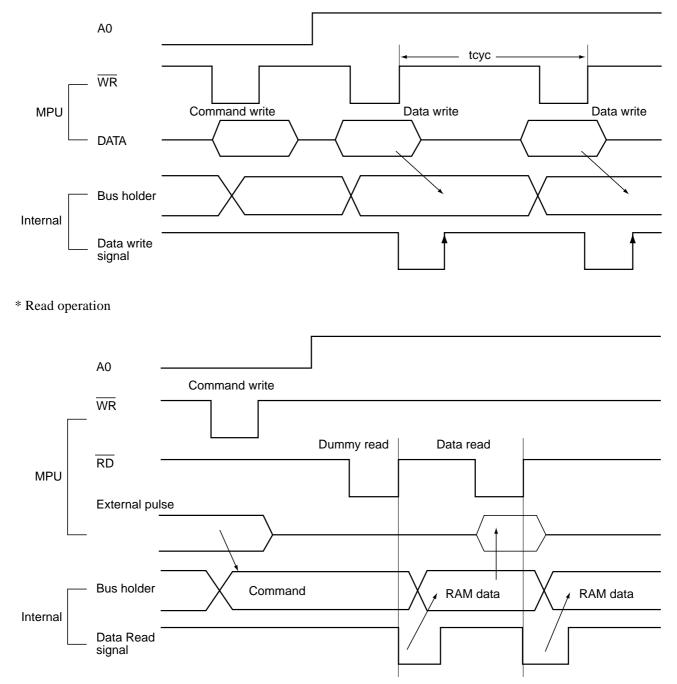

- MPU interface: S1D15G00 can be directly connected to both of the 8/16-bit parallel 80 and 68 series MPU. Two type serial interface are also available.

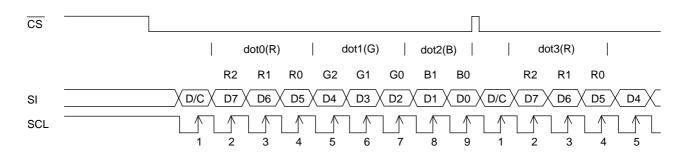

- 3 pins serial : <u>CS</u>, SCL and SI (D/C + 8-bit data)

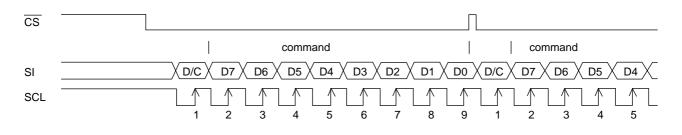

4 pins serial : <u>CS</u>, SCL, SI and A0

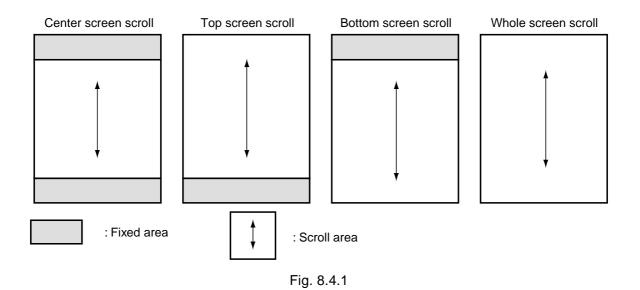

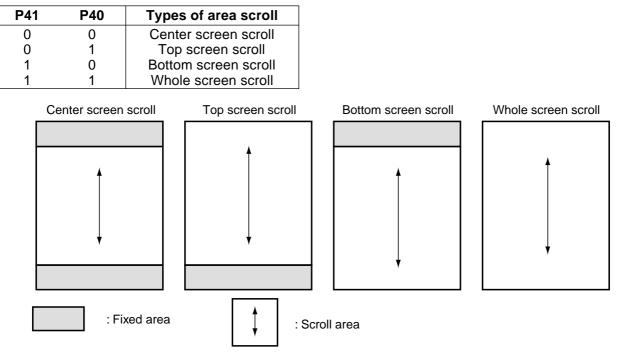

- Abundant command functions: Area scroll function, automatic page & column increment function, display direction switching function and power circuit control function.

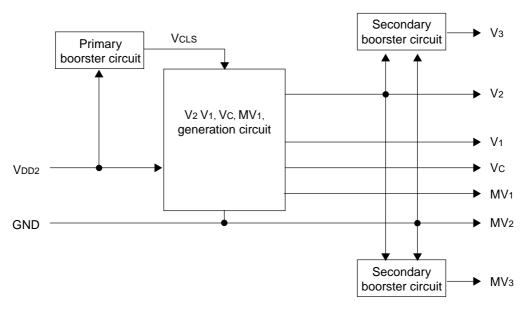

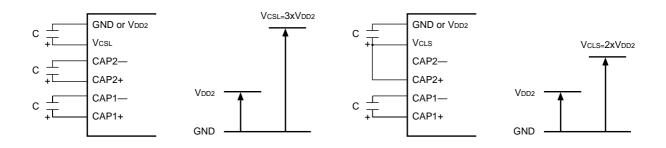

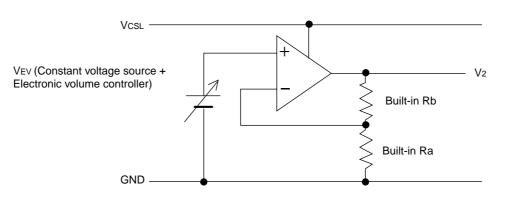

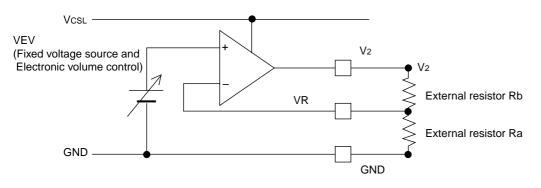

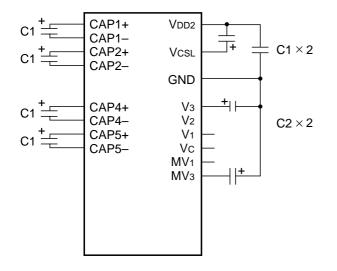

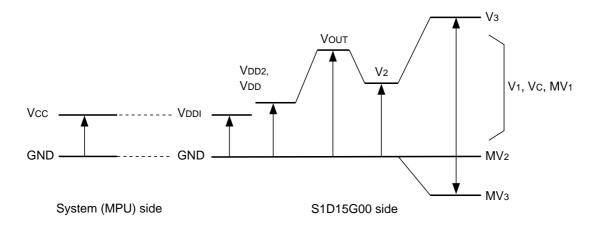

- Built-in liquid crystal drive power circuit: S1D15G00 is equipped the charge pump booster circuit, voltage follower circuit and electric volume control circuit.

- Oscillation circuit with built-in high precision CR (external clock signals acceptable)

- EEPROM interface functions

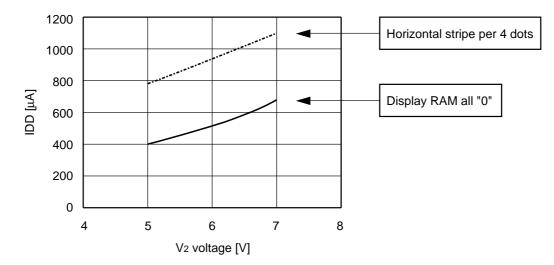

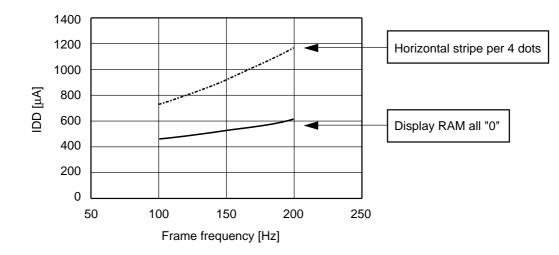

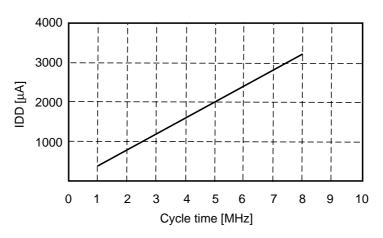

- Low current consumption  $500\mu A$  (Conditions: S1D15G00D01B100, VDD = VDDI = 3.0V, frame frequency 130Hz, V2 = 6.0V, all display RAM data is "0")

- Supply voltage Power for input/output system power: VDDI–GND=1.7V to 3.6V Power for internal circuit operation:

VDD-GND=2.6V to 3.6V

Reference power for booster circuit: VDD2–GND=2.6V to 3.6V

Power for liquid crystal drive:

V3-MV3=12.0V to 21.0V

- Wider operational range: -40°C to 85°C.

- Shipping from: Chip with gold bump. COF.

- Note that the radiation resistant design or light resistance design in strict sense is not employed for S1D15G00.

### 3. BLOCK DIAGRAM

а

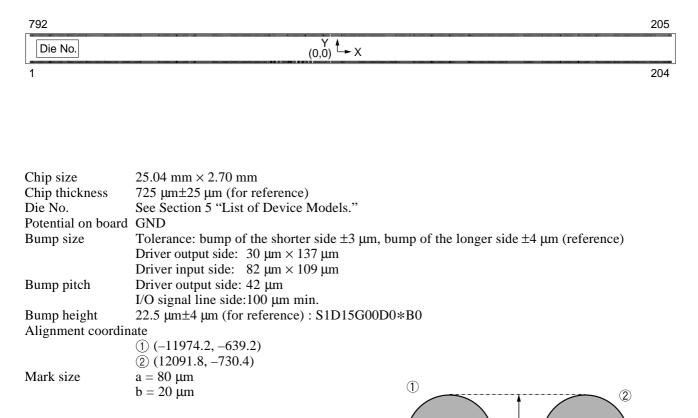

### 4. PIN LAYOUT

### 5. LIST OF DEVICE MODELS

| Model name             | Die No.  | Output<br>count             | V2 voltage<br>control resistor<br>External/Internal | Access<br>to EEPROM | MPU RAM<br>read | Frame frequency<br>/built-in oscillation<br>frequency |

|------------------------|----------|-----------------------------|-----------------------------------------------------|---------------------|-----------------|-------------------------------------------------------|

| S1D15G00D00*100<br>(#) | D15G0D0B | Segment: 396<br>Common: 160 | Internal only<br>(voltage electronically            | 0                   | Unable to read  | 130 Hz<br>/41.6 kHz                                   |

| S1D15G00D05*100        | D15G0D5B |                             | controlled via<br>electronic volume)                |                     | Read enabled    |                                                       |

| S1D15G00D01*100<br>(#) | D15G0D1B |                             | External only<br>(voltage controlled                | ×                   | Unable to read  |                                                       |

| S1D15G00D06*100        | D15G0D6B |                             | via VR pin<br>resistance)                           |                     | Read enabled    |                                                       |

| S1D15G00D03*100<br>(#) | D15G0D3B |                             | External only<br>(voltage controlled                | ×                   | Unable to read  | 180 Hz<br>/57.6 kHz                                   |

| S1D15G00D08*100        | D15G0D8B |                             | via VR pin<br>resistance)                           |                     | Read enabled    |                                                       |

| S1D15G00D10*100<br>(#) | D15G0DAB | Segment: 300<br>Common: 120 | External only (voltage via VR pin resistance)       | ×                   | Unable to read  | 130 Hz<br>/31.2 kHz                                   |

(Note)

For "unable to read" models in the above diagram, the MPU cannot read the RAM. If the RAM must be read, use "read enabled" models.

(#) : These models will be discontinued.

### 6. PIN COORDINATE

Unit: µm

| 1         NC         -1231         58         CAP1         -5671         -1188.5         115         GND *6         1669         -1188.5           3         Val.         -12011         60         GND2         -5551         116         Vol.         *6         116         Vol.         *6         1173         08         1789         *         118         50         1223         5         Val.         -11851         62         GND2         -5314         118         50         1223         123         2335         5         Val.         -11491         64         GND3         -60265         121         D12         2335         5         7         7         Val.         -11491         65         GND3         -4211         122         D13         2335         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7         7                                | PAD<br>No. | Pin<br>Name | x      | Y       | PAD<br>No. | Pin<br>Name | x     | Y        | PAD<br>No. | Pin<br>Name | x       | Y       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|--------|---------|------------|-------------|-------|----------|------------|-------------|---------|---------|

| 3       Val.       -11971       60       GND2       -5446       117       D8       1769         4       Val.       -11851       62       GND2       -52361       118       D9       1923         5       Val.       -11731       63       GND2       -523605       120       D11       2231         7       Val.       -11611       64       GND3       -52605       121       D12       2385         8       Val.       -11491       66       GND3       -4821       122       D13       2339         9       Val.       -11011       66       GND3       -4821       122       D13       2339         10       Vit.       -11011       66       GND       -4501       126       Vob.       6       3001         12       Vit.       -10011       70       Vob.       -4291       128       WR       3365         15       Vcl.       -10531       73       Vob.       -3871       132       IF1       3709         17       Vcl.st.       -10211       76       030       -3376       131       IF1       3609         17       Vcl.st. <td< td=""><td></td><td></td><td></td><td>-1188.5</td><td></td><td></td><td></td><td>-1188.5</td><td></td><td>GND *6</td><td></td><td>-1188.5</td></td<> |            |             |        | -1188.5 |            |             |       | -1188.5  |            | GND *6      |         | -1188.5 |

| $  \begin{array}{ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |             |        |         |            |             |       |          |            |             |         |         |

| 5         Val.         -11731         62         GND2         -523605         119         D10         2077           6         Val.         -11731         63         GND2         -523605         121         D11         2231           7         Val.         -11611         64         GND3         -5026.05         121         D12         2335           8         Val.         -11371         66         GND3         -4921         122         D13         2339           9         Val.         -11311         66         GND3         -4921         122         D13         2339           10         Vit.         -11311         66         GND         -4711         124         D15         2847           11         Vit.         -10651         72         VD04         -4806         125         GND         *6         3001           12         Vit.         -10411         74         TESTG         -3976         131         IF1         300         VDD         *6         3709           18         Vct.st.         -10411         76         VDD         -3766         133         IF3         4017           20                                                           |            |             |        |         |            |             |       |          |            |             |         |         |

| 6 $\forall z_L$ -11611       63       GND2       -513.05       120       D11       2231         7 $\forall z_L$ -11491       66       GND3       -4921       122       D13       2539         9 $\forall z_L$ -11371       66       GND3       -4816       123       D14       2993         10       ViL       -11131       66       GND       -4616       122       D13       2539         11       ViL       -11131       66       GND       -4606       125       GND *6       3001         12       ViL       -11081       70       VDD3       -4396       127       RD       3355         13       ViL       -10651       72       VD4       -4081       130       VD01 *6       3609         14       VcL       -10651       73       VD4       -4081       130       VD01 *6       3609         17       VcL       -10411       74       TESTG       3976       131       IF1       3709         18       VcL       -10531       77       VD0       -3661       133       KD0       *6       471         17       VcL                                                                                                                                                                       |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |             |        |         |            |             |       |          |            |             |         |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |             |        |         |            |             |       |          |            |             |         |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |             |        |         |            |             |       |          |            |             | -       |         |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |             |        |         |            |             |       |          |            |             |         |         |

| 14VcL-1077171VDD3-4291128W/R335515VcL-1053172VDD4-4186129GND *6350916VcL-1053173VDD4-4081130VDD1 *6360917VcL-1041174TESTG-3976131IF1370918VcLsL-1021176VDD-3876133IF2386319VcLsL-1071176VDD-3366134GND *6417120VcLsL-993178VDD1-3456135VDD1 *6427121VcLsL-993178VDD1-3456135VDD1 *6427122MV1L-967181FR-3235138MS467925MV1L-957181FR-3235138MS467926MV3L-921184F2-2773141GND 504327MV3L-921184F2-2773141GND 523.0530TESTA-897186CA-2465143GND 558.0531TESTC-877188SLP-2157145GND 558.0532TESTF-845191CLOCK-1695148GND 558.0533TESTF-845191CLOCK-1695148GND 558.0534TESTF-845191CLOCK-1695148GND 558.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |             |        |         |            |             |       |          |            |             |         |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18         | VCLSL       | -10291 |         | 75         | Vdd         | -3871 |          | 132        | IF2         | 3863    |         |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19         | VCLSL       |        |         | 76         | Vdd         | -3766 |          |            |             |         |         |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |             |        |         |            |             |       |          |            |             |         |         |

| 31TESTC $-8771$ 88 $\overline{SLP}$ $-2157$ 145 $GND4$ $5463.05$ 32TESTD $-8671$ 89 $SDA$ $-2003$ 146 $GND4$ $5568.05$ 33TESTE $-8571$ 90 $RESET$ $-1849$ 147 $GND4$ $5673.05$ 34TESTF $-8451$ 91 $CLOCK$ $-1695$ 148 $GND4$ $5673.05$ 35TESTF $-8336$ 92TEST1 $-1541$ 149 $GND4$ $583.05$ 36TESTF $-8106$ 94 $VDD1$ $66$ $-1387$ 150 $VDD$ $5988.05$ 37TESTF $-8106$ 94 $VDD1$ $66$ $-1287$ 151 $VDD$ $6093.05$ 38TESTF $-7991$ 95 $CL$ $-1187$ 152 $VDD5$ $6198.05$ 39CAP2+ $-7756$ 97GND $*6$ $-879$ 154 $VDD2$ $6446.05$ 41CAP2+ $-7641$ 98 $VDD1$ $*6$ $-779$ 155 $VDD2$ $6551.05$ 42CAP2+ $-7291$ 101GND $*6$ $-371$ 158 $VDD2$ $6866.05$ 43CAP2- $-7291$ 101GND $*6$ $-371$ 158 $VDD2$ $6971.05$ 44CAP2- $-7291$ 101GND $*6$ $137$ 160CAP4+ $7228.05$ 45CAP2- $-6946$ 104SI $-17$ 161CAP4+ $7228.05$ 46CAP2- $-6946$ 107D0 $337$ <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                              |            |             |        |         |            |             |       |          |            |             |         |         |

| 32       TESTD       -8671       89       SDA       -2003       146       GND4       5568.05         33       TESTE       -8571       90       RESET       -1849       147       GND4       5673.05         34       TESTF       -8336       92       TEST1       -1541       149       GND4       578.05         35       TESTF       -8336       92       TEST1       -1541       149       GND4       5883.05         36       TESTF       -8106       94       VDD1*6       -1287       150       VDD       6093.05         38       TESTF       -7991       95       CL       -1187       152       VDD5       6198.05         39       CAP2+       -7756       97       GND *6       -879       154       VDD2       6551.05         41       CAP2+       -7641       98       VDD1*6       -779       155       VDD2       6566.05         42       CAP2+       -7711       100       A0       -525       157       VDD2       6661.05         44       CAP2-       -7291       101       GND *6       -371       158       VDD2       686.05         45                                                                                                                                    |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |             |        |         |            |             |       |          |            |             |         |         |

| 34       TESTF       -8451       91       CLOCK       -1695       148       GND4       5778.05         35       TESTF       -8336       92       TEST1       -1541       149       GND4       588.05         36       TESTF       -8221       93       GND *6       -1387       150       VDD       5988.05         37       TESTF       -8106       94       VDI *6       -1287       151       VDD       6093.05         38       TESTF       -7991       95       CL       -1187       152       VDD       6198.05         39       CAP2+       -7871       96       CLS       -1033       153       VDD       6303.05         40       CAP2+       -7756       97       GND *6       -879       154       VDD2       6446.05         41       CAP2+       -7641       98       VDD1 *6       -779       155       VDD2       6650.05         42       CAP2+       -7291       101       GND *6       -371       158       VDD2       6866.05         43       CAP2-       -7061       102       VDD1 *6       -271       159       VDD2       6971.05         46                                                                                                                               |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |             |        |         |            |             |       |          |            |             |         |         |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |             |        |         |            |             |       |          |            |             |         |         |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |             |        |         |            |             |       |          |            |             |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |             | -7991  |         | 95         |             |       |          |            |             | 6198.05 |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39         | CAP2+       | -7871  |         | 96         | CLS         | -1033 |          | 153        | Vdd5        |         |         |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40         | CAP2+       | -7756  |         | 97         | GND *6      | -879  |          | 154        | Vdd2        | 6446.05 |         |

| 43       CAP2+       -7411       100       A0       -525       157       VDD2       6761.05         44       CAP2-       -7291       101       GND *6       -371       158       VDD2       6866.05         45       CAP2-       -7061       102       VDD1 *6       -271       159       VDD2       6971.05         46       CAP2-       -6946       103       SCL       -171       160       CAP4+       713.05         47       CAP2-       -6831       105       GND *6       137       161       CAP4+       728.05         48       CAP2-       -6831       105       GND *6       137       162       CAP4+       7343.05         49       CAP1+       -6711       106       VDD1 *6       237       163       CAP4+       7458.05         50       CAP1+       -6596       107       D0       337       164       CAP4+       7573.05         51       CAP1+       -6481       108       D1       491       165       CAP4-       7693.05         52       CAP1+       -6366       109       D2       645       166       CAP4-       7808.05       5                                                                                                                                      |            |             |        |         |            |             |       |          |            |             |         |         |

| 44       CAP2-       -7291       101       GND *6       -371       158       VDD2       6866.05         45       CAP2-       -7176       102       VDD1 *6       -271       159       VDD2       6971.05         46       CAP2-       -7061       103       SCL       -171       160       CAP4+       7113.05         47       CAP2-       -6946       104       SI       -17       161       CAP4+       728.05         48       CAP2-       -6831       105       GND *6       137       162       CAP4+       7343.05         49       CAP1+       -6711       106       VDDI *6       237       163       CAP4+       7458.05         50       CAP1+       -6596       107       D0       337       164       CAP4+       7573.05         51       CAP1+       -6481       108       D1       491       165       CAP4-       7693.05         52       CAP1+       -6366       109       D2       645       166       CAP4-       7923.05       54         54       CAP1-       -6131       111       D4       953       168       CAP4-       8038.05       55                                                                                                                               |            |             |        |         |            |             |       |          |            |             |         |         |

| 45       CAP2-       -7176       102       VDDI *6       -271       159       VDD2       6971.05         46       CAP2-       -7061       103       SCL       -171       160       CAP4+       713.05         47       CAP2-       -6946       104       SI       -17       161       CAP4+       7228.05         48       CAP2-       -6831       105       GND *6       137       162       CAP4+       7343.05         49       CAP1+       -6711       106       VDDI *6       237       163       CAP4+       7458.05         50       CAP1+       -6596       107       D0       337       164       CAP4+       7573.05         51       CAP1+       -6481       108       D1       491       165       CAP4-       7693.05         52       CAP1+       -6251       110       D3       799       167       CAP4-       7923.05         54       CAP1-       -6131       111       D4       953       168       CAP4-       8038.05       5         55       CAP1-       -6016       112       D5       1107       169       CAP4-       8153.05       169       CA                                                                                                                         |            |             |        |         |            |             |       |          |            |             |         |         |

| 46       CAP2-       -7061       103       SCL       -171       160       CAP4+       7113.05         47       CAP2-       -6946       104       SI       -17       161       CAP4+       7228.05         48       CAP2-       -6831       105       GND *6       137       162       CAP4+       7343.05         49       CAP1+       -6711       106       VDDI *6       237       163       CAP4+       7458.05         50       CAP1+       -6596       107       D0       337       164       CAP4+       7573.05         51       CAP1+       -6481       108       D1       491       165       CAP4-       7693.05         52       CAP1+       -6366       109       D2       645       166       CAP4-       7808.05         53       CAP1+       -6251       110       D3       799       167       CAP4-       7923.05         54       CAP1-       -6131       111       D4       953       168       CAP4-       8038.05       169         55       CAP1-       -6016       112       D5       1107       169       CAP4-       8153.05       170       CAP5                                                                                                                         |            |             |        |         |            |             |       |          |            |             |         |         |

| 47       CAP2-       -6946       104       SI       -17       161       CAP4+       7228.05         48       CAP2-       -6831       105       GND *6       137       162       CAP4+       7343.05         49       CAP1+       -6711       106       VDDI *6       237       163       CAP4+       7458.05         50       CAP1+       -6596       107       D0       337       164       CAP4+       7573.05         51       CAP1+       -6481       108       D1       491       165       CAP4-       7693.05         52       CAP1+       -6366       109       D2       645       166       CAP4-       7808.05         53       CAP1-       -6131       111       D4       953       167       CAP4-       7923.05         54       CAP1-       -6016       112       D5       1107       169       CAP4-       8038.05       169         56       CAP1-       -5901       113       D6       1261       170       CAP5+       8273.05       170                                                                                                                                                                                                                                         |            |             |        |         |            |             |       |          |            |             |         |         |

| 48       CAP2-       -6831       105       GND *6       137       162       CAP4+       7343.05         49       CAP1+       -6711       106       VDDI *6       237       163       CAP4+       7458.05         50       CAP1+       -6596       107       D0       337       164       CAP4+       7573.05         51       CAP1+       -6481       108       D1       491       165       CAP4-       7693.05         52       CAP1+       -6366       109       D2       645       166       CAP4-       7808.05         53       CAP1+       -6251       110       D3       799       167       CAP4-       7923.05         54       CAP1-       -6131       111       D4       953       168       CAP4-       8038.05         55       CAP1-       -6016       112       D5       1107       169       CAP4-       8153.05       169         56       CAP1-       -5901       113       D6       1261       170       CAP5+       8273.05       170                                                                                                                                                                                                                                         |            |             |        |         |            |             |       |          |            |             |         |         |

| 49       CAP1+       -6711       106       VDDI *6       237       163       CAP4+       7458.05         50       CAP1+       -6596       107       D0       337       164       CAP4+       7458.05         51       CAP1+       -6481       108       D1       491       165       CAP4-       7693.05         52       CAP1+       -6366       109       D2       645       166       CAP4-       7808.05         53       CAP1+       -6251       110       D3       799       167       CAP4-       7923.05         54       CAP1-       -6131       111       D4       953       168       CAP4-       8038.05         55       CAP1-       -6016       112       D5       1107       169       CAP4-       8153.05         56       CAP1-       -5901       113       D6       1261       170       CAP5+       8273.05                                                                                                                                                                                                                                                                                                                                                                     |            |             |        |         |            |             |       |          |            | -           |         |         |

| 50       CAP1+       -6596       107       D0       337       164       CAP4+       7573.05         51       CAP1+       -6481       108       D1       491       165       CAP4-       7693.05         52       CAP1+       -6366       109       D2       645       166       CAP4-       7808.05         53       CAP1+       -6251       110       D3       799       167       CAP4-       7923.05         54       CAP1-       -6131       111       D4       953       168       CAP4-       8038.05         55       CAP1-       -6016       112       D5       1107       169       CAP4-       8153.05         56       CAP1-       -5901       113       D6       1261       170       CAP5+       8273.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |             |        |         |            |             |       |          |            |             |         |         |

| 51       CAP1+       -6481       108       D1       491       165       CAP4-       7693.05         52       CAP1+       -6366       109       D2       645       166       CAP4-       7808.05         53       CAP1+       -6251       110       D3       799       167       CAP4-       7923.05         54       CAP1-       -6131       111       D4       953       168       CAP4-       8038.05         55       CAP1-       -6016       112       D5       1107       169       CAP4-       8153.05         56       CAP1-       -5901       113       D6       1261       170       CAP5+       8273.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |             |        |         |            |             |       |          |            |             |         |         |

| 52       CAP1+       -6366       109       D2       645       166       CAP4-       7808.05         53       CAP1+       -6251       110       D3       799       167       CAP4-       7923.05         54       CAP1-       -6131       111       D4       953       168       CAP4-       8038.05         55       CAP1-       -6016       112       D5       1107       169       CAP4-       8153.05         56       CAP1-       -5901       113       D6       1261       170       CAP5+       8273.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |             |        |         |            |             |       |          |            |             |         |         |

| 53       CAP1+       -6251       110       D3       799       167       CAP4-       7923.05         54       CAP1-       -6131       111       D4       953       168       CAP4-       8038.05         55       CAP1-       -6016       112       D5       1107       169       CAP4-       8153.05         56       CAP1-       -5901       113       D6       1261       170       CAP5+       8273.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |             |        |         |            |             |       |          |            |             |         |         |

| 54       CAP1-       -6131       111       D4       953       168       CAP4-       8038.05         55       CAP1-       -6016       112       D5       1107       169       CAP4-       8153.05         56       CAP1-       -5901       113       D6       1261       170       CAP5+       8273.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |             |        |         |            |             |       |          |            |             |         |         |

| 55       CAP1-       -6016       112       D5       1107       169       CAP4-       8153.05         56       CAP1-       -5901       113       D6       1261       170       CAP5+       8273.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |             |        |         |            |             |       |          |            |             |         |         |

| 56 CAP15901 113 D6 1261 170 CAP5+ 8273.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |             |        |         |            |             |       |          |            |             |         |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |             |        |         |            |             |       |          |            |             |         |         |