## Off-line Controllers for LED Lighting

### ■GENERAL DESCRIPTION

The XC9401 series are off-line controller ICs for LED lighting. Through optimization of the external components, these ICs can be made to operate in a range from 85VAC to 270VAC, as well as by DC input, and a diversity of specifications can be achieved by selecting components appropriate for the circuit configuration. Fixed off-time control is used for the basic control method, and by detecting the current that flows to the external power MOSFET, the current that flows to the LED is monitored to provide a stable power supply for LED lighting. Two product series differing by function type are available, the XC9401A type and the XC9401B type.

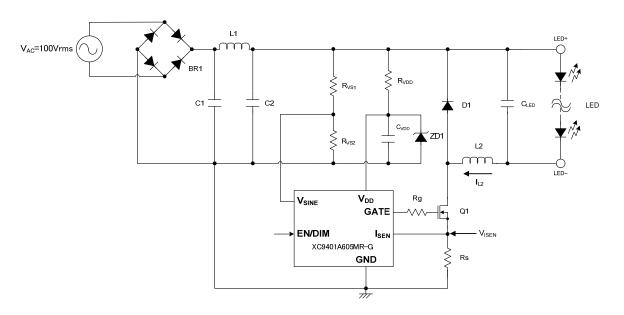

The circuit configuration of type A is designed for the power factor, achieving a high power factor by synchronizing the LED current to the input current (sine wave). In this circuit configuration, a high-capacity, high-withstand voltage electrolytic capacitor is not necessary after the bridge rectifier circuit from the AC input. The input filter removes high frequency switching noise from the AC line, allowing a small-capacity ceramic capacitor to be used.

Type B holds the peak current due to switching that flows to the external power MOSFET constant, enabling the LED current to be kept constant. By keeping the LED current constant, this circuit configuration makes it possible to achieve a stable light source with high efficiency.

#### APPLICATIONS TYPICAL APPLICATION CIRCUITS •LED lights ( <=10W ) (XC9401B605MR-G 100VAC Non-isolation buck Type) LED lamps LED tube lights 100VAC /110VAC LED spot lights BR1 R5 33kΩ Ş •LED stands R6 33kΩ LED ries/110mA C1 C2 D1 071M25 FEATURES 1.1 Operating Voltage 85VAC ~ 270VAC ZD ÷ V<sub>DD</sub> Input Voltage Range : 9V~15V m L2 3.3mH Fixed Off-time 6.0 µ s NF V<sub>DD</sub> **Protection Circuits** Thermal Shutdown 150°C (TYP.) · Q1 IPD60R3K3C6 GATE V<sub>DD</sub> Over voltage protection, V<sub>DD</sub>=18V (TYP.) \_\_\_\_\_ EN/DIM Ŀ UVLO, V<sub>DD</sub>=6.5V (TYP.) Ş R4 GND Over current protection VISEN=0.7V (TYP.) 1 **PWM Dimming** Dimming Package SOT-26 Operating -40°C ~ +85°C Ambient Temperature **Environmentally Friendly** : EU RoHS Compliant, Pb Free

### SOLUTION EXAMPLES

| Input Voltage   | Product Type | Isolation / Non-Isolation | Topology   | Efficiency | Power Factor |

|-----------------|--------------|---------------------------|------------|------------|--------------|

| 100VAC / 110VAC | XC9401B605MR | Non-Isolation             | Buck       | 91%        | 0.6          |

|                 | XC9401B605MR |                           |            | 83%        | 0.6          |

| 220VAC / 240VAC | XC9401A605MR | Isolation                 | Flyback    | 82%        | 0.9          |

| 220VAC / 240VAC | XC9401B605MR | Non-Isolation             | Buck       | 87%        | 0.6          |

|                 | XC9401B605MR | -                         | Buck       | 88%        | -            |

| DC / 12VAC      | XC9401B605MR | -                         | Buck-Boost | 86%        | -            |

\*Due to dispersion of constant values of external components, the above values may be deviated.

Please understand that the above are typical values. For details, refer to the XC9401 Series Application Notes.

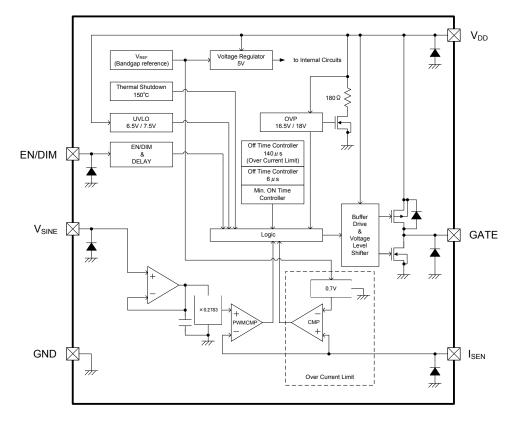

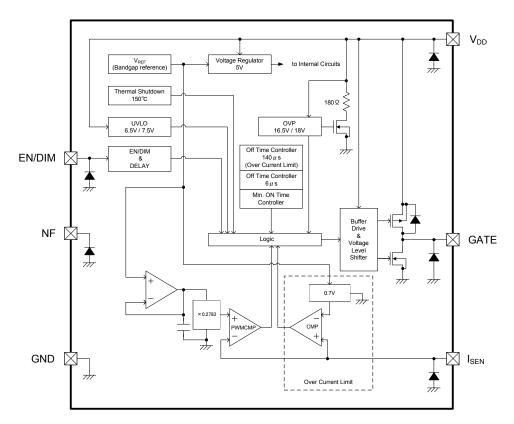

## ■BLOCK DIAGRAM

1) XC9401 Series, Type A

2) XC9401 Series, Type B

## PRODUCT CLASSIFICATION

#### Ordering Information

XC9401123456-7

| DESIGNATOR | ITEM         | SYMBOL | DESCRIPTION                              |  |

|------------|--------------|--------|------------------------------------------|--|

|            |              |        |                                          |  |

| 1          | Туре         | В      | Refer to Selection Guide                 |  |

| 2          | OFF Time     | 6      | OFF Time is fixed in 6 $\mu$ s           |  |

| 34         | Accuracy     | 05     | I <sub>SEN</sub> Voltage Accuracy is ±5% |  |

| 56-7 (*1)  | Package      | MR-G   | SOT-26 (3,000/Reel)                      |  |

|            | (Order Unit) | MR-G   |                                          |  |

(\*1) The "-G" suffix denotes Halogen and Antimony free as well as being fully RoHS compliant.

#### •Selection Guide

| TYPE | COMPARISON WITH ISEN          | PWM DIMMING | DESCRIPTION                                          |

|------|-------------------------------|-------------|------------------------------------------------------|

| Α    | "V <sub>SINE</sub> " × 0.2783 | Yes         | Type A is suitable for PFC circuit.                  |

| В    | "V <sub>REF</sub> " × 0.278   | Yes         | Type B is suitable for constant LED current circuit. |

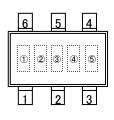

## ■ PIN CONFIGURATION

SOT-26 (TOP VIEW)

## (TOP VIEW

### ■ PIN ASSIGNMENT

| PIN NUMBER | PIN NAME                  | FUNCTIONS                                                        |

|------------|---------------------------|------------------------------------------------------------------|

| SOT-26     |                           | FUNCTIONS                                                        |

| 1          | I <sub>SEN</sub>          | Current Feedback                                                 |

| 2          | V <sub>DD</sub>           | Power Input                                                      |

| 3          | GATE                      | External Power MOS Drive                                         |

| 4          | EN/DIM                    | Active / Stand-by / PWM Dimming Control                          |

| 5          | GND                       | Ground                                                           |

| 6          | Type A: V <sub>SINE</sub> | V <sub>SINE</sub> Pin: Current Feedback Reference Voltage Input. |

| 0          | Type B: NF                | NF Pin: No Function. Please connect to GND.                      |

\*Type B

NF

6

1

$\mathbf{I}_{\text{SEN}}$

GND EN/DIM

4

3

GATE

5

2

$V_{\text{DD}}$

SOT-26

(TOP VIEW)

### **FUNCTION**

| PIN NAME | EN/DIM | STATUS               |  |

|----------|--------|----------------------|--|

|          | L      | Stand-by Mode        |  |

| EN/DIM   | Н      | Active Mode          |  |

|          | OPEN   | Undefined State (*1) |  |

<sup>(\*1)</sup> Prohibited in the XC9401 series due to undefined operation.

## ■ABSOLUTE MAXIMUM RATINGS

|                               |                |                   |                                         | Ta=25°C |

|-------------------------------|----------------|-------------------|-----------------------------------------|---------|

| PARAMET                       | ER             | SYMBOL            | RATINGS                                 | UNITS   |

| V <sub>DD</sub> Pin Vol       | tage           | V <sub>DD</sub>   | -0.3 ~ +19.4                            | V       |

| EN/DIM Pin V                  | /oltage        | VENDIM            | -0.3 ~ +19.4                            | V       |

| GATE Pin Voltage              |                | V <sub>MODE</sub> | -0.3 ~ V_{DD}+0.3 or +19.4 $^{(^{*2})}$ | V       |

| I <sub>SEN</sub> Pin Voltage  |                | VISEN             | -0.3 ~ 5.5                              | V       |

| V <sub>SINE</sub> Pin Voltage |                | V <sub>SINE</sub> | -0.3 ~ 5.5                              | mA      |

| NF Pin Volt                   | NF Pin Voltage |                   | 0.0 0.0                                 |         |

| Power Dissipation             | SOT-26         | Pd                | 250                                     | mW      |

| Operating Ambient Temperature |                | Topr              | -40 ~ +85                               | °C      |

| Storage Temperature           |                | Tstg              | -55 ~ +125                              | °C      |

(\*1) All voltages are described based on GND.

$^{(^{\prime 2})}$  The maximum value should be either  $V_{\text{DD}}\text{+}0.3$  or +19.4V in the lowest.

Ta=25 °C

## ■ELECTRICAL CHARACTERISTICS

#### XC9401 Series, Type A

| XC9401 Series, Type A                                                       |                      |                                                                                                                  |        |        |        |       | Ta=25 °C |

|-----------------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-------|----------|

| PARAMETER                                                                   | SYMBOL               | CONDITIONS                                                                                                       | MIN.   | TYP.   | MAX.   | UNITS | CIRCUIT  |

| V <sub>DD</sub> Voltage Range                                               | $V_{\text{DD}}$      |                                                                                                                  | 9      | -      | 15     | V     | 1        |

| I <sub>SEN</sub> Voltage                                                    | VISEN                | $V_{ISEN}$ =SWEEP <sup>(*1)</sup> , $V_{SINE}$ =1V                                                               | 0.2644 | 0.2783 | 0.2922 | V     | 1        |

| V <sub>SINE</sub> Voltage Range <sup>(*2)</sup>                             | $V_{\text{SINE}}$    |                                                                                                                  | GND    | -      | 1.8    | V     | 1        |

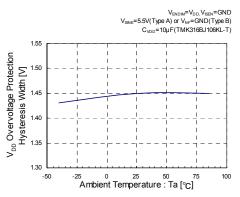

| UVLO Detect Voltage                                                         | $V_{\text{UVLO}}$    | V <sub>DD</sub> =SWEEP (*3)                                                                                      | 5.5    | 6.5    | 7.5    | V     | 1        |

| UVLO Release Voltage                                                        | V <sub>UVLOR</sub>   | V <sub>DD</sub> =SWEEP (*4)                                                                                      | 6.5    | 7.5    | 8.5    | V     | 1        |

| UVLO Hysteresis Width                                                       | V <sub>UVLOH</sub>   | V <sub>UVLOH</sub> =V <sub>UVLOR</sub> - V <sub>UVLO</sub>                                                       | -      | 1.1    | -      | V     | 1        |

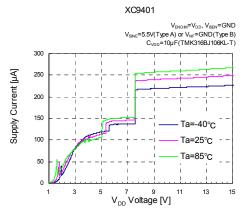

| Supply Current (*5)                                                         | I <sub>DD</sub>      | V <sub>DD</sub> =V <sub>EN/DIM</sub> =15V                                                                        | -      | 250    | 300    | μA    | 1        |

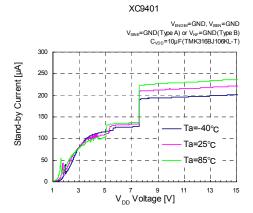

| Stand-by Current (*6)                                                       | I <sub>STB</sub>     | V <sub>DD</sub> =15V, V <sub>EN/DIM</sub> =GND,<br>V <sub>SINE</sub> =GND                                        | -      | 225    | 280    | μA    | 1        |

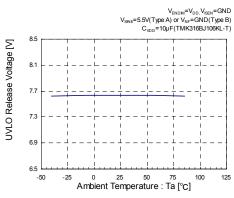

| V <sub>DD</sub> Overvoltage Protection Voltage                              | V <sub>OVP</sub>     | $V_{DD}$ =SWEEP <sup>(*3)</sup> , $V_{EN/DIM}$ = $V_{DD}$                                                        | 17     | 18     | 19     | V     | 1        |

| V <sub>DD</sub> Overvoltage Protection<br>Release Voltage                   | V <sub>OVPR</sub>    | $V_{DD}$ =SWEEP <sup>(*4)</sup> , $V_{EN/DIM}$ = $V_{DD}$                                                        | 15.5   | 16.5   | 17.5   | V     | 1        |

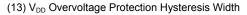

| V <sub>DD</sub> Overvoltage Protection<br>Hysteresis Width                  | V <sub>OVPH</sub>    | V <sub>OVPH</sub> =V <sub>OVP</sub> - V <sub>OVPR</sub>                                                          | -      | 1.5    | -      | V     | 1        |

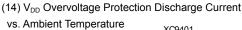

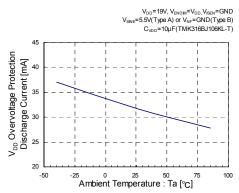

| V <sub>DD</sub> Overvoltage Protection<br>Discharge Current <sup>(*7)</sup> | I <sub>OVP</sub>     | V <sub>DD</sub> =19V                                                                                             | -      | 30     | -      | mA    | 1        |

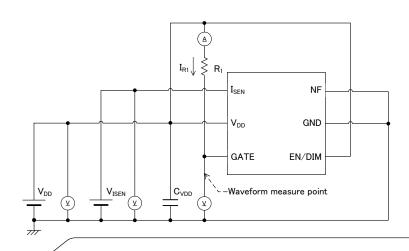

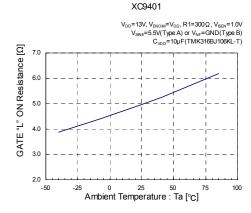

| GATE "H" ON Resistance                                                      | R <sub>GATEH</sub>   | I <sub>GATE</sub> = -10mA<br>R <sub>GATEH</sub> = (V <sub>DD</sub> -V <sub>GATE</sub> ) / I <sub>GATE</sub>      | 2      | 5      | 8      | Ω     | 3        |

| GATE "L" ON Resistance                                                      | R <sub>GATEL</sub>   | $V_{ISEN}$ =1V, R <sub>1</sub> =300Ω<br>R <sub>GATEL</sub> = V <sub>GATE</sub> / I <sub>R1</sub> <sup>(*8)</sup> | -      | 5      | -      | Ω     | 4        |

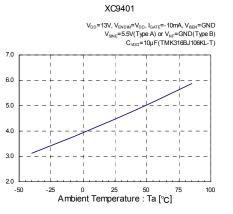

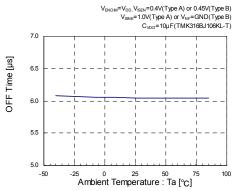

| OFF Time (*9)                                                               | t <sub>OFF</sub>     | V <sub>ISEN</sub> =0.4V, V <sub>SINE</sub> =1V                                                                   | -      | 6      | -      | μs    | 1        |

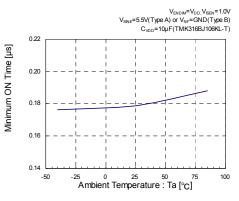

| Minimum ON Time                                                             | t <sub>onmin</sub>   | V <sub>ISEN</sub> =1V                                                                                            | -      | 0.2    | -      | μs    | 1        |

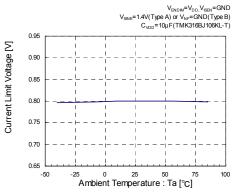

| Current Limit Voltage (*10)                                                 | V <sub>LIM</sub>     | V <sub>ISEN</sub> =SWEEP, V <sub>SINE</sub> =1.4V                                                                | 0.65   | 0.70   | 0.95   | V     | 1        |

| Thermal Shutdown Temperature (*11)                                          | T <sub>TSD</sub>     |                                                                                                                  | -      | 150    | -      | °C    | 1        |

| Thermal Shutdown Release<br>Temperature                                     | T <sub>TSDR</sub>    |                                                                                                                  | -      | 130    | -      | °C    | 1        |

| Thermal Shutdown Hysteresis Width                                           | T <sub>HYS</sub>     |                                                                                                                  | -      | 20     | -      | °C    | 1        |

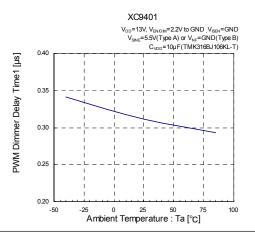

| PWM Dimmer Delay Time1 (*12)                                                | t <sub>PWMDIM1</sub> | V <sub>EN/DIM</sub> =2.2V to GND                                                                                 | -      | 0.3    | 4.0    | μs    | 2        |

| PWM Dimmer Delay Time2 (*13)                                                | t <sub>PWMDIM2</sub> | V <sub>EN/DIM</sub> =GND to 2.2V                                                                                 | 100    | 140    | 200    | μs    | 2        |

| EN/DIM "H" Voltage                                                          | $V_{\text{EN/DIMH}}$ |                                                                                                                  | 2.2    | -      | 15.0   | V     | 1        |

| EN/DIM "L" Voltage                                                          | V <sub>EN/DIML</sub> |                                                                                                                  | GND    | -      | 0.4    | V     | 1        |

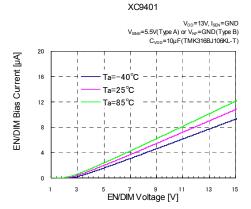

| EN/DIM Bias Current                                                         | I <sub>EN/DIMH</sub> | V <sub>EN/DIM</sub> =15V                                                                                         | -      | -      | 32     | μA    | 1        |

Unless otherwise stated, GND standard,  $V_{DD}$ =13V,  $V_{EN/DIM}$ =V<sub>DD</sub>,  $V_{ISEN}$ =GND,  $V_{SINE}$ =5.5V

(\*1) I<sub>SEN</sub> pin voltage measured at start of GATE pin switching.

$^{(^{2})}$  Indicates V<sub>SINE</sub> pin voltage at which OFF TIME 6  $\mu$  s switching becomes possible.

$^{(^{\ast3})}V_{\text{DD}}$  pin voltage measured when GATE pin=L occurs.

$^{^{(^{\ast}4)}}V_{\text{DD}}$  pin voltage measured when GATE pin=H occurs.

(\*5) Indicates internal supply current when "H" level is input into EN/DIM pin and all circuits are activated. (When not switching.)

(\*6) Indicates internal supply current when "L" level is input into EN/DIM pin and the switching circuit is stopped.

$^{(^{77})}$  Indicates the current that discharges the capacitance between the  $V_{\text{DD}}$  and GND pins at  $V_{\text{OVP}}.$

(\*8) Please refer to P.7 "CIRCUIT④".

$^{(^{9)}}$  May not be fixed at 6  $\mu$  s when UVLO is detected or during DIM signal control.

$^{(*10)}$  When the current limit voltage V<sub>LIM</sub> is exceeded, off time is extended to about 140  $\mu$  s to prevent element damage.

For details, refer to the operation description.

(\*11) To protect the IC from thermal destruction, thermal shutdown activates when the chip temperature reaches 150°C and forcibly sets the GATE pin voltage to "L". When the chip temperature falls to 130°C, operation resumes.

(\*12) Time from attainment of EN/DIM "L" voltage until GATE pin=L.

(\*13) Time from attainment of EN/DIM "H" voltage until GATE pin=H.

TOIREX 5/19

## ■ ELECTRICAL CHARACTERISTICS (Continued)

#### XC9401 Series, Type B

| XC9401 Series, Type B                                                       |                      | Υ.                                                                                                                       | ,      |        |        |       | Ta=25°C |

|-----------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|-------|---------|

| PARAMETER                                                                   | SYMBOL               | CONDITIONS                                                                                                               | MIN.   | TYP.   | MAX.   | UNITS | CIRCUIT |

| V <sub>DD</sub> Voltage Range                                               | V <sub>DD</sub>      |                                                                                                                          | 9      | -      | 15     | V     | 1       |

| I <sub>SEN</sub> Voltage                                                    | VISEN                | V <sub>ISEN</sub> =SWEEP (*1)                                                                                            | 0.3259 | 0.3430 | 0.3602 | V     | 1       |

| UVLO Detect Voltage                                                         | V <sub>UVLO</sub>    | V <sub>DD</sub> =SWEEP (*2)                                                                                              | 5.5    | 6.5    | 7.5    | V     | 1       |

| UVLO Release Voltage                                                        | V <sub>UVLOR</sub>   | V <sub>DD</sub> =SWEEP (*3)                                                                                              | 6.5    | 7.5    | 8.5    | V     | 1       |

| UVLO Hysteresis Width                                                       | V <sub>UVLOH</sub>   | V <sub>UVLOH</sub> =V <sub>UVLOR</sub> - V <sub>UVLO</sub>                                                               | -      | 1.1    | -      | V     | 1       |

| Supply Current (*4)                                                         | I <sub>DD</sub>      | V <sub>DD</sub> =V <sub>EN/DIM</sub> =15V                                                                                | -      | 250    | 300    | μA    | 1       |

| Stand-by Current (*5)                                                       | I <sub>STB</sub>     | V <sub>DD</sub> =15V, V <sub>EN/DIM</sub> =GND                                                                           | -      | 225    | 280    | μA    | 1       |

| V <sub>DD</sub> Overvoltage Protection Voltage                              | V <sub>OVP</sub>     | V <sub>DD</sub> =SWEEP <sup>(*2)</sup>                                                                                   | 17     | 18     | 19     | V     | 1       |

| V <sub>DD</sub> Overvoltage Protection<br>Release Voltage                   | V <sub>OVPR</sub>    | V <sub>DD</sub> =SWEEP (*3)                                                                                              | 15.5   | 16.5   | 17.5   | V     | 1       |

| V <sub>DD</sub> Overvoltage Protection<br>Hysteresis Width                  | V <sub>OVPH</sub>    | V <sub>OVPH</sub> =V <sub>OVP</sub> - V <sub>OVPR</sub>                                                                  | -      | 1.5    | -      | V     | 1       |

| V <sub>DD</sub> Overvoltage Protection<br>Discharge Current <sup>(*6)</sup> | I <sub>OVP</sub>     | V <sub>DD</sub> =19V                                                                                                     | -      | 30     | -      | mA    | 1       |

| GATE "H" ON Resistance                                                      | R <sub>GATEH</sub>   | I <sub>GATE</sub> = -10mA<br>R <sub>GATEH</sub> = (V <sub>DD</sub> - V <sub>GATE</sub> ) / I <sub>GATE</sub>             | 2      | 5      | 8      | Ω     | 3       |

| GATE "L" ON Resistance                                                      | R <sub>GATEL</sub>   | $V_{ISEN}$ =1V, R <sub>1</sub> =300 $\Omega$<br>R <sub>GATEL</sub> = V <sub>GATE</sub> / I <sub>R1</sub> <sup>(*7)</sup> | -      | 5      | -      | Ω     | 4       |

| OFF Time (*8)                                                               | t <sub>OFF</sub>     | V <sub>ISEN</sub> =0.45V                                                                                                 | -      | 6      | -      | μs    | 1       |

| Minimum ON Time                                                             | t <sub>onmin</sub>   | V <sub>ISEN</sub> =1V                                                                                                    | -      | 0.2    | -      | μs    | 1       |

| Current Limit Voltage (*9)                                                  | V <sub>LIM</sub>     | V <sub>ISEN</sub> =SWEEP                                                                                                 | 0.65   | 0.70   | 0.95   | V     | 1       |

| Thermal Shutdown Temperature (*10)                                          | T <sub>TSD</sub>     |                                                                                                                          | -      | 150    | -      | °C    | 1       |

| Thermal Shutdown Release<br>Temperature                                     | T <sub>TSDR</sub>    |                                                                                                                          | -      | 130    | -      | °C    | 1       |

| Thermal Shutdown Hysteresis Width                                           | T <sub>HYS</sub>     |                                                                                                                          | -      | 20     | -      | °C    | 1       |

| PWM Dimmer Delay Time1 (*11)                                                | t <sub>PWMDIM1</sub> | V <sub>EN/DIM</sub> =2.2V to GND                                                                                         | -      | 0.3    | 4.0    | μs    | 1       |

| PWM Dimmer Delay Time2 (*12)                                                | t <sub>PWMDIM2</sub> | V <sub>EN/DIM</sub> =GND to 2.2V                                                                                         | 100    | 140    | 200    | μs    | 2       |

| EN/DIM "H" Voltage                                                          | V <sub>EN/DIMH</sub> |                                                                                                                          | 2.2    | -      | 15.0   | V     | 2       |

| EN/DIM "L" Voltage                                                          | V <sub>EN/DIML</sub> |                                                                                                                          | GND    | -      | 0.4    | V     | 1       |

| EN/DIM Bias Current                                                         | I <sub>EN/DIMH</sub> | V <sub>EN/DIM</sub> =15V                                                                                                 | -      | -      | 32     | μA    | 1       |

Unless otherwise stated, GND standard, V<sub>DD</sub>=13V, V<sub>EN/DIM</sub>=V<sub>DD</sub>, V<sub>ISEN</sub>=GND, V<sub>SINE</sub>=5.5V

(\*1) I<sub>SEN</sub> pin voltage measured at start of GATE pin switching.

$^{(^{2})}$  Indicates V<sub>SINE</sub> pin voltage at which OFF TIME 6  $\mu$  s switching becomes possible.

$^{^{(*3)}}V_{\text{DD}}$  pin voltage measured when GATE pin=L occurs.

$^{^{(*4)}}V_{\text{DD}}$  pin voltage measured when GATE pin=H occurs.

(\*5) Indicates internal supply current when "H" level is input into EN/DIM pin and all circuits are activated. (When not switching.)

(\*6) Indicates internal supply current when "L" level is input into EN/DIM pin and the switching circuit is stopped.

$^{(^{77})}$  Indicates the current that discharges the capacitance between the V\_{DD} and GND pins at V\_{OVP}.

(\*8) Please refer to P.8 "CIRCUIT (4)".

<sup>(\*9)</sup> May not be fixed at  $6 \mu$  s when UVLO is detected or during DIM signal control.

(<sup>10)</sup> When the current limit voltage V<sub>LIM</sub> is exceeded, off time is extended to about 140  $\mu$  s to prevent element damage.

For details, refer to the operation description.

(\*11) To protect the IC from thermal destruction, thermal shutdown activates when the chip temperature reaches 150 °C and forcibly sets the GATE pin voltage to "L". When the chip temperature falls to 130 °C, operation resumes.

(\*12) Time from attainment of EN/DIM "L" voltage until GATE pin=L.

(\*13) Time from attainment of EN/DIM "H" voltage until GATE pin=H.

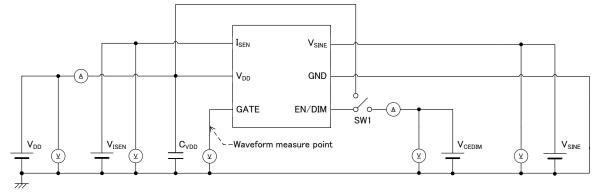

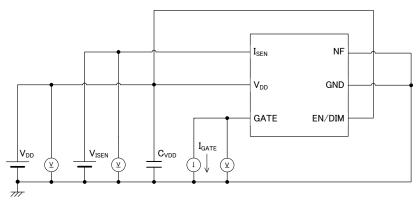

## ■TYPICAL APPLICATION CIRCUIT (Type A)

1) CIRCUIT

2) CIRCUIT<sup>2</sup>

4) CIRCUIT ④

TOIREX 7/19

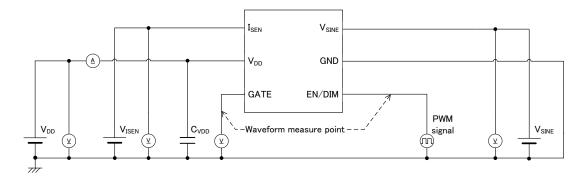

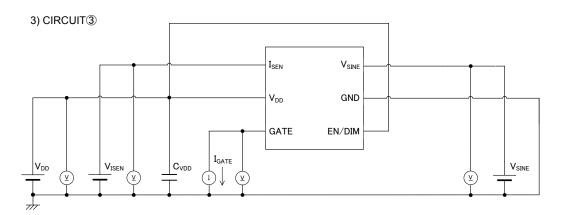

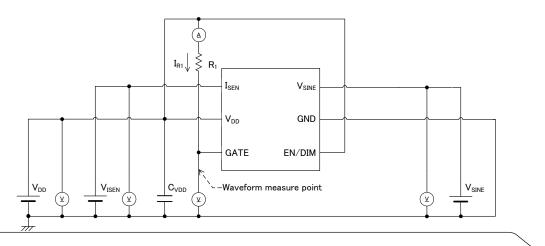

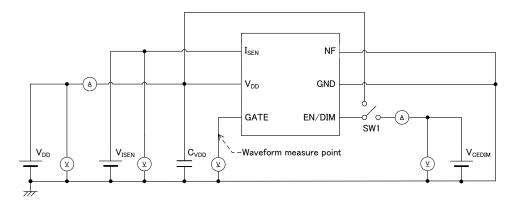

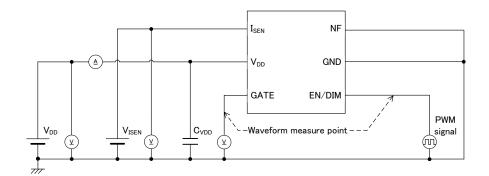

## ■TYPICAL APPLICATION CIRCUIT (Continued) (Type B)

1) CIRCUIT

2) CIRCUIT(2)

3) CIRCUIT③

4) CIRCUIT ④

8/19

## ■OPERATIONAL EXPLANATION

The internal circuitry of the XC9401 series consists of a reference voltage source (V<sub>REF</sub>), PWM comparator (PWMCMP), buffer drive circuit (Buffer Drive), over-current protection circuit (Over Current Limit), under-voltage lockout circuit (UVLO), V<sub>DD</sub> over voltage protection circuit (OVP), thermal shutdown circuit (Thermal Shutdown), and other circuits. (Refer to the block diagram.) The control method is fixed off-time control.

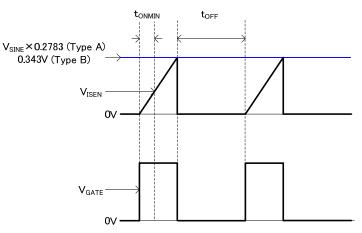

With type A, the PWM comparator compares the voltage at the  $I_{SEN}$  pin to that at the  $V_{SINE}$  pin x 0.2783 (TYP.) The output of the PWM comparator is connected to the buffer drive circuit and an external Power MOS FET drive signal is output from the GATE pin. When the  $I_{SEN}$  pin voltage is 0.2783 times (TYP.) higher than the  $V_{SINE}$  pin voltage, the GATE pin switches to low. After a fixed off-time elapses, the GATE pin switches to high. This operation is repeated continuously.

With type B, the PWM comparator compares the 0.343V (TYP.), which is 0.2783 times (TYP.) the reference voltage, to the  $I_{SEN}$  pin voltage.

Fig.1. Reference Circuit

## OPERATIONAL EXPLANATION (Continued)

Details of each circuit block are as follows.

#### <Reference voltage supply (V<sub>REF</sub>)>

Reference voltage that enables stable operation of the internal functions of the IC.

#### <PWM comparator (PWMCMP)>

With type A, the PWM comparator compares the voltage at the  $I_{SEN}$  pin to that at the  $V_{SINE}$  pin x 0.2783 (TYP.) When the  $I_{SEN}$  pin voltage is higher than  $V_{SINE} \times 0.2783$ , the GATE pin switches to low.

With type B, the PWM comparator compares the 0.343V (TYP.), which is 0.2783 times (TYP.) the reference voltage, to the I<sub>SEN</sub> pin voltage.

#### <Buffer drive circuit (Buffer Drive)>

This outputs an H or L signal from the GATE pin that drives the external Power MOS FET. The H level is the  $V_{DD}$  pin voltage, and the L level is the GND pin voltage. The signal that is output is determined by the PWM comparator, as well as by the below described UVLO circuit,  $V_{DD}$  over-voltage protection circuit, over-current protection circuit, thermal shutdown, and EN/DIM pin voltage.

#### <Enable / PWM Dimming (EN/DIM)>

When the power is turned on, it takes about  $200 \mu$  s (MAX.) for the GATE pin to initially become "H" after the EN/DIM pin voltage is changed from "L" to "H".

Inputting "L" to the EN/DIM pin voltage forcibly puts the GATE pin voltage in the "L" state. The stopped state when the EN/DIM pin voltage is "L" is not shutdown; rather, it is a Stand-by state wherein the switching pulse output is stopped by logic circuit and the internal circuitry continues to operate. For this reason, a high-speed response is possible even when a pulse signal (500 Hz to 1 kHz) is input to the EN/DIM pin, and by adjusting the duty width of the PWM signal input into the EN/DIM pin, the LED can be dimmed.

#### < Minimum on time controller circuit >

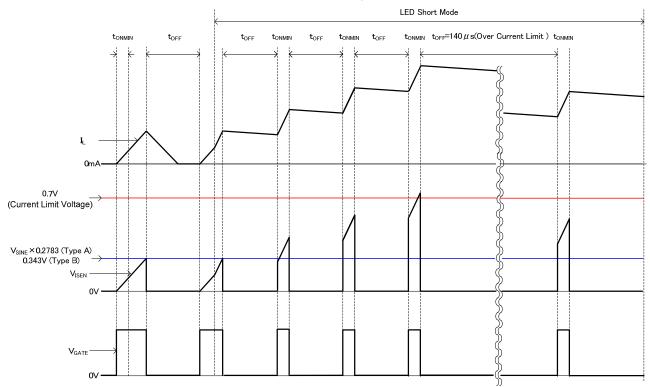

Spike noise and ripple noise occur in the XC9401 series due to switching. To prevent malfunction of the internal circuit by such noises, a minimum on time is established. The GATE pin voltage is forcibly kept at "H" until the minimum on time elapses. (Refer to Fig. 2.)

During the minimum on time, if the below described UVLO, OVP or thermal shutdown is detected, or if the Stand-by state is set from the EN/DIM pin, the GATE pin voltage is immediately changed to "L".

#### <Off Time Controller>

This circuit controls the fixed off time. The off time is normally fixed at  $6 \mu$  s (TYP.), and the GATE pin voltage is kept at "L" during this time. After the fixed off time, the GATE pin voltage becomes "H". (Refer to Fig. 2.)

If the EN/DIM pin voltage is changed from "L" to "H" during the above PWM dimming, the off time is  $140 \,\mu$  s (TYP.) during the over-current protection and ULVO release described below.

Fig.2. Off Time Controller, Min. On Time Controller

TOIREX 11/19

## OPERATIONAL EXPLANATION (Continued)

<Over Current Limit>

When the switching current of the external power MOSFET is in the over-current state and the  $I_{SEN}$  pin voltage reaches 0.7V (TYP.), L level voltage is output to the GATE pin and the external power MOSFET is turned off. In addition, the off time is temporarily extended from the normal 6.0  $\mu$  s (TYP.) to 140  $\mu$  s (TYP.). When the  $I_{SEN}$  pin voltage falls to 0.7V (TYP.) or less after the extended off time, normal operation resumes.

When LED+ and LED- short circuit in the reference circuit shown in Fig.1, the current slope of the coil (L2) becomes smaller during the off time than the slope during normal switching, which prevents sufficient discharge during the 6.0  $\mu$  s (TYP.) off time. During the minimum on time, the external power MOSFET Q1 always turns on, and thus the coil current gradually increases. The ISEN pin voltage becomes higher at the same time as the coil current increases, and when the ISEN pin voltage reaches 0.7V (TYP.), the off time is extended to 140  $\mu$  s (TYP.). (Refer to Fig.3)

Fig.3. Over Current Limit (Fig.1. Operation when LED+ and LED- short-circuit in the reference circuit)

<Under-voltage lockout circuit>

When the  $V_{DD}$  pin voltage falls to the UVLO Detect Voltage ( $V_{UVLO}$ ) or lower, the GATE pin voltage is forcibly set to "L" to prevent incorrect pulse output. When the  $V_{DD}$  pin voltage rises to the UVLO Release Voltage ( $V_{UVLOR}$ ) or higher, switching resumes.

A UVLO stop simply stops pulse output; it is not a shutdown state and the internal circuitry continues to operate.

#### <V<sub>DD</sub> over-voltage protection circuit>

When the  $V_{DD}$  pin voltage rises to the  $V_{DD}$  Overvoltage Protection Voltage ( $V_{OVP}$ ) or higher, the charge of the capacitance between the  $V_{DD}$  pin and GND pin is discharged by the resistance and transistor connected between the  $V_{DD}$  pin and GND pin in order to prevent withstand voltage destruction in the internal circuitry. The GATE pin voltage at this time is forcibly set to "L".

When the  $V_{DD}$  pin voltage falls to the  $V_{DD}$  Overvoltage Protection Release Voltage ( $V_{OVPR}$ ) or lower, switching is resumed.

#### <Thermal shutdown>

To protect the IC from thermal destruction, thermal shutdown activates when the chip temperature reaches 150 °C (TYP.) and forcibly sets the GATE pin voltage to "L". When the chip temperature falls to 130 °C (TYP.), switching is resumed.

## NOTE ON USE

- 1. For the phenomenon of temporal and transitional voltage decrease or voltage increase, the IC may be damaged or deteriorated if IC is used beyond the absolute MAX. specifications.

- 2. In a switching controller such as the XC9401 series, and in a peripheral circuit controlled by a switching controller, spike voltage and ripple voltage occur. These are greatly affected by the peripheral components (inductance value of the coil, capacitors, peripheral component board layout). During design, test sufficiently using the actual equipment.

- 3. A delay time of 200  $\mu$  s (MAX.) after the UVLO release voltage, and after EN/DIM pin voltage "H", has been established in the IC. Keep these delay times in mind during sequence design.

- 4. The NF pin of the XC9401B605MR-G is connected to part of the internal circuitry, although not as a circuit function. When using this IC, connect this pin to GND.

- 5. Make sure to use this IC within specified electric characteristics.

- 6. Please pay attention not to exceed absolute maximum ratings of this IC and external components.

- 7. To reduce  $V_{DD}$  fluctuations as much as possible, connect a bypass capacitor ( $C_{VDD}$ ) over the shortest path between  $V_{DD}$  and GND. If there is too much distance between the IC and  $C_{VDD}$ , operation may become unstable.

- 8. Please mount each external component as close to the IC as possible. Please also wire external components as close to the IC as possible and use thick, short connecting traces to reduce the circuit impedance.

- 9. Sufficiently reinforce the wiring between V<sub>DD</sub> and GND. Noise that enters through V<sub>DD</sub> and GND during switching may cause unstable IC operation.

- Torex places an importance on improving our products and their reliability. We request that users incorporate fail-safe designs and post-aging protection treatment when using Torex products in their systems.

### ■ TYPICAL PERFORMANCE CHARACTERISTICS

(1) Supply Current vs.  $V_{\text{DD}}$  Voltage

(3) Stand-by Current vs. V<sub>DD</sub> Voltage

## (5) EN/DIM Bias Current vs. EN/DIM Voltage

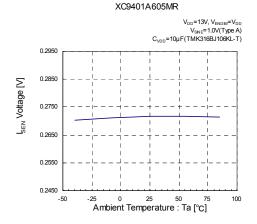

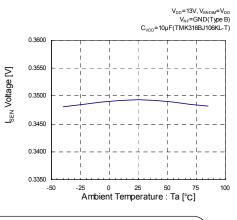

(7) I<sub>SEN</sub> Voltage vs. Ambient Temperature

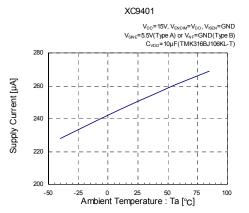

(2) Supply Current vs. Ambient Temperature

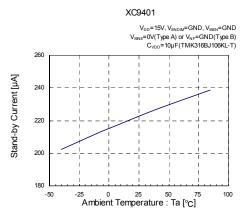

(4) Stand-by Current vs. Ambient Temperature

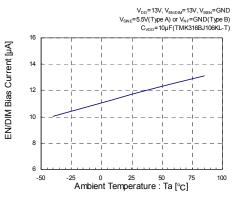

(6) EN/DIM Bias Current vs. Ambient Temperature

XC9401

#### XC9401B605MR

### **TYPICAL PERFORMANCE CHARACTERISTICS (Continued)**

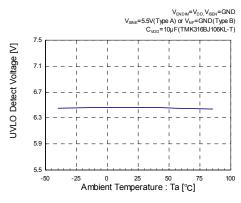

(8) UVLO Detect Voltage vs. Ambient Temperature

#### XC9401

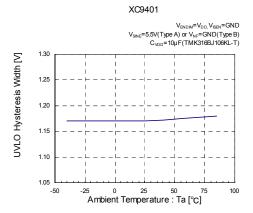

(10) UVLO Hysteresis Width vs. Ambient Temperature

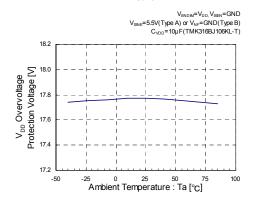

#### (11) V<sub>DD</sub> Overvoltage Protection Voltage

vs. Ambient Temperature XC9401

#### XC9401

(9) UVLO Release Voltage vs. Ambient Temperature

#### XC9401

#### (12) V<sub>DD</sub> Overvoltage Protection Release Voltage vs. Ambient Temperature

XC9401

### TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

(15) GATE "H" ON Resistance vs. Ambient Temperature

(16) GATE "L" ON Resistance vs. Ambient Temperature

(17) OFF Time vs. Ambient Temperature

GATE "H" ON Resistance [Ω]

(19) Current Limit Voltage vs. Ambient Temperature

(20) PWM Dimmer Delay Time1 vs. Ambient Temperature

(18) Minimum ON Time vs. Ambient Temperature

XC9401

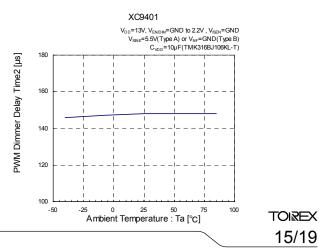

(21) PWM Dimmer Delay Time2 vs. Ambient Temperature

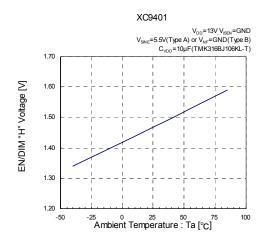

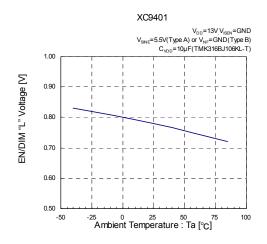

# (22) EN/DIM "H" Voltage vs. Ambient Temperature (23) EN/DIM "L" Voltage vs. Ambient Temperature

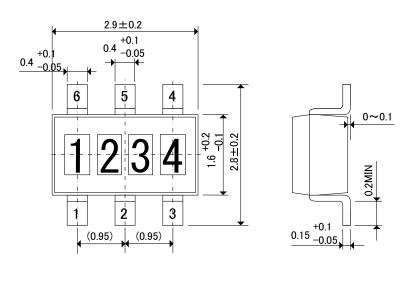

## ■ PACKAGING INFORMATION

●SOT-26 (unit: mm)

## ■MARKING RULE

#### ●SOT-26

#### 1 represents product series

| MARK | PRODUCT SERIES |

|------|----------------|

| 3    | XC9401*****-G  |

#### ②③ represents product type

| MARK |   | PRODUCT SERIES |

|------|---|----------------|

| 2    | 3 | PRODUCT SERIES |

| Α    | А | XC9401A605**-G |

| В    | А | XC9401B605**-G |

(4)(5) represents production lot number

01~09, 0A~0Z, 11~9Z, A1~A9, AA~AZ, B1~ZZ in order.

(G, I, J, O, Q, W excluded)

\*No character inversion used.

- 1. The products and product specifications contained herein are subject to change without notice to improve performance characteristics. Consult us, or our representatives before use, to confirm that the information in this datasheet is up to date.

- 2. We assume no responsibility for any infringement of patents, patent rights, or other rights arising from the use of any information and circuitry in this datasheet.

- 3. Please ensure suitable shipping controls (including fail-safe designs and aging protection) are in force for equipment employing products listed in this datasheet.

- The products in this datasheet are not developed, designed, or approved for use with such equipment whose failure of malfunction can be reasonably expected to directly endanger the life of, or cause significant injury to, the user.

(e.g. Atomic energy; aerospace; transport; combustion and associated safety equipment thereof.)

- Please use the products listed in this datasheet within the specified ranges.

Should you wish to use the products under conditions exceeding the specifications, please consult us or our representatives.

- 6. We assume no responsibility for damage or loss due to abnormal use.

- 7. All rights reserved. No part of this datasheet may be copied or reproduced without the prior permission of TOREX SEMICONDUCTOR LTD.

### TOREX SEMICONDUCTOR LTD.