### GeneSiC SEMICONDUCTOR

### GA50JT12-247

=

=

=

1200 V

1.4 V

50 A

28 mΩ

# Normally – OFF Silicon Carbide Junction Transistor

### Features

- 175 °C maximum operating temperature

- Temperature independent switching performance

- Gate oxide free SiC switch

- Suitable for connecting an anti-parallel diode

- Positive temperature coefficient for easy paralleling

- Low gate charge

- · Low intrinsic capacitance

## Package RoHS Compliant

$V_{\text{DS}}$

ID

V<sub>DS(ON)</sub>

R<sub>DS(ON)</sub>

### Advantages

- · Low switching losses

- Higher efficiency

- High temperature operation

- · High short circuit withstand capability

#### **Applications**

- Down Hole Oil Drilling, Geothermal Instrumentation

- Hybrid Electric Vehicles (HEV)

- Solar Inverters

- Switched-Mode Power Supply (SMPS)

- Power Factor Correction (PFC)

- Induction Heating

- Uninterruptible Power Supply (UPS)

- Motor Drives

### Maximum Ratings unless otherwise specified

| Parameter                         | Symbol           | Conditions                                                          | Values                                                            | Unit |

|-----------------------------------|------------------|---------------------------------------------------------------------|-------------------------------------------------------------------|------|

| Drain – Source Voltage            | V <sub>DS</sub>  | $V_{GS} = 0 V$                                                      | 1200                                                              | V    |

| Continuous Drain Current          | I <sub>D</sub>   | T <sub>C,MAX</sub> = 95 °C                                          | 50                                                                | А    |

| Gate Peak Current                 | I <sub>GM</sub>  |                                                                     | 10                                                                | А    |

| Turn-Off Safe Operating Area      | RBSOA            | $T_{VJ}$ = 175 °C, I <sub>G</sub> = 1 A,<br>Clamped Inductive Load  | I <sub>D,max</sub> = 50<br>@ V <sub>DS</sub> ≤ V <sub>DSmax</sub> | А    |

| Short Circuit Safe Operating Area | SCSOA            | $T_{VJ}$ = 175 °C, $I_G$ = 1 A, $V_{DS}$ = 800 V,<br>Non Repetitive | 20                                                                | μs   |

| Reverse Gate – Source Voltage     | V <sub>SG</sub>  | ·                                                                   | 30                                                                | V    |

| Reverse Drain – Source Voltage    | V <sub>SD</sub>  |                                                                     | 25                                                                | V    |

| Power Dissipation                 | P <sub>tot</sub> | T <sub>c</sub> = 95 °C                                              | 308                                                               | W    |

| Storage Temperature               | T <sub>stg</sub> |                                                                     | -55 to 175                                                        | °C   |

### Electrical Characteristics at T<sub>j</sub> = 175 °C, unless otherwise specified

| Devementer                   | Symbol              | Conditions -                                                                               | Values |      | Unit |      |  |

|------------------------------|---------------------|--------------------------------------------------------------------------------------------|--------|------|------|------|--|

| Parameter                    | Symbol              | Conditions                                                                                 | min.   | typ. | max. | Unit |  |

| On Characteristics           |                     |                                                                                            |        |      |      |      |  |

|                              |                     | $I_D$ = 50 A, $I_G$ = 1000 mA, $T_j$ = 25 °C                                               |        | 1.4  |      |      |  |

| Drain – Source On Voltage    | V <sub>DS(ON)</sub> | $I_D$ = 50 A, $I_G$ = 2000 mA, $T_j$ = 125 °C                                              |        | 1.6  |      | V    |  |

|                              |                     | $I_D$ = 50 A, $I_G$ = 4000 mA, $T_j$ = 175 °C                                              |        | 2.2  |      |      |  |

|                              |                     | I <sub>D</sub> = 50 A, I <sub>G</sub> = 1000 mA, T <sub>j</sub> = 25 °C                    |        | 28   |      |      |  |

| Drain – Source On Resistance | R <sub>DS(ON)</sub> | I <sub>D</sub> = 50 A, I <sub>G</sub> = 2000 mA, T <sub>j</sub> = 125 °C                   |        | 32   |      | mΩ   |  |

|                              | · · ·               | $I_D = 50 \text{ A}, I_G = 4000 \text{ mA}, T_j = 175 \text{ °C}$                          |        | 44   |      |      |  |

| Cata Fanward Valtaga         | N/                  | I <sub>G</sub> = 500 mA, T <sub>j</sub> = 25 °C                                            |        | 3.3  |      | V    |  |

| Gate Forward Voltage         | $V_{GS(FWD)}$       | I <sub>G</sub> = 500 mA, T <sub>j</sub> = 175 °C                                           |        | 3.1  |      | V    |  |

| DC Current Gain              | ρ                   | V <sub>DS</sub> = 5 V, I <sub>D</sub> = 50 A, T <sub>i</sub> = 25 °C                       |        | TBD  |      |      |  |

| DC Current Gain              | β                   | $V_{DS} = 5 \text{ V}, \text{ I}_{D} = 50 \text{ A}, \text{ T}_{j} = 175 ^{\circ}\text{C}$ |        | TBD  |      |      |  |

| Off Characteristics          |                     |                                                                                            |        |      |      |      |  |

|                              |                     | V <sub>R</sub> = 1200 V, V <sub>GS</sub> = 0 V, T <sub>j</sub> = 25 °C                     |        | 18   |      |      |  |

| Drain Leakage Current        | I <sub>DSS</sub>    | V <sub>R</sub> = 1200 V, V <sub>GS</sub> = 0 V, T <sub>j</sub> = 125 °C                    |        | 26   |      | μA   |  |

| -                            |                     | $V_R$ = 1200 V, $V_{GS}$ = 0 V, $T_j$ = 175 °C                                             |        | 35   |      | -    |  |

| Gate Leakage Current         | I <sub>SG</sub>     | V <sub>SG</sub> = 20 V, T <sub>i</sub> = 25 °C                                             |        | 20   |      | nA   |  |

### GA50JT12-247

### Electrical Characteristics at T<sub>j</sub> = 175 °C, unless otherwise specified

| Parameter                           | Symbol              | Symbol Conditions                                                                                                                                                                                 |      | Values |      | Unit |

|-------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|------|

| Parameter                           | Symbol              | Conditions                                                                                                                                                                                        | min. | typ.   | max. | Unit |

| Capacitance Characteristics         |                     |                                                                                                                                                                                                   |      |        |      |      |

| Gate-Source Capacitance             | C <sub>gs</sub>     | V <sub>GS</sub> = 0 V, f = 1 MHz                                                                                                                                                                  |      | tbd    |      | pF   |

| Input Capacitance                   | C <sub>iss</sub>    | $V_{GS}$ = 0 V, $V_{D}$ = 1 V, f = 1 MHz                                                                                                                                                          |      | tbd    |      | pF   |

| Reverse Transfer/Output Capacitance | $C_{rss}/C_{oss}$   | V <sub>D</sub> = 1 V, f = 1 MHz                                                                                                                                                                   |      | tbd    |      | pF   |

| Switching Characteristics           |                     |                                                                                                                                                                                                   |      |        |      |      |

| Turn On Delay Time                  | t <sub>d(on)</sub>  |                                                                                                                                                                                                   |      | tbd    |      | ns   |

| Rise Time                           | tr                  | $V_{DD} = 800 \text{ V}, \text{ I}_{D} = 50 \text{ A},$                                                                                                                                           |      | tbd    |      | ns   |

| Turn Off Delay Time                 | t <sub>d(off)</sub> | $R_{G(on)} = R_{G(off)} = 44 \Omega,$<br>V <sub>GS</sub> = -8/15 V, L = 1.1 mH,                                                                                                                   |      | tbd    |      | ns   |

| Fall Time                           | t <sub>f</sub>      | FWD = GB50SLT12.                                                                                                                                                                                  |      | tbd    |      | ns   |

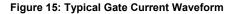

| Turn-On Energy Per Pulse            | Eon                 | T <sub>j</sub> = 25 °C<br>Refer to Figure 15 for gate current<br>waveform                                                                                                                         |      | tbd    |      | μJ   |

| Turn-Off Energy Per Pulse           | E <sub>off</sub>    |                                                                                                                                                                                                   |      | tbd    |      | μJ   |

| Total Switching Energy              | E <sub>ts</sub>     |                                                                                                                                                                                                   |      | tbd    |      | μJ   |

| Turn On Delay Time                  | t <sub>d(on)</sub>  |                                                                                                                                                                                                   |      | tbd    |      |      |

| Rise Time                           | tr                  | $V_{DD} = 800 \text{ V}, \text{ I}_{D} = 50 \text{ A},$                                                                                                                                           |      | tbd    |      | ns   |

| Turn Off Delay Time                 | t <sub>d(off)</sub> | $\begin{array}{c c} R_{G(on)} = R_{G(off)} = 44 \ \Omega, \\ V_{GS} = -8/15 \ V, L = 1.1 \ mH, \\ FWD = GB50SLT12, \\ T_{j} = 175 \ ^{\circ}C \\ \end{array}$ Refer to Figure 15 for gate current |      | tbd    |      | ns   |

| Fall Time                           | t <sub>f</sub>      |                                                                                                                                                                                                   |      | tbd    |      | ns   |

| Turn-On Energy Per Pulse            | Eon                 |                                                                                                                                                                                                   |      | tbd    |      | μJ   |

| Turn-Off Energy Per Pulse           | E <sub>off</sub>    |                                                                                                                                                                                                   |      | tbd    |      | μJ   |

| Total Switching Energy              | E <sub>ts</sub>     | waveform                                                                                                                                                                                          |      | tbd    |      | μJ   |

| Thermal resistance, junction - case | R <sub>thJC</sub> | 0.26 | °C/W |

|-------------------------------------|-------------------|------|------|

| monnal recletance, junction cace    | · (II)C           | 0.20 | 0.11 |

Figures

TBD

Figure 1: Typical Output Characteristics at 25 °C

Figure 2: Typical Output Characteristics at 125 °C

Figure 3: Typical Output Characteristics at 175 °C

Figure 4: Typical Gate Source I-V Characteristics vs. Temperature

**TBD**

Figure 5: Normalized On-Resistance and Current Gain vs. Temperature

Figure 6: Typical Blocking Characteristics

TBD

**Figure 7: Capacitance Characteristics**

Figure 8: Capacitance Characteristics

Figure 9: Typical Hard-switched Turn On Waveforms

Figure 10: Typical Hard-switched Turn Off Waveforms

**TBD**

Figure 11: Typical Turn On Energy Losses and Switching Times vs. Temperature

Figure 12: Typical Turn Off Energy Losses and Switching Times vs. Temperature

TBD

Figure 13: Typical Turn On Energy Losses vs. Drain Current Figure 14: Typical Turn Off Energy Losses vs. Drain Current

Figure 16: Typical Hard Switched Device Power Loss vs. Switching Frequency <sup>1</sup>

**TBD**

Figure 17: Power Derating Curve

Figure 18: Forward Bias Safe Operating Area

TBD

TBD

Figure 19: Turn-Off Safe Operating Area

Figure 20: Transient Thermal Impedance

<sup>1</sup> – Representative values based on device switching energy loss. Actual losses will depend on gate drive conditions, device load, and circuit topology.

### Gate Drive Technique (Option #1)

To drive the GA50JT12-247 with the lowest gate drive losses, please refer to the dual voltage source gate drive configuration described in Application Note AN-10B (http://www.genesicsemi.com/index.php/references/notes).

### Gate Drive Technique (Option #2)

The GA50JT12-247 can be effectively driven using the IXYS IXDN614 / IXDD614 non-inverting gate driver IC or a comparable product. A typical gate driver configuration along with component values using this driver is offered below. Additional information is available in GeneSiC Application Note AN-10A and from the manufacturer at www.ixys.com.

#### Figure 21: Recommended Gate Diver Configuration (Option #2)

| Parameter                           | Symbol Condit    | O and diffience | Values                 |      |                      | 11   |

|-------------------------------------|------------------|-----------------|------------------------|------|----------------------|------|

|                                     |                  | Conditions      | min.                   | typ. | max.                 | Unit |

| Option #2 Gate Drive Conditions (I) | (DD614/IXDN614)  |                 |                        |      |                      |      |

| Supply Voltage                      | V <sub>cc</sub>  |                 | -0.3                   | 15   | 40                   | V    |

| Gate Control Input Signal, Low      | IN               |                 | -5.0                   | 0    | 0.8                  | V    |

| Gate Control Input Signal, High     | IN               |                 | 3.0                    | 5.0  | V <sub>cc</sub> +0.3 | V    |

| Enable, Low                         | EN               | IXDD614 Only    |                        |      | 1/3*V <sub>cc</sub>  | V    |

| Enable, High                        | EN               | IXDD614 Only    | 2/3*V <sub>CC</sub>    |      |                      | V    |

| Output Voltage, Low                 | V <sub>OUT</sub> |                 |                        |      | 0.025                | V    |

| Output Voltage, High                | Vout             |                 | V <sub>CC</sub> -0.025 |      |                      | V    |

| Output Current, Peak                | I <sub>OUT</sub> | Package Limited |                        | tbd  | 14                   | Α    |

| Output Current, Continuous          | I <sub>OUT</sub> |                 |                        | tbd  | 4.0                  | А    |

| Gate Resistance  | R <sub>G</sub> | I <sub>G</sub> ≈ 0.5 A | 5 | tbd | Ω  |

|------------------|----------------|------------------------|---|-----|----|

| Gate Capacitance | C <sub>G</sub> | I <sub>G</sub> ≈ 0.5 A |   | tbd | nF |

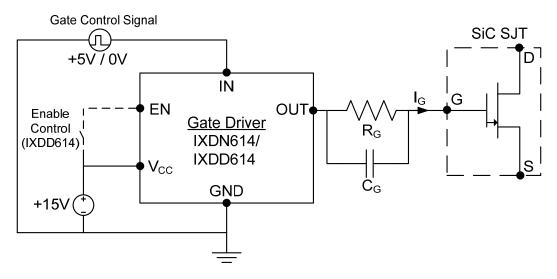

### GA50JT12-247

#### Package Dimensions:

#### NOTE

1. CONTROLLED DIMENSION IS INCH. DIMENSION IN BRACKET IS MILLIMETER.

2. DIMENSIONS DO NOT INCLUDE END FLASH, MOLD FLASH, MATERIAL PROTRUSIONS

| Revision History |          |                 |            |  |  |

|------------------|----------|-----------------|------------|--|--|

| Date             | Revision | Comments        | Supersedes |  |  |

| 2013/09/12       | 0        | Initial release |            |  |  |

|                  |          |                 |            |  |  |

Published by GeneSiC Semiconductor, Inc. 43670 Trade Center Place Suite 155 Dulles, VA 20166

GeneSiC Semiconductor, Inc. reserves right to make changes to the product specifications and data in this document without notice.

GeneSiC disclaims all and any warranty and liability arising out of use or application of any product. No license, express or implied to any intellectual property rights is granted by this document.

Unless otherwise expressly indicated, GeneSiC products are not designed, tested or authorized for use in life-saving, medical, aircraft navigation, communication, air traffic control and weapons systems, nor in applications where their failure may result in death, personal injury and/or property damage.

### **SPICE Model Parameters**

Copy the following code into a SPICE software program for simulation of the GA50JT12 SJT device.

```

*

MODEL OF GeneSiC Semiconductor Inc.

*

*

$Revision: 1.0

$

*

$Date: 26-AUG-2013

$

*

*

GeneSiC Semiconductor Inc.

*

43670 Trade Center Place Ste. 155

*

Dulles, VA 20166

*

http://www.genesicsemi.com/index.php/sic-products/sjt

*

*

COPYRIGHT (C) 2013 GeneSiC Semiconductor Inc.

*

ALL RIGHTS RESERVED

* These models are provided "AS IS, WHERE IS, AND WITH NO WARRANTY

* OF ANY KIND EITHER EXPRESSED OR IMPLIED, INCLUDING BUT NOT LIMITED

* TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A

* PARTICULAR PURPOSE."

* Models accurate up to 2 times rated drain current.

.model GA50JT12 NPN

+ IS

5.00E-47

+ ISE

1.26E-28

+ EG

3.2

100

+ BF

+ BR

0.55

+ IKF

3500

+ NF

1

+ NE

2

0.26

+ RB

+ RE

0.01

+ RC

0.011

1.75E-9

+ CJC

+ VJC

3

+ MJC

0.5

+ CJE

5.57E-9

+ VJE

3

0.5

+ MJE

3

+ XTI

+ XTB

-1.2

+ TRC1

7.00E-3

+ VCEO

1200

+ ICRATING 50

+ MFG GeneSiC_Semiconductor

*

* End of GA50JT12 SPICE Model

```