#### Introduction

The Pyxos platform is a high-speed sensor network ideal both for stand-alone applications and the ones extending LonWorks® networks down to sensor and actuator I/Os. It can be used inside machines and in other high-performance systems.

Pyxos embedded control networks reduce product installation, warranty, and life-cycle costs. Pyxos self-organizing networks reduce installation costs and equipment assembly time by eliminating the need to use special tools or skilled labor for network configuration. This minimizes material and labor costs. The remote diagnostics afforded by the Pyxos platform enable new features that let manufacturers access low-level data from sensors and actuators, such as process efficiency and energy usage. Employing these features for preventive and predictive maintenance provides reduced life-cycle costs and improved customer service.

The Pyxos FT network chip embeds both the protocol for a Pyxos platform and the transceiver for communicating on the Pyxos network. With the networking protocol implemented inside the chip, only application development is left to the user. The chip has a small size (5mm x 5mm) that fits into virtually any sensor or actuator. The chip can be connected directly to digital I/O without a microcontroller, making for an ultra-compact smart

### Pyxos™ FT Network Chip 11500R

- ▼ Low-cost embedded control networking chip for use inside machines and for extending control networks to high-performance sensor networks

- Miniaturized form factor fits into almost every sensor and actuator

- ▼ Extensible architecture for seamless integration with LonWorks® control networks and the Internet

- ▼ Self-organizing feature configures the network without special tools or skilled labor

- ▼ High-speed deterministic operation (≤ 25ms response time)

- ▼ 312.5kbps network transmission speed

- ▼ Polarity-insensitive, free topology, twisted pair wiring

- ▼ Link power allows sending communication and power over same pair of wires

- ▼ Robust performance ideal for industrial and consumer products and applications including automotive, buildings, office machines, and transportation

- ▼ Exceptional data integrity with forward error correction and 18-bit packet CRC

- Exceptionally high common mode noise and interference immunity

- ▼ Network pins ESD protection to over 8kV HBM

- ▼ -40°C to +85°C operating temperature range

- ▼ 20 Pin QFN 5mm x 5mm package

- **▼** RoHS-compliant

device. Alternately, the chip's serial peripheral interface (SPI) port can be interfaced with a wide variety of low-cost microcontrollers to accommodate more complex I/O requirements.

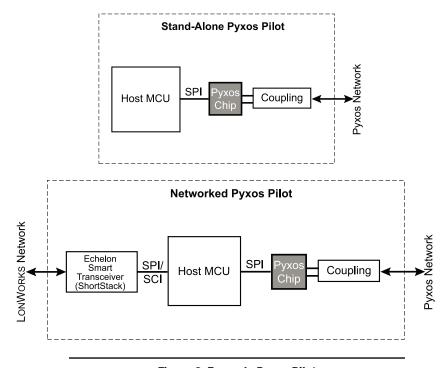

# **Network Architecture and Components**

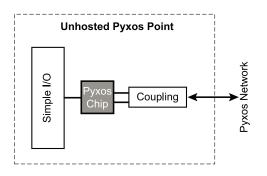

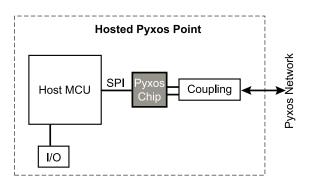

A Pyxos FT network consists of up to 32 Pyxos Points embedded inside sensors and actuators, and a Pyxos Pilot to interface with the outside world or other Pyxos Pilots. Points (Figure 2) can either be *unhosted* (without a micro-

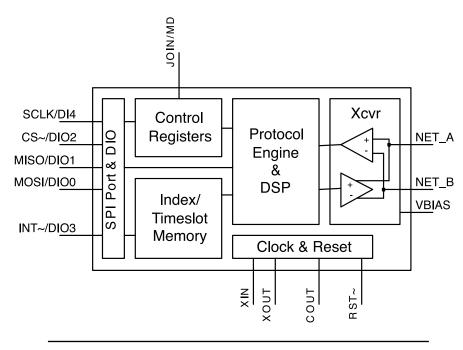

Figure 1. Pyxos FT Transceiver Block Diagram

controller; with only digital I/Os) or *hosted* (with a microcontroller). Pilots (Figure 3) need a microcontroller and can either be *stand-alone* (not connected to any external network) or *networked* (connected to a higher-level external network e.g., LonWorks to communicate with the outside world or with other Pyxos Pilots).

#### **High Speed Deterministic Response Time**

A Pyxos FT network operates at 312.5 kilobits per second using a deterministic signaling method by which all 32 Points in the system are scanned every 25 milliseconds (proportionally faster with fewer Points in the system). This rate of speed allows Pyxos FT networks to be used for closed-loop controls in process and industrial applications, as well as sensing and control applications that require fast response time.

Potential applications include:

- vehicular controls

- fault monitors

- propulsion controls

- HVAC systems

- lighting systems

- burner and boiler controls

- security and fire/life safety devices

- elevator cab and floor call controls

- office automation equipment

#### **Advanced Noise Immunity**

Four different network coupling options are available to cover a wide variety of application environments. For applications within an enclosure, the differential receiver in the Pyxos FT IC provides rail-to-rail common mode range and may be connected directly to the network with no additional components. For network applications where AC mains based common mode noise may be tens of volts, a simple 4 component coupling circuit provides +/-40V 50/60Hz common mode range (far better than typical RS-485 transceivers). For extremely harsh noise environments a transformer coupled option provides a common mode range of 277VAC at 50/60Hz and >50Vpp immunity to higher frequency common mode noise - passing the highest level of EN61000-4-6 conducted RF immunity.

# Free Topology Wiring and Link Power

A Pyxos FT network sends both power and data on the same wire pair, a feature known as "Link Power". Link power eliminates the need for an additional pair of power wires and interface terminals, further reducing the cost, size, and complexity of Pyxos FT Points. Pyxos FT

networks support free topology wiring architecture that allows network cabling in star, loop, daisy chain, or bus topology or any combination of these. Free topology wiring reduces the time and expense of device installation by allowing the wiring to be installed in the most expeditious and cost-effective manner.

#### **Seamless Integration with Outside World**

Control information gathered from Pyxos FT Points is disseminated by a Pyxos FT Pilot to programmable logic controllers (PLCs), data gathering panels, host processors, LonWorks control networks, the Internet, and beyond. The published API makes it easy to interface with the Pyxos Pilot. The Pyxos API uses the same data type definitions as those developed for LonWorks networks, making integration with LonWorks networks seamless.

#### **Block Diagrams**

Figure 2. Example Pyxos Point

Figure 3. Example Pyxos Pilot

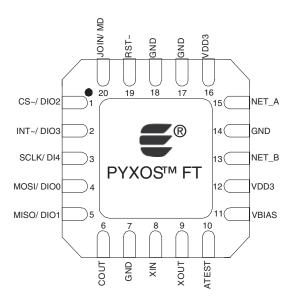

# **Pin Configuration**

Note: There is an exposed die paddle (Pin 21) on the underside of the chip package. This must not be connected to any voltage or signal line on the PCB.

| Name       | Pin Number | Туре           | Pin Description             |

|------------|------------|----------------|-----------------------------|

| CS~/ DIO2  | 1          | Digital I/O    | Chip Select Input or DIO2   |

| INT~/ DIO3 | 2          | Digital I/O    | Interrupt Output or DIO3    |

| SCLK/ DI4  | 3          | Digital In     | SPI Clock Input or DI4      |

| MOSI/ DIO0 | 4          | Digital I/O    | SPI Input or DIO0           |

| MISO/ DIO1 | 5          | Digital I/O    | SPI Output or DIO1          |

| COUT       | 6          | Digital Out    | Clock output/tri-state      |

| GND        | 7          | Ground         | Ground                      |

| XIN        | 8          | Osc In         | Crystal Oscillator In       |

| XOUT       | 9          | Osc Out        | Crystal Oscillator Out      |

| ATEST      | 10         | Analog I/O     | Analog Test                 |

| VBIAS      | 11         | Analog Out     | Network Bias Voltage Output |

| VDD3       | 12         | Power          | 3.3V Power                  |

| NET_B      | 13         | Analog I/O     | Network TX/RX               |

| GND        | 14         | Ground         | Ground                      |

| NET_A      | 15         | Analog I/O     | Network TX/RX               |

| VDD3       | 16         | Power          | 3.3V Power                  |

| GND        | 17         | Ground         | Ground                      |

| GND        | 18         | Ground         | Ground                      |

| RST~       | 19         | Digital I/O    | Reset Input/Output          |

| JOIN/MD    | 20         | Digital In     | Join/Mode pin Input         |

| PAD        | 21         | Do Not Connect | Do Not Connect              |

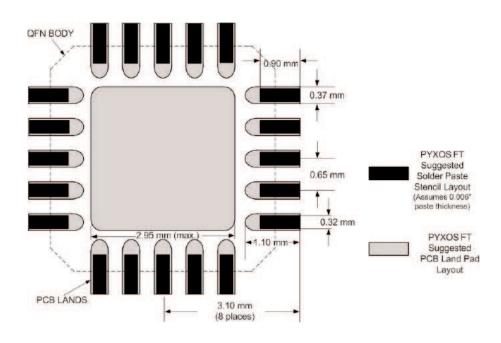

# **Pad Layout**

The center pad in the pad layout is connected to ground. However, the solder stencil mask isolates the center pad on the PCB from the exposed die paddle on the underside of the chip.

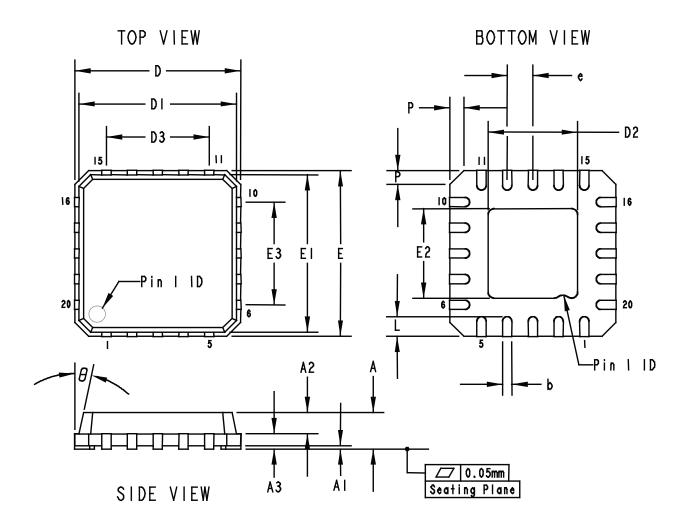

# **Package Diagrams**

| Symbol | mm (prevailing dimensions) |          |      | Inch      |           |        |

|--------|----------------------------|----------|------|-----------|-----------|--------|

|        | Min.                       | Nom.     | Max. | Min.      | Nom.      | Max.   |

| A      | -                          | 0.85     | 1.00 | -         | 0.033     | 0.039  |

| Al     | -                          | 0.01     | 0.05 | -         | 0.0004    | 0.0020 |

| A2     | -                          | 0.65     | 0.80 | ,         | 0.025     | 0.031  |

| A3     | -                          | 0.20 REF | -    | -         | 0.008 REF | -      |

| b      | 0.23                       | 0.28     | 0.35 | 0.009     | 0.011     | 0.014  |

| D      | 5.00 BSC                   |          |      | 0.197 BSC |           |        |

| DI     | 4.75 BSC                   |          |      | 0.187 BSC |           |        |

| D2     | 2.95                       | 3.10     | 3.25 | 0.116     | 0.122     | 0.128  |

| D3     | 2.60 BSC                   |          |      | 0.102 BSC |           |        |

| ė      | 0.65 BSC                   |          |      | 0.026 BSC |           |        |

| E      | 5.00 BSC                   |          |      | 0.197 BSC |           |        |

| El     | 4.75 BSC                   |          |      | 0.187 BSC |           |        |

| E2     | 2.95                       | 3.10     | 3.25 | 0.116     | 0.122     | 0.128  |

| E3     | 2.60 BSC                   |          |      | 0.102 BSC |           |        |

| L      | 0.50                       | 0.60     | 0.75 | 0.020     | 0.024     | 0.030  |

| P      | 0.24                       | 0.42     | 0.60 | 0.009     | 0.017     | 0.024  |

| θ      |                            | -        | 12°  | -         | -         | l 2°   |

# **General Specifications**

| denotal openitoations                                         |                                                                                                                                                                                                  |  |  |  |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Features                                                      | Description                                                                                                                                                                                      |  |  |  |

| Network Connections                                           | Polarity-insensitive                                                                                                                                                                             |  |  |  |

| Protocol                                                      | Deterministic TDM protocol with automatic retries on CRC error                                                                                                                                   |  |  |  |

| Response Time (reading and writing                            | ≤25ms scan time for up to 32 Points. Scan time is proportionally faster                                                                                                                          |  |  |  |

| two 4-byte values in each scan)                               | with less Pyxos Points, e.g., 1.8ms for two Pyxos Points in the system                                                                                                                           |  |  |  |

| Data Integrity                                                | Forward error correction of up to 2 bit errors per packet; 18 bit packet CRC                                                                                                                     |  |  |  |

| MAC ID                                                        | Built-in                                                                                                                                                                                         |  |  |  |

| Installation                                                  | Self-organizing network with automatic, hardwired, or manual service-pin methods                                                                                                                 |  |  |  |

| Maximum Pyxos Points per Pyxos Pilot                          | 32                                                                                                                                                                                               |  |  |  |

| Transmission Speed                                            | 312.5 kilobits per second, fixed polling cycle                                                                                                                                                   |  |  |  |

| Pyxos Network Variables (PNVs)<br>per hosted Pyxos Point      | Up to 128 PNVs per Pyxos Point. A maximum of 512 bytes may be used for PNVs, with memory allocated in 32-bit increments. A PNV may be 1 to 32 bytes.                                             |  |  |  |

| LonWorks Network Variables per Pyxos Pilot                    | 62 when using ShortStack, 4096 when using MIP                                                                                                                                                    |  |  |  |

| Network Wiring                                                | Unshielded CAT-5 24AWG (0.5mm) and Belden 8471 16AWG (1.3mm) twisted pair wire; see Junction Box and Wiring Guidelines application note for cable details                                        |  |  |  |

| Network Length in Free Topology                               | Free Topology (Single termination): 100m (328 feet) maximum total wire Bus Topology (Double termination): 400m (1312 feet) maximum; 0.3m (1 foot) maximum stub lengths                           |  |  |  |

| Link Power                                                    | Supports 24VAC or 24VDC link power with optional external components; reference designs provided for both switching and linear power supplies  Application Output Current: up to 100mA @ 3.3V DC |  |  |  |

| Coupling Options                                              | Direct Connect (for applications within a single enclosure)                                                                                                                                      |  |  |  |

| Couping Options                                               | Non-isolated/Grounded                                                                                                                                                                            |  |  |  |

|                                                               | Non-isolated/Floating                                                                                                                                                                            |  |  |  |

|                                                               | Transformer-isolated (very high common mode and interference immunity)                                                                                                                           |  |  |  |

| EMI                                                           | Designed to comply with FCC Part 15 Level A and EN55022 Level A                                                                                                                                  |  |  |  |

| ESD                                                           | Designed to comply with 61000-4-2 Level 4 (contact - 8kV; air - 15kV)                                                                                                                            |  |  |  |

| ESD Human Body Model (MIL-STD-883) (for pins NET_A and NET_B) | 8kV                                                                                                                                                                                              |  |  |  |

| Radiated Electromagnetic Susceptibility                       | Designed to comply with 61000-4-3 Level 3 (10V/m)                                                                                                                                                |  |  |  |

| Fast Transient/Burst Immunity                                 | Designed to comply with 61000-4-4 Level 4 (2kV)                                                                                                                                                  |  |  |  |

| Surge Immunity                                                | Designed to comply with 61000-4-5 Level 3 (2kV)                                                                                                                                                  |  |  |  |

| Conducted RF Immunity                                         | Designed to comply with 61000-4-6 Level 3 (10Vrms)                                                                                                                                               |  |  |  |

| Common Mode Range (0 – 60Hz)                                  | 277Vrms with Transformer-isolated coupling                                                                                                                                                       |  |  |  |

|                                                               | +/-40V with Non-isolated/Grounded coupling                                                                                                                                                       |  |  |  |

| I/O                                                           | 4 digital I/Os and 1 digital input without a microcontroller (unhosted), 8mA drive, 5V tolerant for LEDs, digital I/O, and transistors                                                           |  |  |  |

| Pyxos Host Microcontroller Interface                          | SPI (Serial Peripheral Interface)                                                                                                                                                                |  |  |  |

| Package                                                       | 20 Pin QFN 5mm x 5mm package                                                                                                                                                                     |  |  |  |

| Operating Voltage                                             | $3.3V \pm 10\%$                                                                                                                                                                                  |  |  |  |

| Operating Temperature                                         | -40°C to +85°C                                                                                                                                                                                   |  |  |  |

### **Ordering Information**

| Echelon Model Number                |  |  |  |

|-------------------------------------|--|--|--|

| 11500R-300 (Dry Pack of Five Tubes) |  |  |  |

| 11500R-5000 (Tape and Reel Package) |  |  |  |

| 11500R-ES                           |  |  |  |

| 11000R-10-1P                        |  |  |  |

| Model Number                        |  |  |  |

| TMS80040CS                          |  |  |  |

|                                     |  |  |  |

TMS60563CS

Transtek Magnetics 1900 W. Grant Road Tuscon, AZ, USA 85745 (800) 378 0015

Switching Power Supply Transformer\*

Copyright © 2007, Echelon Corporation. Echelon, LON, LonWorks, LonMark, LonBuilder, NodeBuilder, LonManager, LonTalk, LonUsers, LonPoint, Digital Home, Neuron, 3120, 3150, LNS, /LON, LonWorko, ShortStack, Panoramix, Panoramix Powered by Echelon, LonMaker, the Echelon logo, and the LonUsers logo are trademarks of Echelon Corporation registered in the United States and other countries. Pyxos, LonLink, LonResponse, LonSupport, LONews, Open Systems Alliance, OpenLDV, LonBridge, Powered by Echelon, LNS Powered by Echelon, LonWorks Powered by Echelon, Networked Energy Services Powered by Echelon, NES Powered by Echelon, and Thinking Inside the Box are trademarks of Echelon Corporation. Other trademarks belong to their respective holders.

DISCLAIMER

PYXOS FT CHIPS, NEURON CHIPS, FREE TOPOLOGY TWISTED PAIR TRANSCEIVER MODULES, AND OTHER OEM PRODUCTS WERE NOT DESIGNED FOR USE IN EQUIPMENT OR SYSTEMS INTENDED FOR SURGICAL IMPLANT INTO THE BODY, OR OTHER APPLICATIONS INTENDED TO SUPPORT OR SUSTAIN LIFE, FOR USE IN FLIGHT CONTROL OR ENGINE CONTROL EQUIPMENT WITHIN AN AIRCRAFT, OR FOR ANY OTHER APPLICATION THAT INVOLVES DANGER TO HUMAN HEALTH OR SAFETY OR A RISK OF PROPERTY DAMAGE. ECHELON ASSUMES NO RESPONSIBILITY OR LIABILITY FOR USE OF THE PYXOS FT CHIPS, NEURON CHIPS OR FREE TOPOLOGY TWISTED PAIR TRANSCEIVER MODULES IN SUCH APPLICATIONS. ECHELON SPECIFICALLY DISCLAIMS ANY IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. ECHELON SHALL NOT BE LIABLE TO ANY USER OF THE PYXOS FT CHIPS, NEURON CHIPS, OR FREE TOPOLOGY TWISTED PAIR TRANSCEIVER MODULES FOR ANY LOST PROFITS OR OTHER SPECIAL, CONSEQUENTIAL, INDIRECT, PUNITIVE OR INCIDENTAL DAMAGES, HOWEVER CAUSED ON ANY THEORY OF LIABILITY, ARISING IN ANY WAY OUT OF THE DEVELOPMENT OR DISTRIBUTION OF APPLICATIONS OR SYSTEMS USING SUCH PRODUCTS.

<sup>\*</sup> Available from: