|                                                                                                                                                |                                                                     |                                                                                                              |                                                                                                         |                                       |                                                                        |                                                                                    |                                                  | ł                     | REVISI              | ONS                              |                    |                                                                                                                                      |                                                                   |                                              |                                          |                                           |                                        |                              |                      |               |

|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------|---------------------|----------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------|------------------------------------------|-------------------------------------------|----------------------------------------|------------------------------|----------------------|---------------|

| LTR                                                                                                                                            |                                                                     |                                                                                                              |                                                                                                         |                                       | [                                                                      | DESCR                                                                              | RIPTIO                                           | N                     |                     |                                  |                    |                                                                                                                                      | DATE (YR-MO-DA)                                                   |                                              |                                          | APPROVED                                  |                                        |                              |                      |               |

| С                                                                                                                                              |                                                                     | onvert drawing to new boilerplate. Corrected vendor simil<br>endor CAGE 34335. Editorial changes throughout. |                                                                                                         |                                       |                                                                        |                                                                                    |                                                  |                       |                     | r part n                         | umber              | for                                                                                                                                  | 90-02-06                                                          |                                              |                                          |                                           | W. Heckman                             |                              | I                    |               |

| D                                                                                                                                              | -                                                                   |                                                                                                              |                                                                                                         | dance w                               |                                                                        |                                                                                    |                                                  |                       |                     |                                  | 00-07-07           |                                                                                                                                      | Monica L. Poelking                                                |                                              | ing                                      |                                           |                                        |                              |                      |               |

| E                                                                                                                                              |                                                                     |                                                                                                              |                                                                                                         |                                       | n D and updated boilerplate and editoria vendor CAGE CODE 3V146. – LTG |                                                                                    |                                                  |                       |                     |                                  | jes                |                                                                                                                                      |                                                                   | 00-0                                         | )9-27                                    |                                           | Monica L. Poelking                     |                              | ling                 |               |

| F                                                                                                                                              | Corre<br>MIL-I                                                      | ect mar<br>PRF-38                                                                                            | king requirements in 3.5. Update boilerplate in act<br>S535 requirements. Editorial changes throughout. |                                       |                                                                        |                                                                                    |                                                  |                       | accorda<br>t PH     | ance wi<br>IN.                   | th                 |                                                                                                                                      | 05-0                                                              | )2-24                                        |                                          | 1                                         | Thomas M. Hess                         |                              | SS                   |               |

| G                                                                                                                                              | 1.2.2                                                               | ect cas<br>Corre<br>Y to SF                                                                                  | ect the                                                                                                 | ne Z ter<br>figure 2<br>CFS.          | minal c<br>2 case :                                                    | ount ar<br>Z termi                                                                 | nd deso<br>nal des                               | criptive<br>scription | design<br>n for loc | ator in<br>cation (              | paragra<br>C11 fro | aph<br>m                                                                                                                             |                                                                   | 07-0                                         | 08-16                                    |                                           | 1                                      | Thomas                       | s M. He              | SS            |

|                                                                                                                                                |                                                                     |                                                                                                              |                                                                                                         |                                       |                                                                        |                                                                                    |                                                  |                       |                     |                                  |                    |                                                                                                                                      |                                                                   |                                              |                                          |                                           |                                        |                              |                      |               |

|                                                                                                                                                |                                                                     |                                                                                                              |                                                                                                         |                                       |                                                                        |                                                                                    |                                                  |                       |                     |                                  |                    |                                                                                                                                      |                                                                   |                                              |                                          |                                           |                                        |                              |                      |               |

| REV                                                                                                                                            | 1                                                                   |                                                                                                              | ŀ                                                                                                       | I                                     |                                                                        |                                                                                    | i                                                | 1                     | 1                   |                                  | 1                  | 1                                                                                                                                    | I                                                                 | 1                                            | 1                                        | 1                                         | 1                                      | 1                            | ł                    | 1             |

| REV                                                                                                                                            |                                                                     |                                                                                                              |                                                                                                         |                                       |                                                                        |                                                                                    |                                                  |                       |                     |                                  |                    |                                                                                                                                      |                                                                   |                                              |                                          |                                           |                                        |                              |                      |               |

| SHEET                                                                                                                                          | F                                                                   | F                                                                                                            | F                                                                                                       | F                                     | F                                                                      | F                                                                                  | F                                                | F                     | F                   | F                                | F                  | F                                                                                                                                    | F                                                                 | F                                            | F                                        | F                                         | F                                      | F                            | F                    | F             |

| SHEET<br>REV                                                                                                                                   | E<br>15                                                             | E<br>16                                                                                                      | E<br>17                                                                                                 | F<br>18                               | F<br>19                                                                | F<br>20                                                                            | F<br>21                                          | F<br>22               | F<br>23             | F<br>24                          | F<br>25            | F<br>26                                                                                                                              | F<br>27                                                           | F<br>28                                      | F<br>29                                  | F<br>30                                   | F<br>31                                | F<br>32                      | F<br>33              | F<br>34       |

| SHEET                                                                                                                                          | E<br>15                                                             | E<br>16                                                                                                      | E<br>17                                                                                                 | F<br>18<br>REV                        | 19                                                                     | F<br>20                                                                            | F<br>21<br>G                                     | F<br>22<br>G          | F<br>23<br>F        | F<br>24<br>F                     | F<br>25<br>E       | F<br>26<br>E                                                                                                                         | F<br>27<br>E                                                      | F<br>28<br>E                                 | F<br>29<br>E                             | F<br>30<br>E                              | F<br>31<br>E                           | F<br>32<br>E                 | F<br>33<br>E         | F<br>34<br>G  |

| SHEET<br>REV<br>SHEET                                                                                                                          |                                                                     |                                                                                                              |                                                                                                         | 18                                    | 19                                                                     |                                                                                    | 21                                               | 22                    | 23                  | 24                               | 25                 | 26                                                                                                                                   | 27                                                                | 28                                           | 29                                       | 30                                        | 31                                     | 32                           | 33                   | 34            |

| SHEET<br>REV<br>SHEET<br>REV STATUS                                                                                                            |                                                                     |                                                                                                              |                                                                                                         | 18<br>REV<br>SHE                      | 19                                                                     | 20                                                                                 | 21<br>G                                          | 22<br>G               | 23<br>F             | 24<br>F                          | 25<br>E            | 26<br>E                                                                                                                              | 27<br>E                                                           | 28<br>E                                      | 29<br>E                                  | 30<br>E                                   | 31<br>E                                | 32<br>E                      | 33<br>E              | 34<br>G       |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A                                                                                   | 15                                                                  | 16                                                                                                           |                                                                                                         | 18<br>REV<br>SHE                      | 19<br>/<br>ET<br>PARED                                                 | 20<br>D BY                                                                         | 21<br>G                                          | 22<br>G<br>2          | 23<br>F             | 24<br>F                          | 25<br>E<br>5       | 26<br>E<br>6<br>EFEN                                                                                                                 | 27<br>E<br>7<br>SE SI                                             | 28<br>E<br>8                                 | 29<br>E<br>9                             | 30<br>E<br>10                             | 31<br>E<br>11                          | 32<br>E<br>12                | 33<br>E<br>13        | 34<br>G       |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STAI                                                                           | 15<br>NDAF                                                          | 16<br><b>RD</b>                                                                                              |                                                                                                         | 18<br>REV<br>SHE<br>PRE               | 19<br>/<br>ET<br>PARED                                                 | 20<br>D BY<br>Jeffery                                                              | 21<br>G<br>1                                     | 22<br>G<br>2          | 23<br>F             | 24<br>F                          | 25<br>E<br>5       | 26<br>E<br>6<br>EFEN                                                                                                                 | 27<br>E<br>7<br>SE SI                                             | 28<br>E<br>8<br>UPPL                         | 29<br>E<br>9<br>Y CE<br>, OHI            | 30<br>E<br>10<br>NTEF<br>O 432            | 31<br>E<br>11<br>R COL<br>218-3        | 32<br>E<br>12                | 33<br>E<br>13        | 34<br>G       |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STAI<br>MICRC                                                                  | 15<br>NDAF<br>DCIR(                                                 | 16<br>RD<br>CUIT                                                                                             |                                                                                                         | 18<br>REV<br>SHE<br>PRE               | 19<br>/<br>EET<br>PARED                                                | 20<br>D BY<br>Jeffery<br>BY                                                        | 21<br>G<br>1                                     | 22<br>G<br>2          | 23<br>F             | 24<br>F                          | 25<br>E<br>5       | 26<br>E<br>6<br>EFEN                                                                                                                 | 27<br>E<br>7<br>SE SI                                             | 28<br>E<br>8<br>UPPL                         | 29<br>E<br>9<br>Y CE<br>, OHI            | 30<br>E<br>10                             | 31<br>E<br>11<br>R COL<br>218-3        | 32<br>E<br>12                | 33<br>E<br>13        | 34<br>G       |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STAI<br>MICRC                                                                  | 15<br>NDAF                                                          | 16<br>RD<br>CUIT                                                                                             |                                                                                                         | 18<br>REV<br>SHE<br>PRE<br>CHE        | 19<br>/<br>EET<br>PARED                                                | 20<br>D BY<br>Jeffery<br>BY<br>Tim H                                               | 21<br>G<br>1<br>Tunsta                           | 22<br>G<br>2          | 23<br>F             | 24<br>F                          | 25<br>E<br>5       | 26<br>E<br>6<br>EFEN                                                                                                                 | 27<br>E<br>7<br>SE SI                                             | 28<br>E<br>8<br>UPPL                         | 29<br>E<br>9<br>Y CE<br>, OHI            | 30<br>E<br>10<br>NTEF<br>O 432            | 31<br>E<br>11<br>R COL<br>218-3        | 32<br>E<br>12                | 33<br>E<br>13        | 34<br>G       |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STAI<br>MICRC<br>DRA<br>THIS DRAWIN<br>FOR US                                  | 15<br>NDAF<br>DCIRC<br>AWIN                                         | 16<br>RD<br>CUIT<br>G<br>VAILAI                                                                              | 17                                                                                                      | 18<br>REV<br>SHE<br>PRE<br>CHE        | 19<br>//<br>PAREE<br>CKED                                              | 20<br>D BY<br>Jeffery<br>BY<br>Tim F<br>D BY                                       | 21<br>G<br>1<br>Tunsta                           | 22<br>G<br>2          | 23<br>F             | 24<br>F<br>4                     | 25<br>E<br>5       | 26<br>E<br>6<br>EFEN<br>C(                                                                                                           | 27<br>E<br>7<br>SE SI<br>DLUM<br><u>http</u>                      | 28<br>E<br>8<br>UPPL<br>IBUS                 | 29<br>E<br>9<br>.Y CE<br>, OHI<br>ww.ds  | 30<br>E<br>10<br>NTEF<br>O 432            | 31<br>E<br>11<br>COL<br>218-3<br>a.mil | 32<br>E<br>12<br>UMB<br>990  | 33<br>E<br>13        | 34<br>G<br>14 |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STAI<br>MICRC<br>DRA<br>THIS DRAWIN<br>FOR US                                  | 15<br>NDAF<br>DCIRC<br>AWIN<br>NG IS A<br>SE BY A<br>RTMEN          | 16<br>RD<br>CUIT<br>G<br>VAILAI<br>ALL<br>ITS                                                                | 17<br>BLE                                                                                               | 18<br>REV<br>SHE<br>PRE<br>CHE        | 19<br>/<br>PAREE<br>CKED<br>PROVE<br>Wil                               | 20<br>D BY<br>Jeffery<br>BY<br>Tim F<br>D BY                                       | 21<br>G<br>1<br>Tunsta<br>I. Noh                 | 22<br>G<br>2<br>II    | 23<br>F             | 24<br>F<br>4<br>MIC<br>MIC       | 25<br>E<br>5<br>DI | 26<br>E<br>6<br>EFEN<br>CO                                                                                                           | 27<br>E<br>7<br>SE SI<br>DLUM<br>http<br>UIT, I<br>CESS           | 28<br>E<br>8<br>UPPL<br>BUS<br>5://ww        | 29<br>E<br>9<br>.Y CE<br>, OHIO<br>ww.ds | 30<br>E<br>10<br>SNTEF<br>O 432<br>Scc.dl | 31<br>E<br>11<br>COL<br>218-3<br>a.mil | 32<br>E<br>12<br>JUMB<br>990 | 33<br>E<br>13<br>SUS | 34<br>G<br>14 |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STAI<br>MICRO<br>DRA<br>THIS DRAWIN<br>FOR US<br>DEPAN                         | 15<br>NDAF<br>DCIRC<br>AWIN<br>NG IS A<br>SE BY<br>RTMEN<br>NCIES ( | 16<br>RD<br>CUIT<br>G<br>VAILAI<br>ALL<br>ITS<br>DF THE                                                      | BLE                                                                                                     | 18<br>REV<br>SHE<br>PRE<br>CHE        | 19<br>/<br>PAREE<br>CKED<br>PROVE<br>Wil                               | 20<br>D BY<br>Jeffery<br>BY<br>Tim H<br>D BY<br>Iliam K.                           | 21<br>G<br>1<br>Tunsta                           | 22<br>G<br>2<br>II    | 23<br>F             | 24<br>F<br>4<br>MIC<br>MIC       | 25<br>E<br>5<br>DI | 26<br>E<br>6<br>EFEN<br>CO                                                                                                           | 27<br>E<br>7<br>SE SI<br>DLUM<br><u>http</u>                      | 28<br>E<br>8<br>UPPL<br>BUS<br>5://ww        | 29<br>E<br>9<br>.Y CE<br>, OHIO<br>ww.ds | 30<br>E<br>10<br>SNTEF<br>O 432<br>Scc.dl | 31<br>E<br>11<br>COL<br>218-3<br>a.mil | 32<br>E<br>12<br>UMB<br>990  | 33<br>E<br>13<br>SUS | 34<br>G<br>14 |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STAI<br>MICRC<br>DRA<br>THIS DRAWIN<br>FOR U<br>DEPAR<br>AND AGEN<br>DEPARTMEN | 15<br>NDAF<br>DCIRC<br>AWIN<br>NG IS A<br>SE BY<br>RTMEN<br>NCIES ( | 16<br>RD<br>CUIT<br>G<br>VAILAI<br>ITS<br>DF THE<br>DEFEN                                                    | BLE                                                                                                     | 18<br>REV<br>SHE<br>PRE<br>CHE<br>APP | 19<br>/<br>PAREE<br>CKED<br>PROVE<br>Wil                               | 20<br>D BY<br>Jeffery<br>BY<br>Tim H<br>D BY<br>Iliam K.<br>APPR(<br>85-1          | 21<br>G<br>Tunsta<br>I. Noh<br>. Heckn<br>DVAL D | 22<br>G<br>2<br>II    | 23<br>F             | 24<br>F<br>4<br>MIC<br>MIC<br>MO | 25<br>E<br>5<br>DI | 26<br>E<br>E<br>F<br>E<br>F<br>E<br>R<br>O<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C | 27<br>E<br>7<br>SE SI<br>DLUM<br>http<br>UIT, [<br>CESS<br>C SILI | 28<br>E<br>8<br>IBUS<br>DIGIT<br>OR,<br>ICON | 29<br>E<br>9<br>.Y CE<br>, OHIO<br>ww.ds | 30<br>E<br>10<br>SNTEF<br>O 432<br>Scc.dl | 31<br>E<br>11<br>218-33<br>a.mil       | 32<br>E<br>12<br>JUMB<br>990 | 33<br>E<br>13<br>SUS | 34<br>G<br>14 |

| SHEET<br>REV<br>SHEET<br>REV STATUS<br>OF SHEETS<br>PMIC N/A<br>STAI<br>MICRC<br>DRA<br>THIS DRAWIN<br>FOR U<br>DEPAR<br>AND AGEN<br>DEPARTMEN | 15<br>NDAF<br>DCIRC<br>AWIN<br>NG IS A<br>SE BY<br>SE BY<br>NT OF I | 16<br>RD<br>CUIT<br>G<br>VAILAI<br>ITS<br>DF THE<br>DEFEN                                                    | BLE                                                                                                     | 18<br>REV<br>SHE<br>PRE<br>CHE<br>APP | 19<br>/<br>EET<br>PAREE<br>CKED<br>PROVE<br>Wil                        | 20<br>D BY<br>Jeffery<br>BY<br>Tim F<br>D BY<br>lliam K.<br>APPR(<br>85-1<br>LEVEL | 21<br>G<br>Tunsta<br>I. Noh<br>. Heckn<br>DVAL D | 22<br>G<br>2<br>II    | 23<br>F             | 24<br>F<br>4<br>MIC<br>MIC<br>MO | 25<br>E<br>5<br>DI | 26<br>E<br>E<br>F<br>E<br>F<br>E<br>R<br>O<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C | 27<br>E<br>7<br>SE SI<br>DLUM<br>http<br>UIT, I<br>CESS<br>C SILI | 28<br>E<br>8<br>IBUS<br>DIGIT<br>OR,<br>ICON | 29<br>E<br>9<br>.Y CE<br>, OHIO<br>ww.ds | 30<br>E<br>10<br>SNTEF<br>O 432<br>Scc.dl | 31<br>E<br>11<br>218-33<br>a.mil       | 32<br>E<br>12<br>UMB<br>990  | 33<br>E<br>13<br>SUS | 34<br>G<br>14 |

| 1. | SCOPE |

|----|-------|

|    |       |

1.1 <u>Scope</u>. This drawing describes device requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A.

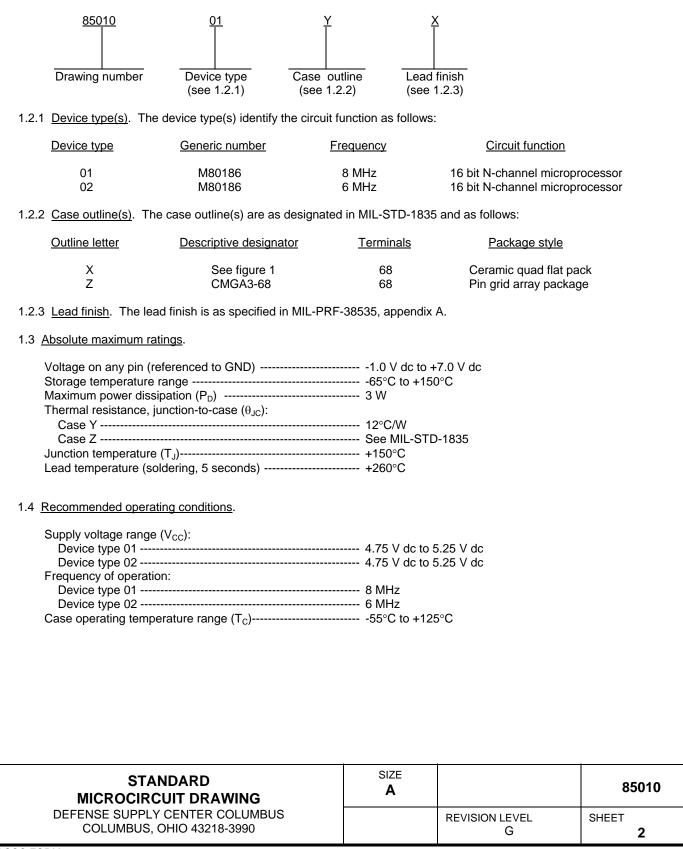

1.2 Part or Identifying Number (PIN). The complete PIN is as shown in the following example:

## 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

## DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

#### DEPARTMENT OF DEFENSE STANDARDS

| MIL-STD-883  | - | Test Method Standard Microcircuits.          |

|--------------|---|----------------------------------------------|

| MIL OTD 100F |   | Interface Standard Flastrania Component Coop |

MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

# DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings.

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at http://assist.daps.dla.mil/quicksearch/ or http://assist.daps.dla.mil or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein. Product built to this drawing that is produced by a Qualified Manufacturer Listing (QML) certified and qualified manufacturer or a manufacturer who has been granted transitional certification to MIL-PRF-38535 may be processed as QML product in accordance with the manufacturers approved program plan and qualifying activity approval in accordance with MIL-PRF-38535. This QML flow as documented in the Quality Management (QM) plan may make modifications to the requirements herein. These modifications shall not affect form, fit, or function of the device. These modifications shall not affect the PIN as described herein. A "Q" or "QML" certification mark in accordance with MIL-PRF-38535 is required to identify when the QML flow option is used. This drawing has been modified to allow the manufacturer to use the alternate die/fabrication requirements of paragraph A.3.2.2 of MIL-PRF-38535 or other alternative approved by the qualifying activity.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535, appendix A and herein.

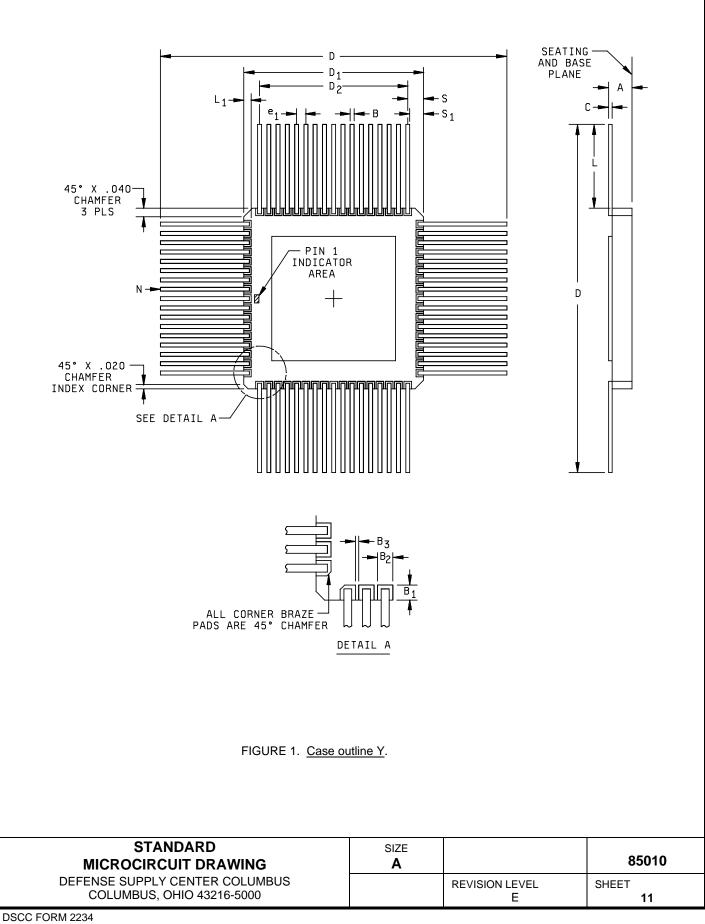

3.2.1 <u>Case outlines</u>. The case outlines shall be in accordance with 1.2.2 herein and figure 1.

3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

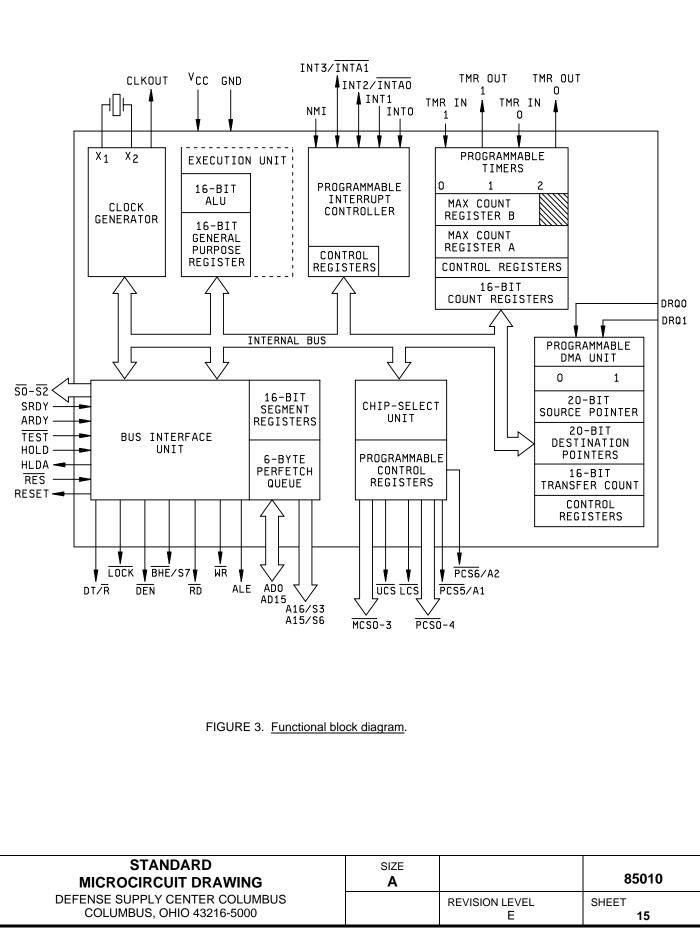

3.2.3 <u>Functional block diagram</u>. The functional block diagram shall be as specified on figure 3.

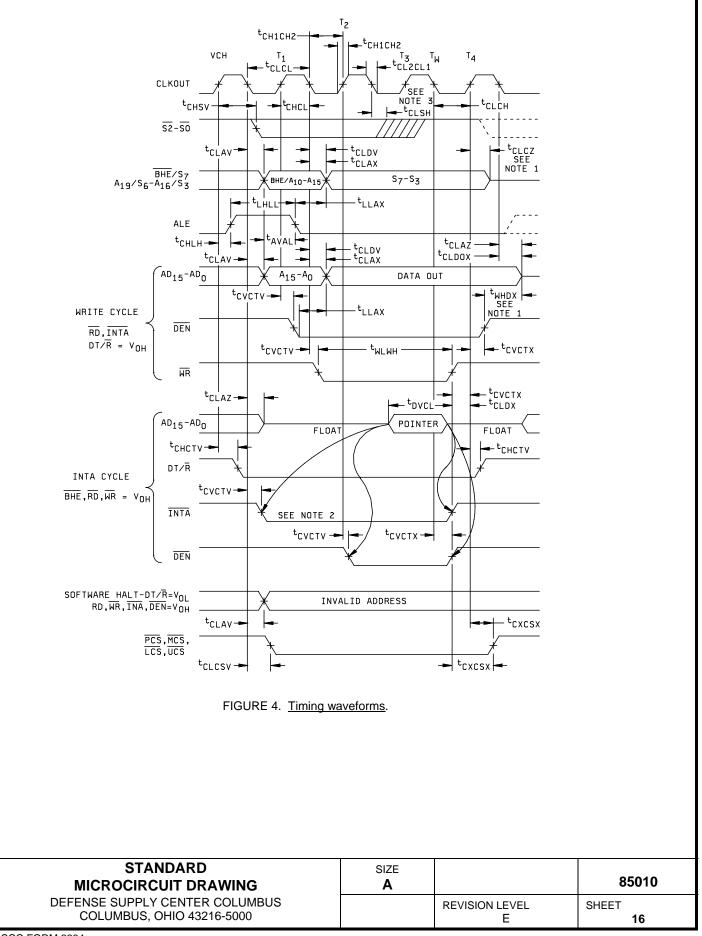

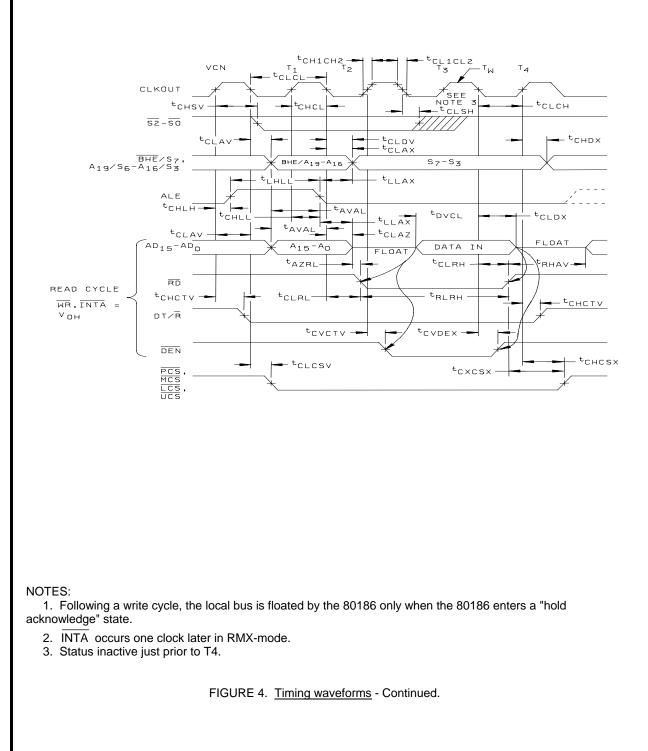

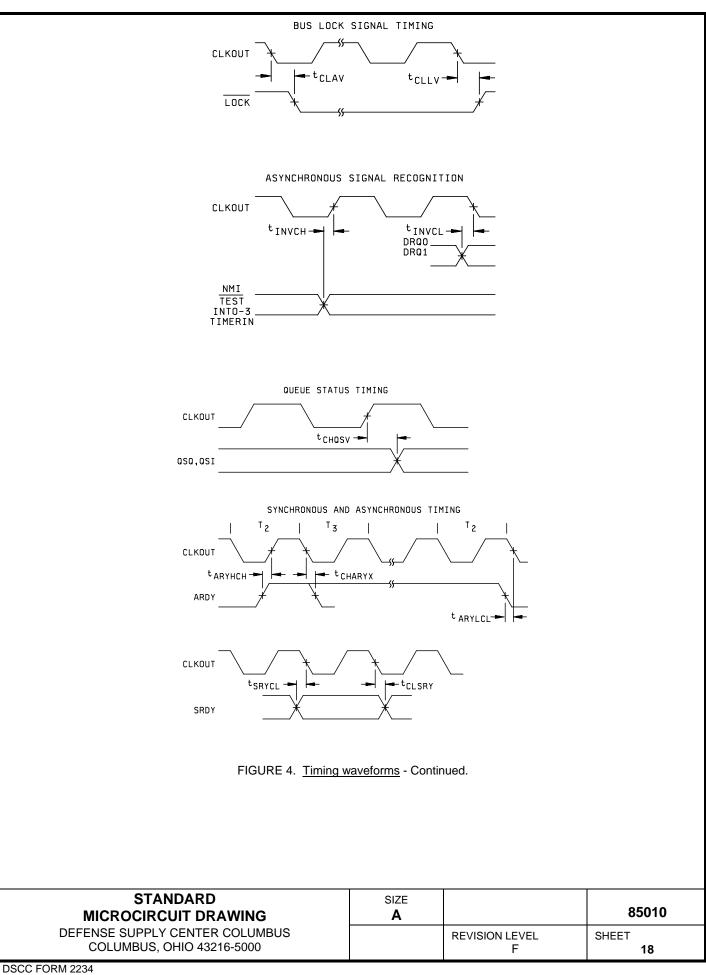

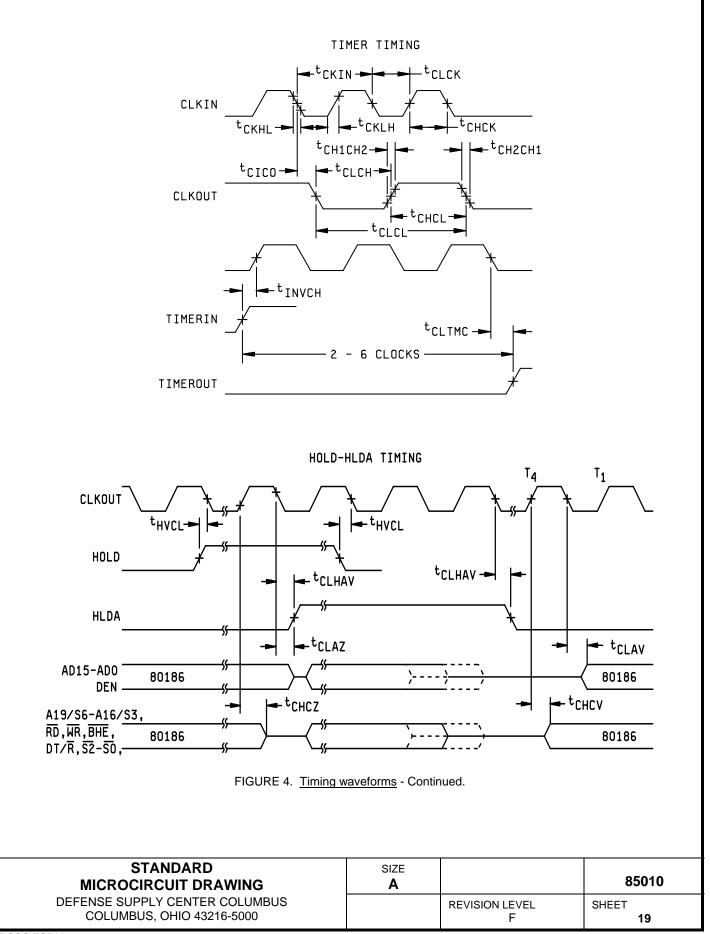

3.2.4 <u>Timing waveforms</u>. The timing waveforms shall be as specified on figure 4.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 85010 |

|----------------------------------|-----------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43218-3990        |           | F              | 3     |

3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

3.5 <u>Marking</u>. Marking shall be in accordance with MIL-PRF-38535, appendix A. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked.

3.5.1 <u>Certification/compliance mark</u>. A compliance indicator "C" shall be marked on all non-JAN devices built in compliance to MIL-PRF-38535, appendix A. The compliance indicator "C" shall be replaced with a "Q" or "QML" certification mark in accordance with MIL-PRF-38535 to identify when the QML flow option is used. For product built in accordance with A.3.2.2 of MIL-PRF-38535, or as modified in the manufacturer's QM plan, the "QD" certification mark shall be used in place of the "Q" or "QML" certification mark.

3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-PRF-38535, appendix A and the requirements herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

3.8 Notification of change. Notification of change to DSCC-VA shall be required for any change that affects this drawing.

3.9 <u>Verification and review</u>. DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 85010          |

|-------------------------------------------------------------|-----------|---------------------|----------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>F | SHEET <b>4</b> |

|                                                          |                  | TABLE I. Electrical performance                                                                                                                                                                          | e characterist | tics.                |        |                         |      |

|----------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|--------|-------------------------|------|

| Test                                                     | Symbol           | $\begin{array}{l} \mbox{Conditions}  \underline{1}/ \\ \mbox{-}55^{\circ}\mbox{C} \leq \mbox{T}_{\mbox{C}} \leq \mbox{+}125^{\circ}\mbox{C} \\ \mbox{V}_{\mbox{CC}} = 5.0 \mbox{ V} \pm 5\% \end{array}$ | Device<br>type | Group A<br>subgroups | Limits |                         | Unit |

|                                                          |                  | unless otherwise specified                                                                                                                                                                               |                |                      | Min    | Max                     |      |

| Low-level input voltage                                  | V <sub>IL</sub>  |                                                                                                                                                                                                          | 01, 02         | 1,2,3                | -0.5   | +0.8                    | V    |

| High-level input voltage<br>(All except X1) and<br>(RES) | V <sub>IH1</sub> |                                                                                                                                                                                                          | 01, 02         | 1,2,3                | 2.0    | V <sub>CC</sub><br>+0.5 | V    |

| High-level input voltage at (RES)                        | V <sub>IH2</sub> |                                                                                                                                                                                                          | 01, 02         | 1,2,3                | 3.0    | V <sub>CC</sub><br>+0.5 | V    |

| Low-level output voltage                                 | V <sub>OL</sub>  | $I_{OL} = 2.5 \text{ mA for } \overline{S0} - \overline{S2}$<br>$I_{OL} = 2.0 \text{ mA for all}$<br>other outputs                                                                                       | 01, 02         | 1,2,3                |        | 0.45                    | V    |

| High-level output voltage                                | V <sub>OH</sub>  | I <sub>OH</sub> = -400 μA                                                                                                                                                                                | 01, 02         | 1,2,3                | 2.4    |                         | V    |

| Power supply current                                     | I <sub>CC</sub>  | V <sub>CC</sub> = 5.25 V                                                                                                                                                                                 | 01, 02         | 1,2,3                |        | 600                     | mA   |

| Input leakage current                                    | IIL              | $0 V < V_{IN} < V_{CC}$                                                                                                                                                                                  | 01, 02         | 1,2,3                |        | ±10                     | μA   |

| Output leakage current                                   | I <sub>OL</sub>  | 0.45V < V <sub>OUT</sub> < V <sub>CC</sub>                                                                                                                                                               | 01, 02         | 1,2,3                |        | ±10                     | μA   |

| Low-level clock output voltage                           | V <sub>CLO</sub> | I <sub>OUT</sub> = 4.0 mA                                                                                                                                                                                | 01, 02         | 1,2,3                |        | 0.6                     | V    |

| High-level clock output voltage                          | V <sub>CHO</sub> | I <sub>OUT</sub> = -200 μA                                                                                                                                                                               | 01, 02         | 1,2,3                | 4.0    |                         | V    |

| Low-level clock input voltage                            | V <sub>CL1</sub> |                                                                                                                                                                                                          | 01, 02         | 1,2,3                | -0.5   | +0.6                    | V    |

| High-level clock input voltage                           | V <sub>CH1</sub> |                                                                                                                                                                                                          | 01, 02         | 1,2,3                | 3.9    | V <sub>cc</sub>         | V    |

|                                                          |                  |                                                                                                                                                                                                          |                |                      |        | +1.0                    |      |

| Functional tests                                         |                  | See 4.3.1d                                                                                                                                                                                               | 01, 02         | 7,8                  |        |                         |      |

| Input capacitance                                        | C <sub>IN</sub>  | See 4.3.1c                                                                                                                                                                                               | 01, 02         | 4                    |        | 10                      | pF   |

| I/O capacitance                                          | C <sub>IO</sub>  | See 4.3.1c                                                                                                                                                                                               | 01, 02         | 4                    |        | 20                      | pF   |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 85010 |

|----------------------------------|------------------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43216-5000        |                  | E              | 5     |

|                                                        | TABLE               | I. Electrical performance chai                                 | racteristics - | Continued.           |                   |     |      |

|--------------------------------------------------------|---------------------|----------------------------------------------------------------|----------------|----------------------|-------------------|-----|------|

| Test                                                   | Symbol              | Conditions <u>1</u> /<br>-55°C ≤ T <sub>C</sub> ≤+125°C        | Device<br>type | Group A<br>subgroups | Limits            |     | Unit |

| 1651                                                   | Symbol              | $V_{CC} = 5.0 \text{ V} \pm 5\%$<br>unless otherwise specified | туре           | subgroups            | Min               | Max |      |

| Data in setup (A/D)                                    | t <sub>DVCL</sub>   | $C_L = 20$ to 200 pF, all                                      | 01,02          | 9,10,11              | 20                |     | ns   |

| Data in hold (A/D)                                     | t <sub>CLDX</sub>   | outputs                                                        | 01,02          | 9,10,11              | 10                |     | ns   |

| Asynchronous ready<br>(ALREADY) active<br>setup time   | t <sub>ARYHCH</sub> |                                                                | 01,02          | 9,10,11              | 20                |     | ns   |

| AREADY inactive setup time                             | t <sub>ARYLCL</sub> |                                                                | 01,02          | 9,10,11              | 38                |     | ns   |

| AREADY hold time                                       | t <sub>CHARYX</sub> |                                                                | 01,02          | 9,10,11              | 15                |     | ns   |

| Synchronous ready<br>(SREADY)<br>transition setup time | t <sub>SRYCL</sub>  |                                                                | 01,02          | 9,10,11              | 35                |     | ns   |

| SREADY transition hold time                            | t <sub>CLSRY</sub>  |                                                                | 01,02          | 9,10,11              | 15                |     | ns   |

| Hold setup <u>2</u> /                                  | t <sub>HVCL</sub>   |                                                                | 01,02          | 9,10,11              | 25                |     | ns   |

| INTR, NMI, TEST ,<br>TIMERIN setup <u>2</u> /          | t <sub>INVCH</sub>  |                                                                | 01,02          | 9,10,11              | 25                |     | ns   |

| DRQ0, DRQ1, setup                                      | t <sub>INVCL</sub>  |                                                                | 01,02          | 9,10,11              | 25                |     | ns   |

| Address valid delay                                    | t <sub>CLAV</sub>   |                                                                | 01             | 9,10,11              | 5                 | 59  | ns   |

|                                                        |                     |                                                                | 02             | 9,10,11              | 5                 | 63  | ns   |

| Address hold                                           | t <sub>CLAX</sub>   |                                                                | 01             | 9,10,11              | 5                 |     | ns   |

|                                                        |                     |                                                                | 02             | 9,10,11              | 5                 |     | ns   |

| Address float delay                                    | t <sub>CLAZ</sub>   |                                                                | 01             | 9,10,11              | t <sub>CLAX</sub> | 35  | ns   |

|                                                        |                     |                                                                | 02             | 9,10,11              | t <sub>CLAX</sub> | 44  | ns   |

| Address valid to clock high                            | t <sub>AVCH</sub>   |                                                                | 01,02          | 9,10,11              | 10                |     | ns   |

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 85010   |

|-------------------------------------------------------------|-----------|---------------------|---------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |           | REVISION LEVEL<br>E | SHEET 6 |

|                        | TABLE              | I. Electrical performance charac                        | <u>teristics</u> - C | continued.           |                          |     |      |

|------------------------|--------------------|---------------------------------------------------------|----------------------|----------------------|--------------------------|-----|------|

| Test                   | Symbol             | Conditions <u>1</u> /<br>-55°C ≤ T <sub>C</sub> ≤+125°C | Device               | Group A<br>subgroups | Limits                   |     | Unit |

| TEST                   | Symbol             | $V_{CC} = 5.0 V \pm 5\%$<br>unless otherwise specified  | type                 | subgroups            | Min                      | Max |      |

| Command lines float    | t <sub>CHCZ</sub>  | $C_L = 20$ to 200 pF, all                               | 01                   | 9,10,11              |                          | 45  | ns   |

| delay                  |                    | outputs                                                 | 02                   | 9,10,11              |                          | 56  | ns   |

| Command lines valid    | t <sub>CHCV</sub>  |                                                         | 01                   | 9,10,11              |                          | 55  | ns   |

| delay (after float)    |                    |                                                         | 02                   | 9,10,11              |                          | 76  | ns   |

| ALE width              | t <sub>LHLL</sub>  |                                                         | 01,02                | 9,10,11              | t <sub>CLCL</sub><br>-35 |     | ns   |

| ALE active delay       | +                  |                                                         | 01                   | 9,10,11              |                          | 35  | ns   |

| ALE active delay       | t <sub>CHLH</sub>  |                                                         | 02                   | 9,10,11              |                          | 44  | ns   |

| ALE inactive delay     | tauna              |                                                         | 01                   | 9,10,11              |                          | 35  | ns   |

|                        | t <sub>CHLL</sub>  |                                                         | 02                   | 9,10,11              |                          | 44  | ns   |

| Address hold to ALE    | t <sub>LLAX</sub>  |                                                         | 01                   | 9,10,11              | t <sub>CHCL</sub><br>-25 |     | ns   |

| inactive               |                    |                                                         | 02                   | 9,10,11              | t <sub>CHCL</sub><br>-30 |     | ns   |

| Data valid delay       | t <sub>CLDV</sub>  |                                                         | 01                   | 9,10,11              | 5                        | 44  | ns   |

|                        |                    |                                                         | 02                   | 9,10,11              | 5                        | 55  | ns   |

| Data hold time         | t <sub>CLDOX</sub> |                                                         | 01,02                | 9,10,11              | 5                        |     | ns   |

| Data hold after WR     | t <sub>WHDX</sub>  |                                                         | 01                   | 9,10,11              | t <sub>CLCL</sub><br>-40 |     | ns   |

|                        |                    |                                                         | 02                   | 9,10,11              | t <sub>CLCL</sub><br>-50 |     | ns   |

| Control active delay 1 | t <sub>CVCTV</sub> |                                                         | 01                   | 9,10,11              | 5                        | 70  | ns   |

|                        |                    |                                                         | 02                   | 9,10,11              | 5                        | 87  | ns   |

| Control active delay 2 | t <sub>CHCTV</sub> |                                                         | 01                   | 9,10,11              | 5                        | 73  | ns   |

|                        |                    |                                                         | 02                   | 9,10,11              | 5                        | 76  | ns   |

| DEN inactive delay     | t <sub>CVDEX</sub> |                                                         | 01                   | 9,10,11              | 10                       | 70  | ns   |

| (non-write cycle)      |                    |                                                         | 02                   | 9,10,11              | 10                       | 87  | ns   |

See footnotes at end of table.

| STANDARD                                                    | SIZE |                     |            |

|-------------------------------------------------------------|------|---------------------|------------|

| MICROCIRCUIT DRAWING                                        | Α    |                     | 85010      |

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |      | REVISION LEVEL<br>E | SHEET<br>7 |

|                             | TAI                | BLE I. Electrical performance                                                                                                          | characteristi | i <u>cs</u> - Continued. |                           |      |      |

|-----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------|---------------------------|------|------|

|                             |                    | Conditions <u>1</u> /                                                                                                                  | Device        | Group A                  | Lin                       | nits | Unit |

| Test                        | Symbol             | $\begin{array}{l} -55^\circ C \leq T_C \leq +125^\circ C \\ V_{CC} = 5.0 \ V \pm 5\% \\ \text{unless otherwise specified} \end{array}$ | type          | subgroups                | Min                       | Max  |      |

| Address float to RD active  | t <sub>AZRL</sub>  | C <sub>L</sub> = 20 to 200 pF, all<br>outputs                                                                                          | 01,02         | 9,10,11                  | 0                         |      | ns   |

| RD active delay             | t <sub>CLRL</sub>  |                                                                                                                                        | 01            | 9,10,11                  | 10                        | 70   | ns   |

|                             |                    |                                                                                                                                        | 02            | 9,10,11                  | 10                        | 87   | ns   |

| RD inactive delay           | t <sub>CLRH</sub>  |                                                                                                                                        | 01            | 9,10,11                  | 10                        | 55   | ns   |

| ,                           |                    |                                                                                                                                        | 02            | 9,10,11                  | 10                        | 76   | ns   |

| $\overline{RD}$ inactive to | t <sub>RHAV</sub>  |                                                                                                                                        | 01            | 9,10,11                  | t <sub>CLCL</sub><br>-40  |      | ns   |

| address active              |                    |                                                                                                                                        | 02            | 9,10,11                  | t <sub>CLCL</sub><br>-50  |      | ns   |

| HLDA valid delay            | t <sub>CLHAV</sub> |                                                                                                                                        | 01,02         | 9,10,11                  | 5                         | 67   | ns   |

| RD width                    | t <sub>RLRH</sub>  |                                                                                                                                        | 01,02         | 9,10,11                  | 2t <sub>CLCL</sub><br>-50 |      | ns   |

| WR width                    | t <sub>wLWH</sub>  |                                                                                                                                        | 01,02         | 9,10,11                  | 2t <sub>CLCL</sub><br>-40 |      | ns   |

| Address valid to ALE        | t <sub>AVAL</sub>  |                                                                                                                                        | 01            | 9,10,11                  | t <sub>с∟сн</sub><br>-25  |      | ns   |

| low                         |                    |                                                                                                                                        | 02            | 9,10,11                  | t <sub>с∟СН</sub><br>-45  |      | ns   |

| Status active delay         | t <sub>CHSV</sub>  |                                                                                                                                        | 01            | 9,10,11                  | 10                        | 55   | ns   |

|                             |                    |                                                                                                                                        | 02            | 9,10,11                  | 10                        | 76   | ns   |

| Status inactive delay       | t <sub>CLSH</sub>  |                                                                                                                                        | 01            | 9,10,11                  | 10                        | 65   | ns   |

|                             |                    |                                                                                                                                        | 02            | 9,10,11                  | 10                        | 76   | ns   |

| Timer output delay          | $t_{CLTMV}$        | $C_L = 100 \text{ pF} \text{ maximum}$                                                                                                 | 01            | 9,10,11                  |                           | 60   | ns   |

|                             |                    |                                                                                                                                        | 02            | 9,10,11                  |                           | 75   | ns   |

| Control inactive delay      | t <sub>CVCTX</sub> | $C_L = 20$ to 200 pF, all                                                                                                              | 01            | 9,10,11                  |                           | 55   | ns   |

|                             |                    | outputs                                                                                                                                | 02            | 9,10,11                  |                           | 76   | ns   |

See footnotes at end of table.

| STANDARD                                                    | SIZE |                     |            |

|-------------------------------------------------------------|------|---------------------|------------|

| MICROCIRCUIT DRAWING                                        | Α    |                     | 85010      |

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |      | REVISION LEVEL<br>E | SHEET<br>8 |

| TABLE I. Electrical performance characteristics - Continued. |                    |                                                                                                                                                      |        |           |                          |      |      |

|--------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|--------------------------|------|------|

|                                                              |                    | Conditions <u>1</u> /                                                                                                                                | Device | Group A   | Limits                   |      | Unit |

| Test                                                         | Symbol             | $\label{eq:CC} \begin{array}{l} -55^\circ C \leq T_C \leq +125^\circ C \\ V_{CC} = 5.0 \ V \pm 5\% \\ \text{unless otherwise specified} \end{array}$ | type   | subgroups | Min                      | Max  |      |

| Reset delay                                                  | t <sub>CLRO</sub>  | $C_{L} = 20$ to 200 pF, all                                                                                                                          | 01     | 9,10,11   |                          | 60   | ns   |

|                                                              |                    | outputs                                                                                                                                              | 02     | 9,10,11   |                          | 75   | ns   |

| Queue status delay                                           | t <sub>CHQSV</sub> |                                                                                                                                                      | 01     | 9,10,11   |                          | 35   | ns   |

|                                                              |                    | -                                                                                                                                                    | 02     | 9,10,11   |                          | 44   | ns   |

| Chip-select active                                           | t <sub>CLCSV</sub> |                                                                                                                                                      | 01     | 9,10,11   | 5                        | 66   | ns   |

| delay                                                        |                    | -                                                                                                                                                    | 02     | 9,10,11   | 5                        | 80   | ns   |

| Chip-select hold from<br>command inactive                    | t <sub>cxcsx</sub> |                                                                                                                                                      | 01,02  | 9,10,11   | 35                       |      | ns   |

| Chip-select inactive delay                                   | t <sub>CHCSX</sub> |                                                                                                                                                      | 01,02  | 9,10,11   | 5                        | 47   | ns   |

| CLKIN period                                                 | t <sub>CKIN</sub>  |                                                                                                                                                      | 01     | 9,10,11   | 62.5                     | 250  | ns   |

|                                                              |                    |                                                                                                                                                      | 02     | 9,10,11   | 83                       | 250  | ns   |

| CLKIN fall time                                              | t <sub>CKHL</sub>  | 3.5 V to 1.0 V <u>3</u> /                                                                                                                            | 01,02  | 9,10,11   |                          | 10   | ns   |

| CLKIN rise time                                              | t <sub>CKLH</sub>  | 1.0 V to 3.5 V <u>3/</u>                                                                                                                             | 01,02  | 9,10,11   |                          | 10   | ns   |

| CLKIN low time                                               | t <sub>CLCK</sub>  | 1.5 V <u>3</u> /                                                                                                                                     | 01     | 9,10,11   | 25                       |      | ns   |

|                                                              |                    |                                                                                                                                                      | 02     | 9,10,11   | 33                       |      | ns   |

| CLKIN high time                                              | t <sub>CHCK</sub>  | 1.5 V <u>3</u> /                                                                                                                                     | 01     | 9,10,11   | 25                       |      | ns   |

|                                                              |                    |                                                                                                                                                      | 02     | 9,10,11   | 33                       |      | ns   |

| CLKIN to CLKOUT skew                                         | t <sub>CICO</sub>  | $C_L = 20$ to 200 pF, all                                                                                                                            | 01     | 9,10,11   |                          | 50   | ns   |

|                                                              |                    | outputs                                                                                                                                              | 02     | 9,10,11   |                          | 62.5 | ns   |

| CLKOUT period                                                | t <sub>CLCL</sub>  |                                                                                                                                                      | 01     | 9,10,11   | 125                      | 500  | ns   |

|                                                              |                    |                                                                                                                                                      | 02     | 9,10,11   | 167                      | 500  | ns   |

| CLKOUT low time                                              | t <sub>CLCH</sub>  | 1.5 V <u>3</u> /                                                                                                                                     | 01,02  | 9,10,11   | 1/2<br>t <sub>CLCL</sub> |      | ns   |

|                                                              |                    |                                                                                                                                                      |        |           | -7.5                     |      |      |

See footnotes at end of table I.

# STANDARD **MICROCIRCUIT DRAWING** DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000

| SIZE<br><b>A</b> |                     | 85010      |

|------------------|---------------------|------------|

|                  | REVISION LEVEL<br>E | SHEET<br>9 |

|                  | TABLE I.            | Electrical performance characte                                                                                                                                              | <u>ristics</u> - Co | ontinued. |                          |      |      |

|------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|--------------------------|------|------|

|                  |                     | Conditions <u>1</u> /                                                                                                                                                        | Device              | Group A   | Lim                      | nits | Unit |

| Test             | Symbol              | $\begin{array}{l} \text{-55°C} \leq \text{T}_{\text{C}} \leq \text{+125°C} \\ \text{V}_{\text{CC}} = 5.0 \text{ V} \pm 5\% \\ \text{unless otherwise specified} \end{array}$ | type                | subgroups | Min                      | Max  |      |

| CLKOUT high time | t <sub>CHCL</sub>   | 1.5 V <u>3</u> /                                                                                                                                                             | 01,02               | 9,10,11   | 1/2<br>t <sub>CLCL</sub> |      | ns   |

|                  |                     |                                                                                                                                                                              |                     |           | -7.5                     |      |      |

| CLKOUT rise time | t <sub>CH1CH2</sub> | 1.0 V to 3.5 V <u>3</u> /                                                                                                                                                    | 01,02               | 9,10,11   |                          | 15   | ns   |

| CLKOUT fall time | t <sub>CL2CL1</sub> | 3.5 V to 1.0 V <u>3/</u>                                                                                                                                                     | 01,02               | 9,10,11   |                          | 15   | ns   |

<u>1</u>/ All AC parameters tested as per circuit on figure 4.

<u>2</u>/ Setup requirements only to guarantee recognition at next CLK.

<u>3</u>/ Voltage indicated refer to voltage measurements on waveforms in figure 4.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE |                | 85010 |

|----------------------------------|------|----------------|-------|

| DEFENSE SUPPLY CENTER COLUMBUS   |      | REVISION LEVEL | SHEET |

| COLUMBUS, OHIO 43216-5000        |      | E              | 10    |

| Dimensions     |          |       |           |        |  |

|----------------|----------|-------|-----------|--------|--|

| Symbol         | Inc      | hes   | Millim    | neters |  |

|                | Min      | Max   | Min       | Max    |  |

| A              | .080     | .106  | 2.03      | 2.69   |  |

| В              | .016     | .020  | 0.41      | 0.51   |  |

| B <sub>1</sub> | .040     | .060  | 1.02      | 1.52   |  |

| B <sub>2</sub> | .030     | .040  | 0.76      | 1.02   |  |

| B <sub>3</sub> | .005     | .020  | 0.13      | 0.51   |  |

| С              | .008     | .012  | 0.20      | 0.30   |  |

| D              | 1.640    | 1.870 | 41.66     | 47.50  |  |

| D <sub>1</sub> | .935     | .970  | 23.75     | 24.64  |  |

| D <sub>2</sub> | .800 BSC |       | 20.32 BSC |        |  |

| e <sub>1</sub> | .050 BSC |       | 1.27      | BSC    |  |

| L              | .375     | .450  | 9.53      | 11.43  |  |

| L <sub>1</sub> | .040     | .060  | 1.02      | 1.52   |  |

| N              | 68 PINS  |       | 68 F      | PINS   |  |

| S              | .66      | .087  | 1.68      | 2.21   |  |

| S <sub>1</sub> | .050     |       | 1.27      |        |  |

FIGURE 1. Case outline Y - Continued.

| STANDARD                                                    | SIZE |                     |             |

|-------------------------------------------------------------|------|---------------------|-------------|

| MICROCIRCUIT DRAWING                                        | Α    |                     | 85010       |

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |      | REVISION LEVEL<br>E | SHEET<br>12 |

| Device type All |                 |            |                 |  |  |  |

|-----------------|-----------------|------------|-----------------|--|--|--|

|                 | Case outline Y  |            |                 |  |  |  |

| Pin number      | Pin symbol      | Pin number | Pin symbol      |  |  |  |

| 1               | V <sub>CC</sub> | 35         | V <sub>CC</sub> |  |  |  |

| 2               | AD4             | 36         | INT2/INTA0      |  |  |  |

| 3               | AD12            | 37         | INT3/INTA1      |  |  |  |

| 4               | AD5             | 38         | DT/R            |  |  |  |

| 5               | AD13            | 39         | DEN             |  |  |  |

| 6               | AD6             | 40         | MCS0            |  |  |  |

| 7               | AD14            | 41         | MCS1            |  |  |  |

| 8               | AD7             | 42         | MCS2            |  |  |  |

| 9               | AD15            | 43         | MCS3            |  |  |  |

| 10              | A16/S3          | 44         | UCS             |  |  |  |

| 11              | A17/S4          | 45         | LCS             |  |  |  |

| 12              | A18/S5          | 46         | PCS6 /A2        |  |  |  |

| 13              | A19/S6          | 47         | PCS5 /A1        |  |  |  |

| 14              | BHE /S7         | 48         | PCS4            |  |  |  |

| 15              | WR /QS1         | 49         | PCS3            |  |  |  |

| 16              | RD/QSMD         | 50         | PCS2            |  |  |  |

| 17              | ALE/QS0         | 51         | PCS1            |  |  |  |

| 18              | V <sub>SS</sub> | 52         | V <sub>SS</sub> |  |  |  |

| 19              | X1              | 53         | PCS0            |  |  |  |

| 20              | X2              | 54         | RES             |  |  |  |

| 21              | RESET           | 55         | TMR OUT1        |  |  |  |

| 22              | CLKOUT          | 56         | TMR OUT0        |  |  |  |

| 23              | ARDY            | 57         | TMR IN1         |  |  |  |

| 24              | S2              | 58         | TMR IN0         |  |  |  |

| 25              | S1              | 59         | DRQ1            |  |  |  |

| 26              | SO              | 60         | DRQ0            |  |  |  |

| 27              | HLDA            | 61         | AD0             |  |  |  |

| 28              | HOLD            | 62         | AD8             |  |  |  |