| LTR         DESCRIPTION         DATE (YR-MOLDA)         APPROVED           A         Technical changes in table I. Editorial changes throughout.         90-08-27         W. Hackman           B         Added Rochester as source of supply Vendor cage 3V146. Updated bolierplate<br>and made additional changes throughout.         90-08-27         W. Hackman           C         Made additional changes throughout.         90-08-27         W. Hackman         Thomas M. Hess           C         Made additional changes throughout.         01-01-04         Thomas M. Hess         01-01-04           D         Correct run, maximum limit in table 1. Update bolierplate to MIL-PRF-38535         04-05-04         Thomas M. Hess           E         Update bolierplate to current MIL-PRF-38535 requirements CFS         09-05-05         Thomas M. Hess           REV         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th>F</th> <th>REVISI</th> <th>ONS</th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                |                |                                                            |                      |                  |                    |                   |                   | F                    | REVISI    | ONS     |          |                 |       |            |       |          |       |                |      |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------|------------------------------------------------------------|----------------------|------------------|--------------------|-------------------|-------------------|----------------------|-----------|---------|----------|-----------------|-------|------------|-------|----------|-------|----------------|------|----|

| B         Added Rochester as source of supply Vendor cage 3V146. Updated boilerplate         01-01-04         Thomas M. Hess           C         Made editorial changes to table 1, sheet 5 on the V, test in the max column.         01-12-13         Thomas M. Hess           D         Correct tuu maximum limit in table 1. Update boilerplate to MIL-PRF-38535         04-05-04         Thomas M. Hess           E         Update boilerplate to ourrent MIL-PRF-38536 requirements CFS         09-05-05         Thomas M. Hess           REV         E         E         Update boilerplate to ourrent MIL-PRF-38636 requirements CFS         09-05-05         Thomas M. Hess           REV         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E <t< td=""><td>LTR</td><td colspan="8">DESCRIPTION</td><td></td><td></td><td></td><td colspan="3">DATE (YR-MO-DA)</td><td></td><td colspan="3">APPROVED</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LTR                                                            | DESCRIPTION    |                                                            |                      |                  |                    |                   |                   |                      |           |         |          | DATE (YR-MO-DA) |       |            |       | APPROVED |       |                |      |    |

| and made editorial changes throughout. – LTG         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O <tho< td="" th<=""><td>А</td><td>Tech</td><td colspan="8">echnical changes in table I. Editorial changes throughout.</td><td></td><td></td><td colspan="2">90-08-27</td><td colspan="2">W. Heckman</td><td></td></tho<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | А                                                              | Tech           | echnical changes in table I. Editorial changes throughout. |                      |                  |                    |                   |                   |                      |           |         |          | 90-08-27        |       | W. Heckman |       |          |       |                |      |    |

| Updated buttetin page         LTG         Image: LTG         Ima                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | В                                                              | Adde<br>and r  | ed Roch<br>made e                                          | nester a<br>ditorial | as sour<br>chang | ce of s<br>es thro | upply V<br>ughout | ′endor<br>. – LTG | cage 3'              | V146. l   | Jpdate  | d boilei | plate           |       | 01-0       | )1-04 |          | Thor  | Thomas M. Hess |      |    |

| requirements.         CFS         09-05-05         Thomas M. Hess           E         Update bolierplate to current MIL-PRF-38535 requirements.         - CFS         09-05-05         Thomas M. Hess           SHEET         I         I         I         I         I         I         I           SHEET         I         I         I         I         I         I         I           SHEET         I         I         I         I         I         I         I         I           SHEET         I         I         I         I         I         I         I         I         I           SHEET         IS         16         17         18         19         20         21         22         23         24         25         26         27         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | С                                                              | Made<br>Upda   | e editor<br>ated bu                                        | ial cha<br>lletin pa | nge to<br>age L  | table I,<br>TG     | sheet             | 5 on th           | e V <sub>IL</sub> te | st in the | e max o | column   |                 |       | 01-1       | 12-13 |          | Thor  | mas M.         | Hess |    |

| REV       Image: Second S | D                                                              | Corre<br>requi | ect t <sub>CLLF</sub>                                      | ₁ maxin<br>is C      | num lin<br>FS    | nit in tal         | ble I. L          | Jpdate            | boilerp              | late to   | MIL-PR  | RF-385   | 35              |       | 04-0       | )5-04 |          | Thor  | Thomas M. Hess |      |    |

| SHEET         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | E                                                              | Upda           | ate boil                                                   | erplate              | to curr          | ent MIL            | -PRF-             | 38535 I           | require              | ments.    | - CFS   | 5        |                 |       | 09-0       | )5-05 |          | Thor  | nas M.         | Hess |    |

| SHEET         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                |                |                                                            |                      |                  |                    |                   |                   |                      |           |         |          |                 |       |            |       |          |       |                |      |    |

| SHEET         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | REV/                                                           | 1              | İ                                                          | 1                    | 1                |                    | 1                 | İ                 | i                    | İ         | i       | İ        | i               | İ     | İ          | 1     | 1        | 1     | 1              | 1    |    |

| SHEET       15       16       17       18       19       20       21       22       23       24       25       26       27       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I <thi< th="">       I       I</thi<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                |                |                                                            |                      |                  |                    |                   |                   |                      |           |         |          |                 |       |            |       |          |       |                |      |    |

| REV STATUS         REV         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E         E <t< td=""><td>REV</td><td>E</td><td>E</td><td>E</td><td>E</td><td>E</td><td>E</td><td>E</td><td>E</td><td>Е</td><td>E</td><td>E</td><td>E</td><td>Е</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | REV                                                            | E              | E                                                          | E                    | E                | E                  | E                 | E                 | E                    | Е         | E       | E        | E               | Е     |            |       |          |       |                |      |    |

| OF SHEETS         SHEET         1         2         3         4         5         6         7         8         9         10         11         12         13         14           PMIC N/A         PREPARED BY<br>Christopher A. Rauch         DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990<br>http://www.dscc.dla.mil           MICROCIRCUIT<br>DRAWING         CHECKED BY<br>Charles Reusing         APPROVED BY         MICROCIRCUIT, DIGITAL, NMOS, 16-BIT         MICROCIRCUIT, DIGITAL, NMOS, 16-BIT           MICROCIRCUIT DEPARTMENTS<br>AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE         DRAWING APPROVAL DATE         MICROCONTROLLER, MONOLITHIC SILICON           AMSC N/A         REVISION LEVEL<br>E         SIZE         CAGE CODE<br>67268         5962-89596                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SHEET                                                          | 15             | 16                                                         | 17                   | 18               | 19                 | 20                | 21                | 22                   | 23        | 24      | 25       | 26              | 27    |            |       |          |       |                |      |    |

| PMIC N/A       PREPARED BY<br>Christopher A. Rauch       DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990<br>http://www.dscc.dla.mil         STANDARD<br>MICROCIRCUIT<br>DRAWING       CHECKED BY       http://www.dscc.dla.mil         MICROCIRCUIT<br>DRAWING       Checked BY       http://www.dscc.dla.mil         MICROCIRCUIT<br>DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTS<br>AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE       APPROVED BY         MICROCIRCUIT, DIGITAL, NMOS, 16-BIT       MICROCONTROLLER, MONOLITHIC SILICON         AMSC N/A       REVISION LEVEL<br>E       SIZE<br>A       CAGE CODE<br>67268       5962-89596                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REV STATUS                                                     |                | •                                                          |                      | RE∖              | /                  |                   | Е                 | E                    | Е         | Е       | Е        | Е               | Е     | Е          | Е     | Е        | Е     | Е              | Е    | E  |

| Christopher A. Rauch       DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990         MICROCIRCUIT<br>DRAWING       CHECKED BY       http://www.dscc.dla.mil         Charles Reusing       APPROVED BY       http://www.dscc.dla.mil         THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTS<br>AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE       William K. Heckman       MICROCIRCUIT, DIGITAL, NMOS, 16-BIT<br>MICROCONTROLLER, MONOLITHIC SILICON         AMSC N/A       REVISION LEVEL<br>E       SIZE       CAGE CODE<br>A       5962-89596         SHEET       SHEET       SHEET       SHEET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OF SHEETS                                                      |                |                                                            |                      | SHE              | ET                 |                   | 1                 | 2                    | 3         | 4       | 5        | 6               | 7     | 8          | 9     | 10       | 11    | 12             | 13   | 14 |

| MICROCIRCUIT<br>DRAWING       Charles Reusing       http://www.dscc.dla.mil         THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTS       APPROVED BY       APPROVED BY         MICROCIRCUIT, DIGITAL, NMOS, 16-BIT<br>MICROCONTROLLER, MONOLITHIC SILICON       DRAWING APPROVAL DATE       MICROCONTROLLER, MONOLITHIC SILICON         AMSC N/A       REVISION LEVEL<br>E       SIZE       CAGE CODE<br>A       5962-89596                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PMIC N/A                                                       |                |                                                            |                      | PRE              |                    |                   | er A. Ra          | auch                 |           |         | DI       | EFEN            | SE SI | UPPL       | Y CE  | NTER     |       | .UMB           | US   |    |

| THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL<br>DEPARTMENTS<br>AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE     MICROCIRCUIT, DIGITAL, NMOS, 16-BIT<br>MICROCONTROLLER, MONOLITHIC SILICON       AMSC N/A     REVISION LEVEL<br>E     SIZE<br>A     CAGE CODE<br>67268     5962-89596                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MICRO                                                          | CIRC           | CUIT                                                       |                      | CHE              |                    |                   | Reusir            | ng                   |           |         |          | CC              |       |            |       |          |       | 990            |      |    |

| FOR USE BY ALL<br>DEPARTMENTS     William K. Heckman     MICROCIRCUIT, DIGITAL, NMOS, 16-BIT       AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE     DRAWING APPROVAL DATE     MICROCONTROLLER, MONOLITHIC SILICON       AMSC N/A     REVISION LEVEL<br>E     SIZE     CAGE CODE<br>A     5962-89596       SHEFT     SHEFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                | •              | -                                                          |                      | APF              | ROVE               | D BY              |                   |                      |           |         |          |                 |       |            |       |          |       |                |      |    |

| DEPARTMENT OF DEFENSE     DRAWING APPROVAL DATE     INFORCEOUNTROLLET, MOROLITHIC OLLIOON       AMSC N/A     REVISION LEVEL     SIZE     CAGE CODE       E     A     67268     5962-89596                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL William K. Heckman |                |                                                            |                      |                  |                    |                   |                   |                      |           |         |          |                 |       |            |       |          |       |                |      |    |

| AMSC N/A REVISION LEVEL E SIZE CAGE CODE A 67268 5962-89596                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                |                |                                                            |                      | DRA              | WING               | APPRO             | OVAL D            | DATE                 |           | MIC     | ROC      | CONT            | ROL   | LER,       | MOI   | NOLI     | THIC  | SILI           | CON  |    |

| E A 67268 5962-89596                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                |                |                                                            |                      |                  |                    | 89-0              | 9-14              |                      |           |         |          | 1               |       |            |       |          |       |                |      |    |

| SHEET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AM                                                             | SC N/A         | L                                                          |                      | REV              | ISION              |                   |                   |                      |           |         |          |                 |       |            |       | į        | 5962· | -8959          | 6    |    |

| 1 OF 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                |                |                                                            |                      |                  |                    |                   |                   |                      |           | SHEET   |          |                 |       |            |       |          |       |                |      |    |

### 1. SCOPE

1.1 <u>Scope</u>. This drawing describes device requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A.

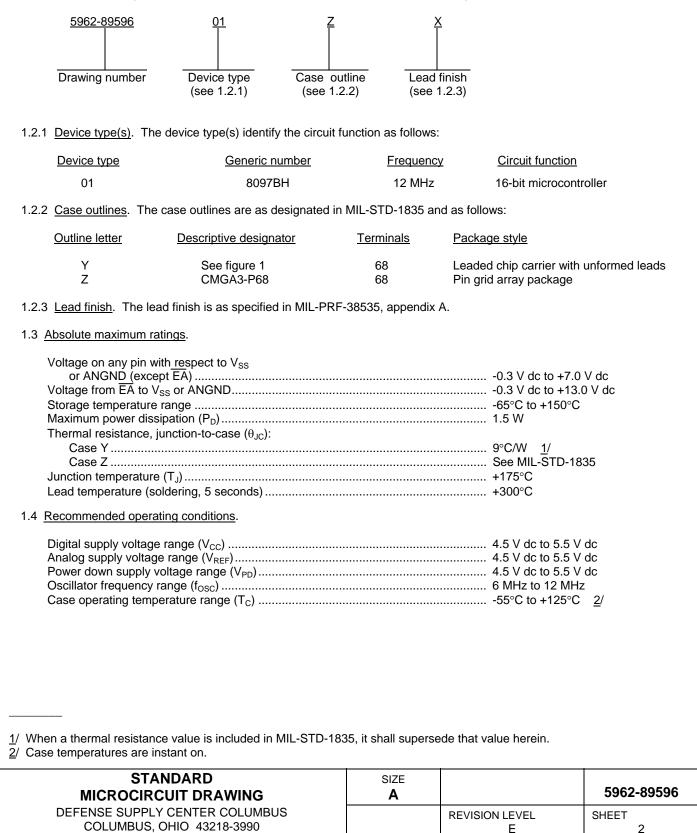

1.2 Part or Identifying Number (PIN). The complete PIN is as shown in the following example:

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

DEPARTMENT OF DEFENSE STANDARDS

| MIL-STD-883  | - | Test Method Standard Microcircuits.                    |

|--------------|---|--------------------------------------------------------|

| MIL-STD-1835 | - | Interface Standard Electronic Component Case Outlines. |

DEPARTMENT OF DEFENSE HANDBOOKS

| MIL-HDBK-103 | - | List of Standard Microcircuit Drawings. |

|--------------|---|-----------------------------------------|

|--------------|---|-----------------------------------------|

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at <u>http://assist.daps.dla.mil/quicksearch/</u> or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

#### 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein. Product built to this drawing that is produced by a Qualified Manufacturer Listing (QML) certified and qualified manufacturer or a manufacturer who has been granted transitional certification to MIL-PRF-38535 may be processed as QML product in accordance with the manufacturers approved program plan and qualifying activity approval in accordance with MIL-PRF-38535. This QML flow as documented in the Quality Management (QM) plan may make modifications to the requirements herein. These modifications shall not affect form, fit, or function of the device. These modifications shall not affect the PIN as described herein. A "Q" or "QML" certification mark in accordance with MIL-PRF-38535 is required to identify when the QML flow option is used. This drawing has been modified to allow the manufacturer to use the alternate die/fabrication requirements of paragraph A.3.2.2 of MIL-PRF-38535 or other alternative approved by the Qualifying Activity.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535, appendix A and herein.

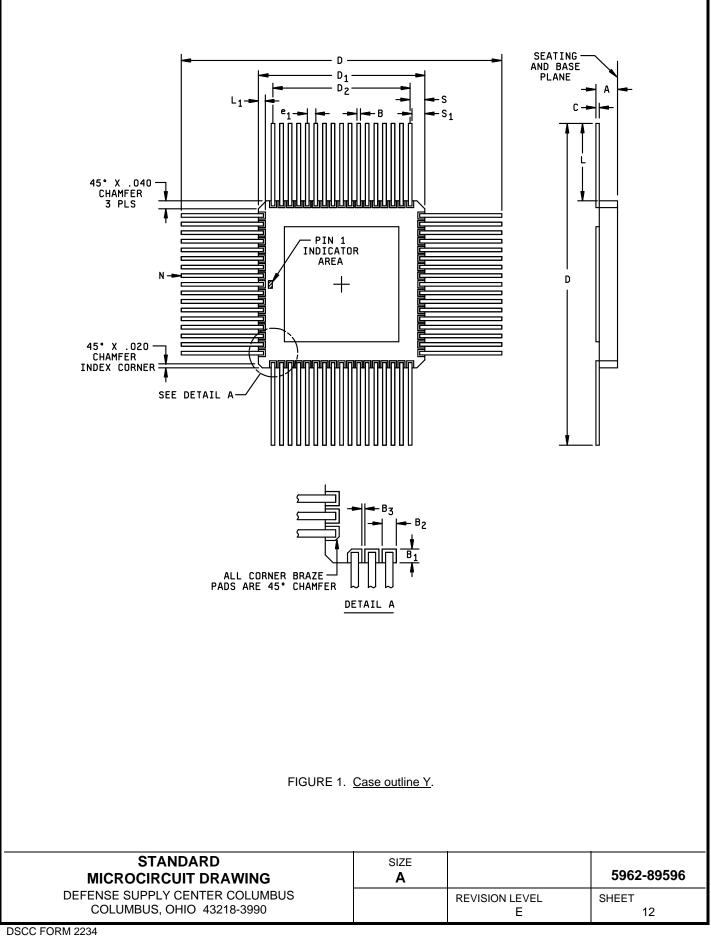

3.2.1 <u>Case outlines</u>. The case outlines shall be as specified on figure 1 or in accordance with 1.2.2 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

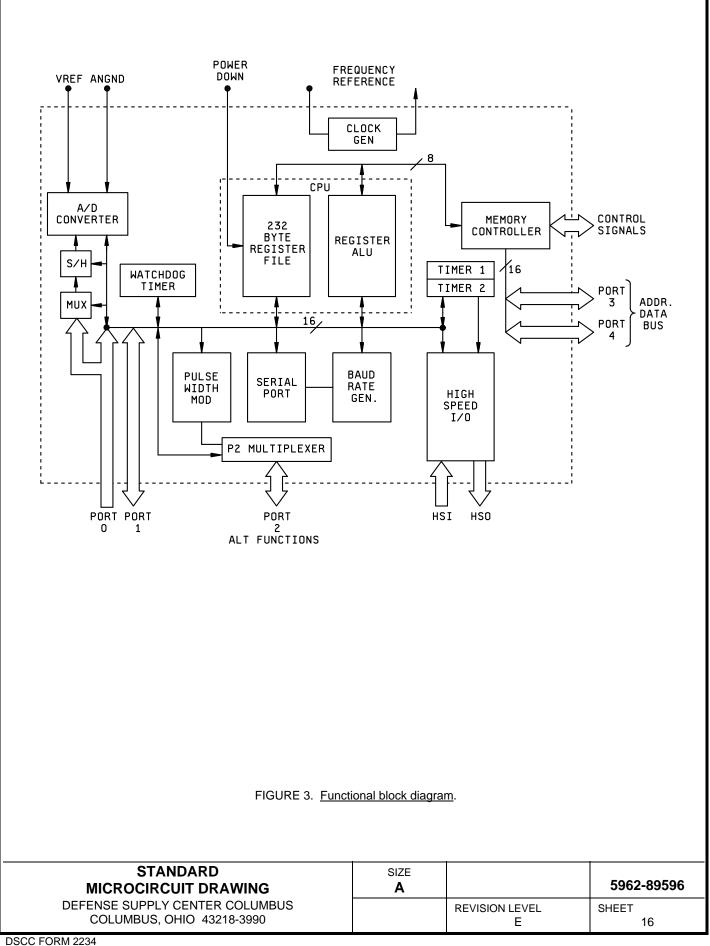

- 3.2.3 <u>Functional block diagram</u>. The functional block diagram shall be as specified on figure 3.

- 3.2.4 <u>Instruction set summary</u>. The instruction set summary shall be as specified on figure 4.

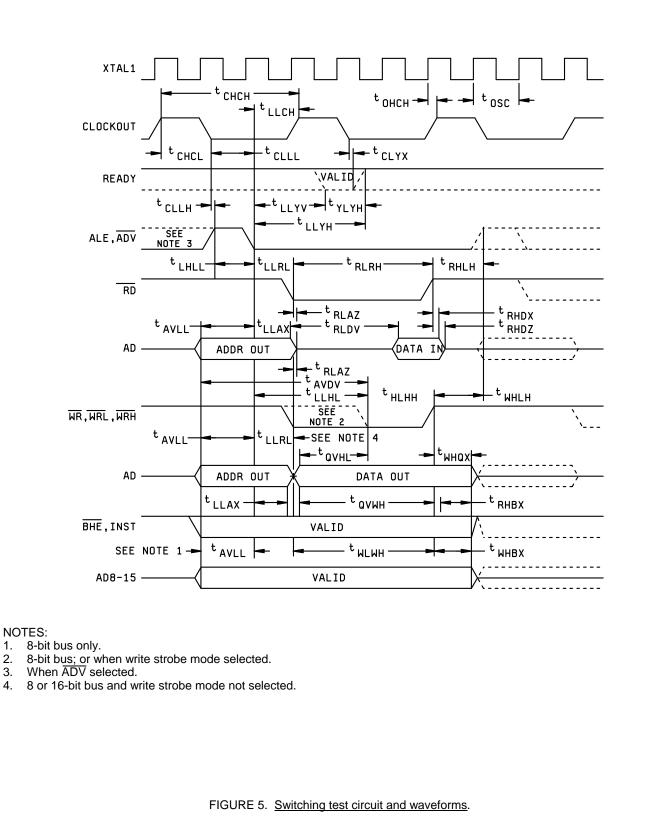

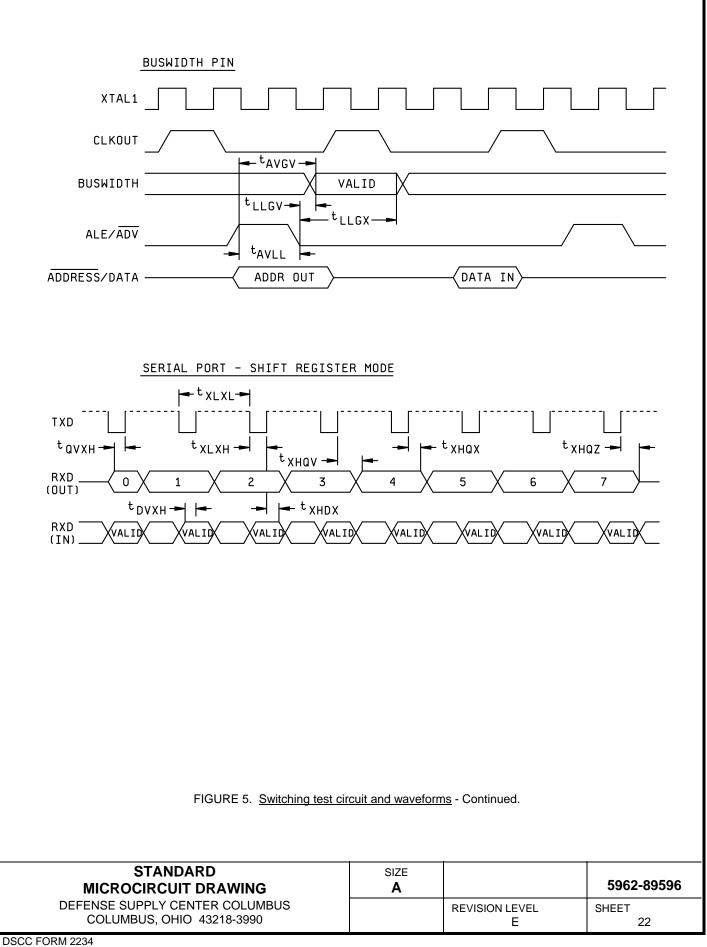

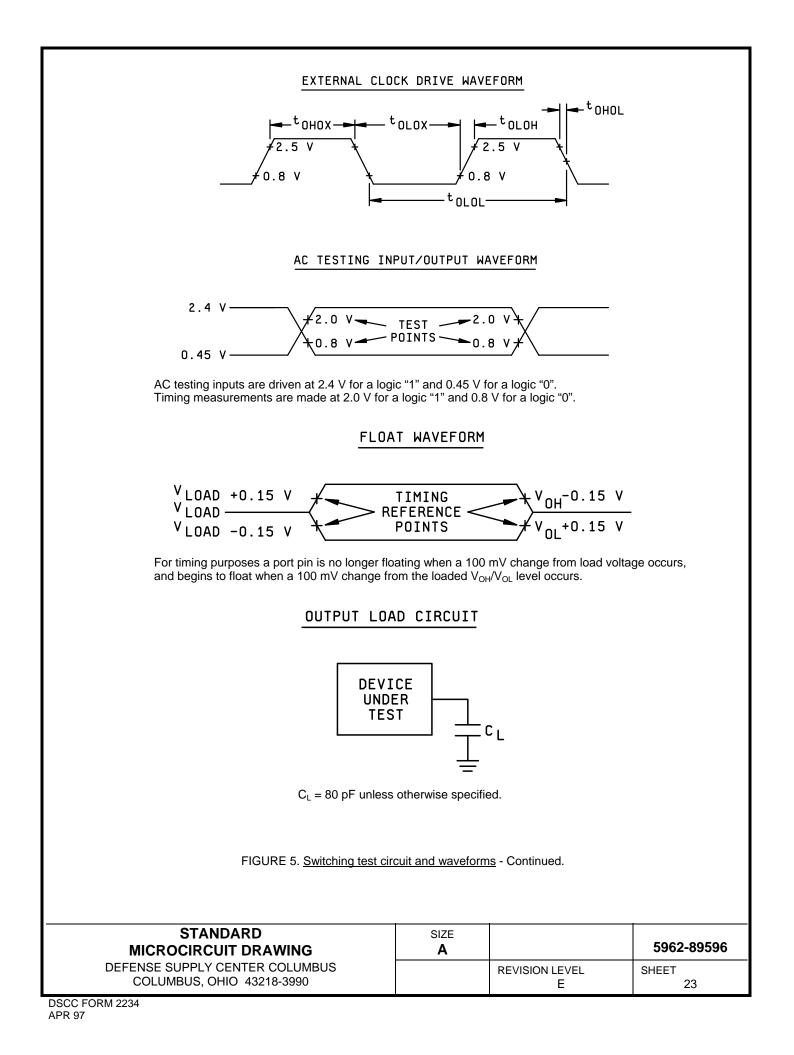

- 3.2.5 <u>Timing waveforms</u>. The timing waveforms shall be as specified on figure 5.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-89596 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | E              | 3          |

3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

3.5 <u>Marking</u>. Marking shall be in accordance with MIL-PRF-38535, appendix A. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device.

3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, Appendix A. For class Q product built in accordance with A.3.2.2 of MIL-PRF-38535, or as modified in the manufacturer's Quality Management (QM) Plan, the "QD" certification mark shall be used in place of the "QML" or "Q" certification mark.

3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.7 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-PRF-38535, appendix A and the requirements herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

3.8 Notification of change. Notification of change to DSCC-VA shall be required for any change that affects this drawing.

3.9 <u>Verification and review</u>. DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

| STANDARD                                                    | SIZE |                     |            |

|-------------------------------------------------------------|------|---------------------|------------|

| MICROCIRCUIT DRAWING                                        | Α    |                     | 5962-89596 |

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |      | REVISION LEVEL<br>E | SHEET<br>4 |

|                                                                         | T                | TABLE I. Electrical performance char                                                                                                                                                                                            | racteristics.        |                |            |                         |      |

|-------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|------------|-------------------------|------|

| Test                                                                    | Symbol           | $\begin{array}{c} Conditions  \underline{1}/\\ -55^\circ C \leq T_C \leq +125^\circ C\\ V_{CC} = V_{PD} = 5 \ V \pm 10\%\\ V_{SS} = ANGND = 0 \ V\\ f_{OSC} = 6.0 \ to \ 12 \ MHz\\ unless \ otherwise \ specified \end{array}$ | Group A<br>subgroups | Device<br>type | Lim<br>Min | nits<br>Max             | Unit |

| Supply current                                                          | I <sub>CC</sub>  | All outputs disconnected. 2/                                                                                                                                                                                                    | 1, 2, 3              | All            |            | 275                     | mA   |

| V <sub>PD</sub> supply current                                          | I <sub>PD</sub>  | Normal operation and power down.                                                                                                                                                                                                | 1, 2, 3              | All            |            | 1                       | mA   |

| V <sub>REF</sub> supply current                                         | I <sub>REF</sub> | <u>2/</u>                                                                                                                                                                                                                       | 1, 2, 3              | All            |            | 8                       | mA   |

| Input low <u>voltage</u><br>(except) RESET                              | V <sub>IL</sub>  |                                                                                                                                                                                                                                 | 1, 2, 3              | All            | -0.3       | 0.8                     | V    |

| Input low voltage, RESET                                                | V <sub>IL1</sub> |                                                                                                                                                                                                                                 | 1, 2, 3              | All            | -0.3       | 0.7                     | V    |

| Input high voltage (except RESET, NMI and XTAL1)                        | V <sub>IH</sub>  |                                                                                                                                                                                                                                 | 1, 2, 3              | All            | 2.0        | V <sub>CC</sub><br>+0.5 | V    |

| Input high voltage RESET rising                                         | V <sub>IH1</sub> |                                                                                                                                                                                                                                 | 1, 2, 3              | All            | 2.4        | V <sub>CC</sub><br>+0.5 | V    |

| Input high voltage, RESET falling hysteresis                            | V <sub>IH2</sub> |                                                                                                                                                                                                                                 | 1, 2, 3              | All            | 2.1        | V <sub>CC</sub><br>+0.5 | V    |

| Input high voltage, NMI,<br>XTAL1                                       | V <sub>IH3</sub> |                                                                                                                                                                                                                                 | 1, 2, 3              | All            | 2.2        | V <sub>CC</sub><br>+0.5 | V    |

| Input leakage current to<br>each pin of HSI, Port 3,<br>Port 4 and P2.1 | ILI              | $V_{IN} = 0$ to $V_{CC}$ $\underline{2}/$                                                                                                                                                                                       | 1, 2, 3              | All            |            | ±10                     | μΑ   |

| DC input leakage current to each pin of Port 0                          | I <sub>LI1</sub> | $V_{IN} = 0$ to $V_{CC}$ $\underline{2}/$                                                                                                                                                                                       | 1, 2, 3              | All            |            | 3                       | μΑ   |

| Input high current to EA                                                | I <sub>IH</sub>  | V <sub>IH</sub> = 2.4 V <u>2</u> /                                                                                                                                                                                              | 1, 2, 3              | All            |            | 100                     | μΑ   |

| Input low current to Port 1,<br>and P2.6, P2.7                          | I <sub>IL</sub>  | V <sub>IL</sub> = 0.45 V<br><u>2</u> /                                                                                                                                                                                          | 1, 2, 3              | All            |            | -125                    | μA   |

| Input low current to RESET                                              | I <sub>IL1</sub> | V <sub>IL</sub> = 0.45 V <u>2/</u>                                                                                                                                                                                              | 1, 2, 3              | All            | -0.25      | -2                      | mA   |

| Input low current P2.2, P2.3,<br>P2.4, READY, BUSWIDTH                  | I <sub>IL2</sub> | V <sub>IL</sub> = 0.45 V <u>2</u> /                                                                                                                                                                                             | 1, 2, 3              | All            |            | -50                     | μA   |

| San fantantan at and of table                                           |                  |                                                                                                                                                                                                                                 |                      |                |            |                         |      |

| SIZE<br>A |                     | 5962-89596 |

|-----------|---------------------|------------|

|           | REVISION LEVEL<br>E | SHEET<br>5 |

|                                                                                                    | TABLE            | I. Electrical performance character                                                                                                                                         | <u>istics</u> - Contin | ued.           |     |      |      |

|----------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|-----|------|------|

|                                                                                                    |                  | Conditions $\frac{1}{-55^{\circ}C} \le T_{C} \le +125^{\circ}C$                                                                                                             |                        |                | Lin |      |      |

| Test                                                                                               | Symbol           | $\label{eq:V_C} \begin{array}{l} V_{CC} = V_{PD} = 5 \ V \pm 10\% \\ V_{SS} = ANGND = 0 \ V \\ f_{OSC} = 6.0 \ to \ 12 \ MHz \\ unless \ otherwise \ specified \end{array}$ | Group A<br>subgroups   | Device<br>type | Min | Max  | Unit |

| Output low voltage on<br>quasi-bidirectional port pins<br>and Port 3, Port 4 when<br>used as ports | V <sub>OL</sub>  | I <sub>OL</sub> = 0.8 mA<br><u>2</u> / <u>3</u> /                                                                                                                           | 1, 2, 3                | All            |     | 0.45 | V    |

| Output low voltage on<br>quasi-bidirectional port pins<br>and Port 3, Port 4 when<br>used as ports | V <sub>OL1</sub> | $I_{OL} = 2.0 \text{ mA}$<br>2/3/4/5/                                                                                                                                       | 1, 2, 3                | All            |     | 0.75 | V    |

| Output low voltage on<br>standard output pins,<br>RESET and Bus/control<br>pins                    | V <sub>OL2</sub> | $I_{OL} = 2.0 \text{ mA}$<br><u>2/3/4/5/6/</u>                                                                                                                              | 1, 2, 3                | All            |     | 0.45 | V    |

| Output high voltage on<br>quasi-bidirectional pins                                                 | V <sub>OH</sub>  | I <sub>OH</sub> = -20 μA <u>2</u> / <u>3</u> /                                                                                                                              | 1, 2, 3                | All            | 2.4 |      | V    |

| Output high voltage on<br>standard output pins and<br>Bus/control pins                             | V <sub>OH1</sub> | I <sub>OH</sub> = -200 μA <u>2</u> / <u>3</u> /                                                                                                                             | 1, 2, 3                | All            | 2.4 |      | V    |

| Output high current on RESET                                                                       | I <sub>OH3</sub> | V <sub>OH</sub> = 2.4 V <u>2</u> /                                                                                                                                          | 1, 2, 3                | All            | -50 |      | μΑ   |

| Pin capacitance                                                                                    | Cs               | f = 1.0 Mhz<br>See 4.3.1c <u>2</u> /                                                                                                                                        | 4                      | All            |     | 10   | pF   |

| Functional tests                                                                                   |                  | See 4.3.1d <u>2</u> /                                                                                                                                                       | 7, 8                   | All            |     |      |      |

| STANDARD                                                    | SIZE |                     | _          |

|-------------------------------------------------------------|------|---------------------|------------|

| MICROCIRCUIT DRAWING                                        | Α    |                     | 5962-89596 |

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |      | REVISION LEVEL<br>E | SHEET<br>6 |

|                                              | TABLE             | I. Electrical performance character                                                                    | ristics - Contin     | ued.           |                          |                            |      |

|----------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------|----------------------|----------------|--------------------------|----------------------------|------|

|                                              |                   | $\begin{array}{l} Conditions  \underline{1}/\\ -55^{\circ}C \leq T_{C} \leq +125^{\circ}C \end{array}$ |                      |                | Lir                      |                            |      |

| Test                                         | Symbol            |                                                                                                        | Group A<br>subgroups | Device<br>type | Min                      | Max                        | Unit |

| READY hold after CLKOUT<br>edge              | t <sub>CLYX</sub> | Timing requirements (system<br>components must meet these<br>specifications).                          | 9,10, 11             | All            | 0                        |                            | ns   |

| End of ALE/ADV to READY valid                | t <sub>LLYV</sub> | See figure 5.<br>f <sub>OSC</sub> = 10 MHz                                                             | 9,10, 11             | All            |                          | 2t <sub>osc</sub> -<br>70  | ns   |

| End of ALE/ADV to READY high                 | t <sub>LLYH</sub> |                                                                                                        | 9,10, 11             | All            | 2t <sub>osc</sub><br>+40 | 4t <sub>OSC</sub> -<br>80  | ns   |

| Non-READY time                               | t <sub>YLYH</sub> |                                                                                                        | 9,10, 11             | All            |                          | 1000                       | ns   |

| Address valid to input data valid <u>7</u> / | t <sub>AVDV</sub> |                                                                                                        | 9,10, 11             | All            |                          | 5t <sub>osc</sub> -<br>120 | ns   |

| RD active to input data valid                | t <sub>RLDV</sub> |                                                                                                        | 9,10, 11             | All            |                          | 3t <sub>OSC</sub> -<br>100 | ns   |

| Data hold after $\overline{RD}$ inactive     | t <sub>RHDX</sub> |                                                                                                        | 9,10, 11             | All            | 0                        |                            | ns   |

| RD inactive to input data float              | t <sub>RHDZ</sub> |                                                                                                        | 9,10, 11             | All            | 0                        | t <sub>osc</sub> -<br>25   | ns   |

| Address valid to BUSWIDTH valid <u>7</u> /   | t <sub>AVGV</sub> |                                                                                                        | 9,10, 11             | All            |                          | 2t <sub>osc</sub> -<br>125 | ns   |

| BUSWIDTH hold after<br>ALE/ADV low           | t <sub>LLGX</sub> |                                                                                                        | 9,10, 11             | All            | t <sub>osc</sub><br>+40  |                            | ns   |

| ALE/ADV low to BUSWIDTH valid                | t <sub>LLGV</sub> |                                                                                                        | 9,10, 11             | All            |                          | t <sub>osc</sub><br>-75    | ns   |

| Oscillator frequency                         | f <sub>osc</sub>  | See figure 5.                                                                                          | 9,10, 11             | All            | 6.0                      | 12.0                       | MHz  |

| Oscillator period                            | t <sub>osc</sub>  |                                                                                                        | 9,10, 11             | All            | 83                       | 166                        | ns   |

| STANDARD                                                    | SIZE |                     |            |

|-------------------------------------------------------------|------|---------------------|------------|

| MICROCIRCUIT DRAWING                                        | Α    |                     | 5962-89596 |

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |      | REVISION LEVEL<br>E | SHEET<br>7 |

|                                                   | TABLE I.          | . Electrical performance characteris                                                                                                                                                                                                                                                                                             | <u>stics</u> - Continue | d.             |                                       |                                       |      |

|---------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------|---------------------------------------|---------------------------------------|------|

| Test                                              | Symbol            | $\begin{array}{c} \mbox{Conditions}  \underline{1} / \\ -55^{\circ}\mbox{C} \leq T_{C} \leq +125^{\circ}\mbox{C} \\ \mbox{V}_{CC} = \mbox{V}_{PD} = 5 \ \mbox{V} \pm 10\% \\ \mbox{V}_{SS} = \mbox{ANGND} = 0 \ \mbox{V} \\ \mbox{f}_{OSC} = 6.0 \ \mbox{to} \ 12 \ \mbox{MHz} \\ \mbox{unless otherwise specified} \end{array}$ | Group A<br>subgroups    | Device<br>type | Lin<br>Min                            | nits<br>Max                           | Unit |

| XTAL1 rising edge to<br>clockout rising edge      | t <sub>онсн</sub> | See figure 5<br>f <sub>OSC</sub> = 10 MHz                                                                                                                                                                                                                                                                                        | 9,10, 11                | All            | 0                                     | 120                                   | ns   |

| CLKOUT period<br><u>8</u> /                       | t <sub>CHCH</sub> | 1                                                                                                                                                                                                                                                                                                                                | 9,10, 11                | All            | 3t <sub>osc</sub>                     | 3t <sub>osc</sub>                     | ns   |

| CLKOUT high time                                  | t <sub>CHCL</sub> |                                                                                                                                                                                                                                                                                                                                  | 9,10, 11                | All            | 3t <sub>osc</sub><br>-35              | 3t <sub>OSC</sub><br>+10              | ns   |