# 8273

# Programmable HDLC/SDLC Protocol Controller

The Intel 8273 Programmable HDLC/SDLC Protocol Controller is a dedicated device designed to support the ISO/CCITT's HDLC and IBM's SDLC communication line protocols. It is fully compatible with Intel's new high performance microcomputer systems such as the MCS 188/186. A frame level command set is achieved by a unique microprogrammed dual processor chip architecture. The processing capability supported by the 8273 relieves the system CPU of the low level real-time tasks normally associated with controllers.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# 8273 PROGRAMMABLE HDLC/SDLC PROTOCOL CONTROLLER

- CCITT X.25 Compatible

- HDLC/SDLC Compatible

- Full Duplex, Half Duplex, or Loop SDLC Operation

- Up to 64K Baud Synchronous Transfers

- Automatic FCS (CRC) Generation and Checking

- Up to 9.6K Baud with On-Board Phase Locked Loop

- Programmable NRZI Encode/Decode

- Two Programmable Modem Control Ports

- Digital Phase Locked Loop Clock Recovery

- Minimum CPU Overhead

- Fully Compatible with 8048/8080/ 8085/8088/8086/80188/80186 CPUs

- Single +5V Supply

The Intel 8273 Programmable HDLC/SDLC Protocol Controller is a dedicated device designed to support the ISO/CCITT's HDLC and IBM's SDLC communication line protocols. It is fully compatible with Intel's new high performance microcomputer systems such as the MCS 188/186<sup>TM</sup>. A frame level command set is achieved by a unique microprogrammed dual processor chip architecture. The processing capability supported by the 8273 relieves the system CPU of the low level real-time tasks normally associated with controllers.

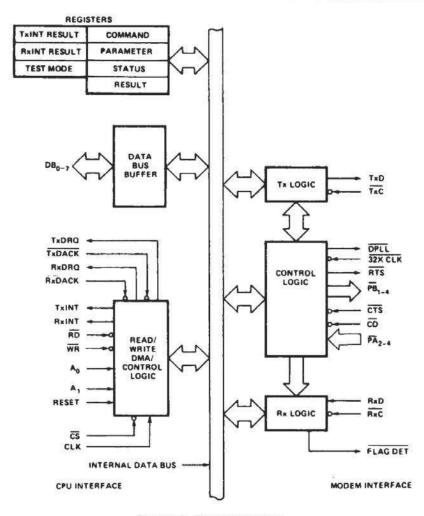

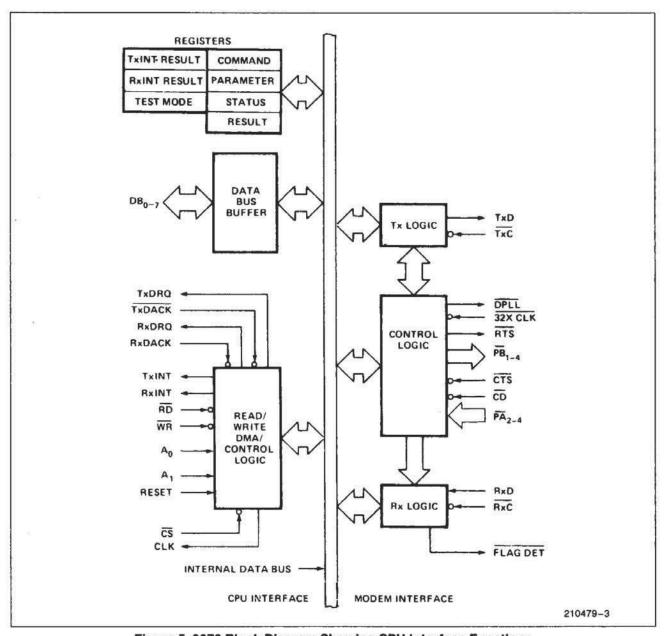

Figure 1. Block Diagram

210479-1

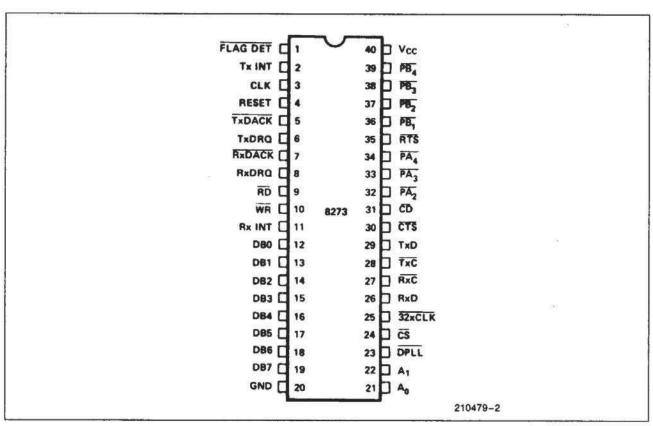

Figure 2. Configuration (PDIP)

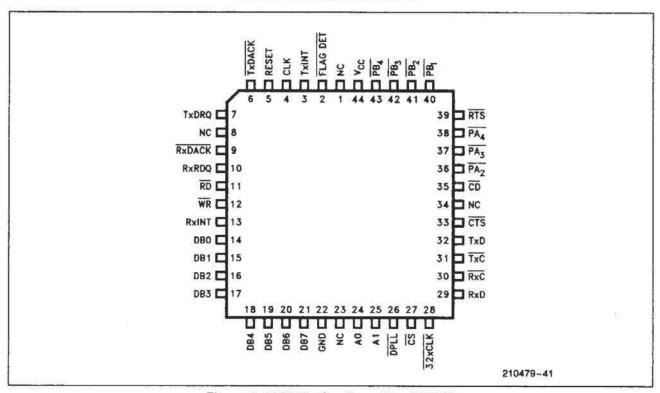

Figure 3. 8273 Pin Configuration (PLCC)

# A BRIEF DESCRIPTION OF HDLC/SDLC PROTOCOLS

#### General

The High Level Data Link Control (HDLC) is a standard communication link protocol established by International Standards Organization (ISO). HDLC is the discipline used to implement ISO X.25 packet switching systems.

The Synchronous Data Link Control (SDLC) is an IBM communication link protocol used to implement the System Network Architecture (SNA). Both the protocols are bit oriented, code independent, and ideal for full duplex communication. Some common applications include terminal to terminal, terminal to CPU, CPU to CPU, satellite communication, packet switching and other high speed data links. In systems which require expensive cabling and interconnect hardware, any of the two protocols could be used to simplify interfacing (by going serial), thereby reducing interconnect hardware costs. Since both the protocols are speed independent, reducing interconnect hardware could become an important application.

#### Network

In both the HDLC and SDLC line protocols, according to a pre-assigned hierarchy, a PRIMARY (Control) STATION controls the overall network (data link) and issues commands to the SECONDARY (Slave) STATIONS. The latter comply with instructions and respond by sending appropriate RE-SPONSES. Whenever a transmitting station must end transmission prematurely it sends an ABORT character. Upon detecting an abort character, a receiving station ignores the transmission block called a FRAME. Time fill between frames can be accomplished by transmitting either continuous frame preambles called FLAGS or an abort character. A time fill within a frame is not permitted. Whenever a station receives a string of more than fifteen consecutive ones, the station goes into an IDLE state.

#### **Frames**

A single communication element is called a FRAME which can be used for both Link Control and data transfer purposes. The elements of a frame are the

beginning eight bit FLAG (F) consisting of one zero, six ones, and a zero, an eight bit ADDRESS FIELD (A), an eight bit CONTROL FIELD (C), a variable (N-bit) INFORMATION FIELD (I), a sixteen bit FRAME CHECK SEQUENCE (FCS), and an eight bit end FLAG (F), having the same bit pattern as the beginning flag. In HDLC the Address (A) and Control (C) bytes are extendable. The HDLC and the SDLC use three types of frames; an Information Frame is used to transfer data, a Supervisory Frame is used for control purposes, and a Non-sequenced Frame is used for initialization and control of the secondary stations.

#### Frame Characteristics

An important characteristic of a frame is that is contents are made code transparent by use of a zero bit insertion and deletion technique. Thus, the user can adopt any format or code suitable for his system-it may even be a computer word length or a "memory dump". The frame is bit oriented that is, bits, not characters in each field, have specific meanings. The Frame Check Sequence (FCS) is an error detection scheme similar to the Cyclic Redundancy Checkword (CRC) widely used in magnetic disk storage devices. The Command and Response information frames contain sequence numbers in the control fields identifying the sent and received frames. The sequence numbers are used in Error Recovery Procedures (ERP) and as implicit acknowledgement of frame communication, enhancing the true full-duplex nature of the HDLC/SDLC protocols.

In contrast, BISYNC is basically half-duplex (two way alternate) because of necessity to transmit immediate acknowledgement frames. HDLC/SDLC therefore saves propagation delay times and have a potential of twice the throughput rate of BISYNC.

It is possible to use HDLC or SDLC over half duplex lines but there is a corresponding loss in throughput because both are primarily designed for full-duplex communication. As in any synchronous system, the bit rate is determined by the clock bits supplied by the modem, protocols themselves are speed independent.

A byproduct of the use of zero-bit insertion-deletion technique is the non-return-to-zero invert (NRZI) data transmission/reception compatibility. The latter allows HDLC/SDLC protocols to be used with asynchronous data communication hardware in which the clocks are derived from the NRZI encoded data.

#### References

IBM Synchronous Data Link Control General Information, IBM, GA27-3093-1.

Standard Network Access Protocol Specification, DATAPAC, Trans-Canada Telephone System CCG111

Recommendation X.25 ISO/CCITT March 2, 1976. IBM 3650 Retail Store System Loop Interface OEM Information, IBM, GA 27-3098-0 Guidebook to Data Communciations, Training Manual, Hewlett-Packard 5955-1715

IBM Introduction to Teleprocessing, IBM, GC 20-8095-02

System Network Architecture, Technical Overview, IBM, GA 27-3102

System Network Architecture Format and Protocol, IBM GA 27-3112

| OPENING  | ADDRESS   | CONTROL   | INFORMATION                           | FRAME CHECK    | CLOSING  |  |

|----------|-----------|-----------|---------------------------------------|----------------|----------|--|

| FLAG (F) | FIELD (A) | FIELD (C) | FIELD (I)                             | SEQUENCE (FCS) | FLAG (F) |  |

| 01111110 | 8 BITS    | 8 BITS    | VARIABLE LENGTH<br>(ONLY IN 1 FRAMES) | 16 BITS        | 01111110 |  |

Figure 4. Frame Format

**Table 1. Pin Description**

| Symbol                           | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                      |

|----------------------------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>                  | 40         |      | POWER SUPPLY: +5V Supply.                                                                                                                                                                                                              |

| GND                              | 20         |      | GROUND: Ground.                                                                                                                                                                                                                        |

| RESET                            | 4          | 1    | RESET: A high signal on this pin will force the 8273 to an idle state. The 8273 will remain idle until a command is issued by the CPU. The modem interface output signals are forced high. Reset must be true for a minimum of 10 TCY. |

| CS                               | 24         | 1    | CHIP SELECT: The RD and WR inputs are enabled by the chip select input.                                                                                                                                                                |

| DB <sub>0</sub> -DB <sub>7</sub> | 12-19      | 1/0  | DATA BUS: The Data Bus lines are bidirectional three-state lines which interface with the system Data Bus.                                                                                                                             |

| WR                               | 10         | Ï    | WRITE INPUT: The Write signal is used to control the transfer of either a command or data from CPU to the 8273.                                                                                                                        |

| RD                               | 9          | ı    | <b>READ INPUT:</b> The Read signal is used to control the transfer of either a data byte or a status word from the 8273 to the CPU.                                                                                                    |

| TxINT                            | 2          | . 0  | TRANSMITTER INTERRUPT: The Transmitter interrupt signal indicates that the transmitter logic requires service.                                                                                                                         |

| RxINT                            | 11         | 0    | <b>RECEIVER INTERRUPT:</b> The Receiver interrupt signal indicates that the Receiver logic requires service.                                                                                                                           |

| TxDRQ                            | 6          | 0    | TRANSMITTER DATA REQUEST: Requests a transfer of data between memory and the 8273 for a transmit operation.                                                                                                                            |

| RxRDQ                            | 8          | 0    | <b>RECEIVER DMA REQUEST:</b> Requests a transfer of data between the 8273 and memory for a receive operation.                                                                                                                          |

Table 1. Pin Description (Continued)

| Symbol                         | Pin<br>No. | Туре | Name and Function                                                                                                                                                                                                                                                               |  |  |  |  |

|--------------------------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TXDACK                         | 5          | 1    | TRANSMITTER DMA ACKNOWLEDGE: The Transmitter DMA acknowledge signal notifies the 8273 that the TxDMA cycle has been granted.                                                                                                                                                    |  |  |  |  |

| RxDACK                         | 7          | 1    | RECEIVER DMA ACKNOWLEDGE: The Receiver DMA acknowledge signal notifies the 8273 that the RxDMA cycle has been granted.                                                                                                                                                          |  |  |  |  |

| A <sub>0</sub> -A <sub>1</sub> | 21-22      | 1    | ADDRESS: These two lines are CPU Interface Register Select lines.                                                                                                                                                                                                               |  |  |  |  |

| TxD                            | 29         | 0    | TRANSMITTER DATA: This line transmits the serial data to the communication channel.                                                                                                                                                                                             |  |  |  |  |

| TxC                            | 28         | 1    | TRANSMITTER CLOCK: The transmitter clock is used to synchronize the transmit data.                                                                                                                                                                                              |  |  |  |  |

| RxD                            | 26         | I    | RECEIVER DATA: This line receives serial data from the communication channel.                                                                                                                                                                                                   |  |  |  |  |

| RxC                            | 27         | 1    | <b>RECEIVER CLOCK:</b> The Receiver Clock is used to synchronize receive data.                                                                                                                                                                                                  |  |  |  |  |

| 32X CLK                        | 25         | 1    | 32X CLOCK: The 32X clock is used to provide clock recovery when ar asynchronous modem is used. In loop configuration the loop station can run without an accurate 1X clock by using the 32X CLK in conjunction with the DPLL output. (This pin must be grounded when not used.) |  |  |  |  |

| DPLL                           | 23         | 0    | DIGITAL PHASE LOCKED LOOP: Digital Phase Locked Loop output can be tied to RxC and/or TxC when 1X clock is not available. DPLL is used with 32X CLK.                                                                                                                            |  |  |  |  |

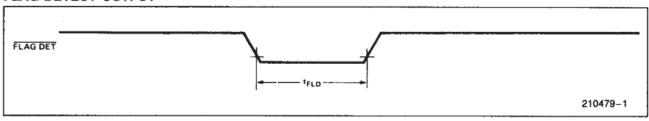

| FLAG DET                       | 1          | 0    | FLAG DETECT: Flag Detect signals that a flag (01111110) has been received by an active receiver.                                                                                                                                                                                |  |  |  |  |

| RTS                            | 35         | 0    | REQUEST TO SEND: Request to Send signals that the 8273 is ready to transmit data.                                                                                                                                                                                               |  |  |  |  |

| CTS                            | 30         | Ī    | CLEAR TO SEND: Clear to Send signals that the modem is ready to accept data from the 8273.                                                                                                                                                                                      |  |  |  |  |

| CD                             | 31         | 1    | CARRIER DETECT: Carrier Detect signals that the line transmission has started and the 8273 may begin to sample data on RxD line.                                                                                                                                                |  |  |  |  |

| PA <sub>2-4</sub>              | 32-34      | ı    | GENERAL PURPOSE INPUT PORTS: The logic levels on these lines can be Read by the CPU through the Data Bus Buffer.                                                                                                                                                                |  |  |  |  |

| PB <sub>1−4</sub>              | 36-39      | 0    | GENERAL PURPOSE OUTPUT PORTS: The CPU can write these output lines through Data Bus Buffer.                                                                                                                                                                                     |  |  |  |  |

| CLK                            | 3          | I    | CLOCK: A square wave TTL clock.                                                                                                                                                                                                                                                 |  |  |  |  |

### **FUNCTIONAL DESCRIPTION**

#### General

The Intel 8273 HDLC/SDLC controller is a micro-computer peripheral device which supports the International Standards Organization (ISO) High Level Data Link Control (HDLC), and IBM Synchronous Data Link Control (SDLC) communications protocols. This controller minimizes CPU software by supporting a comprehensive frame-level instruction set and by hardware implementation of the low level tasks associated with frame assembly/disassembly and data integrity. The 8273 can be used in either synchronous or asynchronous applications.

In asynchronous applications the data can be programmed to be encoded/decoded in NRZI code. The clock is derived from the NRZI data using a digital phase locked loop. The data transparency is achieved by using a zero-bit insertion/deletion technique. The frames are automatically checked for errors during reception by verifying the Frame Check Sequence (FCS); the FCS is automatically generated and appended before the final flag in transmit. The 8273 recognizes and can generate flags (01111110) Abort, Idle, and GA (EOP) characters.

The 8273 can assume either a primary (control) or a secondary (slave) role. It can therefore be readily implemented in an SDLC loop configuration as typified by the IBM 3650 Retail Store System by programming the 8273 into a one-bit delay mode. In such a configuration, a two wire pair can be effectively used for data transfer between controllers and loop stations. The digital phase locked loop output pin can be used by the loop station without the presence of an accurate Tx clock.

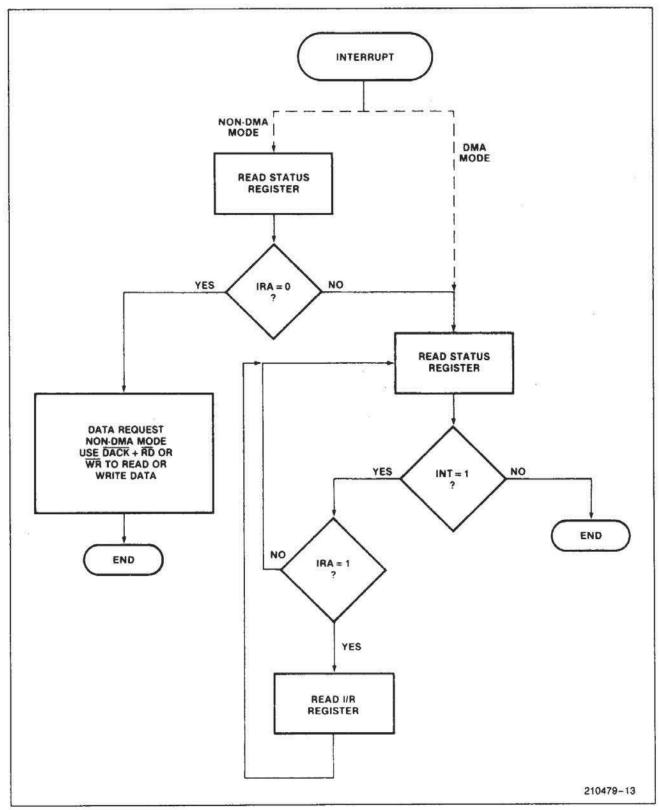

#### **CPU Interface**

The CPU interface is optimized for the MCS-80/85TM bus with an 8257 DMA controller. However, the interface is flexible, and allows either DMA or non-DMA data transfers, interrupt or non-interrupt driven. It further allows maximum line utilization by providing early interrupt mechanism for buffered (only the information field can be transferred to memory) Tx command overlapping. It also provides separate Rx and Tx interrupt output channels for efficient operation. The 8273 keeps the interrupt request active until all the associated interrupt results have been read.

The CPU utilizes the CPU interface to specify commands and transfer data. It consists of seven registers addressed via  $\overline{\text{CIA}}$ ,  $A_1$ ,  $A_0$ ,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  signals and two independent data registers for receive data and transmit data.  $A_1$ ,  $A_0$  are generally derived from two low order bits of the address bus. If an 8080 based CPU is utilized, the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  signals may be driven by the 8228  $\overline{\text{I/OR}}$  and  $\overline{\text{I/OW}}$ . The table shows the seven register select decoding:

| A <sub>1</sub> | A <sub>0</sub> | TXDACK | RXDACK | ĊŚ | RD | WR | Register       |

|----------------|----------------|--------|--------|----|----|----|----------------|

| 0              | 0              | 1      | 1      | 0  | 1  | 0  | Command        |

| 0              | 0              | 1      | 1      | 0  | 0  | 1  | Status         |

| 0              | 1              | 1      | 1      | 0  | 1  | 0  | Parameter      |

| 0              | 1              | 1      | 1      | 0  | 0  | 1  | Result         |

| 1              | 0              | 1      | 1      | 0  | 1  | 0  | Reset          |

| 1              | 0              | 1      | 1      | 0  | 0  | 1  | TxINT Result   |

| 1              | 1              | 1      | 1      | 0  | 1  | 0  | 22 <del></del> |

| 1              | 1              | 1      | 1      | 0  | 0  | 1  | RxINT Result   |

| X              | X              | 0      | 1      | 1  | 1  | 0  | Transmit Data  |

| X              | X              | 1      | 0      | 1  | 0  | 1  | Receive Data   |

Figure 5. 8273 Block Diagram Showing CPU Interface Functions

# **Register Description**

#### COMMAND

Operations are initiated by writing an appropriate command in the Command Register.

#### **PARAMETER**

Parameters of commands that require additioal information are written to this register.

#### RESULT

Contains an immediate result describing an outcome of an executed command.

#### TRANSMIT INTERRUPT RESULT

Contains the outcome of 8273 transmit operation (good/bad completion).

#### RECEIVE INTERRUPT RESULT

Contains the outcome of 8273 receive operation (good/bad completion), followed by additional results which detail the reason for interrupt.

#### STATUS

The status register reflects the state of the 8273 CPU Interface.

#### **DMA Data Transfers**

The 8273 CPU interface supports two independent data interfaces: receive data and transmit data. At high data transmission speeds the data transfer rate of the 8273 is great enough to justify the use of direct memory access (DMA) for the data transfers. When the 8273 is configured in DMA mode, the elements of the DMA interfaces are:

#### **TxDRQ: TRANSMIT DMA REQUEST**

Requests a transfer of data between memory and the 8273 for a transmit operation.

#### TXDACK: TRANSMIT DMA ACKNOWLEDGE

The TxDACK signal notifies the 8273 that a transmit DMA cycle has been granted. It is also used with WR to transfer data to the 8273 in non-DMA mode. Note: RD must not be asserted while TxDACK is active.

#### **RXDRQ: RECEIVE DMA REQUEST**

Requests a transfer of data between the 8273 and memory for a receive operation.

#### RXDACK: RECEIVE DMA ACKNOWLEDGE

The RxDACK signal notifies the 8273 that a receive DMA cycle has been granted. It is also used with RD to read data from the 8273 in non-DMA mode. Note: WR must not be asserted while RxDACK is active.

#### RD, WR: READ, WRITE

The RD and WR signals are used to specify the direction of the data transfer.

DMA transfers require the use of a DMA controller such as the Intel 8257. The function of the DMA controller is to provide sequential addresses and timing for the transfer, at a starting address determined by the CPU. Counting of data blocks lengths is performed by the 8273.

To request a DMA transfer the 8273 raises the appropriate DMA REQUEST. DMA ACKNOWLEDGE and READ enables DMA data onto the bus (independently of CHIP SELECT). DMA ACKNOWLEDGE and WRITE transfers DMA data to the 8273 (independent of CHIP SELECT).

It is also possible to configure the 8273 in the non-DMA data transfer mode. In this mode the CPU module must pass data to the 8273 in response to non-DMA data requests indicated by status word.

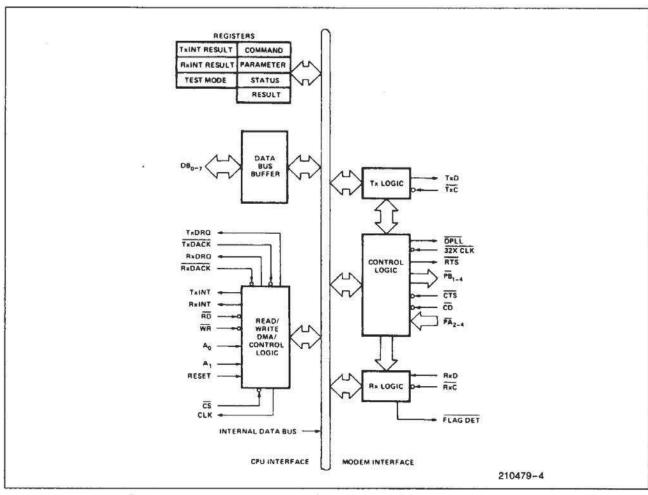

#### Modem Interface

The 8273 Modem interface provides both dedicated and user defined modem control functions. All the control signals are active low so that EIA RS-232C inverting drivers (MC 1488) and inverting receivers (MC 1489) may be used to interface to standard modems. For asynchronous operation, this interface supports programmable NRZI data encode/decode, a digital phase locked loop for efficient clock extraction from NRZI data, and modem control ports with automatic CTS, CD monitoring and RTS generation. This interface also allows the 8273 to operate in PRE-FRAME SYNC mode in which the 8273 prefixes 16 transitions to a frame to synchronize idle lines before transmission of the first flag.

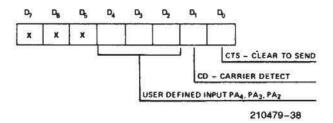

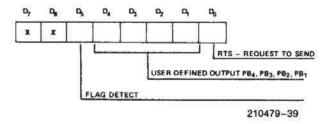

It should be noted that all the 8273 port operations deal with logical values, for instance, bit D0 of Port A will be a one when CTS (Pin 30) is a physical zero (logical one).

#### PORT A-INPUT PORT

During operation, the 8273 interrogates input pins  $\overline{\text{CTS}}$  (Clear to Send) and  $\overline{\text{CD}}$  (Carrier Detect).  $\overline{\text{CTS}}$  is used to condition the start of a transmission. If during transmission  $\overline{\text{CTS}}$  is lost the 8273 generates an interrupt. During reception, if  $\overline{\text{CD}}$  is lost, the 8273 generates an interrupt.

The user defined input bits correspond to the 8273 PA<sub>4</sub>, PA<sub>3</sub> and PA<sub>2</sub> pins. The 8273 does not interrogate or manipulate these bits.

#### PORT B-OUTPUT PORT

During normal operation, if the CPU sets RTS active, the 8273 will not change this pin; however, if the CPU sets RTS inactive, the 8273 will activate it before each transmission and deactivate it one byte time after transmission. While the receiver is active the flag detect pin is pulsed each time a flag sequence is detected in the receive data stream. Following an 8273 reset, all pins of Port B are set to a high, inactive level.

The user defined output bits correspond to the state of PB<sub>4</sub>-PB<sub>1</sub> pins. The 8273 does not interrogate or manipulate these bits.

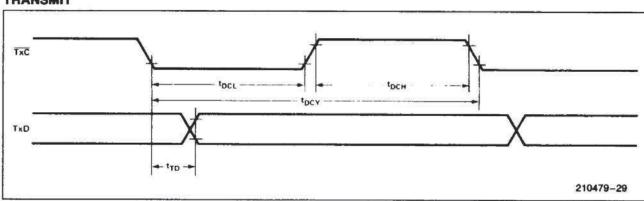

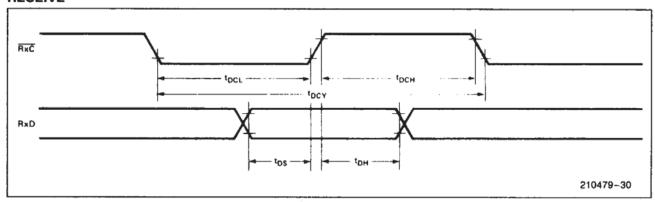

### **Serial Data Logic**

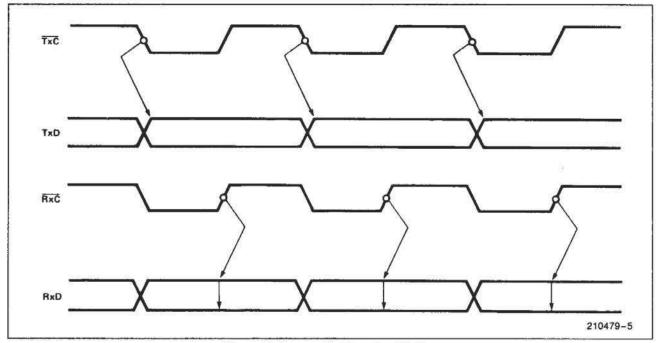

The Serial data is synchronized by the user transmit (TxC) and receive (RxC) clocks. The leading edge of TxC generates new transmit data and the trailing edge of RxC is used to capture receive data. The NRZI encoding/decoding of the receive and transmit data is programmable.

The diagnostic features included in the Serial Data logic are programmable loop back of data and selectable clock for the receiver. In the loop-back mode, the data presented to the TxD pin is internally routed to the receive data input circuitry in place of the RxD pin, thus allowing a CPU to send a message to itself to verify operation of the 8273.

In the selectable clock diagnostic feature, when the data is looped back, the receiver may be presented incorrect sample timing by the external circuitry. The user may select to substitute the  $\overline{TxC}$  pin for the  $\overline{RxC}$  input on-chip so that the clock used to generate the loop back data is used to sample it. Since  $\overline{TxC}$  is generated off the leading edge of  $\overline{TxC}$  and  $\overline{RxD}$  is sampled on the trailing edge, the selected clock allows bit synchronism.

#### **ASYNCHRONOUS MODE INTERFACE**

Although the 8273 is fully compatible with the HDLC/SDLC communication line protocols, which are primarily designed for sychronous communication, the 8273 can also be used in asynchronous applications by using this interface. The interface employs a digital phase locked loop (DPLL) for clock recovery from a receive data stream and programmable NRZI encoding and decoding of data. The use of NRZI coding with SDLC transmission guarantees that within a frame, data transitions will occur at least every five bit times-the longest sequence of ones which may be transmitted without zero-bit insertion. The DPLL should be used only when NRZI coding is used since the NRZI coding will transmit zero sequence as line transitions. The digital phase locked loop also facilitates full-duplex and half-duplex asynchronous implementation with, or without modems.

Figure 6. 8273 Block Diagram Showing Control Logic Functions

Figure 7. Transmit/Receive Timing

#### DIGITAL PHASE LOCKED LOOP

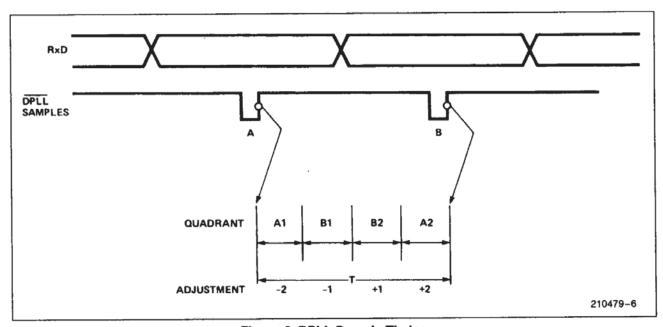

In asynchronous applications, the clock is derived from the receiver data stream by the use of the digital phase locked loop (DPLL). The DPLL requires a clock input at 32 times the required baud rate. The receive data (RxD) is sampled with this \$\frac{32X}{CLK}\$ and the 8273 DPLL supplies a sample pulse nomminally centered on the RxD bit cells. The DPLL has a built-in "stiffness" which reduces sensitivity to line noise and bit distortion. This is accomplished by making phase error adjustments in discrete increments. Since the nominal pulse is made to occur at 32 counts of the \$\frac{32X}{CLK}\$, these counts are subtracted or added to the nominal, depending upon which quadrant of the four error quadrants the data edge occurs in. For example if an RxD edge is detected in

quadrant A1, it is apparent that the  $\overline{DPLL}$  sample "A" was placed too close to the trailing edge of the data cell; sample "B" will then be placed at T =  $(T_{nominal} - 2 \text{ counts}) = 30 \text{ counts of the } \overline{32X \text{ CLK}} \text{ to}$  move the sample pulse "B" toward the nominal center of the next bit cell. A data edge occuring in quadrant B1 would cause a smaller adjustment of phase with T = 31 counts of the  $\overline{32X \text{ CLK}}$ . Using this technique the  $\overline{DPLL}$  pulse will converge to nominal bit center within 12 data bit times, worst case, with constant incoming RxD edges.

A method of attaining bit synchronism following a line idle is to use PRE-FRAME SYNC mode of transmission.

Figure 8. DPLL Sample Timing

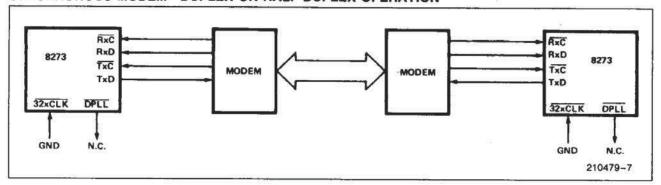

#### SYNCHRONOUS MODEM—DUPLEX OR HALF DUPLEX OPERATION

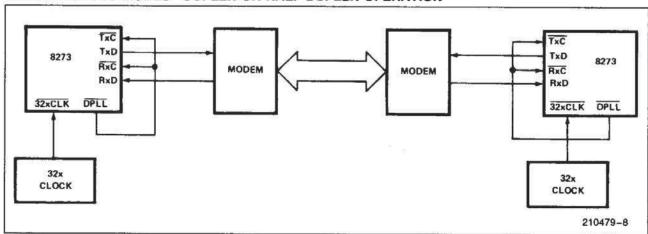

### ASYNCHRONOUS MODES-DUPLEX OR HALF DUPLEX OPERATION

#### ASYNCHRONOUS-NO MODEMS-DUPLEX OR HALF DUPLEX

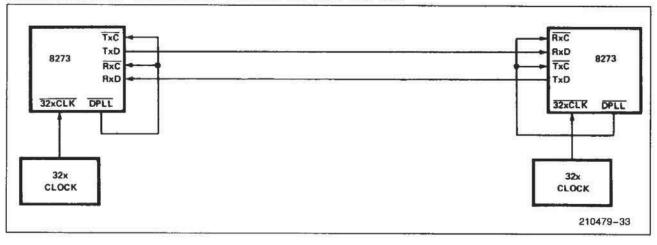

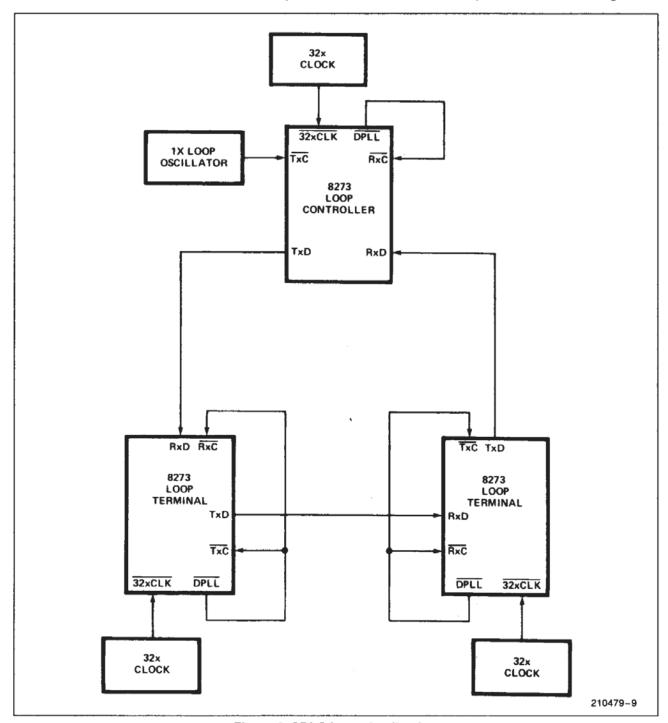

#### SDLC LOOP

The DPLL simplifies the SDLC loop station implementation. In this application, each secondary station on a loop data link is a repeater set in one-bit delay mode. The signals sent out on the loop by the loop controller (primary station) are relayed from station to station then, back to the controller. Any sec-

ondary station finding its address in the A field captures the frame for action at that station. All received frames are relayed to the next station on the loop.

Loop stations are required to derive bit timing from the incoming NRZI data stream. The DPLL generates sample Rx clock timing for reception and uses the same clock to implement Tx clock timing.

Figure 9. SDLC Loop Application

#### PRINCIPLES OF OPERATION

The 8273 is an intelligent peripheral controller which relieves the CPU of many of the rote tasks associated with constructing and receiving frames. It is fully compatible with the MCS-80/85<sup>TM</sup> system bus. As a peripheral device, it accepts commands from a CPU, executes these commands and provides an Interrupt and Result back to the CPU at the end of the execution. The communication with the CPU is done by activation of  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , pins while the A<sub>1</sub>, A<sub>0</sub> select the appropriate registers on the chip as described in the Hardware Description Section.

The 8273 operation is composed of the following sequence of events:

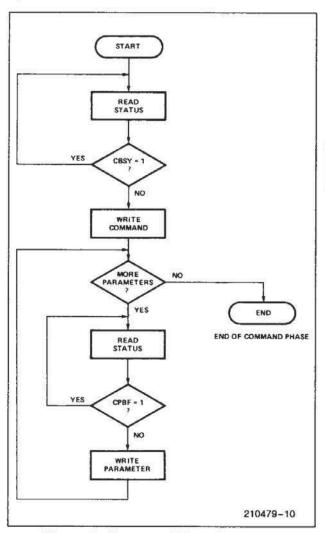

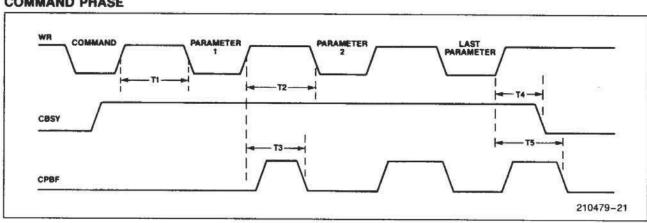

#### The Command Place

During the command phase, the software writes a command to the command register. The command bytes provide a general description of the type of operation requested. Many commands require more detailed information about the command. In such a case up to four parameters are written into the parameter register. The flowchart of the command phase indicates that a command may not be issued if the Status Register indicates that the device is busy. Similarly if a parameter is issued when the Parameter Buffer shows full, incorrect operation will occur.

The 8273 is a duplex device and both transmitter and receiver may each be executing a command or passing results at any given time. For this reason separate interrupt pins are provided. However, the command register must be used for one command sequence at a time.

#### STATUS REGISTER

The status register contains the status of the 8273 activity. The description is as follows.

| D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | $D_2$ | D <sub>1</sub> | Do    |

|----------------|----------------|----------------|----------------|----------------|-------|----------------|-------|

| CBSY           | CBF            | CPBF           | CRBF           | RXINT          | TxINT | RxIRA          | TxIRA |

#### Bit 7 CBSY (Command Busy)

Indicates in-progress command, set for CPU poll when Command Register is full, reset upon command phase completion. It is improper to write a command when CBSY is set; it results in incorrect operation.

Figure 10. Command Phase Flowchart

#### Bit 6 CBF (Command Buffer Full)

Indicates that the command register is full, it is reset when the 8273 accepts the command byte but does not imply that execution has begun.

#### Bit 5 CPBF (Command Parameter Buffer Full)

CPBF is set when the parameter buffer is full, and is reset by the 8273 when it accepts the parameter. The CPU may poll CPBF to determine when additional parameters may be written.

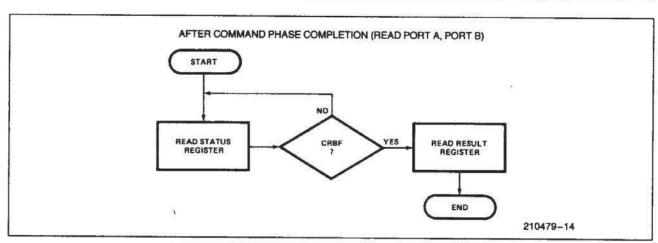

#### Bit 4 CRBF (Command Result Buffer Full)

Indicates that an executed command immediate result is present in the Result Register. It is set by 8273 and reset when CPU reads the result.

#### Bit 3 RxINT (Receiver Interrupt)

RxINT indicates that the receiver requires CPU attention. It is identical to RxINT (pin 11) and is set by the 8273 either upon good/bad completion of a specified command or by Non-DMA data transfer. It is reset only after the CPU has read the result byte or has received a data byte from the 8273 in a Non-DMA data transfer.

#### Bit 2 TxINT (Transmitter Interrupt)

The TxINT indicates that the transmitter requires CPU attention. It is identical to TxINT (pin 2). It is set by 8273 either upon good/bad completion of a specified command or by Non-DMA data transfer. It is reset only after the CPU has read the result byte or has transferred transmit data byte to the 8273 in a Non-DMA transfer.

# Bit 1 RxIRA (Receiver Interrupt Result Available)

The RxIRA is set by the 8273 when an interrupt result byte is placed in the RxINT register. It is reset after the CPU has read the RxINT register.

# Bit 0 TxIRA (Transmitter Interrupt Result Available)

The TxIRA is set by the 8273 when an interrupt result byte is placed in the TxINT register. It is reset when the CPU has read the TxINT register.

#### THE EXECUTION PHASE

Upon accepting the last parameter, the 8273 enters into the Execution Phase. The execution phase may consist of a DMA or other activity, and may or may not require CPU intervention. The CPU intervention is eliminated in this phase if the system utilizes DMA for the data transfers, otherwise, for non-DMA data transfers, the CPU is interrupted by the 8273 via TxINT and RxINT pins, for each data byte request.

#### THE RESULT PHASE

During the result phase, the 8273 notifies the CPU of the execution outcome of a command. This phase is initiated by:

- 1. The successful completion of an operation

- 2. An error detected during an operation.

To facilitate quick network software decisions, two types of execution results are provided:

- 1. An Immediate Result

- 2. A Non-Immediate Result

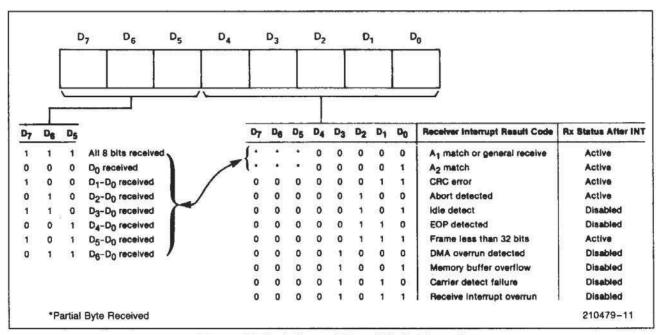

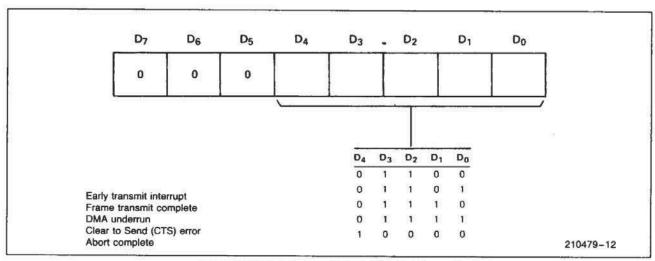

Figure 11. Rx Interrupt Result Byte Format

Figure 12. Tx Interrupt Result Byte Format

Immediate result is provided by the 8273 for commands such as Read Port A and Read Port B which have information (CTS, CD, RTS, etc.) that the network software needs to make quick operational decisions.

A command which cannot provide an immediate result will generate an interrupt to signal the beginning of the Result phase. The immediate results are provided in the Result Register; all non-immediate results are available upon device interrupt, through Tx Interrupt Result Register TxI/R or Rx Interrupt Result Register RxI/R. The result may consist of a one-byte interrupt code indicating the condition for the

interrupt and, if required, one or more bytes which detail the condition.

#### Tx and Rx Interrupt Result Registers

The Result Registers have a result code, the three high order bits  $D_7 - D_5$  of which are set to zero for all but the receive command. This command result contains a count that indicates the number of bits received in the last byte. If a partial byte is received, the high order bits of the last data byte are indeterminate.

All results indicated in the command summary must be read during the result phase.

Figure 13. Result Phase Flowchart—Interrupt Results

Figure 14. (Rx Interrupt Service)

# **DETAILED COMMAND DESCRIPTION**

#### General

The 8273 HDLC/SDLC controller supports a comprehensive set of high level commands which allows the 8273 to be readily used in full-duplex, half-duplex, synchronous, asynchronous and SDLC loop configuration, with or without modems. These frame-level commands minimize CPU and software overhead. The 8273 has address and control byte buffers which allow the receive and transmit commands to be used in buffered or non-buffered modes.

In buffered transmit mode, the 8273 transmits a flag automatically, reads the Address and Control buffer registers and transmits the fields, then via DMA, it fetches the information field. The 8273, having transmitted the information field, automatically appends the Frame Check Sequence (FCS) and the end flag. Correspondingly, in buffered read mode, the Address and Control fields are stored in their respective buffer registers and only Information Field is transferred to memory.

In non-buffered transmit mode, the 8273 transmits the beginning flag automatically, then fetches and transmits the Address, Control and Information fields from the memory, appends the FCS character and an end flag. In the non-buffered receive mode the entire contents of a frame are sent to memory with the exception of the flags and FCS.

# **HDLC** Implementation

HDLC Address and Control field are extendable. The extension is selected by setting the low order bit of the field to be extended to a one, a zero in the low order bit indicates the last byte of the respective field.

Since Address/Control field extension is normally done with software to maximize extension flexibility, the 8273 does not create or operate upon contents of the extended HDLC Address/Control fields. Extended fields are transparently passed by the 8273 to user as either interrupt results or data transfer requests. Software must assemble the fields for transmission and interrogate them upon reception.

However, the user can take advantage of the powerful 8273 commands to minimize CPU/Software overhead and simplify buffer management in handling extended fields. For instance buffered mode can be used to separate the first two bytes, then interrogate the others from buffer. Buffered mode is perfect for a two byte address field.

The 8273 when programmed, recognizes protocol characters unique to HDLC such as Abort, which is a string of seven or more ones (01111111). Since Abort character is the same as the GA (EOP) character used in SDLC Loop applications., Loop Transmit and Receive commands are not recommended to be used in HDLC. HDLC does not support Loop mode.

#### Initialization Set/Reset Commands

These commands are used to manipulate data within the 8273 registers. The Set commands have a single parameter which is a mask that corresponds to the bits to be set. (They perform a logical-OR of the specified register with the mask provided as a parameter). The Register commands have a single parameter which is a mask that has a zero in the bit positions that are to be reset. (They perform a logical-AND of the specified register with the mask).

### SET ONE-BIT DELAY (CMD CODE A4)

|      | A <sub>1</sub> | A <sub>0</sub> | $D_7$ | D <sub>6</sub> | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | $D_0$ |

|------|----------------|----------------|-------|----------------|-------|-------|-------|-------|-------|-------|

| CMD: | 0              | 0              | 1     | 0              | 1     | 0     | 0     | 1     | 0     | 0     |

| PAR: | 0              | 1              | 1     | 0              | 0     | 0     | 0     | 0     | 0     | 0     |

# intel.

When one bit delay is set, 8273 retransmits the received data stream one bit delayed. This mode is entered at a receiver character boundary, and should only be used by Loop Stations.

# RESET ONE-BIT DELAY (CMD CODE 64)

|      |   |   |   |   |   |   |   |   |   | $D_0$ |

|------|---|---|---|---|---|---|---|---|---|-------|

| CMD: | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0     |

| PAR: | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1     |

The 8273 stops the one bit delayed retransmission mode.

# SET DATA TRANSFER MODE (CMD CODE 97)

|      |   |   |   | $D_6$ |   |   |   |   |   |   |

|------|---|---|---|-------|---|---|---|---|---|---|

| CMD: | 0 | 0 | 1 | 0     | 0 | 1 | 0 | 1 | 1 | 1 |

| PAR: | 0 | 1 | 0 | 0     | 0 | 0 | 0 | 0 | 0 | 1 |

When the data transfer mode is set, the 8273 will interrupt when data bytes are required for transmission or are available from a receive. If a transmit interrupt occurs and the status indicates that there is no Transmit Result (TxIRA = 0), the interrupt is a transmit data request. If a receive interrupt occurs and the status indicates that there is no receive result (RxIRA = 0), the interrupt is a receive data request.

# RESET DATA TRANSFER MODE (CMD CODE 57)

|      |   |   |   |   |   |   |   |   |   | $D_0$ |

|------|---|---|---|---|---|---|---|---|---|-------|

| CMD: | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1     |

| PAR: | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0     |

If the Data Transfer Mode is reset, the 8273 data transfers are performed through the DMA requests without interrupting the CPU.

### SET OPERATING MODE (CMD CODE 91)

# RESET OPERATING MODE (CMD CODE 51)

|      |   |   |   | $D_6$ |   |   |   |   |   |   |

|------|---|---|---|-------|---|---|---|---|---|---|

| CMD: | 0 | 0 | 0 | 1     | 0 | 1 | 0 | 0 | 0 | 1 |

| PAR: | 0 | 1 | 1 | 1     |   |   |   |   |   |   |

Any mode switches set in CMD code 91 can be reset using this command by placing zeros in the appropriate positions.

#### (D5) HDLC MODE

In HDLC mode, a bit sequence of seven ones (01111111) is interpreted as as an abort character. Otherwise, eight ones (011111111) signal an abort.

# (D4) EOP INTERRUPT MODE

In EOP interrupt mode, an interrupt is generated whenever an EOP character (01111111) is detected by an active receiver. This mode is useful for the implementation of an SDLC loop controller in detecting the end of a message stream after a loop poll.

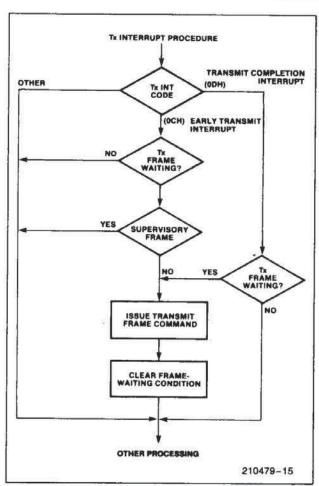

# (D3) TRANSMITTER EARLY INTERRUPT MODE (Tx)

The early interrupt mode is specified to indicate when the 8273 should generate an end of frame interrupt. When set, an early interrupt is generated when the last data character has been passed to the 8273. If the user software responds with another transmit command before the final flag is sent, the final flag interrupt will not be generated and a new frame will immediately begin when the current frame is complete. This permits frames to be separated by a single flag. If no additional Tx commands are provided, a final interrupt will follow.

#### NOTE:

In buffered mode, if a supervisory frame (no Information) Transmit command is sent in response to an early Transmit Interrupt, the 8273 will repeatedly transmit the same supervisory frame with one flag in between, until a non-supervisory transmit is issued.

Early transmitter interrupt can be used in buffered mode by waiting for a transmit complete interrupt instead of early Transmit Interrupt before issuing a transmit frame command for a supervisory frame. See Figure 15.

Figure 15

If this bit is zero, the interrupt will be generated only after the final flag has been transmitted.

#### (D2) BUFFERED MODE

If the buffered mode bit is set to a one, the first two bytes (normally the address (A) and control (C) fields) of a frame are buffered by the 8273. If this bit is a zero the address and control fields are passed to and from memory.

#### (D1) PREFRAME SYNC MODE

If this bit is set to a one the 8273 will transmit two characters before the first flag of a frame.

To guarantee sixteen line transitions, the 8273 sends two bytes of data (00)<sub>H</sub> if NRZI is set or data (55)<sub>H</sub> if NRZI is not set.

#### (D0) FLAG STREAM MODE

If this bit is set to a one, the following table outlines the operation of the transmitter.

| <b>Transmitter State</b>                | Action                                        |  |  |  |  |  |

|-----------------------------------------|-----------------------------------------------|--|--|--|--|--|

| Idle                                    | Send Flags Immediately                        |  |  |  |  |  |

| Transmit or Transmit Transparent Active | Send Flags After the<br>Transmission Complete |  |  |  |  |  |

| Loop Transmit Active                    | Ignore Command.                               |  |  |  |  |  |

| 1 Bit Delay Active                      | Ignore Command.                               |  |  |  |  |  |

If this bit is reset to zero the following table outlines the operation of the transmitter

| Transmitter State                           | Action                                               |

|---------------------------------------------|------------------------------------------------------|

| IDLE                                        | Sends Idles on Next<br>Character boundary.           |

| Transmit or Transmit-<br>Transparent Active | Send Idles after the<br>Transmission<br>is Complete. |

| Loop Transmit Active                        | Ignore Command.                                      |

| 1 Bit Delay Active                          | Ignore Command.                                      |

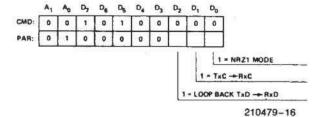

# SET SERIAL I/O MODE (CMD CODE A0)

#### RESET SERIAL I/O MODE (CMD CODE 60)

This command allows bits set in CMD code A0 to be reset by placing zeros in the appropriate positions.

|      | A <sub>1</sub> | A <sub>0</sub> | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | $D_4$ | $D_3$ | $D_2$ | $D_1$ | $D_0$ |

|------|----------------|----------------|----------------|----------------|----------------|-------|-------|-------|-------|-------|

| CMD: | 0              | 0              | 0              | 1              | 1              | 0     | 0     | 0     | 0     | 0     |

| PAR: | 0              | 1              | 1              | 1              | 1              | 1     | 1     |       |       |       |

#### (D2) LOOP BACK

If this bit is set to a one, the transmit data is internally routed to the receive data circuitry.

#### (D1) TxC → RxC

If this bit is set to a one, the transmit clock is internally routed to the receive clock circuitry. It is normally used with the loop back bit (D2).

#### (D0) NRZI MODE

If this bit is set to a one, NRZI encoding and decoding of transmit and receive data is provided. If this bit is a zero, the transmit and receive data is treated as a normal positive logic bit stream.

NRZI encoding specifies that a zero causes a change in the polarity of the transmitted signal and a one causes no polarity change. NRZI is used in all asynchronous operations. Refer to IBM document GA27-3093 for details.

# **Reset Device Command**

|      |   | _ |   |   |   |   |   |   | 1 | $D_0$ |

|------|---|---|---|---|---|---|---|---|---|-------|

| TMR: | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1     |

| TMR: | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     |

An 8273 reset command is executed by outputting a (01)<sub>H</sub> followed by (00)<sub>H</sub> to the reset register (TMR). See 8273 AC timing characteristics for Reset pulse specifications.

The reset command emulates the action of the reset pin.

- The modem control signals are forced high (inactive level).

- The 8273 status register flags are cleared.

- Any commands in progress are terminated immediately.

- The 8273 enters an idle state until the next command is issued.

- The Serial I/O and Operating Mode registers are set to zero and DMA data register transfer mode is selected.

- The device assumes a non-loop SDLC terminal role.

#### Receive Commands

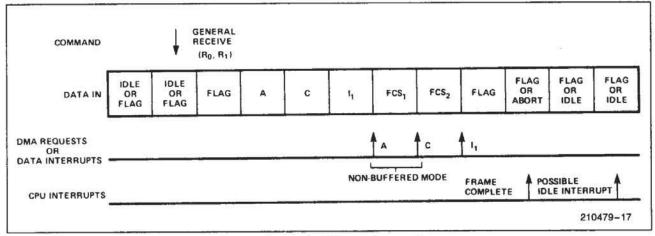

The 8273 supports three receive commands: General Receive, Selective Receive, and Selective Loop Receive.

#### **GENERAL RECEIVE (CMD CODE C0)**

General receive is a receive mode in which frames are received regardless of the contents of the address field.

|      | A <sub>1</sub> | A <sub>0</sub> | $D_7$ | $D_6$       | $D_5$ | $D_4$ | $D_3$ | $D_2$     | $D_1$ | $D_0$ |

|------|----------------|----------------|-------|-------------|-------|-------|-------|-----------|-------|-------|

| CMD: | 0              | 0              | 1     | 1           | 0     | 0     | 0     | 0         | 0     | 0     |

| PAR: | 0              | 1              | OF    |             | REC   | CEIV  |       | BYT       |       |       |

| PAR: | 0              | 1              | OF    | ST S<br>REC | EIVE  | •     |       | BYT<br>1) | E     |       |

#### NOTES:

- If buffered mode is specified, the R0, R1 receive frame length (result) is the number of data bytes received.

- If non-buffered mode is specified, the R0, R1 receive frame length (result) is the number of data bytes received plus two (the count includes the address and control bytes).

- 3. The frame check sequence (FCS) is not transferred to memory.

- Frames with less than 32 bits between flags are ignored (no interrupt generated) if the buffered mode is specified.

- In the non-buffered mode an interrupt is generated when a less than 32 bit frame is received, since data transfer requests have occurred.

- The 8273 receive is always disabled when an Idle is received after a valid frame. The CPU module must issue a receive command to re-enable the receiver.

- The intervening ABORT character between a final flag and an IDLE does not generate an interrupt.

- 8. If an ABORT Character is not preceded by a flag and is followed by an IDLE, an interrupt will be generated for the ABORT followed by an IDLE interrupt one character time later. The reception of an ABORT will disable the receiver.

#### SELECTIVE RECEIVE (CMD CODE C1)

|      | A <sub>1</sub> | A <sub>0</sub> | $D_7$             | D <sub>6</sub> | $D_5$         | $D_4$ | $D_3$ | $D_2$ | $D_1$ | $D_0$ |

|------|----------------|----------------|-------------------|----------------|---------------|-------|-------|-------|-------|-------|

| CMD: | 0              | 0              | 1                 | 1              | 0             | 0     | 0     | 0     | 0     | 1     |

| PAR: | 0              | 1              | OF                | THE            | SIGN<br>REC   | CEIV  | E     |       | Έ     |       |

| PAR: | 0              | 1              | OF                | REC            | EIVE<br>R LEI | =     |       |       | E     |       |

| PAR: | 0              | 1              | P. C. Contraction |                | E FF          |       |       |       | SS    |       |

| PAR: | 0              | 1              |                   |                | E FF          |       |       |       | SS    | 19999 |

Selective receive is a receive mode in which frames are ignored unless the address field matches any one of two address fields given to the 8273 as parameters.

When selective receive is used in HDLC the 8273 looks at the first character, if extended, software must then decide if the message is for this unit.

#### SELECTIVE LOOP RECEIVE (CMD CODE C2)

|      | A <sub>1</sub> | A <sub>0</sub> | D <sub>7</sub> | $D_6$ | $D_5$ | $D_4$ | $D_3$            | D <sub>2</sub> | D <sub>1</sub> | Do |

|------|----------------|----------------|----------------|-------|-------|-------|------------------|----------------|----------------|----|

| CMD: | 0              | 0              | 1              | 1     | 0     | 0     | 0                | 0              | 1              | 0  |

| PAR: | 0              | 0              | OF             | THE   | REC   | CEIV  | ANT<br>E<br>H (B |                | ΓE             |    |

| PAR: | 0              | 1              | OF             | REC   | EIVE  |       | ANT<br>H (B      |                | E              |    |

| PAR: | 0              | 1              |                |       |       |       | E AD<br>NE (     |                | SS             |    |

| PAR: | 0              | 1              |                |       |       |       | E AD             |                | SS             |    |

Selective loop receive operates like selective receive except that the transmitter is placed in flag stream mode automatically after detecting an EOP (01111111) following a valid received frame. The one bit delay mode is also reset at the end of a selective loop receive.

# RECEIVE DISABLE (CMD CODE 5)

Terminates an active receive command immediately.

| 10   |   |   | D <sub>7</sub> |   |   | A. I I |   |   |   |   |

|------|---|---|----------------|---|---|--------|---|---|---|---|

| CMD: | 0 | 0 | 1              | 1 | 0 | 0      | 0 | 1 | 0 | 1 |

PAR: NONE

# **Transmit Commands**

The 8273 supports three transmit commands: Transmit Frame, Loop Transmit, Transmit Transparent.

### TRANSMIT FRAME (CMD CODE C8)

|      | A <sub>1</sub> | A <sub>0</sub> | D <sub>7</sub>     | $D_6$ | $D_5$ | $D_4$         | $D_3$ | $D_2$ | $D_1$ | Do  |

|------|----------------|----------------|--------------------|-------|-------|---------------|-------|-------|-------|-----|

| CMD: | 0              | 0              | 1                  | 1     | 0     | 0             | 1     | 0     | 0     | 0   |

| PAR: | 0              | 1              | LE/                | AST : | SIGN  | IIFIC<br>IGTH | ANT   | BY1   | ΕO    | F   |

| PAR: | 0              | 1              | Contacto Total Co. | ST S  |       |               |       |       | E OF  |     |

| PAR: | 0              | 1              |                    | DRE:  |       | IELC          | OF    | TRA   | NSM   | 1IT |

| PAR: | 0              | 1              |                    | NTR   |       | IELC          | OF    | TRA   | NSN   | AIT |

Transmits one frame including: initial flag, frame check sequence, and the final flag.

If the buffered mode is specified, the L0, L1, frame length provides as a parameter is the length of the information field and the address and control fields must be input.

In unbuffered mode the frame length provided must be the length of the information field plus two and the address and control fields must be the first two bytes of data. Thus only the frame length bytes are required as parameters.

# intel.

### LOOP TRANSMIT (CMD CODE CA)

|      | A <sub>1</sub> | $A_0$ | $D_7$ | $D_6$      | $D_5$ | $D_4$         | $D_3$ | $D_2$    | $D_1$ | D <sub>0</sub> |

|------|----------------|-------|-------|------------|-------|---------------|-------|----------|-------|----------------|

| CMD: | 0              | 0     | 1     | 1          | 0     | 0             | 1     | 0        | 1     | 0              |

| PAR: | 0              | 1     |       |            |       | IIFIC<br>IGTH |       | BYT      | E O   | F              |

| PAR: | 0              | 1     |       |            |       | IFIC/         |       | BYT<br>) | E OF  |                |

| PAR: | 0              | 1     |       | DRE:       |       | IELC          | OF    | TRA      | NSM   | 1IT            |

| PAR: | 0              | 1     | ı     | NTR<br>AME |       | IEL           | OF    | TRA      | NSN   | ИIT            |

Transmits one frame in the same manner as the transmit frame command except:

- If the flag stream mode is not active transmission will begin after a received EOP has been converted to a flag.

- If the flag stream mode is active transmission will begin at the next flag boundary for buffered mode or at the third flag boundary for non-buffered mode.

- At the end of a loop transmit the one-bit delay mode is entered and the flag stream mode is reset.

#### TRANSMIT TRANSPARENT (CMD CODED C9)

|      | A <sub>1</sub> | $A_0$ | $D_7$     | $D_6$ | $D_5$      | $D_4$        | D <sub>3</sub> | $D_2$ | $D_1$ | D <sub>0</sub> |

|------|----------------|-------|-----------|-------|------------|--------------|----------------|-------|-------|----------------|

| CMD: | 0              | 0     | 1         | 1     | 0          |              |                | 0     | 0     | 1              |

| PAR: | 0              | 1     | LE/       | AST S | SIGN       | IIFIC<br>GTH | ANT<br>I (L0)  | BYT   | ΈO    | F              |

| PAR: | 0              | 1     | MO<br>FR/ | ST S  | IGN<br>LEN | IFIC/        | ANT<br>(L1)    | BYT   | E OF  | :              |

The 8273 will transmit a block of raw data without protocol, i.e., no zero bit insertion, flags, or frame check sequences.

# **Abort Transmit Commands**

An abort command is supported for each type of transmit command. The abort commands are ignored if a transmit command is not in progress.

#### ABORT TRANSMIT FRAME (CMD CODE CC)

|      |   |   |   |   |   |   |   |   |   | D <sub>0</sub> |

|------|---|---|---|---|---|---|---|---|---|----------------|

| CMD: | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0              |

PAR: NONE

After an abort character (eight contiguous ones) is transmitted, the transmitter reverts to sending flags or idles as a function of the flag stream mode specified.

#### ABORT LOOP TRANSMIT (CMD CODE CE)

|      |   |   |   | - | _ |   |   |   |   | D <sub>0</sub> |

|------|---|---|---|---|---|---|---|---|---|----------------|

| CMD: | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0              |

PAR: NONE

After a flag is transmitted the transmitter reverts to one bit delay mode.

# ABORT TRANSMIT TRANSPARENT (CMD CODE CD)

|      |   |   |   |   |   |   |   |   |   | D <sub>0</sub> |

|------|---|---|---|---|---|---|---|---|---|----------------|

| CMD: | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1              |

PAR: NONE

The transmitter reverts to sending flags or idles as a function of the flag stream mode specified.

### **Modem Control Commands**

The modem control commands are used to manipulate the modem control ports.

When read Port A or Port B commands are executed the result of the command is returned in the result register. The Bit Set Port B command requires a parameter that is a mask that corresponds to the bits to be set. The Bit Reset Port B command requires a mask that has a zero in the bit positions that are to be reset.

#### **READ PORT A (CMD CODE 22)**

|      | $A_1$ | $A_0$ | $D_7$ | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | D <sub>0</sub> |

|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------------|

| CMD: | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1     | 0              |

PAR: NONE

#### **READ PORT B (CMD CODE 23)**

|      | $A_1$ | $A_0$ | $D_7$ | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | D <sub>0</sub> |

|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----------------|

| CMD: | 0     | 0     | 0     | 0     | 1     | 0     | 0     | 0     | 1     | 1              |

PAR: NONE

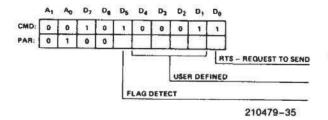

#### SET PORT B BITS (CMD CODE A3)

This command allows user defined Port B pins to be set.

### (D<sub>5</sub>) FLAG DETECT

This bit can be used to set the flag detect pin. However, it will be reset when the next flag is detected.

#### (D4-D1) USER DEFINED OUTPUTS

These bits correspond to the state of the PB<sub>4</sub>-PB<sub>1</sub> output pins.

#### (D<sub>0</sub>) REQUEST TO SEND

This is a dedicted 8273 modem control signal, and reflects the same logical state of RTS pin.

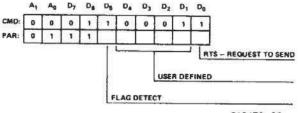

#### RESET PORT B BITS (CMD CODE 63)

This command allows Port B user defined bits to be reset.

210479-36

This command allows Port B (D<sub>4</sub>-D<sub>1</sub>) user defined bits to be reset. These bits correspond to Output Port pins (PB<sub>4</sub>-PB<sub>1</sub>).

### 8273 Command Summary

| Command Description      | Command<br>HEX | Parameter      | Results            | Result<br>Port | Completion<br>Interrupt |

|--------------------------|----------------|----------------|--------------------|----------------|-------------------------|

| Set One Bit Delay        | A4             | Set Mask       | None               | -              | No                      |

| Reset One Bit Delay      | 64             | Reset Mask     | None               | _              | No                      |

| Set Data Transfer Mode   | 97             | Set Mask       | None               | _              | No                      |

| Reset Data Transfer Mode | 57             | Reset Mask     | None               |                | No                      |

| Set Operating Mode       | 91             | Set Mask       | None               | _              | No                      |

| Reset Operating Mode     | 51             | Reset Mask     | None               | 1000           | No                      |

| Set Serial I/O Mode      | A0             | Set Mask       | None               | -              | No                      |

| Reset Serial I/O Mode    | 60             | Reset Mask     | None               | _              | No                      |

| General Receive          | CO             | B0, B1         | RIC,R0,R1,(A,C)(2) | RXI/R          | Yes                     |

| Selective Receive        | C1             | B0,B1,A1,A2    | RIC,R0,R1,(A,C)(2) | RXI/R          | Yes                     |

| Selective Loop Receive   | C2             | B0,B1,A1,A2    | RIC,R0,R1,(A,C)(2) | RXI/R          | Yes                     |

| Receive Disable          | C5             | None           | None               |                | No                      |

| Transmit Frame           | C8             | L0,L1,(A,C)(1) | TIC                | TXI/R          | Yes                     |

| Loop Transmit            | CA             | L0,L1,(A,C)(1) | TIC                | TXI/R          | Yes                     |

| Transmit Transparent     | C9             | L0,L1          | TIC                | TXI/R          | Yes                     |

| Abort Transmit Frame     | CC             | None           | TIC                | TXI/R          | Yes                     |

8273 Command Summary (Continued)

| Command Description        | Command<br>HEX | Parameter  | Results    | Result<br>Port | Completion<br>Interrupt |

|----------------------------|----------------|------------|------------|----------------|-------------------------|

| Abort Loop Transmit        | CE             | None       | TIC        | TXI/R          | Yes                     |

| Abort Transmit Transparent | CD             | None       | TIC        | TXI/R          | Yes                     |

| Read Port A                | 22             | None       | Port Value | Result         | No                      |

| Read Port B                | 23             | None       | Port Value | Result         | No                      |

| Set Port B Bit             | A3             | Set Mask   | None       | _              | No                      |

| Reset Port B Bit           | 63             | Reset Mask | None       |                | No                      |

#### NOTES:

- 1. Issued only when in buffered mode.

- 2. Read as results only in buffered mode.

# 8273 Command Summary Key

- B0— Least significant byte of the receiver buffer length.

- B1— Most significant byte of the receive buffer length.

- L0— Least significant byte of the Tx frame length.

- L1— Most significant byte of the Tx frame length.

- A1- Receive frame address match field one.

- A2- Receive frame address match field two.

- A— Address field of received frame. If nonbuffered mode is specified, this result is not provided.

- C— Control field of received frame. If nonbuffered mode is specified this result is not provided.

- RXI/R- Receive interrupt result register.

- TXI/R- Transmit interrupt result register.

- R0— Least significant byte of the length of the frame received.

- R1— Most significant byte of the length of the frame received.

- RIC— Receiver interrupt result code.

- TIC- Transmitter interrupt result code.

Figure 16. Typical Frame Reception

#### NOTE:

In order to ensure proper operation to the maximum baud rate, Receive commands or Read/Write Port commands should be written only when either the transmitter or the receiver is inactive. In full duplex systems, it is recommended that these commands be issued after servicing a transmitter interrupt but before a new transmit command is issued. When operating in full Duplex (active transmitter or receiver) with commands, the maximum data rate decreases to 49K Baud.

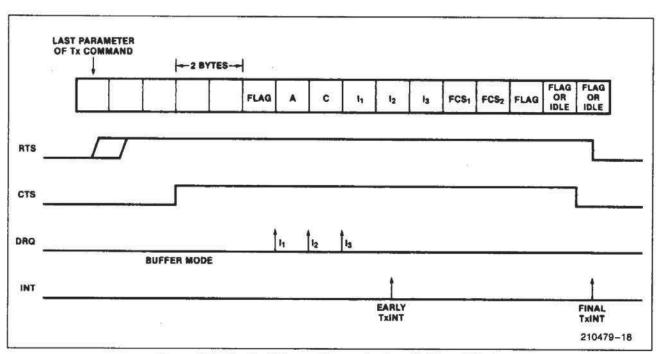

Figure 17a. Typical Frame Transmission, Buffered Mode

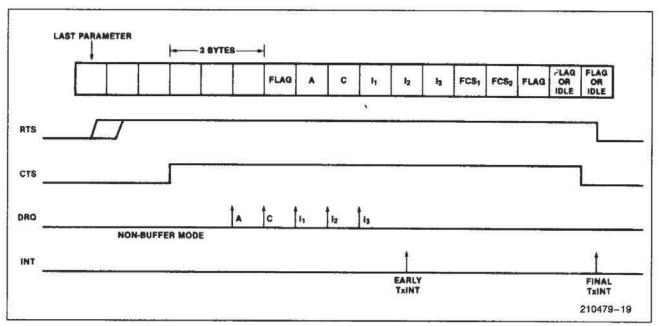

Figure 17b. Typical Frame Transmission, Non-Buffered Mode

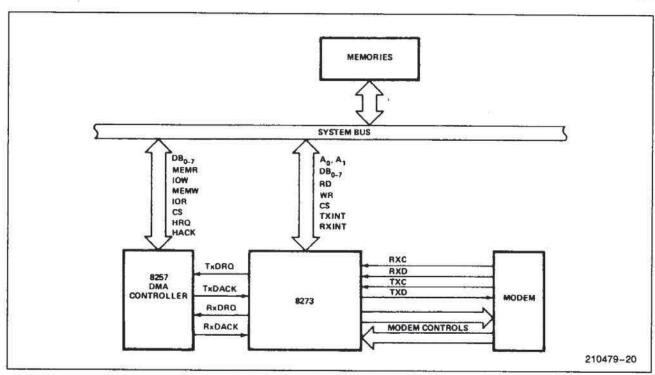

Figure 18. 8273 System Diagram

# **WAVEFORMS**

#### **COMMAND PHASE**

Table 2. Command Phase Timing (Full Duplex)

| Symbol | Timing Parameter                                                 | Buffered |     | Non-Bu | Unit |      |

|--------|------------------------------------------------------------------|----------|-----|--------|------|------|

| -,     | ,                                                                | Min      | Max | Min    | Max  | Oint |

| T1     | Between Command & First Parameter                                | 13       | 756 | 13     | 857  | tcy  |

| T2     | Between Consecutive Parameters                                   | 10       | 604 | 10     | 705  | tcy  |

| ТЗ     | Command Parameter Buffer Full Bit<br>Reset after Parmeter Loaded | 10       | 604 | 10     | 705  | tcy  |

| T4     | Command Busy Bit Reset after Last<br>Parameter                   | 128      | 702 | 128    | 803  | tcy  |

| T5     | CPBF Bit Reset after Last Parameter                              | 10       | 604 | 10     | 705  | tcy  |

# WAVEFORMS (Continued)

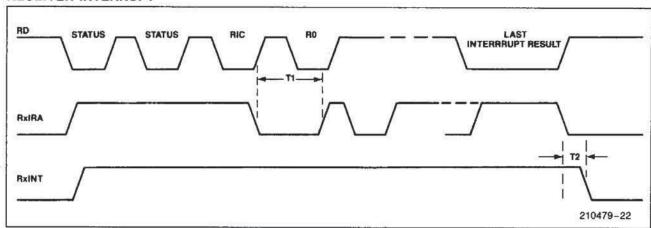

# RECEIVER INTERRUPT

**Table 3. Receiver Interrupt Result Timing**

| Symbol | Timing Parameter (Clock Cycles)                | Buffered |     | Non-Buffered |     | Unit |

|--------|------------------------------------------------|----------|-----|--------------|-----|------|

| - J    | Timing Furumeter (Clock Cycles)                | Min      | Max | Min          | Max | J    |

| T1     | RxIRA Bit Set after RIC Read                   | 18       | 29  | 18           | 29  | tcy  |

| T2     | RxINT Goes Away after Last Int. Result<br>Read | 16       | 27  | 16           | 27  | tcy  |

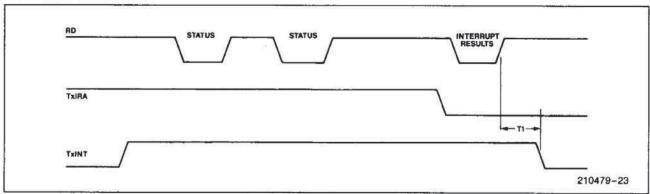

# TRANSMIT INTERRUPT

**Table 4. Transmit Interrupt Result**

| Symbol | Timing (Clock Cycle)                   | Buff            | fered | Non-Bu | uffered | Unit |

|--------|----------------------------------------|-----------------|-------|--------|---------|------|

|        | Timing (Clock Cycle)                   | Min Max Min Max |       |        |         | Oint |

| T1     | TxINT Inactive after Int. Results Read | 13              | 353   | 13     | 454     | tcy  |

# **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature Under Bias0°C to | 70°C |

|--------------------------------------|------|

| Storage Temperature65°C to +15       | 50°C |

| Voltage on Any Pin With              |      |

| Respect to Ground 0.5V to            | + 7V |

| Power Dissipation1                   | Watt |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

# D.C. CHARACTERISTICS 8273 (T<sub>A</sub> = 0°C to 70°C, $V_{CC}$ = $+5.0V \pm 5\%$ )

| Symbol            | Parameter                      | Min    | Max                   | Unit | Test Conditions                                                                                                       |

|-------------------|--------------------------------|--------|-----------------------|------|-----------------------------------------------------------------------------------------------------------------------|

| VIL               | Input Low Voltage              | -0.5   | 0.8                   | ٧    |                                                                                                                       |

| V <sub>IH</sub> , | Input High Voltage             | 2.0    | V <sub>CC</sub> + 0.5 | ٧    |                                                                                                                       |

| V <sub>OL</sub>   | Output Low Voltage             |        | 0.45                  | ٧    | $I_{OL} = 2.0$ mA for Data Bus Pins<br>$I_{OL} = 1.0$ mA for Output Port Pins<br>$I_{OL} = 1.6$ mA for All Other Pins |

| Vон               | Output High Voltage            | 2.4    |                       | . V  | $I_{OH} = -200 \mu A$ for Data Bus Pins $I_{OH} = -100 \mu A$ for All Other Pins                                      |

| I <sub>IL</sub>   | Input Load Current             |        | ±10                   | μΑ   | V <sub>IN</sub> = V <sub>CC</sub> to 0V                                                                               |

| IOFL              | Output Leakage Current         |        | ±10                   | μΑ   | $V_{OUT} = V_{CC}$ to 0.45V                                                                                           |

| lcc               | V <sub>CC</sub> Supply Current | S-196W | 180                   | mA   |                                                                                                                       |

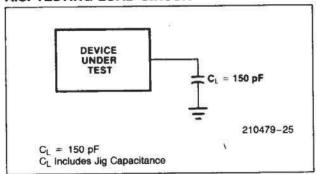

# CAPACITANCE 8273 (TA = 25°C, VCC = GND = 0V)

| Symbol           | Parameter         | Min | Тур | Max | Unit | Test Conditions                    |

|------------------|-------------------|-----|-----|-----|------|------------------------------------|

| CIN              | Input Capacitance |     |     | 10  | pF   | t <sub>c</sub> = 1 MHz             |

| C <sub>I/O</sub> | I/O Capacitance   |     |     | 20  | pF   | Unmeasured Pins<br>Returned to GND |

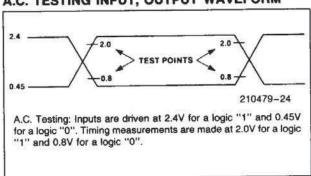

# A.C. CHARACTERISTICS ( $T_A = 0$ °C to 70°C, $V_{CC} = +5.0V \pm 5$ %)

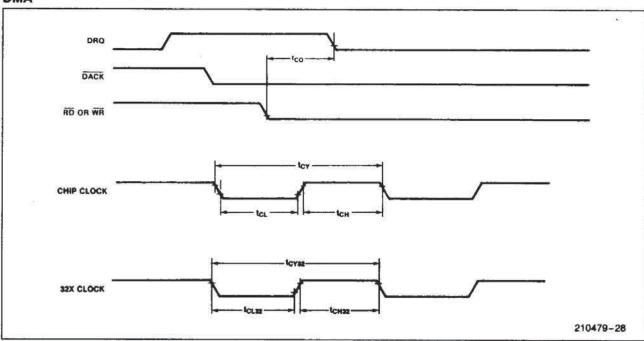

# **CLOCK TIMING (8273)**

| Symbol          | Parameter  | Min | Тур | Max  | Unit | Test Conditions               |

|-----------------|------------|-----|-----|------|------|-------------------------------|

| tcy             | Clock      | 250 |     | 1000 | ns   | 64K Baud Max                  |

| t <sub>CL</sub> | Clock Low  | 120 |     |      | ns   | Operating Rate                |

| t <sub>CH</sub> | Clock High | 120 |     |      | ns   | -07g box -18 May -19 Val Hill |

# A.C. CHARACTERISTICS 8273 (T<sub>A</sub> = 0°C to 70°C, $V_{CC}$ = $\pm 5.0 V \pm 5\%$ )

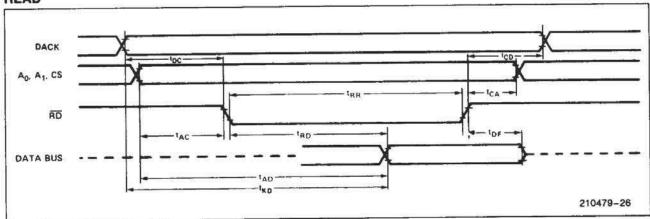

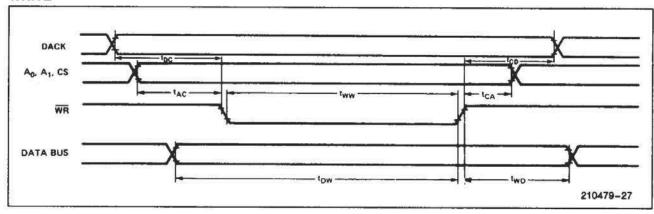

# READ CYCLE

| Symbol          | Parameter               | Min | Max | Unit | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|-------------------------|-----|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|