# 8279, 8279-5

# Programmable Keyboard/Display Interface

The Intel 8279 is a general purpose programmable keyboard and display I/O interface device designed for use with Intel microprocessors. The keyboard portion can provide a scanned interface to a 64-contact key matrix. The keyboard portion will also interface to an array of sensors or a strobed interface keyboard, such as the hall effect and ferrite variety. Key depressions can be 2-key lockout or N-key rollover. Keyboard entries are debounced and strobed in an 8-character FIFO. If more than 8 characters are entered, overrun status is set. Key entries set the interrupt output line to the CPU.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# 8279/8279-5 PROGRAMMABLE KEYBOARD/DISPLAY INTERFACE

- Simultaneous Keyboard Display Operations

- Scanned Keyboard Mode

- Scanned Sensor Mode

- Strobed Input Entry Mode

- 8-Character Keyboard FIFO

- 2-Key Lockout or N-Key Rollover with Contact Debounce

- Dual 8- or 16-Numerical Display

- Single 16-Character Display

- Right or Left Entry 16-Byte Display RAM

- Mode Programmable from CPU

- Programmable Scan Timing

- Interrupt Output on Key Entry

- Available in EXPRESS

- --- Standard Temperature Range

- Extended Temperature Range

The Intel® 8279 is a general purpose programmable keyboard and display I/O interface device designed for use with Intel® microprocessors. The keyboard portion can provide a scanned interface to a 64-contact key matrix. The keyboard portion will also interface to an array of sensors or a strobed interface keyboard, such as the hall effect and ferrite variety. Key depressions can be 2-key lockout or N-key rollover. Keyboard entries are debounced and strobed in an 8-character FIFO. If more than 8 characters are entered, overrun status is set. Key entries set the interrupt output line to the CPU.

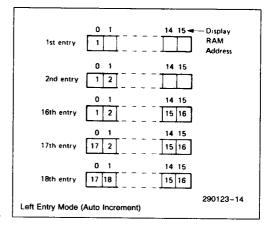

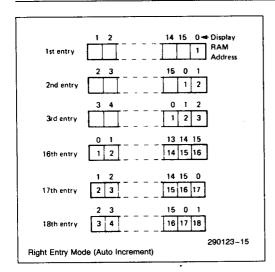

The display portion provides a scanned display interface for LED, incandescent, and other popular display technologies. Both numeric and alphanumeric segment displays may be used as well as simple indicators. The 8279 has 16x8 display RAM which can be organized into dual 16x4. The RAM can be loaded or interrogated by the CPU. Both right entry, calculator and left entry typewriter display formats are possible. Both read and write of the display RAM can be done with auto-increment of the display RAM address.

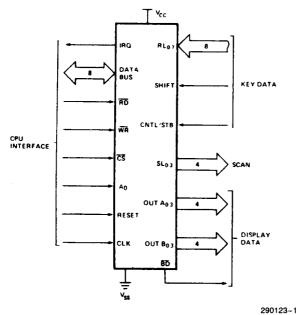

Figure 1. Logic Symbol

Figure 2. Pin Configuration

### HARDWARE DESCRIPTION

The 8279 is packaged in a 40 pin DIP. The following is a functional description of each pin.

**Table 1. Pin Description**

| Symbol                                                                           | Pin<br>No.           | Name and Function                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DB <sub>0</sub> -DB <sub>7</sub>                                                 | 19-12                | <b>BI-DIRECTIONAL DATA BUS:</b> All data and commands between the CPU and the 8279 are transmitted on these lines.                                                                                                                                                                                                                      |

| CLK                                                                              | 3                    | CLOCK: Clock from system used to generate internal timing.                                                                                                                                                                                                                                                                              |

| RESET                                                                            | 9                    | RESET: A high signal on this pin resets the 8279. After being reset the 8279 is placed in the following mode:  1) 16 8-bit character display—left entry.  2) Encoded scan keyboard—2 key lockout.  Along with this the program clock prescaler is set to 31.                                                                            |

| cs                                                                               | 22                   | <b>CHIP SELECT:</b> A low on this pin enables the interface functions to receive or transmit.                                                                                                                                                                                                                                           |

| A <sub>0</sub>                                                                   | 21                   | <b>BUFFER ADDRESS:</b> A high on this line indicates the signals in or out are interpreted as a command or status. A low indicates that they are data.                                                                                                                                                                                  |

| RD, WR                                                                           | 10–11                | <b>INPUT/OUTPUT READ AND WRITE:</b> These signals enable the data buffers to either send data to the external bus or receive it from the external bus.                                                                                                                                                                                  |

| IRQ                                                                              | 4                    | INTERRUPT REQUEST: In a keyboard mode, the interrupt line is high when there is data in the FIFO/Sensor RAM. The interrupt line goes low with each FIFO/Sensor RAM read and returns high if there is still information in the RAM. In a sensor mode, the interrupt line goes high whenever a change in a sensor is detected.            |

| V <sub>SS</sub> , V <sub>CC</sub>                                                | 20, 40               | GROUND AND POWER SUPPLY PINS.                                                                                                                                                                                                                                                                                                           |

| SL <sub>0</sub> -SL <sub>3</sub>                                                 | 32-35                | SCAN LINES: Scan lines which are used to scan the key switch or sensor matrix and the display digits. These lines can be either encoded (1 of 16) or decoded (1 of 4).                                                                                                                                                                  |

| RL <sub>0</sub> -RL <sub>7</sub>                                                 | 38, 39,<br>1, 2, 5–8 | RETURN LINE: Return line inputs which are connected to the scan lines through the keys or sensor switches. They have active internal pullups to keep them high until a switch closure pulls one low. They also serve as an 8-bit input in the Strobed Input mode.                                                                       |

| SHIFT                                                                            | 36                   | SHIFT: The shift input status is stored along with the key position on key closure in the Scanned Keyboard modes. It has an active internal pullup to keep it high until a switch closure pulls it low.                                                                                                                                 |

| CNTL/STB                                                                         | 37                   | CONTROL/STROBED INPUT MODE: For keyboard modes this line is used as a control input and stored like status on a key closure. The line is also the strobe line that enters the data into the FIFO in the Strobed Input mode. (Rising Edge). It has an active internal pullup to keep it high until a switch closure pulls it low.        |

| OUT A <sub>0</sub> -OUT A <sub>3</sub><br>OUT B <sub>0</sub> -OUT B <sub>3</sub> | 27-24<br>31-28       | <b>OUTPUTS:</b> These two ports are the outputs for the 16 x 4 display refresh registers. The data from these outputs is synchronized to the scan lines (SL <sub>0</sub> -SL <sub>3</sub> ) for multiplexed digit displays. The two 4 bit ports may be blanked independently. These two ports may also be considered as one 8-bit port. |

| BD                                                                               | 23                   | <b>BLANK DISPLAY:</b> This output is used to blank the display during digit switching or by a display blanking command.                                                                                                                                                                                                                 |

#### **FUNCTIONAL DESCRIPTION**

Since data input and display are an integral part of many microprocessor designs, the system designer needs an interface that can control these functions without placing a large load on the CPU. The 8279 provides this function for 8-bit microprocessors.

The 8279 has two sections: keyboard and display. The keyboard section can interface to regular type-writer style keyboards or random toggle or thumb switches. The display section drives alphanumeric displays or a bank of indicator lights. Thus the CPU is relieved from scanning the keyboard or refreshing the display.

The 8279 is designed to directly connect to the microprocessor bus. The CPU can program all operating modes for the 8279. These modes include:

### **Input Modes**

- Scanned Keyboard—with encoded (8 x 8 key keyboard) or decoded (4 x 8 key keyboard) scan lines. A key depression generates a 6-bit encoding of key position. Position and shift and control status are stored in the FIFO. Keys are automatically debounced with 2-key lockout or N-key rollover.

- Scanned Sensor Matrix—with encoded (8 x 8 matrix switches) or decoded (4 x 8 matrix switches) scan lines. Key status (open or closed) stored in RAM addressable by CPU.

- Strobed Input—Data on return lines during control line strobe is transferred to FIFO.

#### **Output Modes**

- 8 or 16 character multiplexed displays that can be organized as dual 4-bit or single 8-bit (B<sub>0</sub> = D<sub>0</sub>, A<sub>3</sub> = D<sub>7</sub>).

- · Right entry or left entry display formats.

Other features of the 8279 include:

- Mode programming from the CPU.

- Clock Prescaler

- Interrupt output to signal CPU when there is keyboard or sensor data available.

- An 8 byte FIFO to store keyboard information.

- 16 byte internal Display RAM for display refresh.

This RAM can also be read by the CPU.

#### PRINCIPLES OF OPERATION

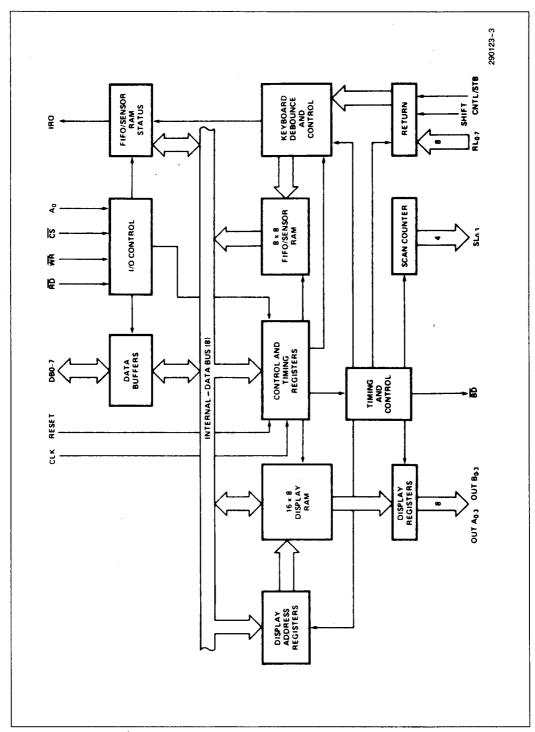

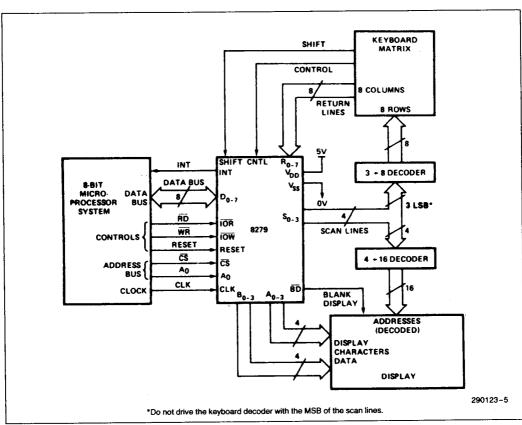

The following is a description of the major elements of the 8279 Programmable Keyboard/Display interface device. Refer to the block diagram in Figure 3.

#### I/0 Control and Data Buffers

The I/O control section uses the  $\overline{CS}$ ,  $A_0$ ,  $\overline{RD}$  and  $\overline{WR}$  lines to control data flow to and from the various internal registers and buffers. All data flow to and from the 8279 is enabled by  $\overline{CS}$ . The character of the information, given or desired by the CPU, is identified by  $A_0$ . A logic one means the information is a command or status. A logic zero means the information is data.  $\overline{RD}$  and  $\overline{WR}$  determine the direction of data flow through the Data Buffers. The Data Buffers are bi-directional buffers that connect the internal bus to the external bus. When the chip is not selected  $\overline{CS} = 1$ ), the devices are in a high impedance state. The drivers input during  $\overline{RD} \bullet \overline{CS}$ .

# Control and Timing Registers and Timing Control

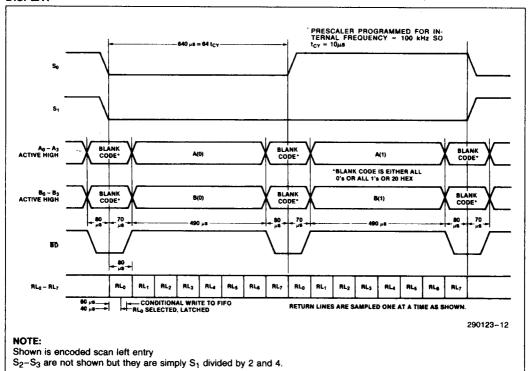

These registers store the keyboard and display modes and other operating conditions programmed by the CPU. The modes are programmed by presenting the proper command on the data lines with  $A_0=1$  and then sending a  $\overline{WR}.$  The command is latched on the rising edge of  $\overline{WR}.$  The command is then decoded and the appropriate function is set. The timing control contains the basic timing counter chain. The first counter is a  $\div$  N prescaler that can be programmed to yield an internal frequency of 100 kHz which gives a 5.1 ms keyboard scan time and a 10.3 ms debounce time. The other counters divide down the basic internal frequency to provide the proper key scan, row scan, keyboard matrix scan, and display scan times.

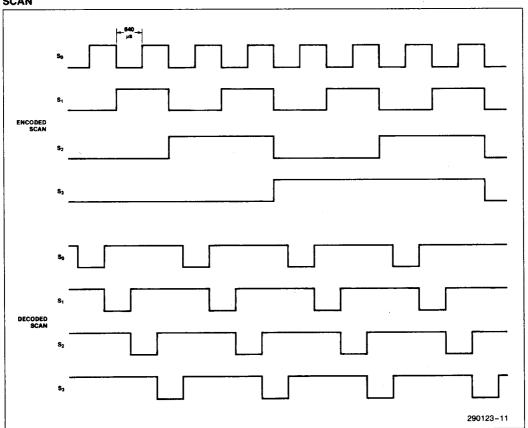

#### Scan Counter

The scan counter has two modes. In the encoded mode, the counter provides a binary count that must be externally decoded to provide the scan lines for the keyboard and display. In the decoded mode, the scan counter decodes the least significant 2 bits and provides a decoded 1 of 4 scan. Note that when the keyboard is in decoded scan, so is the display. This means that only the first 4 characters in the Display RAM are displayed.

In the encoded mode, the scan lines are active high outputs. In the decoded mode, the scan lines are active low outputs.

Figure 3. Internal Block Diagram

# Return Buffers and Keyboard Debounce and Control

The 8 return lines are buffered and latched by the Return Buffers. In the keyboard mode, these lines are scanned, looking for key closures in that row. If the debounce circuit detects a closed switch, it waits about 10 ms to check if the switch remains closed. If it does, the address of the switch in the matrix plus the status of SHIFT and CONTROL are transferred to the FIFO. In the scanned Sensor Matrix modes, the contents of the return lines is directly transferred to the corresponding row of the Sensor RAM (FIFO) each key scan time. In Strobed Input mode, the contents of the return lines are transferred to the FIFO on the rising edge of the CNTL/STB line pulse.

#### FIFO/Sensor RAM and Status

This block is a dual function 8 x 8 RAM. In Keyboard or Strobed Input modes, it is a FIFO. Each new entry is written into successive RAM positions and each is then read in order of entry. FIFO status keeps track of the number of characters in the FIFO and whether it is full or empty. Too many reads or writes will be recognized as an error. The status can be read by an  $\overline{\text{RD}}$  with  $\overline{\text{CS}}$  low and  $A_0$  high. The status logic also provides an IRQ signal when the FIFO is not empty. In Scanned Sensor Matrix mode, the memory is a Sensor RAM. Each row of the Sensor RAM is loaded with the status of the corresponding row of sensor in the sensor matrix. In this mode, IRQ is high if a change in a sensor is detected.

# Display Address Registers and Display RAM

The Display Address Registers hold the address of the word currently being written or read by the CPU and the two 4-bit nibbles being displayed. The read/write addresses are programmed by CPU command. They also can be set to auto increment after each read or write. The Display RAM can be directly read by the CPU after the correct mode and address is set. The addresses for the A and B nibbles are automatically updated by the 8279 to match data entry by the CPU. The A and B nibbles can be entered independently or as one word, according to the mode that is set by the CPU. Data entry to the display can be set to either left or right entry. See Interface Considerations for details.

#### SOFTWARE OPERATION

#### 8279 Commands

The following commands program the 8279 operating modes. The commands are sent on the Data Bus with  $\overline{CS}$  low and  $A_0$  high and are loaded to the 8279 on the rising edge of  $\overline{WR}$ .

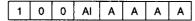

### **Keyboard/Display Mode Set**

|       | MSB |   |   |   |   |   |   | LSB |

|-------|-----|---|---|---|---|---|---|-----|

| Code: | 0   | 0 | 0 | D | D | κ | κ | Κ   |

Where DD is the Display Mode and KKK is the Keyboard Mode.

#### DD

- 0 0 8 8-bit character display-Left entry

- 0 1 16 8-bit character display-Left entry\*

- 1 0 8 8-bit character display---Right entry

- 1 1 16 8-bit character display-Right entry

For description of right and left entry, see Interface Considerations. Note that when decoded scan is set in keyboard mode, the display is reduced to 4 characters independent of display mode set.

#### KKK

- 0 0 Encoded Scan Keyboard—2 Key Lockout\*

- 0 0 1 Decoded Scan Keyboard—2-Key Lockout

- 0 1 0 Encoded Scan Keyboard—N-Key Rollover

- 1 1 Decoded Scan Keyboard—N-Key Rollover

- 1 0 0 Encoded Scan Sensor Matrix

- 0 1 Decoded Scan Sensor Matrix

- 1 1 0 Strobed Input, Encoded Display Scan

- 1 1 Strobed Input, Decoded Display Scan \*Default after reset.

#### **Program Clock**

Code: 0 0 1 P P P P P

All timing and multiplexing signals for the 8279 are generated by an internal prescaler. This prescaler divides the external clock (pin 3) by a programmable integer. Bits PPPPP determine the value of this integer which ranges from 2 to 31. Choosing a divisor that yields 100 kHz will give the specified scan and

Code:

debounce times. For instance, if Pin 3 of the 8279 is being clocked by a 2 MHz signal, PPPPP should be set to 10100 to divide the clock by 20 to yield the proper 100 kHz operating frequency.

#### Read FIFO/Sensor RAM

Code: 0 1 0 Al X A A A

X = Don't Care

The CPU sets the 8279 for a read of the FIFO/Sensor RAM by first writing this command. In the Scan Keyboard Mode, the Auto-Increment flag (AI) and the RAM address bits (AAA) are irrelevant. The 8279 will automatically drive the data bus for each subsequent read ( $A_0=0$ ) in the same sequence in which the data first entered the FIFO. All subsequent reads will be from the FIFO until another command is issued.

In the Sensor Matrix Mode, the RAM address bits AAA select one of the 8 rows of the Sensor RAM. If the AI flag is set (AI = 1), each successive read will be from the subsequent row of the sensor RAM.

#### Read Display RAM

Code:

0 1 1 AI A A A A

The CPU sets up the 8279 for a read of the Display RAM by first writing this command. The address bits AAAA select one of the 16 rows of the Display RAM. If the AI flag is set (A1 = 1), this row address will be incremented after each following read *or write* to the Display RAM. Since the same counter is used for both reading and writing, this command sets the next read or *write* address and the sense of the Auto-Increment mode for both operations.

#### Write Display RAM

Code:

The CPU sets up the 8279 for a write to the Display RAM by first writing this command. After writing the command with  $A_0=1$ , all subsequent writes with  $A_0=0$  will be to the Display RAM. The addressing and Auto-Increment functions are identical to those for the Read Display RAM. However, this command does not affect the source of subsequent Data Reads; the CPU will read from whichever RAM (Display of FIFO/Sensor) which was last specified. If, indeed, the Display RAM was last specified, the Write Display RAM will, nevertheless, change the next Read location.

#### Display Write Inhibit/Blanking

A B A

1 0 1 X W W BL

В

BL

The IW Bits can be used to mask nibble A and nibble B in applications requiring separate 4-bit display ports. By setting the IW flag (IW = 1) for one of the ports, the port becomes marked so that entries to the Display RAM from the CPU do not affect that port. Thus, if each nibble is input to a BCD decoder, the CPU may write a digit to the Display RAM without affecting the other digit being displayed. It is important to note that bit  $B_0$  corresponds to bit  $D_0$  on the CPU bus, and that bit  $A_3$  corresponds to bit  $D_7$ .

If the user wishes to blank the display, the BL flags are available for each nibble. The last Clear command issued determines the code to be used as a "blank." This code defaults to all zeros after a reset. Note that both BL flags must be set to blank a display formatted with a single 8-bit port.

#### Clear

Code:

| 1 | 1 ( | ) C <sub>D</sub> | CD | CD | CF | CA |

|---|-----|------------------|----|----|----|----|

|---|-----|------------------|----|----|----|----|

The  $C_D$  bits are available in this command to clear all rows of the Display RAM to a selectable blanking code as follows:

During the time the Display RAM is being cleared ( $\sim$  160  $\mu$ s), it may not be written to. The most significant bit of the FIFO status word is set during this time. When the Display RAM becomes available again, it automatically resets.

If the  $C_F$  bit is asserted ( $C_F=1$ ), the FIFO status is cleared and the interrupt output line is reset. Also, the Sensor RAM pointer is set to row 0.

$C_A$ , the Clear All bit, has the combined effect of  $C_D$  and  $C_F$ ; it uses the  $C_D$  clearing code on the Display RAM and also clears FIFO status. Furthermore, it resynchronizes the internal timing chain.

### **End Interrupt/Error Mode Set**

Code: 1 1 1 E X X X X X = Don't care

For the sensor matrix modes this command lowers the IRQ line and enables further writing into RAM. (The IRQ line would have been raised upon the detection of a change in a sensor value. This would have also inhibited further writing into the RAM until reset).

For the N-key rollover mode—if the E bit is programmed to "1" the chip will operate in the special Error mode. (For further details, see Interface Considerations Section.)

#### Status Word

The status word contains the FIFO status, error, and display unavailable signals. This word is read by the CPU when  $A_0$  is high and  $\overline{CS}$  and  $\overline{RD}$  are low. See Interface Considerations for more detail on status word.

#### **Data Read**

Data is read when  $A_0$ ,  $\overline{CS}$  and  $\overline{RD}$  are all low. The source of the data is specified by the Read FIFO or Read Display commands. The trailing edge of  $\overline{RD}$  will cause the address of the RAM being read to be incremented if the Auto-Increment flag is set. FIFO reads always increment (if no error occurs) independent of AI.

#### **Data Write**

Data that is written with  $A_0$ ,  $\overline{CS}$  and  $\overline{WR}$  low is always written to the Display RAM. The address is specified by the latest Read Display or Write Display command. Auto-Incrementing on the rising edge of  $\overline{WR}$  occurs if Al is set by the latest display command.

#### INTERFACE CONSIDERATIONS

# Scanned Keyboard Mode, 2-Key Lockout

There are three possible combinations of conditions that can occur during debounce scanning. When a key is depressed, the debounce logic is set. Other depressed keys are looked for during the next two scans. If none are encountered, it is a single key depression and the key position is entered into the

FIFO along with the status of CNTL and SHIFT lines. If the FIFO was empty, IRQ will be set to signal the CPU that there is an entry in the FIFO. If the FIFO was full, the key will not be entered and the error flag will be set. If another closed switch is encountered, no entry to the FIFO can occur. If all other keys are released before ths one, then it will be entered to the FIFO. If this key is released before any other, it will be entirely ignored. A key is entered to the FIFO only once per depression, no matter how many keys were pressed along with it or in what order they were released. If two keys are depressed within the debounce cycle, it is a simultaneous depression. Neither key will be recognized until one key remains depressed alone. The last key will be treated as a single key depression.

# Scanned Keyboard Mode, N-Key Rollover

With N-key Rollover each key depression is treated independently from all others. When a key is depressed, the debounce circuit waits 2 keyboard scans and then checks to see if the key is still down. If it is, the key is entered into the FIFO. Any number of keys can be depressed and another can be recognized and entered into the FIFO. If a simultaneous depression occurs, the keys are recognized and entered according to the order the keyboard scan found them.

#### Scanned Keyboard—Special Error Modes

For N-key rollover mode the user can program a special error mode. This is done by the "End Interrupt/Error Mode Set" command. The debounce cycle and key-validity check are as in normal N-key mode. If during a single debounce cycle, two keys are found depressed, this is considered a simultaneous multiple depression, and sets an error flag. This flag will prevent any further writing into the FIFO and will set interrupt (if not yet set). The error flag could be read in this mode by reading the FIFO STATUS word. (See "FIFO STATUS" for further details.) The error flag is reset by sending the normal CLEAR command with CF = 1.

#### Sensor Matrix Mode

In Sensor Matrix mode, the debounce logic is inhibited. The status of the sensor switch is inputted directly to the Sensor RAM. In this way the Sensor RAM keeps an image of the state of the switches in the sensor matrix. Although debouncing is not provided, this mode has the advantage that the CPU knows how long the sensor was closed and when it

was released. A keyboard mode can only indicate a validated closure. To make the software easier, the designer should functionally group the sensors by row since this is the format in which the CPU will read them.

The IRQ line goes high if any sensor value change is detected at the end of a sensor matrix scan. The IRQ line is cleared by the first data read operation if the Auto-Increment flag is set to zero, or by the End Interrupt command if the Auto-Increment flag is set to one.

#### NOTE:

Multiple changes in the matrix Addressed by  $(SL_0-_3=0)$  may cause multiple interrupts.  $(SL_0=0)$  in the Decoded Mode.) Reset may cause the 8279 to see multiple changes.

#### **Data Format**

In the Scanned Keyboard mode, the character entered into the FIFO corresponds to the position of the switch in the keyboard plus the status of the CNTL and SHIFT lines (non-inverted). CNTL is the MSB of the character and SHIFT is the next most significant bit. The next three bits are from the scan counter and indicate the row the key was found in. The last three bits are from the column counter and indicate to which return line the key was connected.

| MSB  |       |      | LSB    |

|------|-------|------|--------|

| CNTL | SHIFT | SCAN | RETURN |

|      |       |      |        |

SCANNED KEYBOARD DATA FORMAT

In Sensor Matrix mode, the data on the return lines is entered directly in the row of the Sensor RAM that corresponds to the row in the matrix being scanned. Therefore, each switch position maps directly to a Sensor RAM position. The SHIFT and CNTL inputs are ignored in this mode. Note that switches are not necessarily the only thing that can be connected to the return lines in this mode. Any logic that can be triggered by the scan lines can enter data to the return line inputs. Eight multiplexed input ports could be tied to the return lines and scanned by the 8279.

| MSB             |                 |                 |                 |                 |                 |                 | LSB             |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| RL <sub>7</sub> | RL <sub>6</sub> | RL <sub>5</sub> | RL <sub>4</sub> | RL <sub>3</sub> | RL <sub>2</sub> | RL <sub>1</sub> | RL <sub>0</sub> |

In Strobed Input mode, the data is also entered to the FIFO from the return lines. The data is entered by the rising edge of a CNTL/STB line pulse. Data can come from another encoded keyboard or simple switch matrix. The return lines can also be used as a general purpose strobed input.

| MSB             |                 |                 |                 |                 |                 |                 | LSB |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----|

| RL <sub>7</sub> | RL <sub>6</sub> | RL <sub>5</sub> | RL <sub>4</sub> | RL <sub>3</sub> | RL <sub>2</sub> | RL <sub>1</sub> | RLo |

#### Display

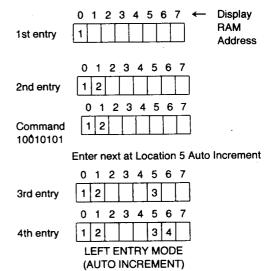

#### **Left Entry**

Left Entry mode is the simplest display format in that each display position directly corresponds to a byte (or nibble) in the Display RAM. Address 0 in the RAM is the left-most display character and address 15 (or address 7 in 8 character display) is the right most display character. Entering characters from position zero causes the display to fill from the left. The 17th (9th) character is entered back in the left most position and filling again proceeds from there.

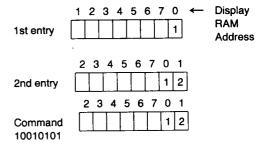

#### **Right Entry**

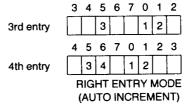

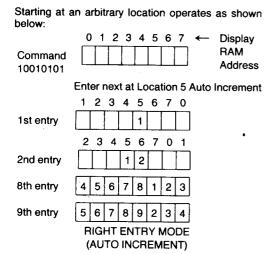

Right entry is the method used by most electronic calculators. The first entry is placed in the right most display character. The next entry is also placed in the right most character after the display is shifted left one character. The left most character is shifted off the end and is lost.

Note that now the display position and register address do not correspond. Consequently, entering a character to an arbitrary position in the Auto Increment mode may have unexpected results. Entry starting at Display RAM address 0 with sequential entry is recommended.

#### **Auto Increment**

In the Left Entry mode, Auto Incrementing causes the address where the CPU will next write to be incremented by one and the character appears in the next location. With non-Auto Incrementing the entry is both to the same RAM address and display position. Entry to an arbitrary address in the Auto Increment mode has no undesirable side effects and the result is predictable:

In the Right Entry mode, Auto Incrementing and non Incrementing have the same effect as in the Left Entry except if the address sequence is interrupted.

Enter next at Location 5 Auto Increment

Entry appears to be from the intial entry point.

#### 8/16 Character Display Formats

If the display mode is set to an 8 character display, the on duty-cycle is double what it would be for a 16 character display (e.g., 5.1 ms scan time for 8 characters vs. 10.3 ms for 16 characters with 100 kHz internal frequency).

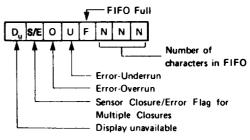

#### G. FIFO Status

FIFO status is used in the Keyboard and Strobed Input modes to indicate the number of characters in the FIFO and to indicate whether an error has occurred. There are two types of errors possible: overrun and underrun. Overrun occurs when the entry of another character into a full FIFO is attempted. Underrun occurs when the CPU tries to read an empty FIFO.

The FIFO status word also has a bit to indicate that the Display RAM was unavailable because a Clear Display or Clear All command had not completed its clearing operation.

In a Sensor Matrix mode, a bit is set in the FIFO status word to indicate that at least one sensor closure indication is contained in the Sensor RAM.

In Special Error Mode the S/E bit is showing the error flag and serves as an indication to whether a simultaneous multiple closure error has occurred.

#### **FIFO STATUS WORD**

290123-4

Figure 4. System Block Diagram

#### **ABSOLUTE MAXIMUM RATINGS\***

| Ambient Temperature     | .0°C to 70°C   |

|-------------------------|----------------|

| Storage Temperature6    | 5°C to 125°C   |

| Voltage on any Pin with |                |

| Respect to Ground       | 0.5V  to  + 7V |

| Power Dissination       | 1 \M/a++       |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

## **D.C. CHARACTERISTICS** $T_A = 0^{\circ}C \text{ to } 70^{\circ}C \text{ V}_{SS} = 0 \text{ (Note 3)}^{\star}$

| Symbol           | Parameter                                        | Min  | Max           | Unit     | Test Conditions                                      |

|------------------|--------------------------------------------------|------|---------------|----------|------------------------------------------------------|

| V <sub>IL1</sub> | Input Low Voltage for Return Lines               | -0.5 | 1.4           | ٧        |                                                      |

| V <sub>IL2</sub> | Input Low Voltage for All Others                 | -0.5 | 0.8           | V        |                                                      |

| V <sub>IH1</sub> | Input High Voltage for Return Lines              | 2.2  |               | V        |                                                      |

| V <sub>IH2</sub> | Input High Voltage for All Others                | 2.0  |               | V        |                                                      |

| V <sub>OL</sub>  | Output Low Voltage                               |      | 0.45          | V        | (Note 1)                                             |

| V <sub>OH1</sub> | Output High Voltage on Interrupt Line            | 3.5  |               | V        | (Note 2)                                             |

| V <sub>OH2</sub> | Other Outputs                                    | 2.4  |               |          | $I_{OH} = {-400 \mu A 8279-5} \atop -100 \mu A 8279$ |

| I <sub>IL1</sub> | Input Current on Shift, Control and Return Lines |      | + 10<br>- 100 | μA<br>μA | $V_{IN} = V_{CC}$<br>$V_{IN} = 0V$                   |

| I <sub>IL2</sub> | Input Leakage Current on All Others              |      | ±10           | μΑ       | V <sub>IN</sub> = V <sub>CC</sub> to 0V              |

| lofL             | Output Float Leakage                             |      | ±10           | μΑ       | $V_{OUT} = V_{CC}$ to 0.45V                          |

| lcc              | Power Supply Current                             |      | 120           | mA       |                                                      |

| C <sub>IN</sub>  | Input Capacitance                                |      | 10            | pF       | f <sub>C</sub> = 1 MHz Unmeasured                    |

| C <sub>OUT</sub> | Output Capacitance                               |      | 20            | pF       | Pins Returned to V <sub>SS</sub> <sup>(6)</sup>      |

## A.C. CHARACTERISTICS $T_A = 0$ °C to 70°C, $V_{SS} = 0$ V (Note 3)\*

#### **Bus Parameters**

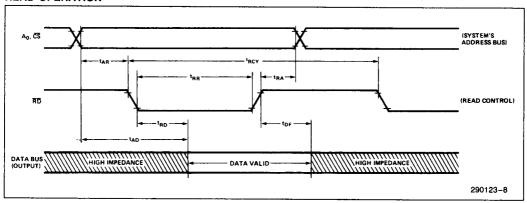

#### **READ CYCLE**

| Cumbal              | Parameter                   | 8279 |     | 8279-5 |     |      |

|---------------------|-----------------------------|------|-----|--------|-----|------|

| Symbol              | Parameter                   | Min  | Max | Min    | Max | Unit |

| t <sub>AR</sub>     | Address Stable Before READ  | 50   |     | 0      |     | ns   |

| t <sub>RA</sub>     | Address Hold Time for READ  | 5    |     | 0      |     | ns   |

| t <sub>RR</sub>     | READ Pulse Width            | 420  |     | 250    |     | ns   |

| t <sub>RD</sub> (4) | Data Delay from READ        |      | 300 |        | 150 | ns   |

| t <sub>AD</sub> (4) | Address to Data Valid       |      | 450 |        | 250 | ns   |

| t <sub>DF</sub>     | READ to Data Floating       | 10   | 100 | 10     | 100 | ns   |

| t <sub>RCY</sub>    | Read Cycle Time             | 1    |     | 1      |     | μς   |

| t <sub>AW</sub>     | Address Stable Before WRITE | 50   |     | 0      |     | ns   |

| twA                 | Address Hold Time for WRITE | 20   |     | 0      |     | ns   |

#### A.C. CHARACTERISTICS (Continued)

#### WRITE CYCLE

|                 |                            | 82  | 279 | 827 | 11-14 |      |

|-----------------|----------------------------|-----|-----|-----|-------|------|

| Symbol          | Parameter                  | Min | Max | Min | Max   | Unit |

| tww             | WRITE Pulse Width          | 400 |     | 250 |       | ns   |

| t <sub>DW</sub> | Data Set Up Time for WRITE | 300 |     | 150 |       | ns   |

| t <sub>WD</sub> | Data Hold Time for WRITE   | 40  |     | 0   |       | ns   |

| twcy            | Write Cycle Time           | 1   |     | 1   |       | μs   |

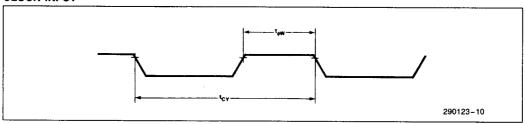

#### **OTHER TIMINGS**

|                 |                   | 8279 |     | 827 | Unit |      |

|-----------------|-------------------|------|-----|-----|------|------|

| Symbol          | Parameter         | Min  | Max | Min | Max  | Unit |

| t <sub>ΦW</sub> | Clock Pulse Width | 230  |     | 120 |      | ns   |

| t <sub>CY</sub> | Clock Period      | 500  |     | 320 |      | ns   |

| Keyboard Scan Time     | 5.1 ms  |

|------------------------|---------|

| Keyboard Debounce Time | 10.3 ms |

| Key Scan Time          | 80 μs   |

| Display Scan Time      | 10.3 ms |

Blanking Time ......160 μs Internal Clock Cycle<sup>(5)</sup> .....10 μs

#### NOTES:

- 1. 8279,  $I_{OL} = 1.6$  mA; 8279-5,  $I_{OL} = 2.2$  mA.

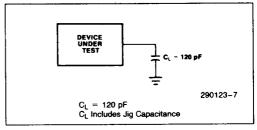

- 3. 8279,  $V_{CC} = +5V \pm 5\%$ ; 8279-5,  $V_{CC} = +5V \pm 10\%$ 4. 8279,  $V_{CC} = 100$  pF; 8279-5,  $V_{CC} = 150$  pF.

- 5. The Prescaler should be programmed to provide a 10  $\mu s$  internal clock cycle.

- 6. Sampled not 100% tested. TA = 25°C.

- \* For Extended Temperature EXPRESS, use M8279A electrical parameters.

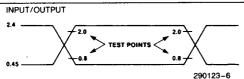

#### A.C. TESTING INPUT, OUTPUT WAVEFORM

A.C. Testing: Inputs are driven at 2.4V for a Logic "1" and 0.45V for a Logic "0". Timing measurements are made at 2.0V for a Logic "1" and 0.8V for a Logic "0".

#### A.C. TESTING LOAD CIRCUIT

### **WAVEFORMS**

#### **READ OPERATION**

#### WRITE OPERATION

#### **CLOCK INPUT**

### WAVEFORMS (Continued)

### **WAVEFORMS** (Continued)

#### **DISPLAY**