# **AM2903A**

# Four-Bit Bipolar Microprocessor Slice

The AM2903A is a four-bit expandable bipolar microprocessor slice. The AM2903A performs all functions performed by the industry standard AM2901 and, in addition, provides a number of significant enhancements that are especially useful in arithmetic-oriented processors. Infinitely expandable memory and three-port, three-address architecture are provided by the AM2903A. In addition to its complete arithmetic and logic instruction set, the AM2903A provides a special set of instructions which facilitate the implementation of multiplication, division, normalization, and other previously time-consuming operations. The AM2903A is identical to the AM2903 but up to 30% faster.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# Am2903A

Four-Bit Bipolar Microprocessor Slice

## DISTINCTIVE CHARACTERISTICS

#### Expandable Register File --

The Am2903A includes the necessary "hooks" to expand the register file externally to any number of registers.

- Built-in Parity Generation and Sign Extension Circuitry Can supply parity across the entire ALU output and

provide sign extension at any slice boundary.

- Built-in Division Logic –

Executes non-restoring, multiple-length division with correction of the quotient.

#### Built-in Normalization Logic -

The mantissa and exponent of a floating-point number can be developed using a single microcycle per shift. Status flags indicate when the operation is complete.

Built-in Multiplication and Division Logic –

Performs unsigned multiplication, two's complement

multiplication and the last cycle of a two's complement multiplication.

## GENERAL DESCRIPTION

The Am2903A is a four-bit expandable bipolar microprocessor slice. The Am2903A performs all functions performed by the industry standard Am2901 and, in addition, provides a number of significant enhancements that are especially useful in arithmetic-oriented processors. Infinitely expandable memory and three-port, three-address architecture are

provided by the Am2903A. In addition to its complete arithmetic and logic instruction set, the Am2903A provides a special set of instructions which facilitate the implementation of multiplication, division, normalization, and other previously time-consuming operations. The Am2903A is identical to the Am2903 but up to 30% faster.

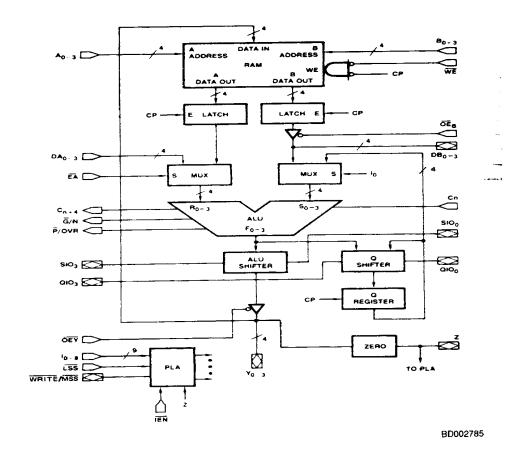

#### **BLOCK DIAGRAM**

Publication # Rev. Amendment 03579 D /0 Issue Date: August 1986

#### **RELATED PRODUCTS**

| Part No. | Description                            |

|----------|----------------------------------------|

| Am2902A  | Carry Look-Ahead Generator             |

| Am2904   | Status and Shift Control Unit          |

| Am2910A  | Microprogram Controller                |

| Am2914   | Vectored Priority Interrupt Controller |

| Am2918   | Pipeline Register                      |

| Am2920   | Octal Register                         |

| Am2922   | Condition Code MUX                     |

| Am2925   | System Clock Generator                 |

| Am2940   | DMA Address Generator                  |

| Am2952   | Bidirectional I/O Port                 |

| Am29705A | Two-Port RAM                           |

| Am27S35  | Registered PROM                        |

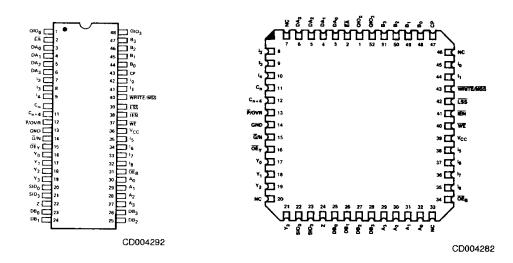

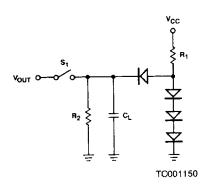

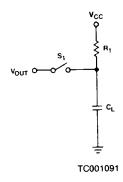

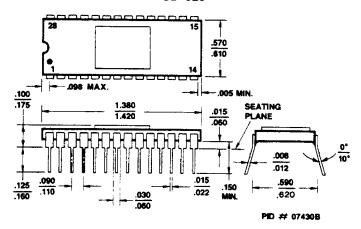

## **CONNECTION DIAGRAMS\***

## **Top View**

Note: Pin 1 is marked for orientation.

\*This device is also available in a 48-Pin Flatpack (CFT048). Pinouts are the same as the DIP.

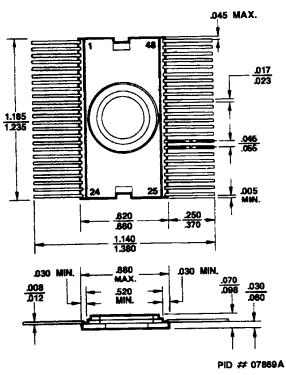

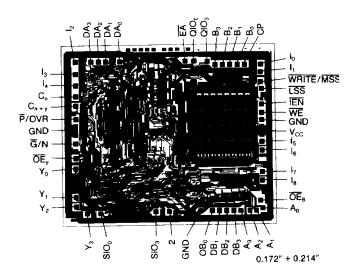

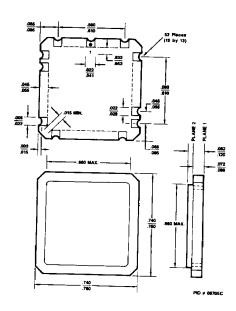

## METALLIZATION AND PAD LAYOUT

DIE SIZE 0.172" x 0.218"

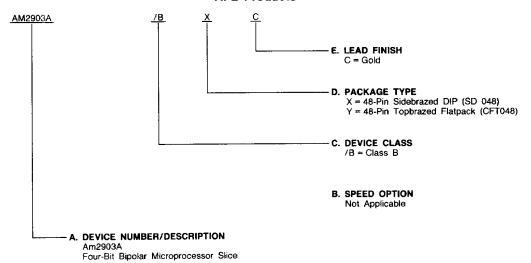

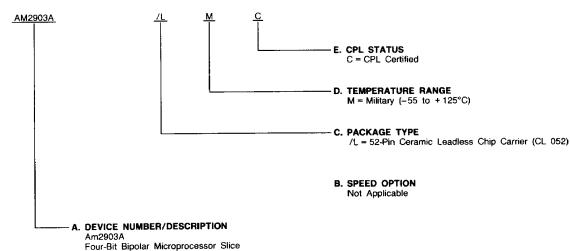

# ORDERING INFORMATION APL and CPL Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. CPL (Controlled Products List) products are processed in accordance with MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) is formed by a combination of:

APL Products: A. Device Number

B. Speed Option (if applicable)

C. Device Class

D. Package Type

E. Lead Finish

CPL Products: A. Device Number

B. Speed Option (if applicable)

C. Package Type

D. Temperature Range

E. CPL Status

#### **CPL Products**

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

|     | Valid Combi | nations    |

|-----|-------------|------------|

| APL | AM2903A     | /BXC, /BYC |

| CPL | AM2903A     | /LMC       |

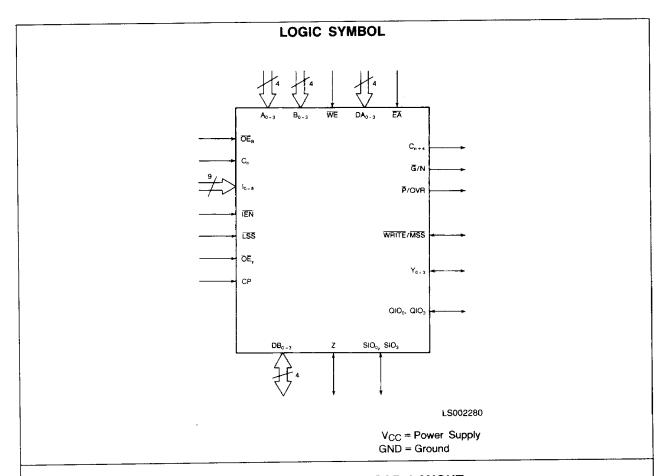

#### PIN DESCRIPTION

#### A<sub>0-3</sub> RAM A Address Inputs (TTL Input)

Four RAM address inputs that contain the address of the RAM word appearing at the RAM A output port.

#### Bo = 3 RAM B Address Inputs (TTL Input)

Four RAM address inputs that contain the address of the RAM word appearing at the RAM B output port and into which new data is written when the  $\overline{\text{WE}}$  input and the CP input are LOW.

#### WE Write Enable Input (TTL Input)

The RAM write enable input. If WE is LOW, data at the Y I/O port is written into the RAM when the CP input is LOW. When WE is HIGH, writing data into the RAM is inhibited.

#### DA<sub>0-3</sub> External Data Inputs (TTL Input)

A four-bit external data input that can be selected as one of the Am2903A ALU operand sources; DA<sub>0</sub> is the least significant bit.

#### EA Control Input (TTL Input)

A control input that, when HIGH, selects  ${\sf DA}_{0-3}$  as the ALU R operand, and, when LOW, selects RAM output A as the ALU R operand.

# DB<sub>0-3</sub> External Data Inputs/Outputs (Three-State Input/Output)

A four-bit external data input/output. Under control of the  $\overline{\text{OE}_B}$  input, RAM output port B can be directly read on these lines, or input data on these lines can be selected as the ALU S operand.

#### OE<sub>B</sub> Control input (TTL input)

$\bar{\text{A}}$  control input that, when LOW, enables RAM output B onto the DB $_{0.3}$  lines and, when HIGH, disables the RAM output B three-state buffers.

#### Cn Carry-in Input (TTL Input)

The carry-in input to the Am2903A ALU.

#### I<sub>0-8</sub> Instruction Inputs (TTL Input)

The nine instruction inputs used to select the Am2903A operation to be performed.

#### IEN Instruction Enable Input (TTL Input)

The instruction enable input that, when LOW, allows the Q Register and the Sign Compare flip-flop to be written. When IEN is HIGH, the Q Register and Sign Compare flip-flop are in the hold mode. On the Am2903A, IEN also controls WRITE.

## Cn+4 Carry-Out Output (TTL Output)

This output generally indicates the carry-out of the Am2903A ALU. Refer to Table 5 for an exact definition of this pin.

#### G/N Carry-Generate Output (TTL Output)

A multi-purpose pin that indicates the carry generate,  $\overline{G}$ , function at the least significant and intermediate slices, and generally indicates the sign, N, of the ALU result at the most significant slice. Refer to Table 5 for an exact definition of this pin.

#### P/OVR Carry-Propagate Output (TTL Output)

A multi-purpose pin that indicates the carry propagate,  $\overline{P}$ , function at the least significant and intermediate slices, and indicates the conventional two's complement overflow, OVR, signal at the most significant slice. Refer to Table 5 for an exact definition of this pin.

# Z Open-Collector I/O Pin (Open-Collector Input/Output)

An open-collector input/output pin that, when HIGH, generally indicates the outputs are all LOW. For some Special Functions, Z is used as an input pin. Refer to Table 5 for an exact definition of this pin.

# SIO<sub>0</sub>, SIO<sub>3</sub> Bidirectional Serial Shift I/Os for the ALU (Three-State Input/Output)

Bidirectional serial shift inputs/outputs for the ALU shifter. During a shift-up operation,  $SIO_0$  is an input and  $SIO_3$  an output. During a shift-down operation,  $SIO_3$  is an input and  $SIO_0$  is an output. Refer to Tables 3 and 4 for an exact definition of these pins.

# QIO<sub>0</sub>, QIO<sub>3</sub> Bidirectional Serial Shiff I/O s for the Q Shifter (Three-State Input/Output)

Bidirectional serial shift inputs/outputs for the Q shifter that operate like  $SIO_0$  and  $SIO_3$ . Refer to Tables 3 and 4 for an exact definition of these pins.

#### LSS Control Input (TTL Input)

An input pin that, when tied LOW, programs the chip to act as the least significant slice (LSS) of an Am2903A array and enables the WRITE output onto the WRITE/MSS pin. When LSS is tied HIGH, the chip is programmed to operate as either an intermediate or most significant slice and the WRITE output buffer is disabled.

#### WRITE/MSS Control Input (Three-State Input/Output)

When LSS is tied LOW, the WRITE output signal appears at this pin; the WRITE signal is LOW when an instruction that writes data into the RAM is being executed. When LSS is tied HIGH, WRITE/MSS is an input pin; tying it HIGH programs the chip to operate as an intermediate slice (IS) and tying it LOW programs the chip to operate as the most significant slice (MSS).

# Y<sub>0-3</sub> Data Inputs/Outputs (Three-State Input/Output)

Four data inputs/outputs of the Am2903A. Under control of the  $\overline{\text{OE}_{Y}}$  input, the ALU shifter output data can be enabled onto these lines, or these lines can be used as data inputs when external data is written directly into the RAM.

#### OEY Control Input (TTL Input)

A control input that, when LOW, enables the ALU shifter output data onto the  $Y_{0-3}$  lines and, when HIGH, disables the  $Y_{0-3}$  three-state output buffers.

#### CP Clock Input (TTL Input)

The clock input to the Am2903A. The Q Register and Sign Compare flip-flop are clocked on the LOW-to-HIGH transition of the CP signal. When enabled by  $\overline{\text{WE}}$ , data is written in the RAM when CP is LOW.

#### **FUNCTIONAL DESCRIPTION**

#### Architecture of the Am2903A

The Am2903A is a high-performance, cascadable, four-bit bipolar microprocessor slice designed for use in CPU's, peripheral controllers, microprogrammable machines, and numerous other applications. The microinstruction flexibility of the Am2903A allows the efficient emulation of almost any digital computing machine. The nine-bit microinstruction selects the ALU sources, function and destination. The Am2903A is cascadable with full lookahead or ripple carry, has three-state outputs, and provides various ALU status flag outputs. Advanced IMOX<sup>TM</sup> processing is used to fabricate this 48-pin LSI circuit.

All data paths within the device are four bits wide. As shown in the block diagram, the device consists of a 16-word by 4-bit, two-port RAM with latches on both output ports, a high-performance ALU and shifter, a multi-purpose Q Register with shifter input, and a nine-bit instruction decoder.

#### Two-Port RAM

Any two RAM words addressed at the A and B address ports can be read simultaneously at the respective RAM A and B output ports. Identical data appear at the two output ports when the same address is applied to both address ports. The latches at the RAM output ports are transparent when the clock input, CP, is HIGH and they hold the RAM output data when CP is LOW. Under control of the  $\overline{\text{OE}_B}$  three-state output enable, RAM data can be read directly at the Am2903A DB (I/O) port.

External data at the Am2903A Y I/O port can be written directly into the RAM, or ALU shifter output data can be enabled onto the Y I/O port and entered into the RAM. Data is written into the RAM at the B address when the write enable input,  $\overline{WE}$ , is LOW and the clock input, CP, is LOW.

#### Arithmetic Logic Unit

The Am2903A high-performance ALU can perform seven arithmetic and nine logic operations on two 4-bit operands. Multiplexers at the ALU inputs provide the capability to select various pairs of ALU source operands. The  $\overline{E_A}$  input selects either the DA external data input or RAM output port A for use as one ALU operand and the  $\overline{OE_B}$  and  $I_0$  inputs select RAM output port B, DB external data input, or the Q Register content for use as the second ALU operand. Also, during some ALU operations, zeroes are forced at the ALU operand inputs. Thus, the Am2903A ALU can operate on data from two external sources, from an internal and external source, or from two internal sources. Table I shows all possible pairs of ALU source operands as a function of the  $\overline{E_A}$ ,  $\overline{OE_B}$ , and  $I_0$  inputs.

When instruction bits  $I_4$ ,  $I_3$ ,  $I_2$ ,  $I_1$ , and  $I_0$  are LOW, the Am2903A executes special functions. Table 4 defines these special functions and the operation which the ALU performs for each. When the Am2903A executes instructions other than the nine special functions, the ALU operation is determined by instruction bits  $I_4$ ,  $I_3$ ,  $I_2$ , and  $I_1$ . Table 2 defines the ALU operation as a function of these four instruction bits.

TABLE 1. ALU OPERAND SOURCES

| EA | l <sub>0</sub> | OE <sub>B</sub> | ALU Operand R     | ALU Operand S     |

|----|----------------|-----------------|-------------------|-------------------|

| L  | L              | L               | RAM Output A      | RAM Output B      |

| L  | L              | н               | RAM Output A      | DB <sub>0-3</sub> |

| L  | н              | х               | RAM Output A      | Q Register        |

| Н  | L              | L               | DA <sub>0-3</sub> | RAM Output B      |

| Н  | L              | н               | DA <sub>0-3</sub> | DB <sub>0-3</sub> |

| Н  | Н              | Х               | DA <sub>0-3</sub> | Q Register        |

L = LOW

H = HIGH

X = Don't Care

TABLE 2. Am2903A ALU FUNCTIONS

| 14 | lз | l <sub>2</sub> | l <sub>1</sub> | Hex<br>Code | Α                                | LU FUNCTIONS                                        |  |  |  |  |

|----|----|----------------|----------------|-------------|----------------------------------|-----------------------------------------------------|--|--|--|--|

| Γ. |    | L              | L              | 0           | 1 <sub>0</sub> = L               | Special Functions                                   |  |  |  |  |

| L  | L  | L              | -              | . 0         | 1 <sub>0</sub> = H               | F <sub>i</sub> = HIGH                               |  |  |  |  |

| L  | L  | L              | Ξ              | 1           | F = S                            | Minus R Minus 1 plus<br>C <sub>n</sub>              |  |  |  |  |

| L  | L  | Н              | ∟              | 2           | F=R                              | Minus S Minus 1 Plus<br>C <sub>n</sub>              |  |  |  |  |

| L  | L  | Η              | I              | 3           | F = R Plus S Plus C <sub>n</sub> |                                                     |  |  |  |  |

| L  | Н  | L              | L              | 4           |                                  | F = S Plus C <sub>n</sub>                           |  |  |  |  |

| L  | Н  | L              | Н              | 5           | $F = \overline{S}$ Plus $C_n$    |                                                     |  |  |  |  |

| L  | Н  | Н              | L              | 6           |                                  | F = R Plus C <sub>n</sub>                           |  |  |  |  |

| L  | Н  | Н              | Н              | 7           |                                  | $F = \overline{R}$ Plus $C_n$                       |  |  |  |  |

| Н  | L  | L              | L              | 8           |                                  | F <sub>i</sub> = LOW                                |  |  |  |  |

| Н  | L  | L              | Н              | 9           |                                  | $F_i = \overline{R}_i$ AND $S_i$                    |  |  |  |  |

| Н  | L  | Н              | L              | Α           | F <sub>i</sub> = R               | ; EXCLUSIVE NOR S;                                  |  |  |  |  |

| Н  | L  | Н              | Н              | В           | F <sub>1</sub> = F               | R <sub>i</sub> EXCLUSIVE OR S <sub>i</sub>          |  |  |  |  |

| Н  | Н  | L              | L              | С           |                                  | F <sub>i</sub> = R <sub>i</sub> AND S <sub>i</sub>  |  |  |  |  |

| Н  | Н  | L              | Н              | D           |                                  | Fi = Ri NOR Si                                      |  |  |  |  |

| Н  | Н  | Н              | L              | E           |                                  | F <sub>i</sub> = R <sub>i</sub> NAND S <sub>i</sub> |  |  |  |  |

| Н  | Н  | Н              | Н              | F           |                                  | Fi = Ri OR Si                                       |  |  |  |  |

L = LOW

H = HIGH

i = 0 to 3

Am2903As may be cascaded in either a ripple carry or lookahead carry fashion. When a number of Am2903As are cascaded, each slice must be programmed to be a most significant slice (MSS), intermediate slice (IS), or least significant slice (LSS) of the array. The carry generate, G, and carry propagate, P, signals required for a lookahead carry scheme are generated by the Am2903A and are available as outputs of the least significant and intermediate slices.

The Am2903A also generates a carry-out signal,  $C_{n+4}$ , which is generally available as an output of each slice. Both the carry-in,  $C_n$ , and carry-out,  $C_{n+4}$ , signals are active HIGH. The ALU generates two other status outputs. These are negative, N, and overflow, OVR. The N output is generally the most significant (sign) bit of the ALU output and can be used to determine positive or negative results. The OVR output indicates that the arithmetic operation being performed exceeds the available two's complement number range. The N

and OVR signals are available as outputs of the most significant slice. Thus, the multipurpose  $\overline{G}/N$  and  $\overline{P}/OVR$  outputs indicate  $\overline{G}$  and  $\overline{P}$  at the least significant and intermediate slices, and sign and overflow at the most significant slice. To some extent, the meaning of the  $C_{n+4}$ ,  $\overline{P}/OVR$ , and  $\overline{G}/N$  signals vary with the ALU function being performed. Refer to Table 5 for an exact definition of these four signals as a function of the Am2903A instruction.

#### **ALU Shifter**

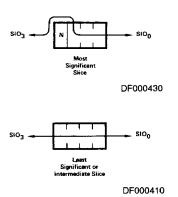

Under instruction control, the ALU shifter passes the ALU output (F) non-shifted, shifts it up one bit position (2F), or shifts it down one bit position (F/2). Both arithmetic and logical shift operations are possible. An arithmetic shift operation shifts data around the most significant (sign) bit position of the most significant slice, and a logical shift operation shifts data through this bit position (see Figure 1). SIO<sub>0</sub> and SIO<sub>3</sub> are bidirectional serial shift inputs/outputs. During a shift-up operation, SIO<sub>0</sub> is generally a serial shift input and SIO<sub>3</sub> a serial shift input and SIO<sub>6</sub> a serial shift output.

To some extent, the meaning of the SIO<sub>0</sub> and SIO<sub>3</sub> signals is instruction dependent. Refer to Tables 3 and 4 for an exact definition of these pins.

The ALU shifter also provides the capability to sign extend at slice boundaries. Under instruction control, the  $SIO_0$  (sign) input can be extended through  $Y_0$ ,  $Y_1$ ,  $Y_2$ ,  $Y_3$  and propagated to the  $SIO_3$  output.

A cascadable, five-bit parity generator/checker is designed into the Am2903A ALU shifter and provides ALU error detection capability. Parity for the  $F_0$ ,  $F_1$ ,  $F_2$ ,  $F_3$  ALU outputs and SIO $_3$  input is generated and, under instruction control, is made available at the SIO $_0$  output.

The instruction inputs determine the ALU shifter operation. Table 4 defines the special functions and the operation the ALU shifter performs for each. When the Am2903A executes instructions other than the special functions, the ALU shifter operation is determined by instruction bits I<sub>8</sub>, I<sub>7</sub>, I<sub>6</sub>, I<sub>5</sub>. Table 3 defines the ALU shifter operation as a function of these four bits

#### Q Register

The Q Register is an auxiliary four-bit register which is clocked on the LOW-to-HIGH transition of the CP input. It is intended primarily for use in multiplication and division operations; however, it can also be used as an accumulator or holding register for some applications. The ALU output, F, can be loaded into the Q Register, and/or the Q Register can be selected as the source for the ALU S operand. The shifter at the input to the Q Register provides the capability to shift the Q Register contents up one bit position (2Q) or down one bit position (Q/2). Only logical shifts are performed. QIO<sub>0</sub> and

${\rm QIO_3}$  are bidirectional shift serial inputs/outputs. During a Q Register shift-up operation,  ${\rm QIO_0}$  is a serial shift input and  ${\rm QIO_3}$  is a serial shift output. During a shift-down operation,  ${\rm QIO_3}$  is a serial shift input and  ${\rm QIO_0}$  is a serial shift output.

Figure 1-1.

Am2903A Arithmetic Shift Path

Figure 1-2.

Am2903A Logical Shift Path

Double-length arithmetic and logical shifting capability is provided by the Am2903A. The double-length shift is performed by connecting  $QlO_3$  of the most significant slice to  $SlO_0$  of the least significant slice, and executing an instruction which shifts both the ALU output and the Q Register.

The Q Register and shifter are controlled by the instruction inputs. Table 4 defines the Am2903A special functions and the operations which the Q Register and shifter perform for each. When the Am2903A executes instructions other than the special functions, the Q Register and shifter operation is controlled by instruction bits Ig, I7, I6, I5. Table 3 defines the Q Register and shifter operation as a function of these four bits.

#### **Output Buffers**

The DB and Y ports are bidirectional I/O ports driven by three-state output buffers with external output enable controls. The Y output buffers are enabled when the  $\overline{\text{OE}_Y}$  input is LOW and are in the high impedance state when  $\overline{\text{OE}_Y}$  is HIGH. The DB output buffers are enabled when the  $\overline{\text{OE}_B}$  input is LOW.

TABLE 3. ALU DESTINATION CONTROL FOR  $I_0$  OR  $I_1$  OR  $I_2$  OR  $I_3$  = HIGH,  $\overline{\text{IEN}}$  = LOW.

|                |    |    |                |             |                                                                                         | SIO               | 3                | Y <sub>3</sub>    |                  | Y2                |                  |                  |                  |                  |       | 0.000                          |                  |                  |

|----------------|----|----|----------------|-------------|-----------------------------------------------------------------------------------------|-------------------|------------------|-------------------|------------------|-------------------|------------------|------------------|------------------|------------------|-------|--------------------------------|------------------|------------------|

| l <sub>8</sub> | 17 | 16 | l <sub>5</sub> | Hex<br>Code | ALU Shifter<br>Function                                                                 | Most Sig<br>Slice | Other<br>Slices  | Most Sig<br>Slice | Other<br>Slices  | Most Sig<br>Slice | Other<br>Slices  | Y <sub>1</sub>   | Yo               | SIO <sub>0</sub> | Write | Q Reg &<br>Shifter<br>Function | QIO <sub>3</sub> | QIO <sub>0</sub> |

| L              | L  | L  | L              | 0           | Arith. F/2 → Y                                                                          | Input             | Input            | F <sub>3</sub>    | SIO <sub>3</sub> | SIO <sub>3</sub>  | F <sub>3</sub>   | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | L     | Hold                           | Z                | Z                |

| L              | L  | L  | Н              | 1           | Log. F/2→Y                                                                              | Input             | Input            | SIO <sub>3</sub>  | SIO <sub>3</sub> | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | L     | Hold                           | Z                | Z                |

| L              | L  | Н  | L              | 2           | Arith. F/2 → Y                                                                          | Input             | Input            | F <sub>3</sub>    | SIO <sub>3</sub> | SIO <sub>3</sub>  | F <sub>3</sub>   | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | L     | Log. Q/<br>2 → Q               | Input            | $Q_0$            |

| L              | L  | Н  | Н              | 3           | Log. F/2→Y                                                                              | Input             | Input            | SIO <sub>3</sub>  | SIO <sub>3</sub> | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | L     | Log. Q/<br>2→Q                 | Input            | Q <sub>0</sub>   |

| L              | Н  | L  | L              | 4           | F→Y                                                                                     | Input             | Input            | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>2</sub>    | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | Parity           | L     | Hold                           | Z                | Z                |

| L              | Н  | L  | Н              | 5           | F→Y                                                                                     | Input             | Input            | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>2</sub>    | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | Parity           | н     | Log. Q/<br>2→Q                 | Input            | $Q_0$            |

| L              | Н  | Н  | L              | 6           | F→Y                                                                                     | Input             | Input            | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>2</sub>    | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | Parity           | Н     | F→Q                            | Z                | Z                |

| L              | Н  | Н  | Н              | 7           | F→Y                                                                                     | Input             | Input            | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>2</sub>    | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | Parity           | L     | F→Q                            | Z                | Z                |

| Н              | L  | L  | L              | 8           | Arith. 2F → Y                                                                           | F <sub>2</sub>    | F <sub>3</sub>   | F <sub>3</sub>    | F <sub>2</sub>   | F₁                | F <sub>1</sub>   | F <sub>0</sub>   | SIO <sub>0</sub> | Input            | Ł     | Hold                           | Z                | Z                |

| Н              | L  | L  | Н              | 9           | Log. 2F → Y                                                                             | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>2</sub>    | F <sub>2</sub>   | F <sub>1</sub>    | F <sub>1</sub>   | F <sub>0</sub>   | SIO <sub>0</sub> | Input            | L     | Hold                           | Z                | Z                |

| Н              | L  | Н  | L              | Α           | Arith. 2F → Y                                                                           | F <sub>2</sub>    | F <sub>3</sub>   | F <sub>3</sub>    | F <sub>2</sub>   | F <sub>1</sub>    | F <sub>1</sub>   | F <sub>0</sub>   | SIO <sub>0</sub> | Input            | L     | Log.<br>2Q → Q                 | Q <sub>3</sub>   | Input            |

| Н              | L  | Н  | Н              | В           | Log. 2F → Y                                                                             | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>2</sub>    | F <sub>2</sub>   | F <sub>1</sub>    | F <sub>1</sub>   | F <sub>0</sub>   | SIO <sub>0</sub> | Input            | L     | Log.<br>2Q → Q                 | Q <sub>3</sub>   | Input            |

| Н              | Н  | L  | L              | Ç           | F→Y                                                                                     | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>2</sub>    | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | Z                | н     | Hold                           | Z                | Z                |

| н              | Н  | L  | Н              | D           | F-Y                                                                                     | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>2</sub>    | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | Z                | н     | Log.<br>2Q → Q                 | Q <sub>3</sub>   | Input            |

| Н              | Н  | Н  | L              | E           | SIO <sub>0</sub> → Y <sub>0</sub> ,<br>Y <sub>1</sub> , Y <sub>2</sub> , Y <sub>3</sub> | SIO <sub>0</sub>  | SIO <sub>0</sub> | SIO <sub>0</sub>  | SIO <sub>0</sub> | SIO <sub>0</sub>  | SIO <sub>0</sub> | SIO <sub>0</sub> | SIO <sub>0</sub> | Input            | L     | Hold                           | Z                | Z                |

| Н              | Н  | Н  | Н              | F           | F→Y                                                                                     | F <sub>3</sub>    | F <sub>3</sub>   | F <sub>3</sub>    | F3               | F <sub>2</sub>    | F <sub>2</sub>   | F <sub>1</sub>   | F <sub>0</sub>   | Z                | L     | Hold                           | Z                | Z                |

$\begin{array}{lll} \text{Parity} = \text{F}_3 \ \, \triangledown \, \, \text{F}_2 \ \, \triangledown \, \, \text{F}_1 \ \, \triangledown \, \, \text{F}_0 \ \, \triangledown \, \, \text{SIO}_3 & \qquad \qquad \text{L} = \text{LOW} \\ \quad \, \triangledown \, = \text{Exclusive OR} & \quad \, \text{H} = \text{HIGH} \end{array}$

Z = High-Impedance

TABLE 4. SPECIAL FUNCTIONS FOR  $I_4 = I_3 = I_2 = I_1 = I_0 = LOW$  (Note 4)

|                                                                      |                                                        |                                                                            |                         | SIO                             | 3               |                  | 0.0                            |                  |                |         |

|----------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------|-------------------------|---------------------------------|-----------------|------------------|--------------------------------|------------------|----------------|---------|

| (Hex)<br>  <sub>8</sub>   <sub>7</sub>   <sub>6</sub>   <sub>5</sub> | Special Function                                       | ALU Function                                                               | ALU Shifter<br>Function | Most Sig<br>Slice               | Other<br>Slices | SIO <sub>0</sub> | Q Reg &<br>Shifter<br>Function | Q1O <sub>3</sub> | Q <sub>0</sub> | WRITE   |

| 0                                                                    | Unsigned Multiply                                      | $F = S + C_n$ if $Z = L$<br>$F = R + S + C_n$ if $Z = H$                   | Log F/2→Y<br>(Note 1)   | Z                               | Input           | F <sub>0</sub>   | Log Q/2                        | Input            | Q <sub>0</sub> | L       |

| 1                                                                    | (Note 5)                                               |                                                                            |                         |                                 |                 |                  |                                | <del> </del>     |                |         |

| 2                                                                    | Two's Complement<br>Multiply                           | $F = S + C_n$ if $Z = L$<br>$F = R + S + C_n$ if $Z = H$                   | Log F/2→Y<br>(Note 2)   | Z                               | Input           | F <sub>0</sub>   | Log Q/2<br>→ Q                 | Input            | Q <sub>0</sub> | L.      |

| 3                                                                    | (Note 5)                                               |                                                                            |                         |                                 |                 |                  |                                | -                |                | <b></b> |

| 4                                                                    | Increment by<br>One or Two                             | F = S + 1 + C <sub>n</sub>                                                 | F→Y                     | Input                           | Input           | Parity           | Hold                           | Z                | Z              | L       |

| 5                                                                    | Sign/Magnitude<br>Two's Complement                     | $F = S + C_n \text{ if } Z = L$ $F = \overline{S} + C_n \text{ if } Z = H$ | F→Y<br>(Note 3)         | Input                           | Input           | Parity           | Hold                           | Z                | Z              | L       |

| 6                                                                    | Two's Complement<br>Multiply, Last Cycle               | $F = S + C_n$ if $Z = L$<br>$F = S - R - 1 + C_n$ if $Z = H$               | Log F/2 - Y<br>(Note 2) | Z                               | Input           | F <sub>0</sub>   | Log Q/2<br>→Q                  | Input            | Q <sub>0</sub> | L       |

| 7                                                                    | (Note 5)                                               |                                                                            |                         |                                 |                 |                  |                                |                  |                |         |

| 8                                                                    | Single Length<br>Normalize                             | $F = S + C_n$                                                              | F→Y                     | F <sub>3</sub>                  | F <sub>3</sub>  | Z                | Log 2Q<br>→Q                   | Q <sub>3</sub>   | Input          | L       |

| 9                                                                    | (Note 5)                                               |                                                                            |                         |                                 |                 |                  |                                |                  | _              |         |

| A                                                                    | Double Length<br>Normalize and First<br>Divide Op      | $F = S + C_n$                                                              | Log 2F→Y                | R <sub>3</sub> ∇ F <sub>3</sub> | F <sub>3</sub>  | Input            | Log 2Q<br>→Q                   | Q <sub>3</sub>   | Input          | L       |

| В                                                                    | (Note 5)                                               |                                                                            |                         |                                 |                 |                  |                                |                  |                |         |

| С                                                                    | Two's Complement<br>Divide                             | $F = S + R + C_n$ if $Z = L$<br>$F = S - R - 1 + C_n$ if $Z = H$           | Log 2F→Y                | R <sub>3</sub> ∇ F <sub>3</sub> | F <sub>3</sub>  | Input            | Log 2Q<br>→Q                   | Q <sub>3</sub>   | Input          | L       |

| D                                                                    | (Note 5)                                               |                                                                            |                         |                                 |                 |                  |                                |                  |                |         |

| E                                                                    | Two's Complement<br>Divide Correction<br>and Remainder | $F = S + R + C_n$ if $Z = L$<br>$F = S - R - 1 + C_n$ if $Z = H$           | F→Y                     | F <sub>3</sub>                  | F <sub>3</sub>  | Z                | Log 2Q<br>→Q                   | Q <sub>3</sub>   | Input          | L       |

| F                                                                    | (Note 5)                                               |                                                                            |                         |                                 |                 |                  |                                |                  |                |         |

Notes: 1. At the most significant slice only, the C<sub>n+4</sub> signal is internally gated to the Y<sub>3</sub> output.

2. At the most significant slice only, F<sub>3</sub> ♥ OVR is internally gated to the Y<sub>3</sub> output.

3. At the most significant slice only, S<sub>3</sub> ♥ F<sub>3</sub> is generated at the Y<sub>3</sub> output.

4. The Q Register cannot be used explicitly as an operand for any Special Functions. It is defined implicitly within the functions.

5. Not valid.

= LOW Z ♥ = High-Impedance = HIGH = Exclusive OR

= Don't Care = SIO3 V F3 V F2 V F1 V F0 Parity

The zero, Z, pin is an open collector input/output that can be wire-OR'ed between slices. As an output it can be used as a zero detect status flag and generally indicates that the Yo-3 pins are all LOW. To some extent the meaning of this signal varies with the instruction being performed. Refer to Table 5 for an exact definition of this signal as a function of the Am2903A instructions.

#### Instruction Decoder

The Instruction Decoder generates required internal control signals as a function of the nine instruction inputs, In-8; the Instruction Enable input, IEN; the LSS input; and the WRITE/ MSS input/output.

The WRITE output is LOW when an instruction which writes data into the RAM is being executed. Refer to Tables 3 and 4 for a definition of the WRITE output as a function of the Am2903A instruction inputs.

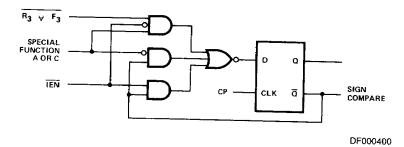

On the Am2903A, when IEN is HIGH, the WRITE output is forced HIGH and the Q Register and Sign Compare Flip-Flop contents are preserved. When IEN is LOW, the WRITE output is enabled and the Q Register and Sign Compare Flip-Flop can be written according to the Am2903A instruction. The Sign Compare Flip-Flop is an on-chip flip-flop which is used during an Am2903A divide operation (see Figure 2).

#### Programming the Am2903A Slice Position

Tying the LSS input LOW programs the slice to operate as a least significant slice (LSS) and enables the WRITE output signal onto the  $\overline{\text{WRITE}}/\overline{\text{MSS}}$  bidirectional I/O pin. When  $\overline{\text{LSS}}$ is tied HIGH, the WRITE/MSS pin becomes an input pin; tying the WRITE/MSS pin HIGH programs the slice to operate as an intermediate slice (IS) and tying it LOW programs the slice to operate as a most significant slice (MSS). The WRITE/MSS pin must be tied HIGH through a resistor. WRITE/MSS and LSS should not be connected together.

|                                                  |          |    |                                                                                                          | TAE                                                                    | BLE 5. /               | Am2903A                                    | STAT            | JS OUTPU                                                                                | TS              |                                                            |                                                            |                                                                                                   |

|--------------------------------------------------|----------|----|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------|--------------------------------------------|-----------------|-----------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

|                                                  |          |    |                                                                                                          |                                                                        |                        | P/OV                                       | R               | Ğ/N                                                                                     |                 |                                                            | Z( <del>OE</del> <sub>Y</sub> = LOW)                       |                                                                                                   |

| (Hex)                                            | (Hex)    | lo | Gi<br>(i = 0 to 3)                                                                                       | Pi<br>(i = 0 to 3)                                                     | C <sub>n+4</sub>       | Most Sig<br>Slice                          | Other<br>Slices | Most Sig<br>Slice                                                                       | Other<br>Slices | Most Sig<br>Slice                                          | Intermediate<br>Slice                                      | Least Sig<br>Slice                                                                                |

| X                                                | 0        | H  | 0                                                                                                        | 1                                                                      |                        | 0                                          | 0               | F <sub>3</sub>                                                                          | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| х                                                | 1        | x  | R <sub>i</sub> ∧S <sub>i</sub>                                                                           | R̄ <sub>i</sub> v S <sub>i</sub>                                       | G v<br>PC <sub>n</sub> | C <sub>n + 3</sub> ∇<br>C <sub>n + 4</sub> | P               | F <sub>3</sub>                                                                          | Ğ               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| X                                                | 2        | х  | R <sub>i</sub> ∧ <del>S</del> i                                                                          | Ri v Si                                                                | G v<br>PCn             | C <sub>n + 3</sub> ∇<br>C <sub>n + 4</sub> | P               | F <sub>3</sub>                                                                          | ัด              | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| х                                                | 3        | x  | R <sub>i</sub> ^S <sub>i</sub>                                                                           | R <sub>i</sub> v S <sub>i</sub>                                        | G v<br>PCn             | C <sub>n + 3</sub> ∇<br>C <sub>n + 4</sub> | ₽               | F <sub>3</sub>                                                                          | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| Х                                                | 4        | х  | 0                                                                                                        | Si                                                                     | G v<br>PCn             | C <sub>n + 3</sub> ∇<br>C <sub>n + 4</sub> | Ē               | F <sub>3</sub>                                                                          | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overrightarrow{Y}_0\overrightarrow{\nabla}_1\overrightarrow{\nabla}_2\overrightarrow{\nabla}_3$ |

| ×                                                | 5        | х  | 0                                                                                                        | Īs <sub>i</sub>                                                        | G v<br>PCn             | C <sub>n+3</sub> ∇<br>C <sub>n+4</sub>     | P               | F <sub>3</sub>                                                                          | <u>G</u>        | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                             |

| Х                                                | 6        | ×  | 0                                                                                                        | Ri                                                                     | G v<br>PCn             | C <sub>n + 3</sub> ∇<br>C <sub>n + 4</sub> | P               | F <sub>3</sub>                                                                          | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| x                                                | 7        | ×  | 0                                                                                                        | $\overline{R}_{i}$                                                     | G v<br>PCn             | C <sub>n + 3</sub> ∇<br>C <sub>n + 4</sub> | P               | F3                                                                                      | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| X                                                | 8        | x  | 0                                                                                                        | 1                                                                      | 0                      | 0                                          | 0               | F <sub>3</sub>                                                                          | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| X                                                | 9        | 1  | R <sub>i</sub> ∧S <sub>i</sub>                                                                           | 1                                                                      | 0                      | 0                                          | 0               | F <sub>3</sub>                                                                          | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                                                             |

| X                                                | Α        | X  | R₁∧Sį                                                                                                    | R <sub>i</sub> v S <sub>i</sub>                                        | 0                      | 0                                          | 0               | F <sub>3</sub>                                                                          | Ğ               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| Х                                                | В        | X  | R̄ <sub>i</sub> ∧S <sub>i</sub>                                                                          | R <sub>i</sub> v S <sub>i</sub>                                        | 0                      | 0                                          | 0               | F <sub>3</sub>                                                                          | Ğ               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| X                                                | С        | X  | R <sub>i</sub> ∧S <sub>i</sub>                                                                           | 1                                                                      | 0                      | 0                                          | 0               | F <sub>3</sub>                                                                          | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| X                                                | D        | X  | Āi^Ši                                                                                                    | 1                                                                      | 0                      | 0                                          | 0               | F <sub>3</sub>                                                                          | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| Х                                                | Е        | X  | Pi^Si                                                                                                    | 1                                                                      | 0                      | 0                                          | 0               | F <sub>3</sub>                                                                          | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overrightarrow{Y}_0\overrightarrow{Y}_1\overrightarrow{Y}_2\overrightarrow{Y}_3$                |

| X                                                | F        | X  | Ā <sub>i</sub> ∧Š <sub>i</sub>                                                                           | 1                                                                      | 0                      | 0                                          | 0               | F <sub>3</sub>                                                                          | G               | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$ | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| 0                                                | 0        | L  | 0 if $Z = L$<br>$R_i \land S_i$ if $Z = H$                                                               | S <sub>i</sub> if Z = L<br>R <sub>i</sub> v S <sub>i</sub> if<br>Z = H | G v<br>PC <sub>n</sub> | C <sub>n+3</sub> ♥<br>C <sub>n+4</sub>     | P               | F <sub>3</sub>                                                                          | G               | Input                                                      | Input                                                      | Q <sub>0</sub>                                                                                    |

| 1                                                | 0        | L  | (Note 6)                                                                                                 |                                                                        |                        |                                            |                 | <u> </u>                                                                                |                 |                                                            |                                                            | <u></u>                                                                                           |

| 1                                                | 8        | L  | (Note 6)                                                                                                 |                                                                        |                        |                                            |                 |                                                                                         |                 |                                                            |                                                            |                                                                                                   |

| 2                                                | 0        | L  | 0 if $Z = L$<br>$R_i \wedge S_i$ if $Z = H$                                                              | Si if Z = L<br>Ri v Si if<br>Z = H                                     | G v<br>PCn             | C <sub>n+3</sub> ♥<br>C <sub>n+4</sub>     | P               | F <sub>3</sub>                                                                          | G               | Input                                                      | Input                                                      | Q <sub>0</sub>                                                                                    |

| 3                                                | 0        | L  | (Note 6)                                                                                                 |                                                                        |                        |                                            |                 | <u> </u>                                                                                | ļ               |                                                            |                                                            |                                                                                                   |

| 4                                                | 0        | L  | (Note 1)                                                                                                 | (Note 2)                                                               | G v<br>PCn             | C <sub>n + 3</sub>                         | P               | Fg                                                                                      | G               | $\vec{Y}_0\vec{Y}_1\vec{Y}_2\vec{Y}_3$                     | $\nabla_0 \nabla_1 \nabla_2 \nabla_3$                      | $\overline{Y}_0\overline{Y}_1\overline{Y}_2\overline{Y}_3$                                        |

| 5                                                | 0        | L  | 0                                                                                                        | Si if Z = L<br>Si if Z = H                                             | G v<br>PC <sub>n</sub> | C <sub>n+3</sub> ♥<br>C <sub>n+4</sub>     | ₽               | $\begin{array}{c} F_3 \text{ if } Z = L \\ F_3 \ \ S_3 \text{ if} \\ Z = H \end{array}$ | G               | S <sub>3</sub>                                             | Input                                                      | Input                                                                                             |

| 6                                                | 0        | L  | $\frac{0}{R_i} \text{ if } Z = L$ $\frac{0}{R_i} \text{ if } Z = H$                                      | Si if Z = L<br>Ri v Si if<br>Z = H                                     | G v<br>PC <sub>n</sub> | C <sub>n + 3</sub> ∇<br>C <sub>n + 4</sub> | Ē               | F <sub>3</sub>                                                                          | G               | Input                                                      | Input                                                      | Q <sub>0</sub>                                                                                    |

| 7                                                | 0        | L  |                                                                                                          |                                                                        |                        |                                            | <del> </del>    | 1                                                                                       | G               | 5555                                                       | 5555                                                       | $\overline{Q}_0\overline{Q}_1\overline{Q}_2\overline{Q}_3$                                        |

| 8                                                | 0        | L  | 0                                                                                                        | Si                                                                     | (Note 3)               | Q2 7 Q1                                    | P               | Q <sub>3</sub>                                                                          | G               | $\overline{Q}_0\overline{Q}_1\overline{Q}_2\overline{Q}_3$ | $\overline{Q}_0\overline{Q}_1\overline{Q}_2\overline{Q}_3$ | <u>u0u1u2u3</u>                                                                                   |

| 9                                                | 0        | L  | ·                                                                                                        | ļ                                                                      | ļ                      | ļ                                          | <del></del>     | <del> </del>                                                                            | 1-              | <del> </del>                                               |                                                            |                                                                                                   |

| 9                                                | 8        | —  | (Note 6)                                                                                                 | <u> </u>                                                               |                        |                                            | P               | <del>  </del>                                                                           | G               | (Nigto 5)                                                  | (Note 5)                                                   | (Note 5)                                                                                          |

| Α                                                | 0        | L  |                                                                                                          | S <sub>i</sub>                                                         | (Note 4)               | F <sub>2</sub> ∇ F <sub>1</sub>            | P               | F <sub>3</sub>                                                                          | <u> </u>        | (Note 5)                                                   | (More 5)                                                   | (140(8-3)                                                                                         |

| В                                                | 0        | L  | (Note 6)                                                                                                 | <u> </u>                                                               | <b>_</b>               | <u> </u>                                   | ļ <u>.</u>      | <b>!</b>                                                                                | ļ.——            | <del>                                     </del>           |                                                            |                                                                                                   |

| С                                                | 0        | L  | $\begin{cases} R_{i} \land S_{i} & \text{if } Z = L \\ R_{i} \land S_{i} & \text{if } Z = H \end{cases}$ | $R_i \vee S_i$ if $Z = L$<br>$R_i \vee S_i$ if $Z = H$                 | G v<br>PCn             | C <sub>n+3</sub> ∇<br>C <sub>n+4</sub>     | P               | F <sub>3</sub>                                                                          | G               | Sign<br>Compare FF<br>Output                               | Input                                                      | Input                                                                                             |

| D                                                | 0        | L  | (Note 6)                                                                                                 |                                                                        |                        | <u> </u>                                   |                 |                                                                                         | ļ               | ļ <u>.</u>                                                 |                                                            | ļ                                                                                                 |

| E                                                | 0        | _  | $\frac{R_i \wedge S_i \text{ if } Z = L}{R_i \wedge S_i \text{ if } Z = H}$                              | $R_i \vee S_i$ if $Z = L$<br>$R_i \vee S_i$ if $Z = H$                 | G v<br>PC <sub>n</sub> | C <sub>n+3</sub> ∇<br>C <sub>n+4</sub>     | ₽               | F <sub>3</sub>                                                                          | G               | Sign<br>Compare FF<br>Output                               | Input                                                      | Input                                                                                             |

| F                                                | 0        | 1  | . (Note 6)                                                                                               | <del>                                     </del>                       |                        |                                            |                 |                                                                                         |                 |                                                            |                                                            |                                                                                                   |

| <del>                                     </del> | <u> </u> |    |                                                                                                          | <u> </u>                                                               |                        |                                            |                 |                                                                                         |                 |                                                            |                                                            |                                                                                                   |

Notes: 1. If  $\overline{LSS}$  is LOW,  $G_0=S_0$  and  $G_{1,\ 2,\ 3}=0$ . If  $\overline{LSS}$  is HIGH,  $G_{0,\ 1,\ 2,\ 3}=0$ . 2. If  $\overline{LSS}$  is LOW,  $P_0=1$  and  $P_{1,\ 2,\ 3}=S_{1,\ 2,\ 3}$ . If  $\overline{LSS}$  is HIGH,  $P_1=S_1$ . 3. At the most significant slice,  $C_n+4=Q_3$   $\forall$   $Q_2$ . At other slices,  $C_n+4=G$   $\vee$   $PC_n$ . 4. At the most significant slice,  $C_n+4=F_3$   $\forall$   $F_2$ . At other slices,  $C_n+4=G$   $\vee$   $PC_n$ . 5.  $Z=\overline{Q_0}$   $\overline{Q_1}$   $\overline{Q_2}$   $\overline{Q_3}$   $\overline{F_0}$   $\overline{F_1}$   $\overline{F_2}$   $\overline{F_3}$ . 6. Not valid.

$<sup>\</sup>begin{array}{lll} L &= LOW = 0 \\ H &= HIGH = 1 \\ v &= OR \\ & \Leftarrow AND \\ \hline ? &= EXCLUSIVE \ OR \\ P &= P_3P_2P_1P_0 \\ G &= G_3 \ v \ G_2P_3 \ v \ G_1P_2P_3 \ v \ G_0P_1P_2P_3 \\ C_{n+3} &= G_2 \ v \ G_1P_2 \ v \ G_0P_1P_2 \ v \ C_nP_0P_1P_2 \end{array}$

#### Am2903A Special Functions

The Am2903A provides nine Special Functions which facilitate the implementation of the following operations:

- Single- and Double-Length Normalization

- Two's Complement Division

- Unsigned and Two's Complement Multiplication

- Conversion Between Two's Complement and Sign/Magnitude Representation

- Incrementation by One or Two

Table 4 defines these Special Functions.

The Single-Length and Double-Length Normalization functions can be used to adjust a single-precision or double-precision floating point number in order to bring its mantissa within a specified range.

Three Special Functions which can be used to perform a two's complement, non-restoring divide operation are provided by the Am2903A. These functions provide both single- and double-precision divide operations and can be performed in

"n" clock cycles, where "n" is the number of bits in the quotient.

The Unsigned Multiply Special Function and the two Two's Complement Multiply Special Functions can be used to multiply two n-bit, unsigned or two's complement numbers, respectively, in n clock cycles. These functions utilize the conditional add and shift algorithm. During the last cycle of the two's complement multiplication, a conditional subtraction, rather than addition, is performed because the sign bit of the multiplier carries negative weight.

The Sign/Magnitude-Two's Complement Special Function can be used to convert number representation systems. A number expressed in Sign/Magnitude representation can be converted to the Two's Complement representation, and vice-versa, in one clock cycle.

The Increment by One or Two Special Function can be used to increment an unsigned or two's complement number by one or two. This is useful in 16-bit word, byte-addressable machines, where the word addresses are multiples of two.

Figure 2. Sign Compare Flip-Flop

The sign compare signal appears at the Z output of the most significant slice during special functions C and E. Refer to Table 5.

# Cycle Times for 16-Bit System for Common Operations

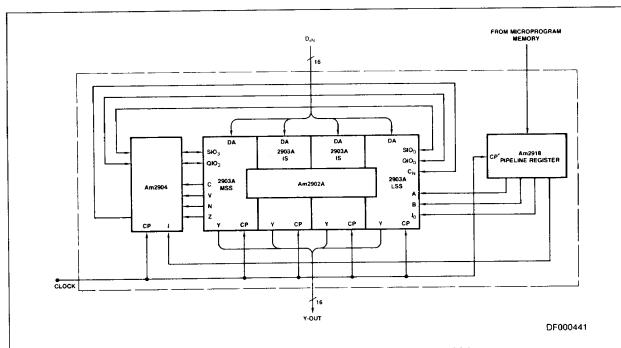

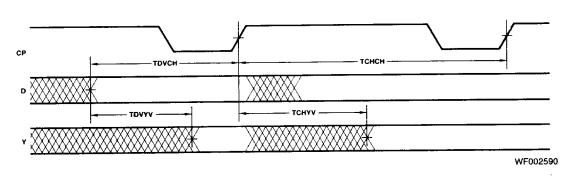

Figure 3 shows a typical configuration using 4 Am2903A Superslices, an Am2902A carry lookahead chip, and the Am2904 for shift multiplexers, status registers, and carry-in control. For the system enclosed within the dashed lines, there are four major switching paths whose values for various kinds of cycles are summarized below, and shown on the timing waveform, Figure 4.

- MICROCYCLE TIME (TCHCH).

The minimum time which must elapse between a LOW-TO-HIGH clock transition and the next LOW-TO-HIGH clock transition.

- DATA SET-UP TIME (TDVCH).

The minimum time which must be allowed between valid, stable data on the D inputs and the clock LOW-TO-HIGH transition.

- D TO Y (TDVYV).

The maximum time required to obtain valid Y output data after the D inputs are valid. This is the combinational delay through the parts from D to Y.

- CP TO Y (TCHYV).

The maximum time required to obtain valid Y outputs after a clock LOW-TO-HIGH transition.

The types of cycles for which data is summarized are as follows:

- 1. Logic Any logical operation without a shift.

- Logic Rotate Any logic operation with a rotate or shift.

- 3. Arithmetic An add or subtract with no shift.

- Multiply The first cycle of a 2's complement multiply instruction. Subsequent cycles require less time.

- Divide The iterative divide cycle. The first divide instruction and the last divide (correction) instruction require less time.

## Time in ns Over Commercial Operating Range

| CYCLE        | тснсн | TDVCH | TDVYV | TCHYV |

|--------------|-------|-------|-------|-------|

| LOGIC        | 99    | 79    | 59    | 81    |

| LOGIC ROTATE | 118   | 99    | 79    | 98    |

| ARITHMETIC   | 130   | 109   | 91    | 112   |

| MULTIPLY     | 152   | 113   | 95    | 135   |

| DIVIDE       | 139   | 113   | 95    | 121   |

Figure 3. 16-Bit System with Am2903A, Am2902A, Am2904

Figure 4. Timing Waveforms for Data in, Clock, and Y Out

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                             |

|-------------------------------------------------|

| Continuous0.5 V to +7.0 V                       |

| DC Voltage Applied to Outputs For               |

| High Output State0.5 V to +V <sub>CC</sub> Max. |

| DC Input Voltage0.5 V to +5.5 V                 |

| DC Output Current, Into Outputs30 mA            |

| DC input Current30 mA to +5.0 mA                |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices |                  |

|------------------------|------------------|

| Temperature            | 0 to +70°C       |

| Supply Voltage         |                  |

| Military (M) Devices   |                  |

| Temperature            | 55 to +125°C     |

| Supply Voltage         | +4.5 V to +5.5 V |

Operating ranges define those limits over which the functionality of the device is guaranteed.

## DC CHARACTERISTICS over operating range unless otherwise specified

Table continued on next page

| Parameters      | Description                                     | Te                                                                                              | est Condi                                                              |                                                                                                                                                             |                                                                                                                                                             | Min. | Typ.<br>(Note 1) | Max.  | Units |  |

|-----------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------|-------|-------|--|

|                 |                                                 |                                                                                                 |                                                                        | IOH<br>Yo-                                                                                                                                                  | = - 1.6 mA<br>Y <sub>3</sub> , G/N                                                                                                                          | 2.4  |                  |       |       |  |

| VOH             | Output HIGH Voltage                             | V <sub>CC</sub> = Min.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub>                  |                                                                        | DB <sub>i</sub>                                                                                                                                             | = -800 µA<br><sub>0-3</sub> , P/OVR<br><sub>10</sub> , SIO <sub>3</sub> , QIO <sub>0</sub> , QIO <sub>3</sub> ,<br>ITE, C <sub>n+4</sub>                    | 2.4  |                  |       | Volts |  |

| ICEX            | Output Leakage Current<br>for Z Output (Note 4) | V <sub>CC</sub> = Min., V <sub>OH</sub><br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | = Min., V <sub>OH</sub> = 5.5 V<br>V <sub>IH</sub> or V <sub>IL</sub>  |                                                                                                                                                             |                                                                                                                                                             |      |                  | 250   | μΑ    |  |

|                 |                                                 |                                                                                                 | Y <sub>0</sub> , Y <sub>1</sub> , Y<br>Y <sub>3</sub> , Z              | 2                                                                                                                                                           | I <sub>OL</sub> = 20 mA (COM'L) I <sub>OL</sub> = 16 mA (MIL)                                                                                               |      |                  | 0.5   |       |  |

| V <sub>OL</sub> | Output LOW Voltage                              | V <sub>CC</sub> = Min.                                                                          | DB <sub>0</sub> , DB <sub>1</sub><br>DB <sub>2</sub> , DB <sub>3</sub> |                                                                                                                                                             | $I_{OL} = 12$ mA (COM'L)<br>$I_{OL} = 8.0$ mA (MIL)                                                                                                         |      |                  | 0.5   | Valle |  |