## **AM2914**

## Vectored Priority Interrupt Controller

The AM2914 is a high-speed, eight-bit priority interrupt unit that is cascadable to handle any number of priority interrupt request levels. The high-speed of the AM2914 makes it ideal for use in AM2900 family microcomputer designs, but it can be used with the AM9080A MOS microprocessor.

The AM2914 receives interrupt requests on 8 interrupt input lines ( $\overline{P}_0$  -  $\overline{P}_7$ ). A LOW level is a request. An internal latch may be used to catch pulses on these lines, or the latch may be bypassed so the request lines drive the level-triggered interrupt register directly. An 8-bit mask register is used to mask individual interrupts. Considerable flexibility is provided for controlling the mask register. Requests in the mask register are ANDed with the corresponding bits in the mask register and the results are sent to an 8-input priority encoder, which produces a three-bit encoded vector representing the highest numbered input which is not masked.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

Advanced Micro Devices

#### DISTINCTIVE CHARACTERISTICS

- Accepts 8 interrupt inputs –

Interrupts may be pulses or levels and are stored internally

- Built-in mask register –

Six different operations can be performed on

mask register

- Built-in status register –

Status register holds code for lowest allowed interrupt

- Vectored output –

Output is binary code for highest priority unmasked interrupt

- Expandable –

Any number of Am2914's may be stacked for large interrupt systems

- Microprogrammable –

Executes 16 different microinstructions

Instruction enable pin aids in vertical microprogramming

#### **GENERAL DESCRIPTION**

The Am2914 is a high-speed, eight-bit priority interrupt unit that is cascadable to handle any number of priority interrupt request levels. The high-speed of the Am2914 makes it ideal for use in Am2900 family microcomputer designs, but it can also be used with the Am9080A MOS microprocessor.

The Am2914 receives interrupt requests on 8 interrupt input lines ( $\bar{P}_0$ - $\bar{P}_7$ ). A LOW level is a request. An internal latch may be used to catch pulses on these lines, or the latch may be bypassed so the request lines drive the level-triggered interrupt register directly. An 8-bit mask register is used to mask individual interrupts. Considerable flexibility is provided for controlling the mask register. Requests in the interrupt register are ANDed with the corresponding bits in the mask register and the results are sent to an 8-input priority encoder, which produces a three-bit encoded vector representing the highest numbered input which is not masked.

An internal status register is used to point to the lowest priority at which an interrupt will be accepted. The contents of the status register are compared with the output of the priority encoder, and an interrupt request output will occur if the vector is greater than or equal to status. Whenever a vector is read from the Am2914 the status register is automatically updated to point to one level higher than the vector read. (The status register can be loaded externally or read out at any time using the S pins.) Signals are provided for moving the status upward across devices (Group Advance Send and Group Advance Receive) and for inhibiting lower priorities from higher order devices (Ripple Disable, Parallel Disable, and Interrupt Disable). A status overflow output indicates that an interrupt has been read at the highest priority.

The Am2914 is controlled by a 4-bit instruction field  $I_0$ - $I_3$ . The command on the instruction lines is executed if  $\overline{IE}$  is LOW and is ignored if  $\overline{IE}$  is HIGH, allowing the 4 I bits to be shared with other devices.

#### RELATED PRODUCTS

| Part No.  | Description                 |

|-----------|-----------------------------|

| Am2902A   | Carry Look-ahead Generator  |

| Am2913    | Priority Interrupt Expander |

| Am25LS138 | 3-to-8 Decoder              |

| Am27S19   | Mapping PROM                |

3

Orig

004778

4778

AMD

Publication # Rev. Amendment / 03576 E /0 Issue Date: January 1987

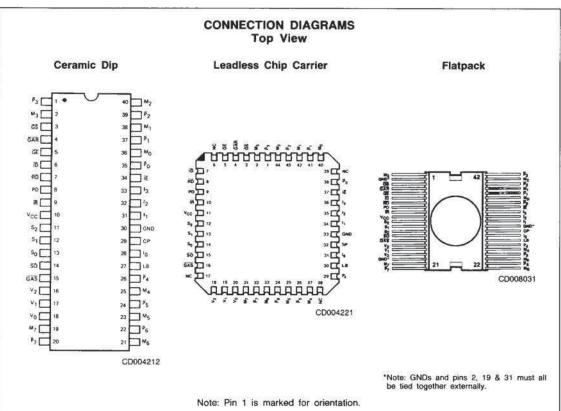

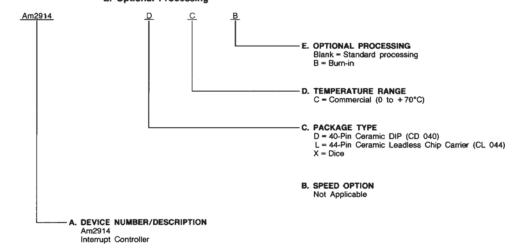

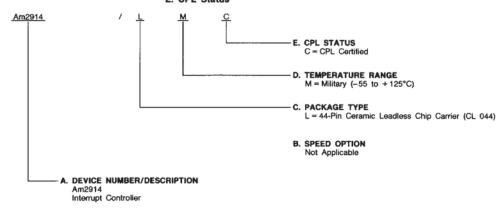

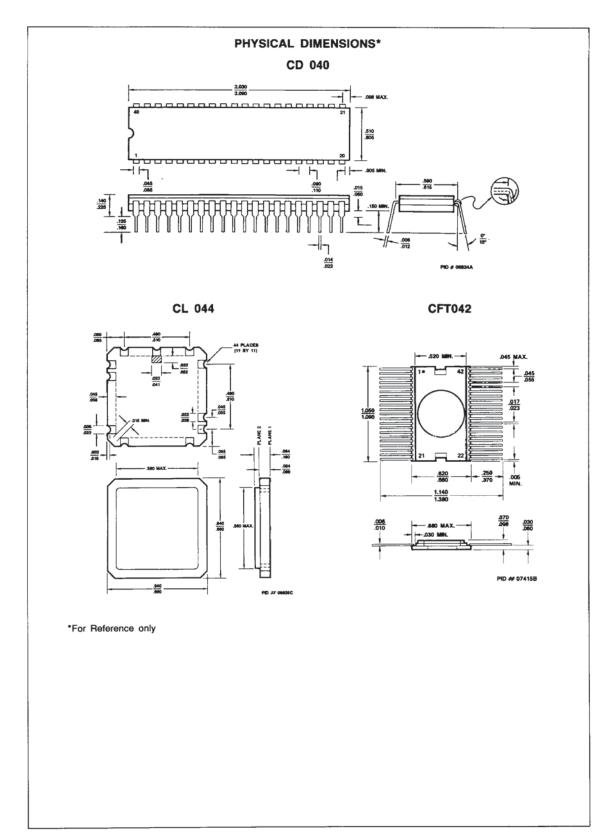

## ORDERING INFORMATION Standard Products

AMD products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: A. Device Number

- B. Speed Option (if applicable)

- C. Package Type

- D. Temperature Range

- E. Optional Processing

| Valid Combinations |                    |  |  |  |  |  |  |

|--------------------|--------------------|--|--|--|--|--|--|

| Am2914             | DC, DCB,<br>LC, XC |  |  |  |  |  |  |

|                    |                    |  |  |  |  |  |  |

|                    | add                |  |  |  |  |  |  |

#### Valid Combinations

Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released valid combinations, and to obtain additional data on AMD's standard military grade products.

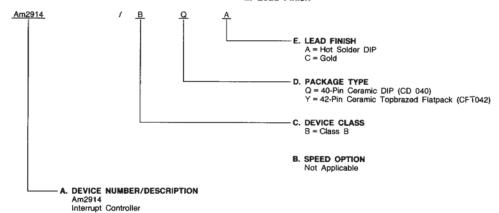

## ORDERING INFORMATION (Cont.) APL Products

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-M-38510 and MIL-STD-883C requirements. CPL (Controlled Products List) products are processed in accordance with MIL-M-38510 and MIL-STD-883C, but are inherently non-compliant because of package, solderability, or surface treatment exceptions to those specifications. The order number (Valid Combination) for APL products is formed by a combination of: **A. Device Number**

- B. Speed Option (if applicable)

- C. Device Class

- D. Package Type

- E. Lead Finish

| Valid Combinations |              |  |  |  |  |  |

|--------------------|--------------|--|--|--|--|--|

| APL                |              |  |  |  |  |  |

| Am2914             | /BQA<br>/BYC |  |  |  |  |  |

| CPL                |              |  |  |  |  |  |

| Am2914             | /LMC         |  |  |  |  |  |

#### Valid Combinations

Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

#### **Group A Tests**

Group A Tests consist of subgroups: 1, 2, 3, 7, 8, 9, 10, 11

### **CPL PRODUCTS**

The order number (Valid Combination) for CPL products is formed by a combination of:

- A. Device Number

- B. Speed Option (if applicable)

- C. Package Type

- D. Temperature Range

- E. CPL Status

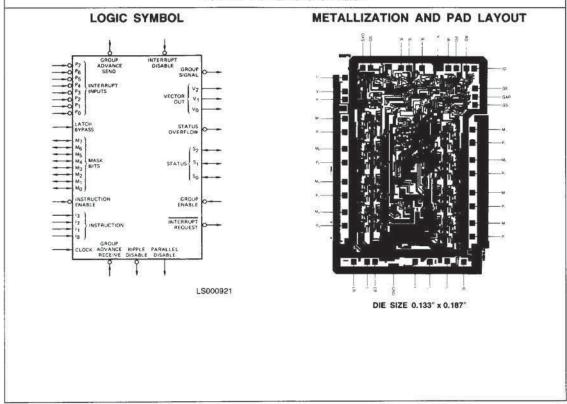

#### PIN DESCRIPTION

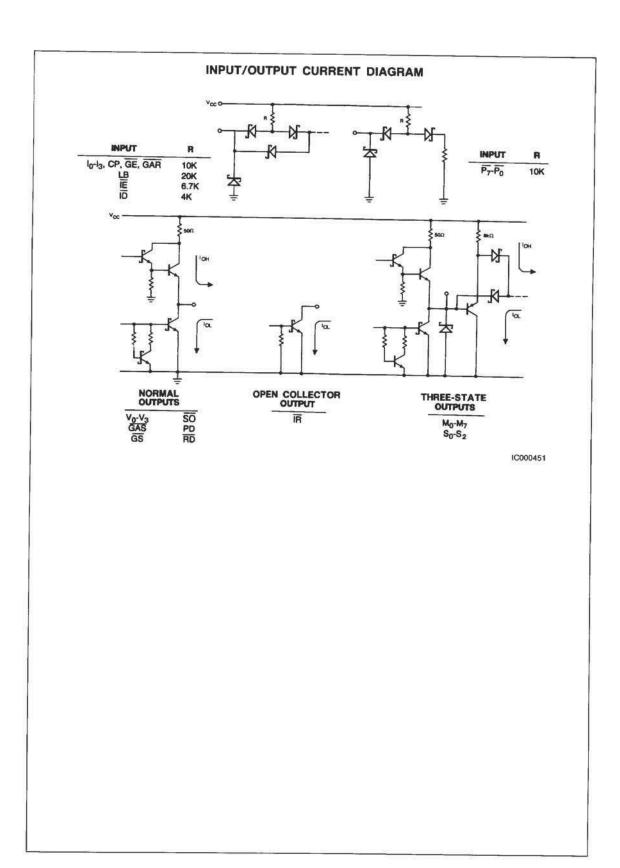

#### P<sub>7-0</sub> Interrupt Request (Inputs)

Active LOW level or latched pulses.

#### LB Latch Bypass (Input)

When HIGH, the interrupt latches are transparent. When LOW, the latches are negative pulse catchers.

#### M<sub>7-0</sub> Mask Bus (Input/Ouput)

Bidirectional bus to load or read interrupt mask.

#### 13-0 Microinstruction Inputs (Input)

#### IE Instruction Enable (Input)

The microinstruction is executed if  $\overline{\mathsf{IE}}$  is LOW and is ignored if  $\overline{\mathsf{IE}}$  is HIGH.

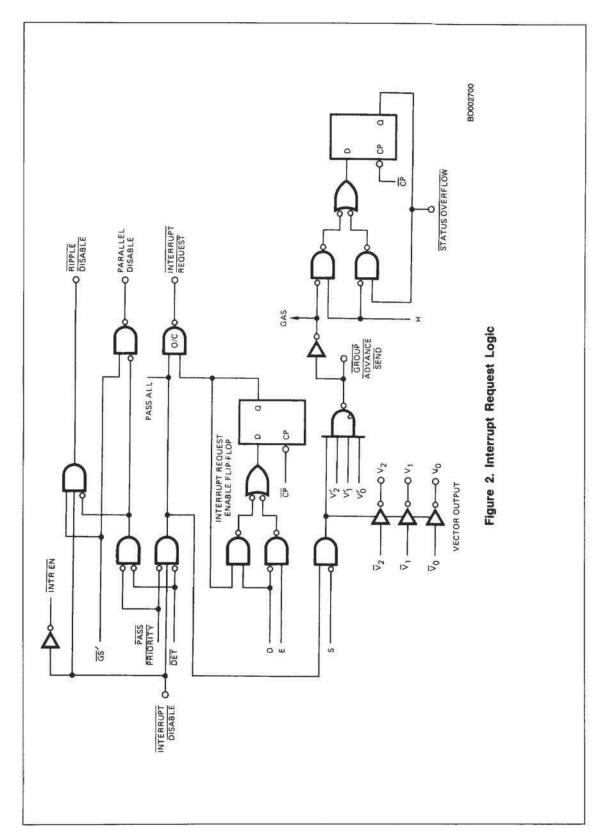

#### GAR Group Advance Receive (Input)

During a Master Clear or Read Vector microinstruction, this input signal is used to load the Lowest Group Enable flipflop. GAR of the lowest priority group must be LOW.

#### GAS Group Advance Send (Output)

During a Read Vector microinstruction, this output signal is LOW when the highest priority vector of the group is being read. GAS should be connected to GAR of the next higher group in a cascaded system.

#### RD Ripple Disable (Output)

This output is LOW when Interrupt Disable (ID) is LOW, or the Lowest Group Enabled is LOW, or an Interrupt Request (IR) is generated in the group. This output is connected to the Interrupt Disable (ID) input of the next lower group.

#### PD Parallel Disable (Output)

This output is HIGH when the Lowest Group Enabled flipflop is LOW or an interrupt is generated in the group.

#### GS Group Signal (Output)

The output of the Lowest Group Enabled flipflop.

#### GE Group Enable (Input)

Input to the Lowest Group Enabled flipflop.

#### SO Status Overflow (Output)

This output signal is LOW after the highest priority vector of the group has been read. It stays LOW until a Master Clear or Load Status microinstruction is executed. SO of the highest priority group should be connected to the Interrupt Disable (ID) of the same group. SO signals of lower priority groups are unused.

#### S2-0 Status Bus (Input/Output)

Bidirectional bus to load or read the status register.

#### ID Interrupt Disable (Input)

When LOW, this input inhibits the Interrupt Request (IR) output and generates a Ripple Disable (RD) output.

#### IR Interrupt Request (Output)

Open collector output which is active LOW.

#### V2-0 Vector Output (Output)

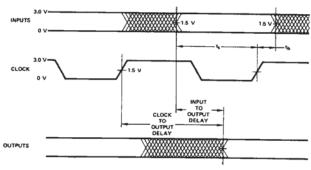

CP Clock Input (Input)

#### **FUNCTIONAL DESCRIPTION**

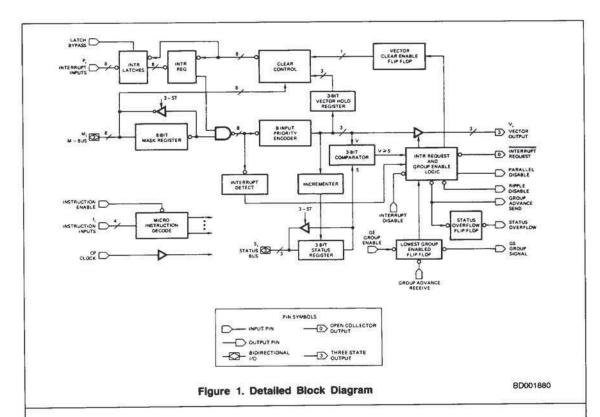

The Microinstruction Decode circuitry decodes the Interrupt Microinstructions and generates required control signals for the chip.

The Interrupt Register holds the Interrupt Inputs and is an eight-bit, edge-triggered register which is set on the rising edge of the Clock (CP) signal.

The Interrupt latches are set/reset-type latches. When the Latch Bypass (LB) signal is LOW, the latches are enabled and act as negative pulse catchers on the inputs to the Interrupt Register. When the Latch Bypass (LB) signal is HIGH, the Interrupt latches are transparent.

The Mask Register holds the eight mask bits associated with the eight interrupt levels. The register may be loaded from or read to the M Bus. Also, the entire register or individual mask bits may be set or cleared.

The Interrupt Detect circuitry detects the presence of any unmasked Interrupt  $(\overline{P}_{0-7})$  Input. The eight-input Priority Encoder determines the highest priority, non-masked Interrupt Input and forms a binary coded Interrupt Vector. Following a Vector Read, the three-bit Vector Hold Register holds the binary coded interrupt vector. This stored vector is used for clearing interrupts.

The three-bit Status Register holds the status bits and may be loaded from or read to the S Bus. During a Vector Read, the Incrementer increments the Interrupt Vector by one, and the result is clocked into the Status Register. Thus the Status

Register always points to the lowest level at which an interrupt will be accepted.

The three-bit Comparator compares the Interrupt Vector with the contents of the Status Register and indicates if the Interrupt Vector is greater than or equal to the contents of the Status Register.

The Lowest Group Enabled Flip-Flop is used when a number of Am2914's are cascaded. In a cascaded system, only one Lowest Group Enabled Flip-Flop is LOW at a time. It indicates the eight interrupt group, which contains the lowest priority interrupt level which will be accepted and is used to form the higher order status bits.

The Interrupt Request and Group Enable logic contain various gating to generate the Interrupt Request ( $\overline{\text{IR}}$ ), Parallel Disable (PD), Ripple Disable ( $\overline{\text{RD}}$ ), and Group Advance Send ( $\overline{\text{GAS}}$ ) signals.

The Status Overflow (SO) signal is used to disable all interrupts. It indicates the highest priority Interrupt Vector has been read and the Status Register has overflowed.

The Clear Control logic generates the eight individual clear signals for the bits in the Interrupt Latches and Register. The Vector Clear Enable Flip-Flop indicates if the last vector read was from this group. When it is set, it enables the Clear Control Logic.

The clock (CP) signal is used to clock the Interrupt Register, Mask Register, Status Register, Vector Hold Register, and the Lowest Group Enabled, Vector Clear Enable and Status Overflow Flip-Flops, all on the clock LOW-to-HIGH transition.

TABLE 1.

MICROINSTRUCTION SET FOR Am2914 PRIORITY INTERRUPT CIRCUIT

| 13121110 | Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Instruction                                                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Mask Register Functions                                                                                                                         |

| 1110     | LDM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Load mask register from M bus                                                                                                                   |

| 0111     | RDM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Read mask register to M bus                                                                                                                     |

| 1100     | CLRM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Clear mask register (enables all priorities)                                                                                                    |

| 1000     | SETM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Set mask register (inhibits all interrupts)                                                                                                     |

| 1010     | BCLRM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit clear mask register from M bus *Note 1                                                                                                      |

| 1011     | BSETM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit set mask register from M bus *Note 1                                                                                                        |

|          | Viscondension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Status Register Functions                                                                                                                       |

| 1001     | LDSTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Load status register from S bus and LGE flip-                                                                                                   |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | flop from GE input                                                                                                                              |

| 0110     | RDSTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Read status register to S bus                                                                                                                   |

|          | E14575 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Interrupt Request Control                                                                                                                       |

| 1111     | ENIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Enable interrupt request                                                                                                                        |

| 1101     | DISIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Disable interrupt request                                                                                                                       |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Vectored Output                                                                                                                                 |

| 0101     | RDVC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Read vector output to V outputs, load V + 1<br>into status register, load V into vector hold<br>register and set vector clear enable flip-flop. |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Priority Interrupt Register Clear                                                                                                               |

| 0001     | CLRIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Clear all interrupts                                                                                                                            |

| 0011     | CLRMR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Clear interrupts from mask register data (uses                                                                                                  |

| 9911     | ( <del>1000</del> ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 ( 1000 | the M bus)                                                                                                                                      |

| 0010     | CLRMB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Clear interrupts from M bus data *Note 1                                                                                                        |

| 0100     | CLRVC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Clear the individual interrupt associated with                                                                                                  |

|          | C diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | the last vector read                                                                                                                            |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Master Clear                                                                                                                                    |

| 0000     | MCLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Clear all interrupts, clear mask register, clea<br>status register, clear LGE flip-flop, enable<br>interrupt request.                           |

Note 1: SET/CLEAR those bits which have corresponding M-Bus bits equal to one.

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65 to              | +150°C  |

|---------------------------------------|---------|

| (Ambient) Temperature Under Bias55 to | +110°C  |

| Supply Voltage to Ground Potential    |         |

| Continuous0.5 V to                    | +7.0 V  |

| DC Voltage Applied to Outputs For     |         |

| High Output State0.5 V to +1          | CC Max. |

| DC Input Voltage0.5 V to              | +5.5 V  |

| DC Output Current, Into Outputs       | 30 mA   |

| DC Input Current30 mA to              |         |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

| Commercial (C) Devices     |                      |

|----------------------------|----------------------|

| Temperature TA             | 0 to +70°C           |

| Supply Voltage             | . +4.75 V to +5.25 V |

| Military (M) Devices       |                      |

| Temperature T <sub>C</sub> | 55 to +125°C         |

| Supply Voltage             | +4.5 V to +5.5 V     |

Operating ranges define those limits over which the functionality of the device is guaranteed.

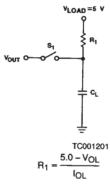

## DC CHARACTERISTICS over operating range unless otherwise specified; Included in Group A, Subgroup 1, 2, 3 Tests unless otherwise noted

| Parameters                             | Description                              | Т                                                                              | est Condition     | s (Note 1)                   | Min. | Max.  | Unit      |

|----------------------------------------|------------------------------------------|--------------------------------------------------------------------------------|-------------------|------------------------------|------|-------|-----------|

| ************************************** |                                          | V <sub>CC</sub> = Min.,                                                        | M                 | L, I <sub>OH</sub> = -1.0 mA | 2.4  |       | 1,000,000 |

| Voн                                    | Output HIGH Voltage                      | VIN = VIH or VI                                                                |                   | OM'L, IOH = -2.6 mA          | 2.4  |       | Volt      |

| ICEX                                   | Output Leakage Current<br>for IR Output  | V <sub>CC</sub> = Min., V <sub>O</sub>                                         | ≖ 5.5 V           |                              |      | 250   | μА        |

|                                        |                                          | 100 500                                                                        | lo                | L = 4.0 mA                   |      | 0.4   |           |

| VOL                                    | Output LOW Voltage                       | V <sub>CC</sub> = Min.,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>I</sub> | lo                | L = 8.0 mA                   |      | 0.45  | Volt      |

| 334                                    | 2 2                                      | 1 000 20 00                                                                    | 10                | L = 12.0 mA                  |      | 0.5   | 53,633    |

| VIH                                    | Input HIGH Level                         | Guaranteed inp<br>for all inputs                                               | ut logical HIGH v | roltage                      | 2.0  |       | Volt      |

| V <sub>IL</sub>                        | Input LOW Level                          | Guaranteed inp<br>for all inputs                                               | ut logical LOW v  | oltage                       |      | 0.8   | Volt      |

| VI                                     | Input Clamp Voitage                      | V <sub>CC</sub> = Min., I <sub>IN</sub>                                        | = -18 mA          |                              |      | -1.5  | Valt      |

| ·                                      |                                          |                                                                                | Mo                | )-7                          |      | -0.15 |           |

|                                        |                                          | V <sub>CC</sub> = Max.,<br>V <sub>IN</sub> = 0.4 V                             |                   | -2                           |      | -0.1  | 1         |

| 2                                      | TO TOTAL SECTION OF                      |                                                                                |                   | B.                           |      | -0.4  | 1         |

| lı.                                    | Input LOW Current                        |                                                                                |                   | Ď.                           |      | -2.0  | mA        |

|                                        |                                          |                                                                                |                   |                              |      | -1.2  | 1         |

|                                        |                                          |                                                                                |                   | Others                       |      | -0.8  | 1         |

|                                        |                                          | $V_{CC} = Max.$ , $M_{0-7}$ $S_{0-2}$ $GE$ , $G$                               |                   | 1-7                          |      | 150   |           |