# AM29821, AM29823, AM29825

# High Performance Bus Interface Registers

The AM29821/823/825 bus interface registers are designed to eliminate the extra packages required to buffer existing registers and provide extra data width for wider address/data paths or buses carrying parity. The AM29821 is a buffered, 10-bit wide version of the popular '374/'534 functions. The AM29823 is a 9-bit wide buffered register with Clock Enable ( $\overline{\text{EN}}$ ) and Clear ( $\overline{\text{CLR}}$ ) - ideal for parity bus interfacing in high performance microprogrammed systems. The AM29825 is an 8-bit buffered register with all the '823 controls plus multiple enables ( $\overline{\text{OE}_1}$ ,  $\overline{\text{OE}_2}$ ,  $\overline{\text{OE}_3}$ ) to allow multiuser control of the interface, e.g.,  $\overline{\text{CS}}$ , DMA, and  $\overline{\text{RD/WR}}$ . It is ideal for use as an output port requiring high  $I_{\text{OL}}/I_{\text{OH}}$ .

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# Advanced Micro Devices

# Am29821/823/825

## **High Performance Bus Interface Registers**

## DISTINCTIVE CHARACTERISTICS

- High-speed parallel registers with positive edge-triggered D-type flip-flops

- Noninverting CP-Y tpD = 7.5 ns typ

- Inverting CP-Y tpb = 7.5 ns typ

- Buffered common Clock Enable (EN)

- Buffered common asynchronous Clear input (CLR)

- Three-state outputs glitch free during power-up and down

- Outputs have Schottky clamp to ground

- 48 mA Commercial lou

- Low input/output capacitance

- 6 pF inputs (typical)

- 8 pF outputs (typical)

- Metastable "Hardened" Registers

- lon specified at 2.0 V and 2.4 V

- 24-pin 0.3" space saving package

- IMOX<sup>TM</sup> high performance <u>IM</u>planted <u>OX</u>ide isolated process

### **GENERAL DESCRIPTION**

The Am29821/823/825 bus interface registers are designed to eliminate the extra packages required to buffer existing registers and provide extra data width for wider address/data paths or buses carrying parity. The Am29821 is a buffered, 10-bit wide version of the popular '374/'534 functions. The Am29823 is a 9-bit wide buffered register with Clock Enable ( $\overline{\text{EN}}$ ) and Clear ( $\overline{\text{CLR}}$ ) – ideal for parity bus interfacing in high performance microprogrammed systems. The Am29825 is an 8-bit buffered register with all the '823 controls plus mul-

tiple enables ( $\overline{OE}_1$ ,  $\overline{OE}_2$ ,  $\overline{OE}_3$ ) to allow multiuser control of the interface, e.g.,  $\overline{CS}$ , DMA, and RD/ $\overline{WR}$ . It is ideal for use as an output port requiring high lot/loh.

All of the Am29800 high performance interface family are designed for high capacitance load drive capability while providing low capacitance bus loading at both inputs and outputs. All inputs are Schottly diode inputs, and all outputs are designed for low capacitance bus loading in the high impedance state.

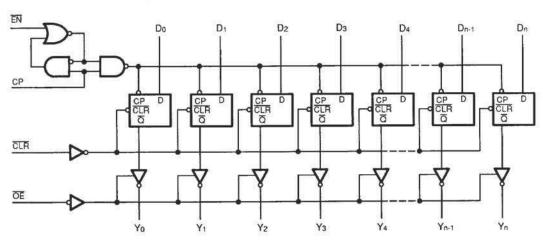

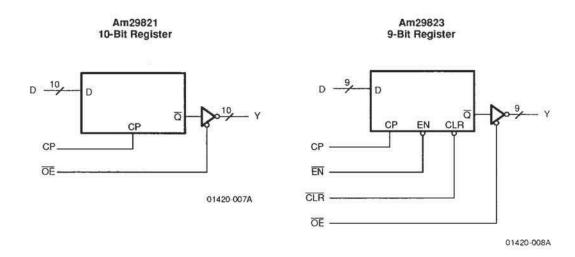

#### BLOCK DIAGRAMS Am29821

01420-001A

IMOX is a trademark of Advanced Micro Devices, Inc.

Publication# 01420

Anenumencu

Issue Date: December 1990

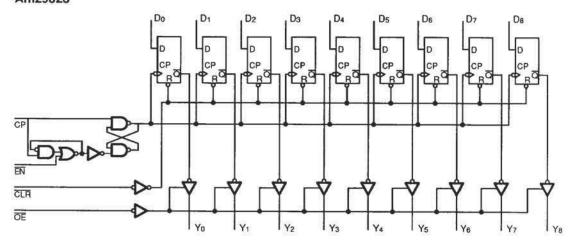

## BLOCK DIAGRAMS (Continued) Am29823

01420-002A

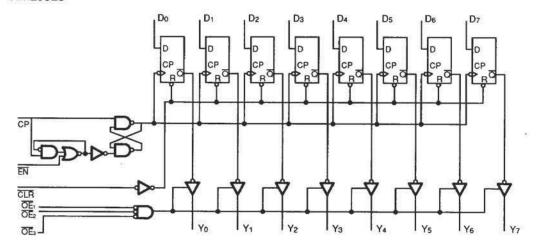

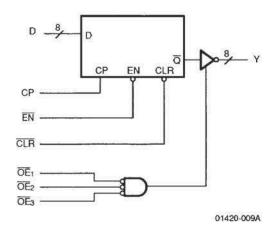

## Am29825

01420-003A

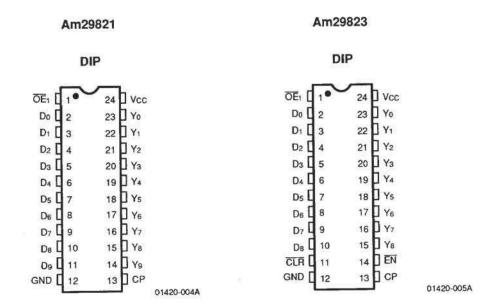

# CONNECTION DIAGRAMS Top View

## Am29825

DIP

## LOGIC SYMBOLS

## Am29825 8-Bit Register

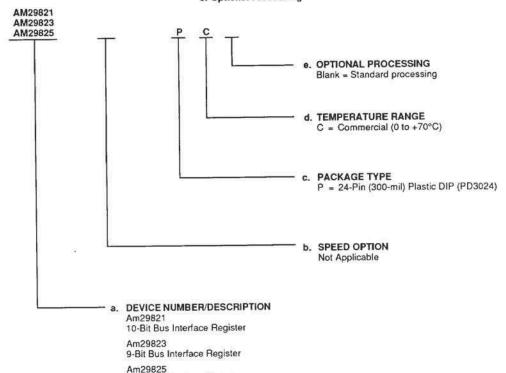

## ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of:

a. Device Number

- a. Device Number

b. Speed Option (if applicable)

c. Package Type

d. Temperature Range

e. Optional Processing

| Valid Com | binations |

|-----------|-----------|

| AM29821   |           |

| AM29823   | PC        |

| AM29825   |           |

8-Bit Bus Interface Register

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

## PIN DESCRIPTION

D

The D flip-flop data inputs.

#### CLR

For both inverting and noninverting register, when the clear input is LOW and  $\overline{OE}$  is LOW, the Q<sub>i</sub> outputs are LOW. When the clear input is HIGH, data can be entered into the register.

#### CP

Clock Pulse for the Register; enters data into the register on the LOW-to-HIGH transition.

#### Y

The register three-state outputs.

#### Note:

The Am29823 and Am29825 registers achieve short throughput delay and setup time and reduced power consumption by

means of a clock gating and latching circuit. This circuit is sensitive to very short (<3 ns) HIGH-to-LOW-to-HIGH going spikes

on EN while CP is HIGH. The designer should be aware of this and avoid the use of decoders or other potentially glitching

devices in the EN logic.</li>

## **FUNCTION TABLE**

| Inputs |     |    | Internal | Outputs  | 1  |    |            |  |

|--------|-----|----|----------|----------|----|----|------------|--|

| ŌĒ     | CLR | ĒN | Di       | СР       | Qi | Yi | Function   |  |

| H      | Х   | L  | L        | 1        |    | 7  | 1 4.101.01 |  |

| Н      | X   | L  | н        | î        | н  | Z  | Hi-Z       |  |

| Н      | L   | Х  | Х        | Х        | L  | Z  |            |  |

| L      | L   | Х  | ×        | X        | L  | L  | Clear      |  |

| Н      | Н   | Н  | X        | Х        | NC | Z  |            |  |

| L      | Н   | Н  | X        | X        | NC | NC | Hold       |  |

| Н      | н   | L  | L        | 1        | L  | Z  |            |  |

| Н      | н   | L  | н        | <b>↑</b> | н  | 7  | Load       |  |

| L      | н   | L  | L        | 1        | L  | Ē. |            |  |

| L      | н   | L  | н        | 1        | н  | н  |            |  |

H = HIGH

L = LOW

X = Don't Care

NC = No Change

1 = LOW-to-HIGH Transition

Z = High Impedance

#### EN

Clock Enable. When the clock enable is LOW, data on the Di input is transferred to the Qi output on the LOW-to-HIGH clock transition. When the clock enable is HIGH, the Qi outputs do not change state, regardless of the data or clock input transitions. (Note 1.)

## OE

Output Control. When the  $\overline{OE}$  input is HIGH, the  $Y_i$  outputs are in the high impedance state. When the  $\overline{OE}$  input is LOW, the TRUE register data is present at the Y outputs.

## **ABSOLUTE MAXIMUM RATINGS**

Storage Temperature -65°C to +150°C

Ambient Temperature with

-55°C to +125°C Power Applied

Supply Voltage to Ground

DC Input Current

-0.5 V to +7.0 V Potential Continuous

DC Voltage Applied to Outputs

-0.5 V to +5.5 V for High Output State -0.5 V to +5.5 V DC Input Voltage

100 mA DC Output Current, Into Outputs

Stresses above those listed under Absolute Maximum Rat-

ings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **OPERATING RANGES**

Commercial (C) Devices

0°C to +70°C Ambient Temperature, (TA) 5.0 V ± 10% Supply Voltage, (Vcc) 4.5 V to 5.5 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over operating ranges unless otherwise specified

-30 mA to +5.0 mA

| Parameter<br>Symbol         | Parameter Description                    | Test Conditions                                      |                          | Min. | Max.      | Unit |

|-----------------------------|------------------------------------------|------------------------------------------------------|--------------------------|------|-----------|------|

| Voн                         | Output HIGH Voltage                      | Vcc = 4.5 V                                          | Iон = −15 mA             | 2.4  |           |      |

|                             |                                          | VIN = VIH OF VIL                                     | I <sub>OH</sub> = −24 mA | 2.0  |           | V    |

| Vol                         | Output LOW Voltage                       | Vcc = 4.5 V<br>Vin = ViH or ViL                      | IoL = 48 mA              |      | 0.5       | V    |

| VIH                         | Input HIGH Level                         | Guaranteed input logical HIGH voltage for all inputs |                          | 2.0  |           | ٧    |

| VIL                         | Input LOW Level                          | Guaranteed input logical LOW voltage for all inputs  |                          |      | 0.8       | V    |

| Vı                          | Input Clamp Voltage                      | Vcc = 4.5 V, lin = -18 mA                            |                          |      | -1.2      | V    |

| IIL Input LOW               | Input LOW Current                        | Vcc = 5.5 V,<br>ViN = 0.4 V                          | Data, CLR                |      | -1.0      | m/   |

|                             | December 1 September 1                   |                                                      | OE, EN, CP               |      | -2.0      | 111/ |

| lін                         | Input HIGH Current                       | Vcc = 5.5 V, Vin = 2.7 V                             |                          |      | 50        | μА   |

| li                          | Input HIGH Current                       | Vcc = 5.5 V, Vin = 5.5 V                             |                          |      | 1.0       | mA   |

| loz                         | Output Off-State (Hi-Z)                  | 100 - 0.0 1                                          | Vo = 0.4 V               |      | -50<br>50 | μА   |

| 9550                        | Output Current                           |                                                      | Vo = 2.4 V               |      |           | μ,   |

| Isc                         | Output Short Circuit<br>Current (Note 1) | V <sub>CC</sub> = 5.5 V                              |                          | -75  | -250      | mA   |

| lcc Supply Current (Note 2) | Supply Current                           | Vcc = 5.5 V                                          | Over Temperature Range   |      | 140       | mA   |

|                             | (Note 2)                                 | Outputs Open  EN = LOW                               | +70°C                    |      | 130       | mA   |

#### Notes:

- 1. Not more than one output should be shorted at a time, and duration of the short-circuit should not exceed one second.

- 2. Clock input, CP, is HIGH after clocking in data to produce outputs = LOW.

## AMD 🎵

# SWITCHING CHARACTERISTICS (TA = 25°C, Vcc = 5.0 V)

| Parameter<br>Symbol | Parameter Description                                |                             | Test Conditions<br>(Note 1)               | Min. | Тур. | Max. | Unit |

|---------------------|------------------------------------------------------|-----------------------------|-------------------------------------------|------|------|------|------|

| <b>TPLH</b>         |                                                      |                             | W                                         | 3.5  |      | 8.5  | ns   |

| <b>TPHL</b>         | Propagation Delay Clock to Y <sub>1</sub> (OE = LOW) | C <sub>L</sub> = 50 pF      | 3.5                                       |      | 10.5 | ns   |      |

| <b>t</b> PLH        |                                                      | C <sub>L</sub> = 300 pF     |                                           |      | 14   | ns   |      |

| <b>TPHL</b>         |                                                      |                             |                                           |      | 18   | ns   |      |

| ts                  | Data to CP Setup Time                                |                             |                                           | 2.0  | 0    |      | ns   |

| tн                  | Data to CP Hold Time                                 |                             |                                           | 2.0  | 0.5  | - "  | ns   |

| ts                  | Enable (EN ) to CP Se                                | etup Time                   |                                           | 3.0  | 1.5  |      | ns   |

| ts                  | Enable (EN _ ) to CP Se                              | ble (EN 1) to CP Setup Time |                                           | 3.0  | 1.5  |      | ns   |

| tн                  | Enable (EN) Hold Time                                |                             |                                           | 0    | -1.5 | 9    | ns   |

| <b>TPHL</b>         | Propagation Delay, Clear                             | to Yi                       |                                           |      | 12.9 | 15.0 | ns   |

| ts                  | Clear Recovery (CLR_F)                               | Time                        |                                           | 5.0  | 1.1  |      | ns   |

| tpwn                | Clock Pulse Width HIGH                               |                             | 5.0                                       | 3.5  |      | ns   |      |

| tpwL                | Clock Fulse Width                                    | LOW                         | $C_L = 50 pF$                             | 5.0  | 3.0  |      | ns   |

| tpwL                | Clear (CLR = LOW) Pulse                              | Width                       | SARAH BASKATA                             | 5.0  | 4.0  | 2.1  | ns   |

| tzн                 |                                                      |                             | 0 000-5                                   |      |      | 17   | ns   |

| tzL                 | Output Enable Time OE _ to Yi                        |                             | C <sub>L</sub> = 300 pF                   |      |      | 21   | ns   |

| tzн                 |                                                      |                             |                                           |      | 11.5 | 12   | ns   |

| tzı                 |                                                      |                             | C <sub>L</sub> = 50 pF                    |      | 11.0 | 12   | ns   |

| tHZ                 | Output Disable Time OE _ 10 Yi                       |                             | CL = 50 pF                                |      |      | 9    | ns   |

| tız                 |                                                      |                             |                                           |      |      | 9    | ns   |

| tHZ                 |                                                      |                             | 790 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |      | 5.2  | 8    | ns   |

| tız                 |                                                      |                             | $C_L = 5 pF$                              |      | 5.5  | 8    | ns   |

## Note:

<sup>1.</sup> See test circuit and waveforms (Chapter 2).

## SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                                                                 |          | Test Conditions (Note 1) | Min. | Max. | Unit |

|---------------------|---------------------------------------------------------------------------------------|----------|--------------------------|------|------|------|

| <b>t</b> PLH        | Propagation Delay Clock to Yi (OE = LOW)  Data to CP Setup Time  Data to CP Hold Time |          | C <sub>L</sub> = 50 pF   | 3.5  | 10   | ns   |

| t <sub>PHL</sub>    |                                                                                       |          |                          | 3.5  | 12   | ns   |

| t <sub>PLH</sub>    |                                                                                       |          | C <sub>L</sub> = 300 pF  |      | 16   | ns   |

| t <sub>PHL</sub>    |                                                                                       |          |                          |      | 20   | ns   |

| ts                  |                                                                                       |          |                          | 4    |      | ns   |

| tн                  |                                                                                       |          |                          | 2    |      | ns   |

| ts                  | Enable (EN 1 ) to CP Se                                                               | tup Time | 0. 50 25                 | 4    |      | ns   |

| ts                  | Enable (EN _ ) to CP Set                                                              | tup Time |                          | 4    |      | ns   |

| tн                  | Enable (EN) Hold Time                                                                 |          |                          | 2    |      | ns   |

| t <sub>PHL</sub>    | Propagation Delay, Clear to Yi Clear Recovery (CLR _ T) Time                          |          | C <sub>L</sub> = 50 pF   |      | 20   | ns   |

| ts                  |                                                                                       |          |                          | 7    |      | ns   |

| tpwh                | Clock Pulse Width                                                                     | HIGH     |                          | 7    |      | ns   |

| t <sub>PWL</sub>    |                                                                                       | LOW      |                          | 7    |      | ns   |

| tpwL                | Clear (CLR = LOW) Pulse Width                                                         |          |                          | 7    |      | ns   |

| tzн                 | Output Enable Time $\overline{OE}$ to Y <sub>i</sub>                                  |          | C <sub>L</sub> = 300 pF  |      | 20   | ns   |

| tzL                 |                                                                                       |          |                          |      | 23   | ns   |

| tzн                 |                                                                                       |          | C <sub>L</sub> = 50 pF   |      | 14   | ns   |

| tzL                 |                                                                                       |          |                          |      | 14   | ns   |

| tHZ                 | Output Disable Time OE _ to Yi                                                        |          | C <sub>L</sub> = 50 pF   |      | 16   | ns   |

| tız                 |                                                                                       |          |                          |      | 12   | ns   |

| tHZ                 |                                                                                       |          | C <sub>L</sub> = 5 pF    |      | 9    | ns   |

| tLZ                 |                                                                                       |          |                          |      | 9    | ns   |

## Note:

<sup>1.</sup> See test circuit and waveforms (Chapter 2).

# INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

## PD3024

## CD3024

\*For reference only.

1954 6 - 03

112

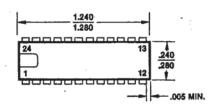

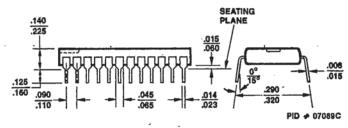

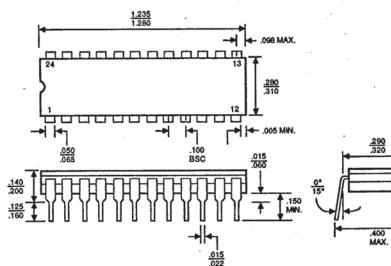

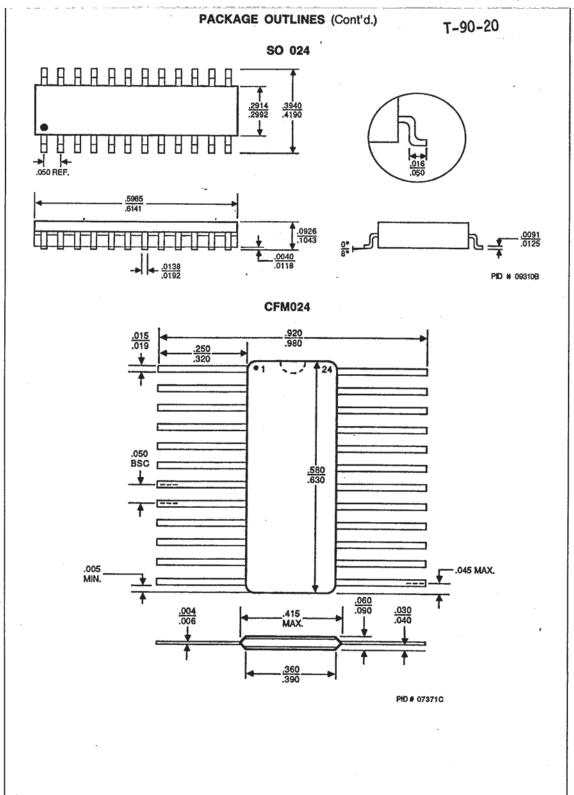

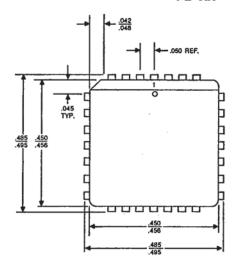

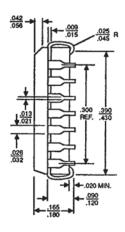

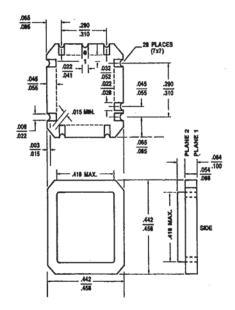

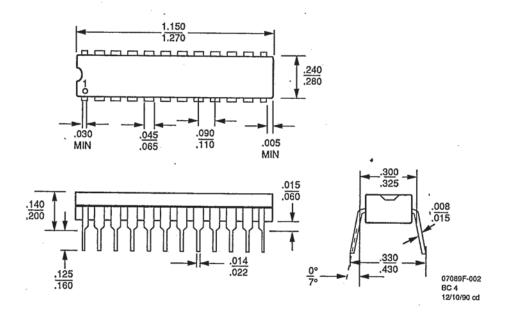

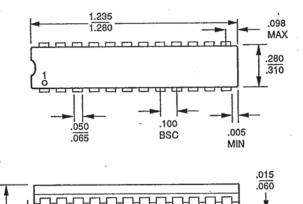

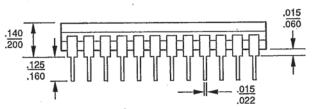

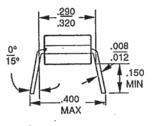

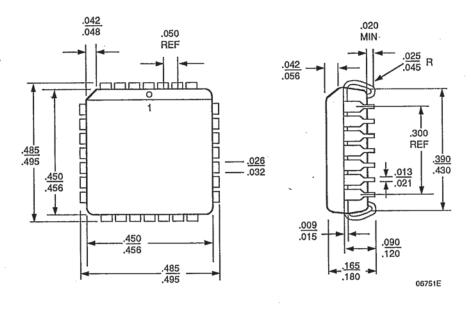

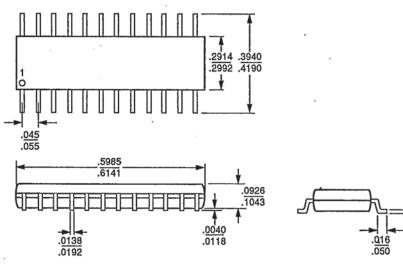

## PACKAGE OUTLINES (Cont'd.)

T-90-20

PL 028

PID # 06751E

**CL 028**

PHD # 06595D

Advanced Micro Devices reserves the right to make changes in its product without notice in order to improve design or performance characteristics. The performance characteristics listed in this document are guaranteed by specific tests, correlated testing, guard banding, design and other practices common to the industry. For specific testing details, contact your local AMD sales representative. The company assumes no responsibility for the use of any circuits described herein.

ADVANCED MICRO DEVICES 901 Thompson Pl., P.O. Box 3453, Sunnyvale, CA 94088, USA TEL: (408) 732-2400 • TWX: 910-339-9280 • TELEX: 34-6306 • TOLL FREE: (800) 538-8450

© 1988 Advanced Micro Devices, Inc. Printed in U.S.A. AIS-WCP-20M-01/88-0

**Bus Interface Products**

PD3024 24-Pin 300-mil Plastic SKINNYDIP

Note:

For reference only. All dimensions measured in inches. BSC is an ANSI standard for Basic Space Centering.

T-90-20

## CD3024 24-Pin 300-mil Ceramic SKINNYDIP

06850C

PL 028 28-Pin Plastic Leaded Chip Carrier

**Bus Interface Products**

SO 024 24-Pin Plastic Small Outline Package

T-90-20

6–5