## AM82S62

## Nine-Input Parity Checker/Generator

The AM82S62 is a 9-bit parity generator/parity checker with both an ODD parity output and an EVEN parity output. The device can be used to detect errors in data transmission or data retrieval systems as well as to generate this parity check bit.

The AM82S62 features one special high-speed input ( $P_9$ ) to facilitate expansion. The propagation delay to the outputs through this path is considerably reduced when compared to the  $P_1$  through  $P_8$  paths. This short delay path allows parity checkers/generators of larger size than 9-bits to be built with a minimum of additional delay.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# Am82S62

## Nine-Input Parity Checker/Generator

### **Distinctive Characteristics**

- ODD/EVEN parity outputs

- Inhibit input to disable both outputs

- High-speed expansion input Po

- PNP inputs

- Advanced Schottky technology

- 100% reliability assurance testing in compliance wi MIL-STD-883.

### **FUNCTIONAL DESCRIPTION**

The Am82S62 is a 9-bit parity generator/parity checker with both an ODD parity output and an EVEN parity output. The device can be used to detect errors in data transmission or data retrieval systems as well as to generate this parity check bit.

The Am82S62 features one special high-speed input (Pg) to facilitate expansion. The propagation delay to the outputs through this path is considerably reduced when compared to the P<sub>1</sub> through P<sub>8</sub> paths. This short delay path allows parity checkers/generators of larger size than 9-bits to be built with a minimum of additional delay.

The device is built using advanced Schottky technology and incorporates PNP input transistors to reduce input loading to 0.4 STTL unit loads. The EVEN output is one gate propagation delay time shorter than the ODD output.

### LOGIC SYMBOL

V<sub>CC</sub> = Pin 14 GND = Pin 7

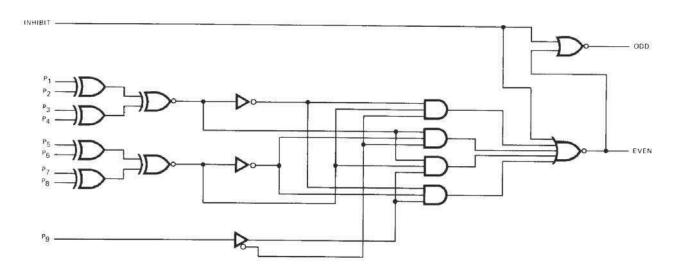

### LOGIC DIAGRAM

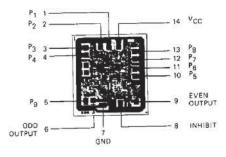

#### ORDERING INFORMATION CONNECTION DIAGRAM Top View □ Vcc Package Temperature Order Type Range Number 0°C to +75°C Molded DIP N82S62A □ P6 4 Am82S62 11 0°C to +75°C Hermetic DIP N82S62F 0°C to +75°C Dice N82S62X 10 P5 P9 [ -55°C to +125°C Hermetic DIP S82S62F ODD DEVEN OUTPUT -55°C to +125°C Dice S82S62X INHIBIT Note: Pin 1 is marked for orientation.

## **MAXIMUM RATINGS** (Above which the useful life may be impaired)

| -65°C to +150°C                |

|--------------------------------|

| -05 C 10 + 130 C               |

| -55°C to +125°C                |

| -0.5V to +7V                   |

| -0.5V to +V <sub>CC</sub> max. |

|                                |

| -0.5V to +5.5V                 |

| 30mA                           |

| -30mA to +5.0mA                |

|                                |

|                                |

# ELECTRICAL CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (Unless otherwise noted)

N82S62

$T_A = 0^{\circ}C$  to  $+75^{\circ}C$

V<sub>CC</sub> = 5.0V ±5%

MIN. = 4.75V

MAX. = 5.25V

| 82S62 $T_A = -55^{\circ} \text{C to } +125^{\circ} \text{C}$ arameters Description |                                          | Test Conditions (Note                                                                                  | 1)     | Min. | Typ.<br>(Note 2) | Max.  | Units |

|------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------|--------|------|------------------|-------|-------|

|                                                                                    |                                          | V <sub>CC</sub> = MIN., 1 <sub>OH</sub> = -1mA                                                         | S82    | 2.5  |                  |       | Volts |

| <b>v</b> OH                                                                        | Output HIGH Voltage                      | VIN = VIH or VIL                                                                                       | N82    | 2.7  |                  |       | Voits |

| V <sub>OL</sub>                                                                    | Output LOW Voltage                       | V <sub>CC</sub> = MIN., I <sub>OL</sub> = 20mA<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> |        |      | 0.5              | Volts |       |

| VIH                                                                                | Input HIGH Level                         | Guaranteed input logical HIGH voltage for all inputs                                                   |        | 2.0  |                  |       | Volts |

| VIL                                                                                | Input LOW Level                          | Guaranteed input logical LOW voltage for all inputs                                                    |        |      |                  | 8.0   | Volts |

| V.                                                                                 | Input Clamp Voltage                      | VCC = MIN., IIN = -18mA                                                                                |        |      |                  | -1.2  | Volts |

| V <sub>1</sub>                                                                     | Input clamp voltage                      | T po                                                                                                   |        |      |                  | -0.4  | mA.   |

| IL<br>(Note 3)                                                                     | Input LOW Current                        | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 0.5V                                                         | Others |      |                  | -0.8  | -     |

| I <sub>IH</sub><br>(Note 3)                                                        | Input HIGH Current                       | V <sub>CC</sub> = MAX., V <sub>IN</sub> = 4.5V                                                         |        |      |                  | 10    | μА    |

| I <sub>I</sub>                                                                     | Input HIGH Current                       | VCC = MAX., VIN = 5.5V                                                                                 |        |      |                  | 1.0   | mA    |

| Isc                                                                                | Output Short Circuit Current<br>(Note 4) | V <sub>CC</sub> = MAX., V <sub>OUT</sub> = 0.0V                                                        |        | -40  |                  | -100  | mA    |

| Icc                                                                                | Power Supply Current                     | VCC = MAX. (Note 5)                                                                                    |        |      | 67               | mA    |       |

For conditions shown as MIN. or MAX., use the appropriate value specified under Electrical Characteristics for the applicable device type.

Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

Actual input currents = Unit Load Current x Input Load Factor (See Loading Rules).

Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

5. P1 through P9 grounded; inhibit at 4.5V; outputs open.

# Switching Characteristics ( $T_A = +25^{\circ}C$ )

| rameters Description |                                                      | Test Conditions                                     | Min. | Тур.         | Max. | Units |

|----------------------|------------------------------------------------------|-----------------------------------------------------|------|--------------|------|-------|

| tPLH                 | P <sub>1</sub> through P <sub>8</sub> to Even Output | rough Po to Even Output                             |      |              | 23   | ns    |

| tPHL                 | 1 1 timodan 8 to                                     |                                                     |      | <del> </del> |      | 2000  |

| tPLH                 | P1 through P8 to Odd Output                          |                                                     | 1    |              | 28   | ns    |

| tPHL                 | .                                                    | $V_{CC} = 5.0V$ , $R_L = 280\Omega$ , $C_L = 15 pF$ |      | -            |      |       |

| tPLH                 | Pg to Even Output                                    |                                                     | ľ    | 1            | 12   | ns    |

| <b>t</b> PHL         |                                                      |                                                     |      | +            |      | ns    |

| tPLH                 | Pg to Odd Output                                     |                                                     |      |              | 18   | ns    |

| tPHL                 | 9                                                    |                                                     | -    |              | 9    | ns    |

| tPLH                 | Inhibit to Even Output                               |                                                     |      |              | 9    | ns    |

| tPHL                 | 160. 37                                              |                                                     | -    |              | -    | ns    |

| tPLH                 | Inhibit to Odd Output                                |                                                     | 1    |              | 9    | ns    |

| <b>tPHL</b>          |                                                      |                                                     |      |              |      |       |

| TR   | ITH          | ITA  | RI |     |

|------|--------------|------|----|-----|

| 1 17 | $\mathbf{o}$ | 1 12 | DL | . = |

| INHIBIT | NUMBER ( | UMBER OF P INPUTS OUT |     |      |

|---------|----------|-----------------------|-----|------|

|         | LOW      | HIGH                  | ODD | EVEN |

| L       | 0        | 9                     | Н   | L    |

| L       | 1        | 8                     | L   | н    |

| L       | 2        | 7                     | н   | L    |

| L       | 3        | 6                     | L   | н    |

| L       | 4        | 5                     | н   | L    |

| L       | 5        | 4                     | L   | н    |

| Ĺ       | 6        | 3                     | н   | L    |

| L       | 7        | 2                     | L   | н    |

| L       | 8        | 1                     | н   | L,   |

| L       | 9        | 0                     | L   | н    |

| н       | ×        | Х                     | Ļ   | L    |

H = HIGH L ≈ LOW

X = Don't Care

### LOADING RULES (In Unit Loads)

|                 |           |                    | Fan-out        |               |  |

|-----------------|-----------|--------------------|----------------|---------------|--|

| Input/Output    | Pin No.'s | Input<br>Unit Load | Output<br>HIGH | Output<br>LOW |  |

| P <sub>1</sub>  | 1         | 0.4                | _              | -             |  |

| P <sub>2</sub>  | 2         | 0.4                | _              | _             |  |

| P3              | 3         | 0.4                | _              | _             |  |

| P <sub>4</sub>  | 4         | 0.4                |                |               |  |

| P <sub>9</sub>  | 5         | 0.2                | _              |               |  |

| ODD             | 6         | _                  | 20             | 10            |  |

| GND             | 7         | _                  | _              | _             |  |

| INHIBIT         | 8         | 0.4                |                |               |  |

| EVEN            | 9         | _                  | 20             | 10            |  |

| P <sub>5</sub>  | 10        | 0.4                | _              | _             |  |

| P <sub>6</sub>  | 11        | 0.4                | _              |               |  |

| P <sub>7</sub>  | 12        | 0.4                |                | _             |  |

| P <sub>8</sub>  | 13        | 0.4                | _              |               |  |

| v <sub>cc</sub> | 14        | _                  |                | _             |  |

|                 |           |                    |                |               |  |

A Schottky TTL Unit Load is defined as  $50\mu A$  measured at 2.7V HIGH and -2.0mA measured at 0.5V LOW.

### **DEFINITION OF FUNCTIONAL TERMS**

P<sub>1</sub> through P<sub>9</sub> The nine inputs to the parity tree.

**INHIBIT** A HIGH on the inhibit input forces both the odd output and even output LOW regardless of the P inputs. When the inhibit is LOW, the odd and even outputs will always be of opposite phase.

ODD The odd parity output of the device. When an odd number of P inputs are at a HIGH level, the odd output will be HIGH.

**EVEN** The even parity output of the device. When an even number of P inputs are at a HIGH level, the even output will be HIGH.

### LOGIC EQUATIONS

ODD Output =  $P_1 \oplus P_2 \oplus P_3 \oplus P_4 \oplus P_5 \oplus P_6 \oplus P_7 \oplus P_8 \oplus P_9$ EVEN Output =  $P_1 \oplus P_2 \oplus P_3 \oplus P_4 \oplus P_5 \oplus P_6 \oplus P_7 \oplus P_8 \oplus P_9$

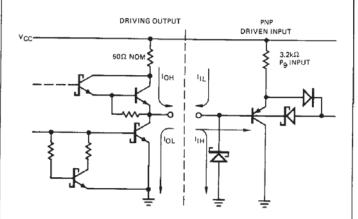

# SCHOTTKY INPUT/OUTPUT CURRENT INTERFACE CONDITIONS

Note: Actual current flow direction shown.

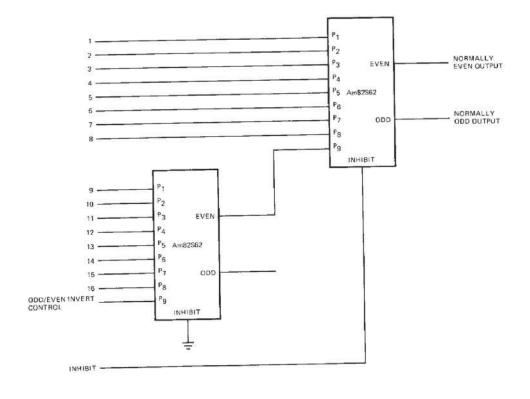

### 16-BIT PARITY GENERATOR WITH INVERT CONTROL

### Metallization and Pad Layout

DIE SIZE 0.067" X 0.072"

12