## CA3081, CA3082

## General Purpose High Current NPN Transistor Arrays

The CA3081 and CA3082 consist of seven high current (to 100mA) silicon NPN transistors on a common monolithic substrate. The CA3081 is connected in a common emitter configuration and the CA3082 is connected in a common collector configuration.

The CA3081 and CA3082 are capable of directly driving seven segment displays, and light emitting diode (LED) displays. These types are also well suited for a variety of other drive applications, including relay control and thyristor firing.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

May 2001

File Number

480.6

## General Purpose High Current NPN Transistor Arrays

CA3081 and CA3082 consist of seven high current (to 100mA) silicon NPN transistors on a common monolithic substrate. The CA3081 is connected in a common emitter configuration and the CA3082 is connected in a common collector configuration.

The CA3081 and CA3082 are capable of directly driving seven segment displays, and light emitting diode (LED) displays. These types are also well suited for a variety of other drive applications, including relay control and thyristor firing.

#### Part Number Information

| PART NUMBER<br>(BRAND) | TEMP.<br>RANGE (°C) | PACKAGE                     | PKG.<br>NO. |

|------------------------|---------------------|-----------------------------|-------------|

| CA3081                 | -55 to 125          | 16 Ld PDIP                  | E16.3       |

| CA3081F                | -55 to 125          | 16 Ld CERDIP                | F16.3       |

| CA3081M<br>(3081)      | -55 to 125          | 16 Ld SOIC                  | M16.15      |

| CA3082                 | -55 to 125          | 16 Ld PDIP                  | E16.3       |

| CA3082M<br>(3082)      | -55 to 125          | 16 Ld SOIC                  | M16.15      |

| CA3082M96<br>(3082)    | -55 to 125          | 16 Ld SOIC Tape<br>and Reel | M16.15      |

#### **Features**

- CA3081 Common Emitter Array

- CA3082 Common Collector Array

- Directly Drive Seven Segment Incandescent Displays and Light Emitting Diode (LED) Display

- 7 Transistors Permit a Wide Range of Applications in Either a Common Emitter (CA3081) or Common Collector (CA3082) Configuration

- Low V<sub>CESAT</sub> (at 50mA) . . . . . . . . . . 0.4V (Typ)

## **Applications**

- Drivers for

- Incandescent Display Devices

- LED Displays

- · Relay Control

- · Thyristor Firing

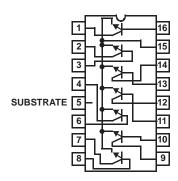

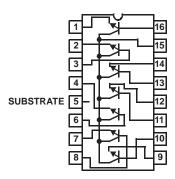

#### **Pinouts**

## CA3081 COMMON EMITTER CONFIGURATION (PDIP, CERDIP, SOIC) TOP VIEW

# CA3082 COMMON COLLECTOR CONFIGURATION (PDIP, SOIC) TOP VIEW

#### **Absolute Maximum Ratings TA = 25°C**

| Collector-to-Emitter Voltage (V <sub>CEO</sub> )               |

|----------------------------------------------------------------|

| Collector-to-Base Voltage (V <sub>CBO</sub> )                  |

| Collector-to-Substrate Voltage (V <sub>CIO</sub> , Note 1) 20\ |

| Emitter-to-Base Voltage (V <sub>EBO</sub> ) 5\                 |

| Collector Current (I <sub>C</sub> )100mA                       |

| Base Current (I <sub>B</sub> )                                 |

#### **Operating Conditions**

| Temperature Range   | -55°C to 125°C     |

|---------------------|--------------------|

| Tomporature realige | <br>-55 0 10 125 0 |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 2)    | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (oC/W)                   |

|-----------------------------------------|----------------------|----------------------------------------|

| CERDIP Package                          | 115                  | 45                                     |

| PDIP Package                            |                      | N/A                                    |

| SOIC Package                            | 190                  | N/A                                    |

| Maximum Power Dissipation (Any One Tr   |                      | 500mW                                  |

| Maximum Junction Temperature (Ceramic I | Package)             | 175 <sup>o</sup> C                     |

| Maximum Junction Temperature (Plastic F | Package)             | 150 <sup>o</sup> C                     |

| Maximum Storage Temperature Range       | 65                   | 5 <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 1   | 0s)                  | 300°C                                  |

| (SOIC - Lead Tips Only)                 |                      |                                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. The collector of each transistor of the CA3081 and CA3082 is isolated from the substrate by an integral diode. The substrate must be connected to a voltage which is more negative than any collector voltage in order to maintain isolation between transistors and provide normal transistor action. To avoid undesired coupling between transistors, the substrate terminal (5) should be maintained at either DC or signal (AC) ground. A suitable bypass capacitor can be used to establish a signal ground.

- 2.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

#### **Electrical Specifications** For Equipment Design at $T_A = 25^{\circ}C$

| PARAMETER                                     | SYMBOL               | TEST CONDITIONS                               | MIN | TYP  | MAX | UNITS |

|-----------------------------------------------|----------------------|-----------------------------------------------|-----|------|-----|-------|

| Collector-to-Base Breakdown Voltage           | V <sub>(BR)CBO</sub> | $I_C = 500\mu A, I_E = 0$                     | 20  | 60   | -   | V     |

| Collector-to-Substrate Breakdown Voltage      | V <sub>(BR)CIO</sub> | $I_C = 500\mu A, I_B = 0$                     | 20  | 60   | -   | V     |

| Collector-to-Emitter Breakdown Voltage        | V <sub>(BR)CEO</sub> | $I_C = 1 \text{mA}, I_B = 0$                  | 16  | 24   | -   | V     |

| Emitter-to-Base Breakdown Voltage             | V <sub>(BR)EBO</sub> | I <sub>C</sub> = 500μA                        | 5.0 | 6.9  | -   | V     |

| DC Forward Current Transfer Ratio             | h <sub>FE</sub>      | V <sub>CE</sub> = 0.5V, I <sub>C</sub> = 30mA | 30  | 68   | -   | -     |

|                                               |                      | V <sub>CE</sub> = 0.8V, I <sub>C</sub> = 50mA | 40  | 70   | -   | -     |

| Base-to-Emitter Saturation Voltage (Figure 4) | V <sub>BESAT</sub>   | I <sub>C</sub> = 30mA, I <sub>B</sub> = 1mA   | -   | 0.87 | 1.2 | V     |

| Collector-to-Emitter Saturation Voltage       | VCESAT               |                                               |     |      |     |       |

| CA3081, CA3082                                |                      | $I_C = 30 \text{mA}, I_B = 1 \text{mA}$       | -   | 0.27 | 0.5 | V     |

| CA3081 (Figure 5)                             |                      | I <sub>C</sub> = 50mA, I <sub>B</sub> = 5mA   | -   | 0.4  | 0.7 | V     |

| CA3082 (Figure 5)                             |                      | I <sub>C</sub> = 50mA, I <sub>B</sub> = 5mA   | -   | 0.4  | 0.8 | V     |

| Collector Cutoff Current                      | ICEO                 | V <sub>CE</sub> = 10V, I <sub>B</sub> = 0     | -   | -    | 10  | μΑ    |

| Collector Cutoff Current                      | I <sub>CBO</sub>     | V <sub>CB</sub> = 10V, I <sub>E</sub> = 0     | -   | -    | 1.0 | μΑ    |

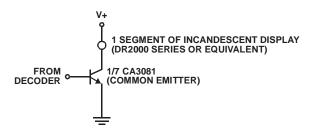

## Typical Read - Out Driver Applications

FIGURE 1. SCHEMATIC DIAGRAM SHOWING ONE TRANSISTOR OF THE CA3081 DRIVING ONE SEGMENT OF AN INCANDESCENT DISPLAY

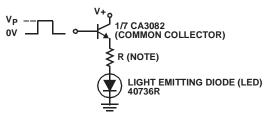

NOTE: The Resistance for R is determined by the relationship:

$$R = \frac{V_P - V_{BE} - V_F(LED)}{I(LED)}$$

$$R = 0 \text{ for } V_P = V_{BF} + V_F(LED)$$

Where:  $V_P = Input Pulse Voltage$

$V_F$  = Forward Voltage Drop Across the Diode

FIGURE 2. SCHEMATIC DIAGRAM SHOWING ONE TRANSISTOR OF THE CA3082 DRIVING A LIGHT EMITTING DIODE (LED)

## **Typical Performance Curves**

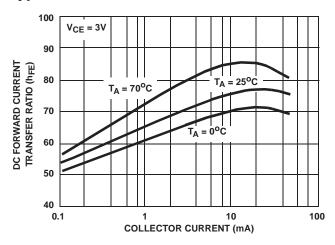

FIGURE 3. DC FORWARD CURRENT TRANSFER RATIO vs COLLECTOR CURRENT

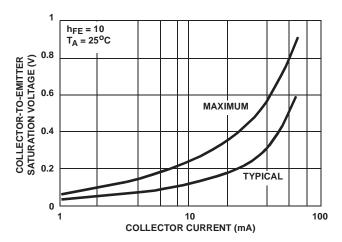

FIGURE 5. COLLECTOR-TO-EMITTER SATURATION VOLTAGE vs COLLECTOR CURRENT

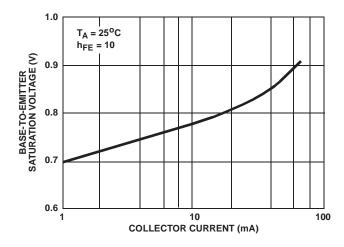

FIGURE 4. BASE-TO-EMITTER SATURATION VOLTAGE vs COLLECTOR CURRENT

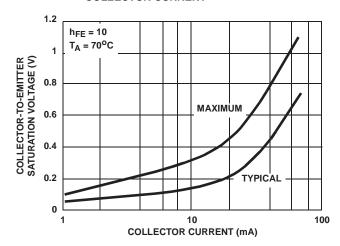

FIGURE 6. COLLECTOR-TO-EMITTER SATURATION VOLTAGE vs COLLECTOR CURRENT

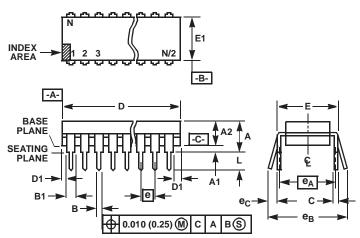

### Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- Dimensions A, A1 and L are measured with the package seated in JE-DEC seating plane gauge GS-3.

- D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-.

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- 10. Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 0.045 inch (0.76 1.14mm).

E16.3 (JEDEC MS-001-BB ISSUE D)

16 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INC   | HES   | MILLIMETERS |          |       |

|----------------|-------|-------|-------------|----------|-------|

| SYMBOL         | MIN   | MAX   | MIN         | MAX      | NOTES |

| А              | -     | 0.210 | -           | 5.33     | 4     |

| A1             | 0.015 | -     | 0.39        | -        | 4     |

| A2             | 0.115 | 0.195 | 2.93        | 4.95     | -     |

| В              | 0.014 | 0.022 | 0.356       | 0.558    | -     |

| B1             | 0.045 | 0.070 | 1.15        | 1.77     | 8, 10 |

| С              | 0.008 | 0.014 | 0.204       | 0.355    | -     |

| D              | 0.735 | 0.775 | 18.66       | 19.68    | 5     |

| D1             | 0.005 | -     | 0.13        | -        | 5     |

| Е              | 0.300 | 0.325 | 7.62        | 8.25     | 6     |

| E1             | 0.240 | 0.280 | 6.10        | 7.11     | 5     |

| е              | 0.100 | BSC   | 2.54        | 2.54 BSC |       |

| e <sub>A</sub> | 0.300 | BSC   | 7.62 BSC    |          | 6     |

| e <sub>B</sub> | -     | 0.430 | -           | 10.92    | 7     |

| L              | 0.115 | 0.150 | 2.93        | 3.81     | 4     |

| N              | 1     | 6     | 16          |          | 9     |

Rev. 0 12/93

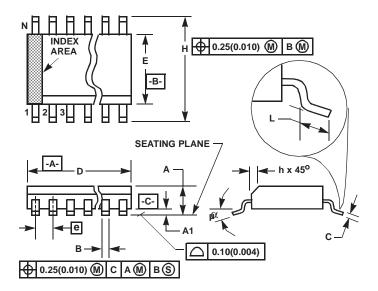

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

M16.15 (JEDEC MS-012-AC ISSUE C)

16 LEAD NARROW BODY SMALL OUTLINE PLASTIC

PACKAGE

|        | INCHES    |                | MILLIM   |       |       |

|--------|-----------|----------------|----------|-------|-------|

| SYMBOL | MIN       | MAX            | MIN      | MAX   | NOTES |

| Α      | 0.0532    | 0.0688         | 1.35     | 1.75  | -     |

| A1     | 0.0040    | 0.0098         | 0.10     | 0.25  | -     |

| В      | 0.013     | 0.020          | 0.33     | 0.51  | 9     |

| С      | 0.0075    | 0.0098         | 0.19     | 0.25  | -     |

| D      | 0.3859    | 0.3937         | 9.80     | 10.00 | 3     |

| Е      | 0.1497    | 0.1574         | 3.80     | 4.00  | 4     |

| е      | 0.050 BSC |                | 1.27 BSC |       | -     |

| Н      | 0.2284    | 0.2440         | 5.80     | 6.20  | -     |

| h      | 0.0099    | 0.0196         | 0.25     | 0.50  | 5     |

| L      | 0.016     | 0.050          | 0.40     | 1.27  | 6     |

| N      | 16        |                | 1        | 6     | 7     |

| α      | 0°        | 8 <sup>0</sup> | 0°       | 8º    | -     |

Rev. 0 12/93

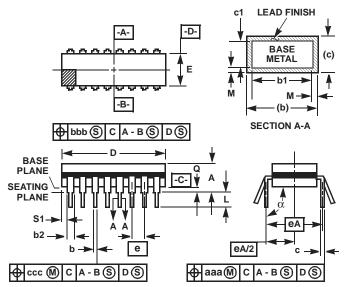

### Ceramic Dual-In-Line Frit Seal Packages (CERDIP)

#### NOTES:

- Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- The maximum limits of lead dimensions b and c or M shall be measured at the centroid of the finished lead surfaces, when solder dip or tin plate lead finish is applied.

- Dimensions b1 and c1 apply to lead base metal only. Dimension M applies to lead plating and finish thickness.

- Corner leads (1, N, N/2, and N/2+1) may be configured with a partial lead paddle. For this configuration dimension b3 replaces dimension b2.

- 5. This dimension allows for off-center lid, meniscus, and glass overrun.

- 6. Dimension Q shall be measured from the seating plane to the base plane.

- 7. Measure dimension S1 at all four corners.

- 8. N is the maximum number of terminal positions.

- 9. Dimensioning and tolerancing per ANSI Y14.5M 1982.

- 10. Controlling dimension: INCH.

F16.3 MIL-STD-1835 GDIP1-T16 (D-2, CONFIGURATION A)

16 LEAD CERAMIC DUAL-IN-LINE FRIT SEAL PACKAGE

|        | INC             | INCHES MILLIMETERS |                 |                  |       |

|--------|-----------------|--------------------|-----------------|------------------|-------|

| SYMBOL | MIN             | MAX                | MIN             | MAX              | NOTES |

| А      | -               | 0.200              | -               | 5.08             | -     |

| b      | 0.014           | 0.026              | 0.36            | 0.66             | 2     |

| b1     | 0.014           | 0.023              | 0.36            | 0.58             | 3     |

| b2     | 0.045           | 0.065              | 1.14            | 1.65             | -     |

| b3     | 0.023           | 0.045              | 0.58            | 1.14             | 4     |

| С      | 0.008           | 0.018              | 0.20            | 0.46             | 2     |

| c1     | 0.008           | 0.015              | 0.20            | 0.38             | 3     |

| D      | -               | 0.840              | -               | 21.34            | 5     |

| E      | 0.220           | 0.310              | 5.59            | 7.87             | 5     |

| е      | 0.100 BSC       |                    | 2.54 BSC        |                  | -     |

| eA     | 0.300           | BSC                | 7.62            | BSC              | -     |

| eA/2   | 0.150           | BSC                | 3.81            | 3.81 BSC         |       |

| L      | 0.125           | 0.200              | 3.18            | 5.08             | -     |

| Q      | 0.015           | 0.060              | 0.38            | 1.52             | 6     |

| S1     | 0.005           | -                  | 0.13            | -                | 7     |

| α      | 90 <sup>0</sup> | 105 <sup>0</sup>   | 90 <sup>0</sup> | 105 <sup>0</sup> | -     |

| aaa    | -               | 0.015              | -               | 0.38             | -     |

| bbb    | -               | 0.030              | -               | 0.76             | -     |

| ccc    | -               | 0.010              | -               | 0.25             | -     |

| М      | -               | 0.0015             | -               | 0.038            | 2, 3  |

| N      | 1               | 6                  | 16              |                  | 8     |

Rev. 0 4/94

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at website <a href="https://www.intersil.com/design/quality/iso.asp">www.intersil.com/design/quality/iso.asp</a>.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

#### Sales Office Headquarters

NORTH AMERICA Intersil Corporation 2401 Palm Bay Rd. Palm Bay, FL 32905 TEL: (321) 724-7000 FAX: (321) 724-7240 EUROPE Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05 ASIA Intersil Ltd. 8F-2, 96, S

RF-2, 96, Sec. 1, Chien-kuo North, Taipei, Taiwan 104 Republic of China TEL: 886-2-2515-8508

FAX: 886-2-2515-8369