### **DS3884A**

### BTL Handshake Transceiver

The DS3884A is pin to pin and functionality compatible with the DS3884. The DS3884A is a speed and power enhanced version of the DS3884. There are two minor differences between the DS3884 and DS3884A.

The external resistor used in the DS3884A is different from that used in the DS3884. REXT for the DS3884 is 6.2k while REXT for the DS3884A is 13k. The available filter settings for DS3884A are 5 ns, 10 ns, 14 ns, 24 ns, while the settings for the DS3884 are 5 ns, 7.5 ns, 15 ns, and 25 ns.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

### DS3884A BTL Handshake Transceiver

### **General Description**

The DS3884A is pin to pin and functionally compatible with the DS3884. The DS3884A is a speed and power enhanced version of the DS3884. There are two minor differences between the DS3884 and DS3884A.

The external resistor used in the DS3884A is different from that used in the DS3884. REXT for the DS3884 is 6.2k while REXT for the DS3884A is 13k. The available filter settings for the DS3884A are 5 ns, 10 ns, 14 ns, 24 ns, while the settings for the DS3884 are 5 ns, 7.5 ns, 15 ns, and 25 ns.

The DS3884A is one in a series of transceivers designed specifically for the implementation of high performance Futurebus+ and proprietary bus interfaces. The DS3884A is a BTL 6-bit Handshake Transceiver designed to conform to IEEE 1194.1 (Backplane Transceiver Logic—BTL) as specified in the IEEE 896.2 Futurebus+ specification. Utilization of the DS3884A simplifies the implementation of all handshake signals which require Wired-OR glitch filtering. Three of the six bits have an additional parallel Wired-OR filtered receive output giving a total of nine receiver outputs.

In Wired-OR applications, the glitch generated as drivers are released from the bus, is dependent upon the backplane and parasitic wiring components causing the characteristics of the glitch to vary in pulse width and amplitude. To accommodate this variation the DS3884A features two pins defined as PS1 and PS2 which allow selection of a 5 ns, 10 ns, 14 ns and 24 ns filter setting to optimize glitch filtering for a given situation. The REXT pin is issued in conjunction with the filtering circuitry and requires a 13 k $\Omega$  resistor to ground. For additional information on Wired-OR glitch, reference Application Note AN-774.

The DS3884A driver output configuration is an NPN open collector which allows Wired-OR connection on the bus. Each driver output incorporates a Schottky diode in series with its collector to isolate the transistor output capacitance from the bus thus reducing the bus loading in the inactive state. The combined output capacitance of the driver and receiver input is typically less than 5 pF. The driver also has high sink current capability to comply with the bus loading requirements defined within IEEE 1194.1 BTL specification.

Backplane Transceiver Logic (BTL) is a signaling standard that was invented and first introduced by National Semiconductor, then developed by the IEEE to enhance the performance of backplane buses. BTL compatible transceivers feature low output capacitance drivers to minimize bus loading, a 1V nominal signal swing for reduced power consumption and receivers with precision thresholds for maximum noise immunity. The BTL standard eliminates settling time delays that severely limit TTL bus performance, and thus provide significantly higher bus transfer rates. The backplane bus is intended to be operated with termination resistors (selected to match the bus impedance) connected to 2.1V at both ends. The low voltage is typically 1V.

TRI-STATE® is a registered trademark of National Semiconductor Corporation

Separate ground pins are provided for each BTL output to minimize induced ground noise during simultaneous switching.

The device's unique driver circuitry meets a maximum slew rate of 0.5V/ns which allows controlled rise and fall times to reduce noise coupling to adjacent lines.

The transceiver's high impedance control and driver inputs are fully TTL compatible.

The receiver is a high speed comparator that utilizes a bandgap reference for precision threshold control allowing maximum noise immunity to the BTL 1V signaling level.

Separate  $QV_{CC}$  and QGND pins are provided to minimize the effects of high current switching noise. Output pins FR1-FR3 are the filtered outputs and R1-R6 are the unfiltered outputs. All receiver outputs are fully TTL compatible.

The DS3884A supports live insertion as defined for Future-bus+ through the LI (Live Insertion) pin. To implement live insertion the LI pin should be connected to the live insertion power connector. If this function is not supported the LI pin must be tied to the  $V_{\rm CC}$  pin. The DS3884A also provides power up/down glitch free protection during power sequencing.

The DS3884A has two types of power connections in addition to the LI pin. They are the Logic  $V_{\rm CC}$  ( $V_{\rm CC}$ ) and the Quiet  $V_{\rm CC}$  (QV $_{\rm CC}$ ). There are two  $V_{\rm CC}$  pins on the DS3884A that provide the supply voltage for the logic and control circuitry. Multiple connections are provided to reduce the effects of package inductance and thereby minimize switching noise. As these pins are common to the V $_{\rm CC}$  bus internal to the device, a voltage difference should never exist between these pins and the voltage difference between V $_{\rm CC}$  and QV $_{\rm CC}$  should never exceed  $\pm 0.5$ V because of ESD circuitry. Additionally, the ESD circuitry between the V $_{\rm CC}$  pins and all other pins except for BTL I/O's and LI pins requires that any voltage on these pins should not exceed the voltage on V $_{\rm CC}$ + 0.5V.

There are three different types of ground pins on the DS3884A. They are the logic ground (GND), BTL grounds (B1GND-B6GND) and the Bandgap reference ground (QGND). All of these ground reference pins are isolated within the chip to minimize the effects of high current switching transients. For optimum performance the QGND should be returned to the connector through a quiet channel that does not carry transient switching current. The GND and B1GND-B6GND should be connected to the nearest backplane ground pin with the shortest possible path.

Since many different grounding schemes could be implemented and ESD circuitry exist on the DS3884A, it is important to note that any voltage difference between ground pins, QGND, GND or B1GND–B6GND should not exceed  $\pm 5V$  including power up/down sequencing.

Additional transceivers included in the Futurebus+ / BTL family are; the DS3883A BTL 9-bit Transceiver, and the DS3886A BTL 9-bit Latching Data Transceiver featuring

#### General Description (Continued)

edge triggered latches in the driver which may be bypassed during a fall-through mode and a transparent latch in the receiver.

#### **Features**

- Fast propagation delay (3 ns typ)

- 6-bit BTL transceiver

- Selective receiver glitch filtering (FR1–FR3)

- Meets 1194.1 Standard on Backplane Transceiver Logic (BTL)

- Supports live insertion

- Glitch free power-up/down protection

- Typically less than 5 pF bus-port capacitance

- Low Bus-port voltage swing (typically 1V) at 80 mA

- TTL compatible driver and control inputs

- Separate TTL I/O

- Open collector bus-port outputs allow Wired-OR connection

- Controlled rise and fall time to reduce noise coupling to adjacent lines

- Built in Bandgap reference with separate QV <sub>CC</sub> and QGND pins for precise receiver thresholds

- Exceeds 2 kV ESD testing (Human Body Model)

- Individual Bus-port ground pins

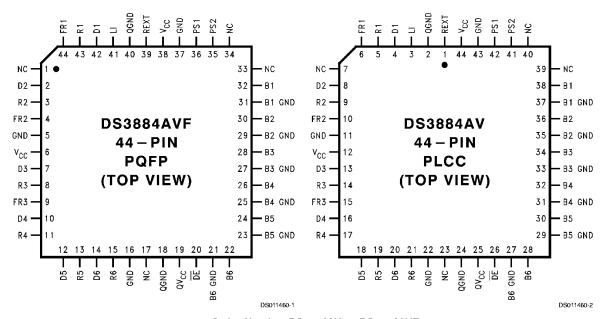

- Product offered in PLCC and PQFP package styles

### **Connection Diagrams**

Order Number DS3884AV or DS3884AVF See NS Package V44A or VF44B

www.national.com 2

## Logic Diagram D1 -— в1 R1 -FR1 -DELAY D2 -**-** B2 R2 -FR2 -DELAY D3 -**-** B3 R3 -FR3 -DELAY D4 -- B4 R4 -D5 -**–** B5 R5 -D6 -R6 -DE PS2 DS011460-3

#### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage 6.5V

Control Input Voltage 6.5V

Driver Input and Receiver Output 5.5V

Receiver Input Current ±15 mA

Bus Termination Voltage 2.4V

Power Dissipation at 25°C

PLCC 2.5W PQFP 1.3W

Derate PLCC Package 20 mW/°C

Derate PQFP Package 11.1 mW/°C

Storage Temperature Range -65°C to +150°C

Lead Temperature

260°C

(Soldering, 4 seconds):

## Recommended Operating Conditions

$\begin{array}{lll} \text{Supply Voltage, V}_{\text{CC}} & 4.5\text{V}-5.5\text{V} \\ \text{Bus Termination Voltage (V}_{\text{T}}) & 2.06\text{V}-2.14\text{V} \\ \text{Operating Free Air Temperature} & 0^{\circ}\text{C to } 70^{\circ}\text{C} \end{array}$

### DC Electrical Characteristics (Notes 2, 3)

$T_A = 0 \text{ to } +70^{\circ}\text{C}, V_{CC} = 5V \pm 10\%$

| Symbol                                           | Parameter                                  | Conditions                                           | Min  | Тур  | Max  | Units |  |

|--------------------------------------------------|--------------------------------------------|------------------------------------------------------|------|------|------|-------|--|

| DRIVER AND CONTROL INPUT: (Dn, DE*, PS1 and PS2) |                                            |                                                      |      |      |      |       |  |

| V <sub>IH</sub>                                  | Minimum Input High Voltage                 |                                                      | 2.0  |      |      | ٧     |  |

| V <sub>IL</sub>                                  | Maximum Input Low Voltage                  |                                                      |      |      | 0.8  | ٧     |  |

| I <sub>I</sub>                                   | Input Leakage Current                      | V <sub>IN</sub> = V <sub>CC</sub> = 5.5V             |      |      | 100  | μΑ    |  |

| I <sub>IH</sub>                                  | Input High Current                         | $V_{IN} = 2.4V$                                      |      |      | 40   | μΑ    |  |

| I <sub>IL</sub>                                  | Input Low Current                          | V <sub>IN</sub> = 0.5V                               |      |      | -100 | μΑ    |  |

| V <sub>CL</sub>                                  | Input Diode Clamp Voltage                  | I <sub>CLAMP</sub> = -12 mA                          |      |      | -1.2 | ٧     |  |

| DRIVER                                           | OUTPUT/RECEIVER INPUT: (Bn)                | •                                                    | •    | •    |      |       |  |

| V <sub>OLB</sub>                                 | Output Low Bus Voltage                     | Dn = 2.4V, DE* = 0V,                                 | 0.75 | 1.0  | 1.1  | ٧     |  |

|                                                  | (Note 5)                                   | I <sub>OL</sub> = 80 mA                              |      |      |      |       |  |

| I <sub>OLBZ</sub>                                | Output Low Bus Current                     | Dn = 0.5V, DE* = 2.4V, Bn = 0.75V                    |      |      | 100  | μΑ    |  |

| I <sub>OHBZ</sub>                                | Output High Bus Current                    | Dn = 0.5V, DE* = 2.4V, Bn = 2.1V                     |      |      | 100  | μΑ    |  |

| I <sub>OLB</sub>                                 | Output Low Bus Current                     | Dn = 0.5V, DE* = 0V, Bn = 0.75V                      |      |      | 220  | μΑ    |  |

| I <sub>ОНВ</sub>                                 | Output High Bus Current                    | Dn = 0.5V, DE* = 0V, Bn = 2.1V                       |      |      | 350  | μΑ    |  |

| V <sub>TH</sub>                                  | Receiver Input Threshold                   | DE* = 2.4V                                           | 1.47 | 1.55 | 1.62 | ٧     |  |

| V <sub>CLP</sub>                                 | Positive Clamp Voltage                     | V <sub>CC</sub> = Max or 0V, I <sub>Bn</sub> = 1 mA  | 2.4  | 3.4  | 4.5  | ٧     |  |

|                                                  |                                            | V <sub>CC</sub> = Max or 0V, I <sub>Bn</sub> = 10 mA | 2.9  | 3.9  | 5.0  | ٧     |  |

| V <sub>CLN</sub>                                 | Negative Clamp Voltage                     | I <sub>CLAMP</sub> = -12 mA                          |      |      | -1.2 | ٧     |  |

| RECEIVE                                          | R OUTPUT: (FRn and Rn)                     |                                                      |      |      |      |       |  |

| V <sub>OH</sub>                                  | Voltage Output High                        | Bn = 1.1V, DE* = 2.4V, $I_{OH} = -2 \text{ mA}$      | 2.4  | 3.2  |      | ٧     |  |

| V <sub>OL</sub>                                  | Voltage Output Low                         | Bn = 2.1V, DE* = 2.4V, I <sub>OL</sub> = 24 mA       |      | 0.35 | 0.5  | ٧     |  |

|                                                  |                                            | Bn = 2.1V, DE* = 2.4V, I <sub>OL</sub> = 8 mA        |      | 0.35 | 0.4  | ٧     |  |

| los                                              | Output Short Circuit Current               | Bn = 1.1V, DE* = 2.4V (Note 4)                       | -40  | -70  | -100 | mA    |  |

| SUPPLY CURRENT                                   |                                            |                                                      |      |      |      |       |  |

| Icc                                              | Supply Current: Includes V <sub>CC</sub> , | DE* = 0.5V, All Dn = 2.4V                            |      | 50   | 70   | mA    |  |

|                                                  | QV <sub>CC</sub> and LI                    | DE* = 2.4V, All Bn = 2.1V                            |      | 50   | 70   | mA    |  |

| ILI                                              | Live Insertion Current                     | DE* = 2.4V, All Dn = 0.5V                            |      | 1    | 3    | mA    |  |

|                                                  |                                            | DE* = 0.5V, All Dn = 2.4V                            |      | 2    | 5    | mA    |  |

|                                                  |                                            |                                                      |      |      |      |       |  |

Note 1: "Absolute Maximum Ratings" are those beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provide conditions for actual device operation.

Note 2: All input and/or output pins shall not exceed  $V_{CC}$  plus 0.5V and shall not exceed the absolute maximum rating at anytime, including power-up and power-down. This prevents the ESD structure from being damaged due to excessive currents flowing from the input and/or output pins to  $QV_{CC}$  and  $V_{CC}$ . There is a diode between each input and/or output to  $V_{CC}$  which is forward biased when incorrect sequencing is applied. Alternatively, a current limiting resistor can be used when pulling-up the inputs to prevent damage. The current into any input/output pin shall be no greater than 50 mA. Exception, LI and Bn pins do not have power sequencing requirements with respect to  $V_{CC}$  and  $QV_{CC}$ . Furthermore, the difference between  $V_{CC}$  and  $QV_{CC}$  should never be greater than 0.5V at any time including power-up

Note 3: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground unless otherwise specified. All typical values are specified under these conditions.: V<sub>CC</sub> = 5V and T<sub>A</sub> = 25°C unless otherwise stated.

Note 4: Only one output should be shorted at a time, and duration of the short should not exceed one second.

Note 5: Referenced to appropriate signal ground. Do not exceed maximum power dissipation of package.

www.national.com

## AC Electrical Characteristics (Note 6) $T_A = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = 5V \pm 10\%$

| Symbol            | Par               | ameter         | Conditions                                           | Min | Тур | Max | Units |

|-------------------|-------------------|----------------|------------------------------------------------------|-----|-----|-----|-------|

| DRIVER            |                   |                | 1                                                    | 1   |     |     |       |

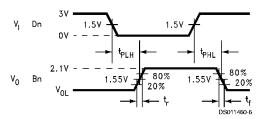

| t <sub>PHL</sub>  | Dn to Bn          | Prop. Delay    | DE* = 0V                                             | 1   | 3   | 5   | ns    |

| t <sub>PLH</sub>  |                   |                | (Figure 1, Figure 2)                                 | 1   | 3   | 5   | ns    |

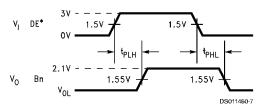

| t <sub>PHL</sub>  | DE* to Bn         | Enable Time    | Dn = 3V                                              | 2   | 4   | 6   | ns    |

| t <sub>PLH</sub>  |                   | Disable Time   | (Figure 1, Figure 3)                                 | 2   | 4   | 6   | ns    |

| t <sub>r</sub>    | Transition Time-  | - Rise/Fall    | (Figure 1, Figure 2)                                 | 1   | 2   | 3.5 | ns    |

| t <sub>f</sub>    | 20% to 80%        |                |                                                      | 1   | 2   | 3.5 | ns    |

| SR                | Skew Rate is Cal  | culated        | (Note 11)                                            |     |     | 0.5 | V/ns  |

|                   | from 1.3V to 1.8V | 1              |                                                      |     |     |     |       |

| t <sub>skew</sub> | Skew between Di   | rivers in      | (Note 7)                                             |     | 1   | 3   | ns    |

|                   | the Same Packag   | je             |                                                      |     |     |     |       |

| RECEIVE           | R                 |                |                                                      | ·   |     |     |       |

| t <sub>PHL</sub>  | Bn to Rn          | Prop. Delay    | DE* = 3V                                             | 2   | 4   | 5   | ns    |

| t <sub>PLH</sub>  |                   |                | (Figure 4, Figure 5)                                 | 2   | 4   | 6   | ns    |

| t <sub>skew</sub> | Skew between Re   | eceivers in    | (Note 7)                                             |     | 1   | 3   | ns    |

|                   | Same Package      |                |                                                      |     |     |     |       |

| FILTERE           | DRECEIVER         |                | •                                                    |     | •   |     |       |

| t <sub>PHL</sub>  | Bn to FRn         | Prop. Delay    | PS1 = 0V PS2 = 0V DE* = 3V                           | 6   | 12  | 16  | ns    |

|                   |                   |                | (Figure 4, Figure 5), $R_{EXT} = 13 \text{ k}\Omega$ |     |     |     |       |

|                   |                   |                | PS1 = 0V PS2 = 3V DE* = 3V                           | 11  | 16  | 21  | ns    |

|                   |                   |                | (Figure 4, Figure 5), $R_{EXT} = 13 \text{ k}\Omega$ |     |     |     |       |

|                   |                   |                | PS1 = 3V PS2 = 0V DE* = 3V                           | 15  | 21  | 27  | ns    |

|                   |                   |                | (Figure 4, Figure 5), $R_{EXT} = 13 \text{ k}\Omega$ |     |     |     |       |

|                   |                   |                | PS1 = 3V PS2 = 3V DE* = 3V                           | 25  | 33  | 45  | ns    |

|                   |                   |                | (Figure 4, Figure 5), $R_{EXT} = 13 \text{ k}\Omega$ |     |     |     |       |

| t <sub>PLH</sub>  | Bn to FRn         | Prop. Delay    | DE* = 3V (Figure 4, Figure 5)                        | 2   | 5   | 7   | ns    |

|                   |                   |                | (Note 8)                                             | _   |     | ′   | 113   |

|                   |                   |                | $R_{EXT} = 13 \text{ k}\Omega$                       |     |     |     |       |

| t <sub>GR</sub>   | Glitch Rejection  |                | PS1 = 0V PS2 = 0V DE* = 3V                           | 5   | 9   | 16  | ns    |

|                   |                   |                | (Figure 4, Figure 6), $R_{EXT} = 13 \text{ k}\Omega$ |     |     |     |       |

|                   |                   |                | PS1 = 0V PS2 = 3V DE* = 3V                           | 10  | 13  | 18  | ns    |

|                   |                   |                | (Figure 4, Figure 6), $R_{EXT} = 13 \text{ k}\Omega$ |     |     |     |       |

|                   |                   |                | PS1 = 3V PS2 = 0V DE* = 3V                           | 14  | 18  | 24  | ns    |

|                   |                   |                | (Figure 4, Figure 6), $R_{EXT} = 13 \text{ k}\Omega$ |     |     |     |       |

|                   |                   |                | PS1 = 3V PS2 = 3V DE* = 3V                           | 24  | 31  | 42  | ns    |

|                   |                   |                | (Figure 4, Figure 6), $R_{EXT} = 13 \text{ k}\Omega$ |     |     |     |       |

|                   |                   | G REQUIREMENTS |                                                      |     | ,   |     |       |

| t <sub>s</sub>    | PSn to Bn         | Set-Up Time    | (Figure 7), $R_{EXT} = 13 \text{ k}\Omega$           | 250 |     |     | ns    |

|                   | TERS NOT TESTE    |                |                                                      |     | ,   |     |       |

| Coutput           | Capacitance at B  | n              | (Note 9)                                             |     | 5   |     | pF    |

| t <sub>NR</sub>   | Noise Rejection   |                | (Note 10)                                            |     | 1   |     | ns    |

Note 6: Input waveforms shall have a rise/fall time of 3 ns.

Note 7: t<sub>skew</sub> is an absolute value defined as differences seen in propagation delays between drivers in the same package with identical load conditions.

Note 8: Filtered receiver  $t_{\text{PLH}}$  is independent of filter setting.

Note 9: The parameter is tested using TDR techniques described in P1194.0 BTL Backplane Design Guide.

Note 10: This parameter is tested during device characterization. The measurements revealed that the part will reject 1 ns pulse width.

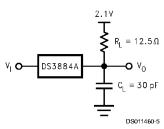

Note 11: Futurebus+ transceivers are required to limit bus signal rise and fall times to no faster than 0.5V/ns, measured between 1.3V and 1.8V (approximately 20% to 80% of nominal voltage swing). The rise and fall times are measured with a transceiver loading equivalent to 12.5 $\Omega$  tied to +2.1V DC.

### **Pin Descriptions**

| Pin Name         | Number of | Input/ | Description                                                                                                                                                                                                                                                     |

|------------------|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | Pins      | Output |                                                                                                                                                                                                                                                                 |

| B1-B6            | 6         | I/O    | BTL receiver input and driver output                                                                                                                                                                                                                            |

| B1GND-B6GND      | 6         | NA     | Driver output ground reduces bounce due to high current switching of driver outputs (Note 12)                                                                                                                                                                   |

| DE*              | 1         | Į.     | Driver Enable Low                                                                                                                                                                                                                                               |

| D1-D6            | 6         | ı      | TTL Driver Input                                                                                                                                                                                                                                                |

| FR1-FR3          | 3         | 0      | TTL Filtered Receiver Output                                                                                                                                                                                                                                    |

| GND              | 3         | NA     | Ground reference for switching circuits. (Note 12)                                                                                                                                                                                                              |

| LI               | 1         | NA     | Power supply for live insertion. Boards that require live insertion should connect LI to the live insertion pin on the connector. (Note 13)                                                                                                                     |

| NC               | 4         | NA     | No Connect                                                                                                                                                                                                                                                      |

| PS1, PS2         | 2         | I      | Pulse Width Selection pin determines glitch filter setting (Note 14)                                                                                                                                                                                            |

| R1-R6            | 6         | 0      | TTL Receiver Output                                                                                                                                                                                                                                             |

| REXT             | 1         | NA     | External Resistor pin. External resistor is used for internal biasing of filter circuitry. The 13 k $\Omega$ resistor shall be connected between REXT and GND. The resistor shall have a tolerance of 1% and a temperature coefficient of 100 ppm/°C or better. |

| QGND             | 2         | NA     | Ground reference for receiver input bandgap reference and non-switching circuits (Note 12)                                                                                                                                                                      |

| QV <sub>cc</sub> | 1         | NA     | V <sub>CC</sub> supply for bandgap reference and non-switching circuits (Note 13)                                                                                                                                                                               |

| V <sub>cc</sub>  | 2         | NA     | V <sub>CC</sub> supply for switching circuits (Note 13)                                                                                                                                                                                                         |

Note 12: the multiplicity of grounds reduces the effective inductance of bonding wires and leads, which then reduces the noise caused by transients on the ground path. The various ground pins can be tied together provided that the external ground has low inductance (i.e., ground plane with power pins and many signal pins connected to the backplane ground). If the external ground floats considerably during transients, precautionary steps should be taken to prevent QGND from moving with reference to the backplane ground. The receiver threshold should have the same ground reference as the signal coming from the backplane. A voltage offset between their grounds will degrade the noise margin.

Note 13: The same considerations for ground are used for V  $_{CC}$  in reducing lead inductance (see Note 12).  $QV_{CC}$  and  $V_{CC}$  should be tied together externally. If live insertion is not supported, the LI pin can be tied together with  $QV_{CC}$  and  $V_{CC}$ .

Note 14: See AC characteristics for filter setting.

www.national.com 6

### **Truth Table**

| DE* | Dn | FRn | Rn | Bn |

|-----|----|-----|----|----|

| Н   | Х  | Н   | Н  | L  |

| Н   | Х  | L   | L  | Н  |

| L   | Н  | Н   | Н  | L  |

| L   | L  | L   | L  | Н  |

- X: High or low logic state

- L: Low state

- H: High state

- L-H: Low to high transition

### Glitch Filter Table

| PS1 | PS2 | Filter Setting |

|-----|-----|----------------|

| L   | L   | 5 ns           |

| L   | Н   | 10 ns          |

| Н   | L   | 14 ns          |

| Н   | Н   | 24 ns          |

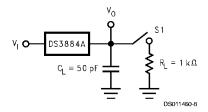

FIGURE 1. Driver Propagation Delay Set-Up

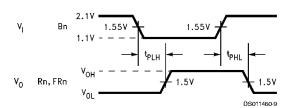

FIGURE 2. Driver: Dn to Bn

FIGURE 3. Driver: DE\* to Bn

|    | Switch Position                  |       |  |  |

|----|----------------------------------|-------|--|--|

|    | t <sub>PLH</sub> t <sub>Pt</sub> |       |  |  |

| S1 | open                             | close |  |  |

FIGURE 4. Receiver Propagation Delay Set-Up

FIGURE 5. Receiver: Bn to FRn, Bn to Rn

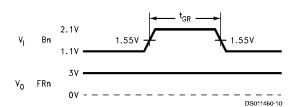

FIGURE 6. Receiver:  $t_{GR}$ , FRn(min) = 2V

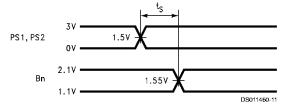

FIGURE 7. Receiver: PSn to Bn

7