# **M2732A**

# 32K (4K x 8) UV Erasable PROM

The Intel M2732A is a 5V only, 32,768 bit ultraviolet erasable and electrically programmable read-only memory (EPROM). The standard M2732A's access time is 450 ns with speed selection (M2732A-25) available at 250 ns. The access time is compatible to high performance microprocessors, such as the 5 MHz MiAPX 86/10. In these systems, the M2732A allows the microprocessor to operate without the addition of WAIT states.

An important M2732A feature is the separate output control, Output Enable ( $\overline{OE}$ ), from the Chip Enable control ( $\overline{CE}$ ). The  $\overline{OE}$  control eliminates bus contention in multiple bus microprocessor systems.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

# **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# M2732A 32K (4K x 8) UV ERASABLE PROM

Military

- 250 ns (M2732A-25) Maximum Access Time ... HMOS\* -E Technology

- Compatible to High Speed 5 MHz MIAPX 86/10 MPU ... Zero Wait State

- Military Temperature Range: -55°C to +125°C (T<sub>C</sub>)

- **Industry Standard Pinout ... JEDEC Approved**

- Two Line Control

- Low Standby Current . . . 35 mA Max.

The Intel M2732A is a 5V only, 32,768 bit ultraviolet erasable and electrically programmable read-only memory (EPROM). The standard M2732A's access time is 450 ns with speed selection (M2732A-25) available at 250 ns. The access time is compatible to high performance microprocessors, such as the 5 MHz MiAPX 86/10. In these systems, the M2732A allows the microprocessor to operate without the addition of WAIT states.

An important M2732A feature is the separate output control, Output Enable (OE), from the Chip Enable control (CE). The OE control eliminates bus contention in multiple bus microprocessor systems. Intel's Application Note AP-72 describes the microprocessor system implementation of the OE and CE controls on Intel's EPROMs. AP-72 is available from Intel's Literature Department.

The M2732A has a standby mode which reduces the power dissipation without increasing access time. The maximum active current is 115 mA, while the maximum standby current is only 35 mA, a 66% saving. The standby mode is achieved by applying a TTL-high signal to the CE input.

The M2732A is fabricated with HMOS-E technology, Intel's high speed N-channel MOS Silicon Gate Technol-

\*HMOS is a patented process of Intel Corporation.

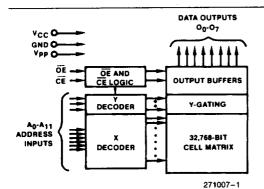

Figure 1. Block Diagram

# Mode Selection

| Mode Selection  |                 |                            |                      |                          |  |  |  |  |

|-----------------|-----------------|----------------------------|----------------------|--------------------------|--|--|--|--|

| Pins<br>Mode    | CE<br>(18)      | OE/V <sub>PP</sub><br>(20) | V <sub>CC</sub> (24) | Outputs<br>(9-11, 13-17) |  |  |  |  |

| Read            | $V_{IL}$        | V <sub>IL</sub>            | +5                   | D <sub>OUT</sub>         |  |  |  |  |

| Standby         | $V_{1H}$        | Don't Care                 | +5                   | High Z                   |  |  |  |  |

| Program         | ۶               | V <sub>PP</sub>            | +5                   | D <sub>IN</sub>          |  |  |  |  |

| Program Verify  | VIL             | V <sub>IL</sub>            | +5                   | D <sub>OUT</sub>         |  |  |  |  |

| Program Inhibit | V <sub>IH</sub> | V <sub>PP</sub>            | +5                   | High Z                   |  |  |  |  |

#### M2732A 24 VCC 23 A 22 A9 4 □ A11 20 TE/VPP 19 A10 18 TE 17 07 Aol 16 🗀 06 15 🗀 05 14 04 Ool 11 ]03 GND 13

271007-2

Figure 2. Configuration

| Pin Names                       |               |  |  |  |  |  |

|---------------------------------|---------------|--|--|--|--|--|

| A <sub>0</sub> -A <sub>11</sub> | Addresses     |  |  |  |  |  |

| Œ                               | Chip Enable   |  |  |  |  |  |

| ŌĒ                              | Output Enable |  |  |  |  |  |

| 00-07                           | Outputs       |  |  |  |  |  |

# **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias55°C to +135°C                                               |

|------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                  |

| All Input or Output Voltages with Respect to Ground +6V to −0.3V                   |

| $V_{PP}$ Supply Voltage with Respect to Ground During Programming + 22V to $-0.3V$ |

NOTICE: This is a production data sheet. The specifications are subject to change without notice.

\*WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

# D.C. AND A.C. OPERATING CONDITIONS DURING READ

|                                               | M2732A-25       | M2732A-45       |

|-----------------------------------------------|-----------------|-----------------|

| Operating Temperature Range (T <sub>C</sub> ) | -55°C to +125°C | -55°C to +125°C |

| V <sub>CC</sub> Power Supply                  | 5V ±10%         | 5V ±10%         |

## **READ OPERATION**

### D.C. CHARACTERISTICS

| Symbol           | Parameter                         |      | Limits |                     | Unit | Test Conditions                                  |

|------------------|-----------------------------------|------|--------|---------------------|------|--------------------------------------------------|

|                  | raidilletei                       | Min  | Typ(1) | Max                 |      |                                                  |

| I <sub>IL</sub>  | Input Load Current                |      |        | 10                  | μА   | V <sub>IN</sub> = 5.5V                           |

| lo               | Output Leakage Current            |      |        | 10                  | μА   | V <sub>OUT</sub> = 5.5V                          |

| I <sub>CC1</sub> | V <sub>CC</sub> Current (Standby) |      |        | 35                  | mA   | $\overline{CE} = V_{IH}, \overline{OE} = V_{IL}$ |

| I <sub>CC2</sub> | V <sub>CC</sub> Current (Active)  |      |        | 115                 | mA   | OE = CE = VIL                                    |

| V <sub>IL</sub>  | Input Low Voltage                 | -0.1 |        | 8.0                 | V    |                                                  |

| V <sub>IH</sub>  | Input High Voltage                | 2.0  |        | V <sub>CC</sub> + 1 | ٧    |                                                  |

| V <sub>OL</sub>  | Output Low Voltage                |      |        | 0.45                | V    | I <sub>OL</sub> = 2.1 mA                         |

| V <sub>OH</sub>  | Output High Voltage               | 2.4  |        |                     | V    | I <sub>OH</sub> ± 400 μA                         |

#### NOTE:

### A.C. CHARACTERISTICS

| Symbol              | Parameter                                                           |     | M2732A-25 |     | M2732A-45 |        |     | Unit | Test                                     |

|---------------------|---------------------------------------------------------------------|-----|-----------|-----|-----------|--------|-----|------|------------------------------------------|

|                     | raiametei                                                           | Min | Typ(1)    | Max | Min       | Typ(1) | Max | ]    | Conditions                               |

| tACC                | Address to Output Delay                                             |     |           | 250 |           |        | 450 | ns   | $\overline{CE} = \overline{OE} = V_{IL}$ |

| t <sub>CE</sub>     | CE to Output Delay                                                  |     |           | 250 |           |        | 450 | ns   | OE = V <sub>IL</sub>                     |

| t <sub>OE</sub>     | Output Enable to Output<br>Delay                                    | 10  |           | 100 | 10        |        | 150 | ns   | CE = V <sub>IL</sub>                     |

| t <sub>DF</sub> (2) | Output Enable High to Output<br>Float                               | 0   |           | 90  | 0         |        | 130 | ns   | CE = V <sub>IL</sub>                     |

| t <sub>OH</sub> (2) | Output Hold from Addresses,<br>CE or OE Whichever Occurred<br>First | 0   |           |     | 0         |        |     | ns   | CE = OE = V <sub>IL</sub>                |

<sup>1.</sup> Typical values are for  $T_C = 25^{\circ}C$  and nominal supply voltages.

# CAPACITANCE (1), (2)

$T_{C}(5) = 25^{\circ}C. f = 1 MHz$

| 1000             | 20 0, 1 1 111112                               |     |     |      |                       |

|------------------|------------------------------------------------|-----|-----|------|-----------------------|

| Symbol           | Parameter                                      | Тур | Max | Unit | Conditions            |

| C <sub>IN</sub>  | Input Capacitance<br>Except OE/V <sub>PP</sub> | 4   | 6   | pF   | V <sub>IN</sub> = 0V  |

| CIN              | OE/V <sub>PP</sub> Input<br>Capacitance        |     | 20  | рF   | V <sub>IN</sub> = 0V  |

| C <sub>OUT</sub> | Output Capacitance                             |     | 12  | pF   | V <sub>OUT</sub> = 0V |

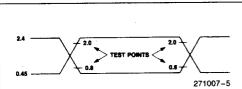

# A.C. TESTING, OUTPUT WAVEFORM

A.C. Testing: inputs are driven at 2.4V for a Logic "1" and 0.45V for a Logic "0". Timing Measurements are made at 2.0V for a Logic "1" and 0.8V for a Logic "0".

# A.C. TEST CONDITIONS

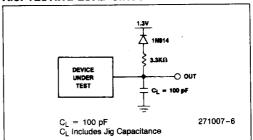

### A.C. TESTING LOAD CIRCUIT

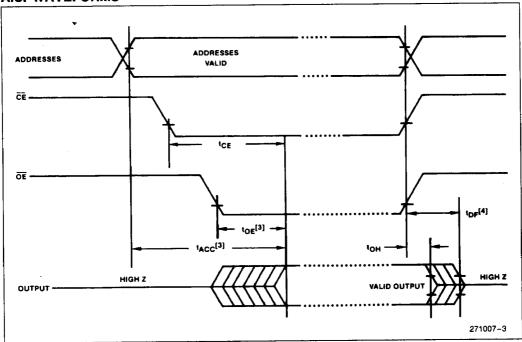

## A.C. WAVEFORMS

#### NOTES:

- 1. Typical values are for  $T_C = 25^{\circ}C$  and nominal supply voltages.

- 2. This parameter is only sampled and is not 100% tested.

- 3. OE may be delayed up to tACC-tOE after the falling edge of CE without impact on tACC.

- 4. This parameter is only sampled and is not 100% tested. Output Float is defined as the point where data is no longer driven.

- 5. Case temperatures are "instant on".

### **DEVICE OPERATION**

The five modes of operation of the M2732A are listed in Table 1. A single 5V power supply is required in the read mode. All inputs are TTL levels except for  $\overline{\text{OE}/\text{Vpp}}$  during programming. In the program mode the  $\overline{\text{OE}/\text{Vpp}}$  input is pulsed from a TTL level to 21V.

**Table 1. Mode Selection**

| Pins            | CE<br>(18)      | OE/V <sub>PP</sub> (20) | V <sub>CC</sub> (24) | Outputs<br>(9-11, 13-17) |

|-----------------|-----------------|-------------------------|----------------------|--------------------------|

| Read            | VIL             | V <sub>IL</sub>         | +5                   | D <sub>OUT</sub>         |

| Standby         | V <sub>IH</sub> | Don't Care              | +5                   | High Z                   |

| Program         | VIL             | Vpp                     | +5                   | D <sub>IN</sub>          |

| Program Verify  | ٧ <sub>IL</sub> | V <sub>IL</sub>         | +5                   | D <sub>OUT</sub>         |

| Program Inhibit | VIH             | V <sub>PP</sub>         | +5                   | High Z                   |

### Read Mode

The M2732A has two control functions, both of which must be logically satisfied in order to obtain data at the outputs. Chip Enable ( $\overline{\text{CE}}$ ) is the power control and should be used for device selection. Output Enable ( $\overline{\text{OE}}$ ) is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time ( $t_{ACC}$ ) is equal to the delay from  $\overline{\text{CE}}$  to output ( $t_{CE}$ ). Data is available at the outputs after the falling edge of  $\overline{\text{OE}}$ , assuming that  $\overline{\text{CE}}$  has been low and addresses have been stable for at least  $t_{ACC}$ – $t_{CE}$ .

# Standby Mode

The M2732A has a standby mode which reduces the active power current by 66%, from 115 mA to 35 mA. The M2732A is placed in the standby mode by applying a TTL high signal to the  $\overline{CE}$  input. When in standby mode, the outputs are in a high impedance state, independent of the  $\overline{OE}$  input.

# **Output OR-Tieing**

Because EPROMs are usually used in larger memory arrays, Intel has provided a 2 line control function that accommodates this use of multiple memory connection. The two line control function allows for:

- a) the lowest possible memory power dissipation, and

- b) complete assurance that output bus contention will not occur.

To use these two control lines most efficiently, it is recommended that  $\overline{CE}$  (pin 18) be decoded and used as the primary device selecting function, while  $\overline{OE}$  (pin 20) be made a common connection to all devices in the array and connected to the READ line from the system control bus. This ensures that all deselected memory devices are in their low power standby mode and that the outputs pins are only active when data is desired from a particular memory device.

## **Programming**

Programming is the same as Intel's M2732 except for the programming voltage. In the program mode the M2732A  $\overline{OE}/V_{PP}$  input is pulsed from a TTL low level to 21V (25V for the M2732). *Exceeding 21.5V will damage the M2732A*.

Initially, and after each erasure, all bits of the M2732A are in the "1" state. Data is introduced by selectively programming "0's" into the desired bit locations. Although only "0's" will be programmed, both "1's" and "0's" can be present in the data word. The only way to change a "0" to a "1" is by ultraviolet light erasure.

The M2732A is in the programming mode when the  $\overline{\text{OE}/\text{Vpp}}$  input is at 21V. It is required that a 0.1  $\mu\text{F}$  capacitor be placed across  $\overline{\text{OE}/\text{Vpp}}$  and ground to suppress spurious voltage transients which may damage the device. The data to be programmed is applied 8 bits in parallel to the data output pins. The levels required for the address and data inputs are TTL.

When the address and data are stable, a 50 ms, active low, TTL program pulse is applied to the  $\overline{\text{CE}}$  input. A program pulse must be applied at each address location to be programmed. You can program any location at any time—either individually, sequentially, or at random. The program pulse has a maximum width of 55 ms. The M2732A must not be programmed with a DC signal applied to the  $\overline{\text{CE}}$  input.

Programming of the multiple M2732As in parallel with the same data can be easily accomplished due to the simplicity of the programming requirements. Like inputs of the paralleled M2732As may be connected together when they are programmed with the same data. A low level TTL pulse applied to the CE input programs the paralleled M2732As.

# Program Inhibit

Programming of multiple M2732As in parallel with different data is also easily accomplished. Except for CE, all like inputs (including OE) of the parallel M2732As may be common. A TTL level program pulse applied to a M2732A's CE input with OE/Vpp at 21V will program that M2732A. A high level CE input inhibits the other M2732As from being programmed.

# **Program Verify**

A verify should be performed on the programmed bits to determine that they were correctly programmed. The verify is accomplished with OE/Vpp and CE at VIL. Data should be verified tov after the falling edge of CE.

# **ERASURE CHARACTERISTICS**

The erasure characteristics of the M2732A are such that erasure begins to occur when exposed to light with wavelengths shorter than approximately 4000

Angstroms (Å). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000-4000Å range. Data shows that constant exposure to room level fluorescent lighting could erase the typical M2732A in approximately 3 years, while it would take approximately 1 week to cause erasure when exposed to direct sunlight. If the M2732A is to be exposed to these types of lighting conditions for extended periods of time, opaque labels should be placed over the M2732A window to prevent unintentional erasure.

The recommended erasure procedure for the M2732A is exposure to shortwave ultraviolet light which has a wavelength of 2537 Angstroms (Å). The integrated dose (i.e., UV intensity  $\times$  exposure time) for erasure should be a minimum of 15W-sec/cm2. The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with 12000 µW/cm<sup>2</sup> power rating. The M2732A should be placed within 1 inch of the lamp tubes during erasure. Some lamps have a filter on their tubes which should be removed before erasure.

# **PROGRAMMING**

# D.C. PROGRAMMING CHARACTERISTICS(1)

$T_C = 25^{\circ}C \pm 5^{\circ}C; V_{CC} = 5V \pm 5\%; V_{PP} = 21V \pm 0.5V$

| Symbol          | Donomotor                                   |      | L   | imits               | Test Conditions |                                                 |

|-----------------|---------------------------------------------|------|-----|---------------------|-----------------|-------------------------------------------------|

|                 | Parameter                                   |      | Тур | Max                 | Unit            |                                                 |

| 1 <sub>LI</sub> | Input Current (All Inputs)                  |      |     | 10                  | μΑ              | $V_{IN} = V_{IL} \text{ or } V_{IH}$            |

| VOL             | Output Low Voltage During Verify            |      |     | 0.45                | ٧               | I <sub>OL</sub> = 2.1 mA                        |

| VoH             | Output High Voltage During Verify           | 2.4  |     |                     | ٧               | $I_{OH} = -400 \mu\text{A}$                     |

| loc             | V <sub>CC</sub> Supply Current              |      | 85  | 125                 | mA              |                                                 |

| V <sub>IL</sub> | Input Low Level (All Inputs)                | -0.1 |     | 0.8                 | V               |                                                 |

| V <sub>IH</sub> | Input High Level (All Inputs Except OE/Vpp) | 2.0  |     | V <sub>CC</sub> + 1 | V               |                                                 |

| І <sub>РР</sub> | V <sub>PP</sub> Supply Current              |      |     | 35                  | mA              | $\overline{CE} = V_{IL}, \overline{OE} = V_{I}$ |

### NOTE:

<sup>1.</sup> When programming the M2732A, a 0.1 μF capacitor is required across OE/V<sub>PP</sub> and ground to suppress spurious voltage transients which may damage the device.

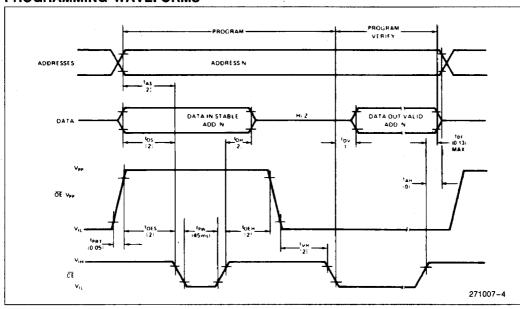

# A.C. PROGRAMMING CHARACTERISTICS

$T_C = 25^{\circ}C \pm 5^{\circ}C; V_{CC} = 5V \pm 5\%; V_{PP} = 21V \pm 0.5V$

| Symbol           | Parameter                             |     | Liı | Test Conditions* |      |                    |

|------------------|---------------------------------------|-----|-----|------------------|------|--------------------|

|                  |                                       | Min | Тур | Max              | Unit | 1 est Conditions   |

| t <sub>AS</sub>  | Address Setup Time                    | 2   |     |                  | μs   |                    |

| toes             | OE Setup Time                         | 2   |     |                  | μs   |                    |

| t <sub>DS</sub>  | Data Setup Time                       | 2   |     |                  | μs   |                    |

| t <sub>AH</sub>  | Address Hold Time                     | 0   |     |                  | μs   |                    |

| t <sub>OEH</sub> | OE Hold Time                          | 2   |     |                  | μs   |                    |

| t <sub>DH</sub>  | Data Hold Time                        | 2   |     |                  | μs   |                    |

| t <sub>DF</sub>  | Chip Enable to Output Float Delay     | 0   |     | 130              | ns   |                    |

| t <sub>DV</sub>  | Data Valid from CE                    |     |     | 1                | μs   | CE = VIL, OE = VIL |

| tpw              | CE Pulse Width During Programming     | 45  | 50  | 55               | ms   |                    |

| terr             | OE Pulse Rise Time During Programming | 50  |     |                  | ns   |                    |

| t <sub>VR</sub>  | V <sub>PP</sub> Recovery Time         | 2   |     |                  | μs   |                    |

### \*A.C. TEST CONDITIONS

### PROGRAMMING WAVEFORMS

### NOTES:

- 1. All times shown in ( ) are minimum and in  $\mu s$  unless otherwise specified.

- 2. The input timing reference level is 1V for a  $V_{IL}$  and 2V for a  $V_{IH}$ .