# M8097BH, M8397BH, M8797BH

## Advanced 16-Bit Microcontroller with 8- or 16-Bit External Bus

The Military M8X97BH is an advanced 16-bit microcontroller family designed for high-speed functions. The CPU supports bit, byte, and word operations. Thirty-two bit double-words are supported for a subset of the instruction set. With a 12 MHz input frequency the M8097BH can do a 16-bit addition in 1.0  $\mu$ s and a 16 x 16-bit multiply or 32/16 divide in 6.25  $\mu$ s. Instruction execution times average 1 to 2  $\mu$ s in typical applications.

Four high-speed trigger inputs are provided to record the times at which external events occur. Six high-speed pulse generator outputs are provided to trigger external events at preset times. The high-speed output unit can simultaneously perform software timer functions. Up to four 16-bit software timers can be in operation at once.

# Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# M8097BH, M8397BH, M8797BH T-49-19-16 ADVANCED 16-BIT MICROCONTROLLER WITH 8- OR 16-BIT EXTERNAL BUS --49-19-59

Military

- M8797BH: an M8097BH with 8K Bytes of On-Chip EPROM

M8397BH: an M8097BH with 8K Bytes of On-Chip ROM

- **232** Byte Register File

- Register-to-Register Architecture

- 10-Bit A/D Converter with S/H

- Five 8-Bit I/O Ports

- 20 Interrupt Sources

- **Pulse-Width Modulated Output**

- **ROM/EPROM Lock**

- **Run-Time Programmable EPROM**

- High Speed I/O Subsystem

- Full Duplex Serial Port

- **■** Dedicated Baud Rate Generator

- 6.25 μs 16 x 16 Multiply

- 6.25 µs 32/16 Divide

- **16-Bit Watchdog Timer**

- Four 16-Bit Software Timers

- **Two 16-Bit Counter/Timers**

- Military Temperature Range: -55°C to +125°C (Tc)

The Military M8X97BH is an advanced 16-bit microcontroller family designed for high-speed functions. The CPU supports bit, byte, and word operations. Thirty-two bit double-words are supported for a subset of the instruction set. With a 12 MHz input frequency the M8097BH can do a 16-bit addition in 1.0  $\mu$ s and a 16 x 16-bit multiply or 32/16 divide in 6.25  $\mu$ s. Instruction execution times average 1 to 2  $\mu$ s in typical applications.

Four high-speed trigger inputs are provided to record the times at which external events occur. Six high-speed pulse generator outputs are provided to trigger external events at preset times. The high-speed output unit can simultaneously perform software timer functions. Up to four 16-bit software timers can be in operation at once.

The on-chip A/D converter includes a Sample and Hold, and converts up to 8 multiplexed analog input channels to 10-bit digital values. With a 12 MHz crystal, each conversion takes 22 µs.

Also provided on-chip are a serial port, a Watchdog Timer, and a pulse-width modulated output signal.

The M8X97BH family members are manufactured using Intel's HMOS-III process technology.

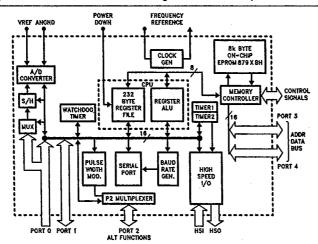

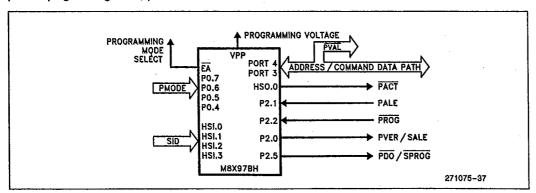

Figure 1, M8X97BH Block Diagram

271075-1

#### FUNCTIONAL OVERVIEW

The following section is an overview of the Military M8X97BH product family.

#### **CPU Architecture**

The M8097BH uses the same address space for both program and data memory, except in the address range from 00H through 0FFH. Data fetches in this range are always to the Register File, while instruction fetches from these locations are directed to external memory. (Locations 00H through 0FFH in external memory are reserved for Intel development systems).

Within the Register File, locations 00H through 17H are register mapped I/O control registers, also referred to as Special Function Registers (SFRs). The rest of the Register File (018H through 0FFH) contains 232 bytes of RAM, which can be referenced as bytes, words, or double-words. This register space allows the user to keep the most frequently-used variables in on-chip RAM, which can be accessed faster than external memory. Locations 0F0H through 0FFH can be preserved during power down via a separate power down pin (VPD).

Outside of the Register File, program memory, data memory, and peripherals can be intermixed. The addresses with special significance are:

| 1 |        |       |                               |

|---|--------|-------|-------------------------------|

|   | -H0000 | 0017H | Register Mapped I/O (SFRs)    |

| ļ | 0018H- | 0019H | Stack Pointer                 |

|   | 1FFEH- | 1FFFH | Ports 3 and 4                 |

|   | 2000H- | 2011H | Interrupt Vectors             |

| 1 | 2012H- | 2017H | Reserved                      |

|   | 2018H  |       | Chip Configuration Byte       |

|   | 2019H  |       | Reserved                      |

|   | 201AH- | 201BH | "Jump to Self" Opcode (27 FE) |

|   | 201CH- | 201FH | Reserved                      |

|   | 2020H- | 202FH | Security Key                  |

|   | 2030H- | 207FH | Reserved                      |

|   | 2080H  |       | Reset Location                |

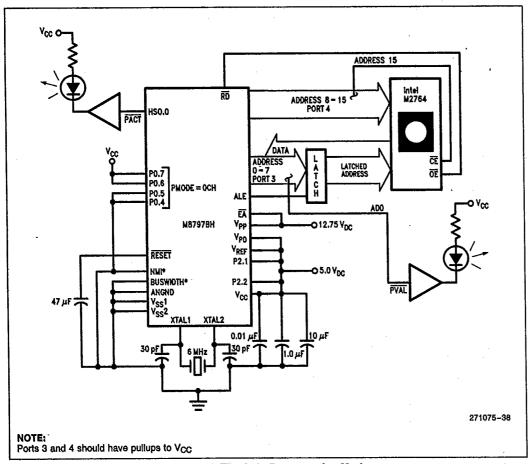

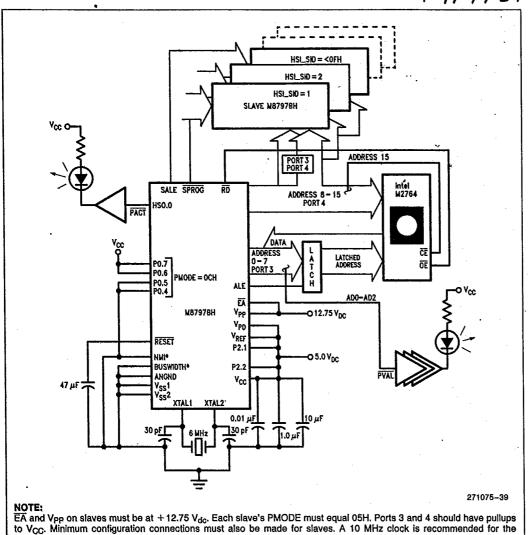

The M8397BH carries 8K bytes of ROM, while the M8797BH has 8K bytes of EPROM. With ROM and EPROM parts, the internal program memory occupies addresses 2000H through 3FFFH. Instruction or data fetches from these addresses access the onchip memory if the EA pin is externally held at 5V. If the EA pin is at 0V, these addresses access off-chip memory. On the M8797BH parts, holding EA at + 12.75V puts the part in Programming Mode, which is described in the EPROM Characteristics Section of this data sheet.

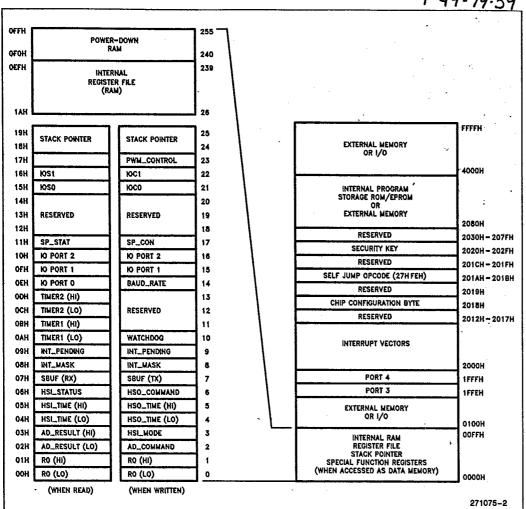

A memory map for the M8X97BH product family is shown in Figure 2.

The RALU (Register/ALU) section consists of a 17bit ALU, the Program Status Word, the Program Counter, and several temporary registers. A key feature of the M8097BH is that it does not use an accumulator. Rather, it operates directly on any register in the Register File. Being able to operate directly on data in the Register File without having to move it into and out of an accumulator results in a significant improvement in execution speed.

In addition to the normal arithmetic and logical functions, the M8X97BH instruction set provides the following special features:

6.25 µs Multiply and Divide Multiple Shift Instruction 3 Operand Instructions Normalize Instruction Software Reset Instruction

All operations on the M8097BH take place in a set number of "State Times." The M8097BH uses a three phase internal clock, so each state time is 3 oscillator periods. With a 12 MHz clock, each state time requires 0.25  $\mu$ s, based on a T<sub>osc</sub> of 83 ns.

#### **Operating Modes**

The M8097BH supports a variety of options to simplify memory systems, interfacing requirements and ready control. Bus flexibility is provided by allowing selection of bus control signal definitions and runtime selection of the external bus width. In addition, several ready control modes are available to simplify the external hardware requirements for accessing slow devices. The Chip Configuration Register is used to store the operating mode information.

intel

M8X97BH ADVANCE INFORMATION

T-49-19-16

Figure 2. Memory Map

4826175 0081908 0

advance information

T-49-19-16 T-49-19-59

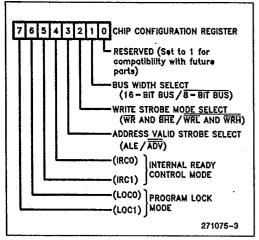

#### **CHIP CONFIGURATION REGISTER (CCR)**

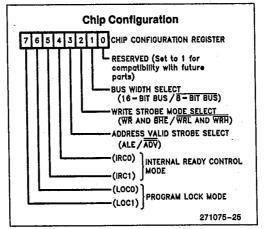

Configuration information is stored in the Chip Configuration Register (CCR). Four of the bits in the register specify the bus control mode and ready control mode. Two bits also govern the level of ROM/EPROM protection and one bit is NANDed with the BUSWIDTH pin every bus cycle to determine the bus size. The CCR bit map is shown in Figure 3, and the functions associated with each bit are described later.

Figure 3. Chip Configuration Register

The CCR is loaded on reset with the Chip Configuration Byte, located at address 2018H. The CCR register is a non-memory mapped location that can only be written to during the reset sequence; once it is loaded it cannot be changed until the next reset occurs. The M8097BH will correctly read this location in every bus mode.

In order to work properly with an 8-bit only system, it is necessary to hold the upper address byte on the address bus throughout the CCB read cycle since an address latch may not be present. However, in a 16-bit system, the M8X97BH must float the high half of the bus to avoid contention with the high data byte during the CCB read. To accomplish a correct read on either 8- or 16-bit busses, the upper address lines are current sensed (during CCB read only) and will be floated if a current of approximately 1 mA or more is detected, indicating a bus contention.

If the  $\overline{EA}$  pin is set to a logical 0, the access to 2018H comes from external memory. If  $\overline{EA}$  is a logical 1, the access comes from internal ROM/EPROM. If  $\overline{EA}$  is +12.5V, the CCR is loaded with a byte from a separate non-memory-mapped location called PCCB (Programming CCB). The Pro-

gramming Mode is described in the EPROM Characteristics Section.

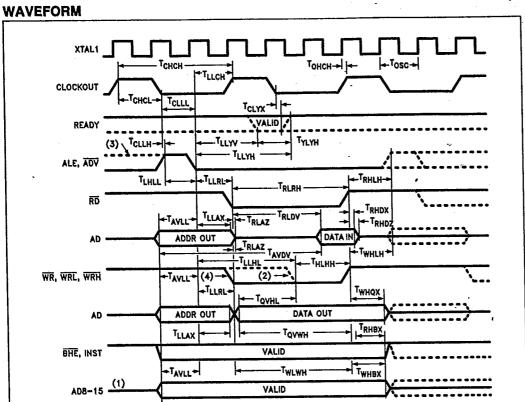

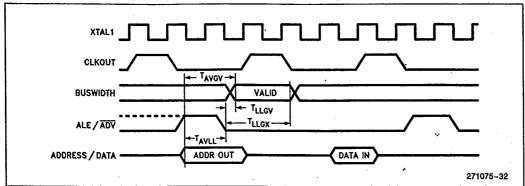

#### **BUS WIDTH**

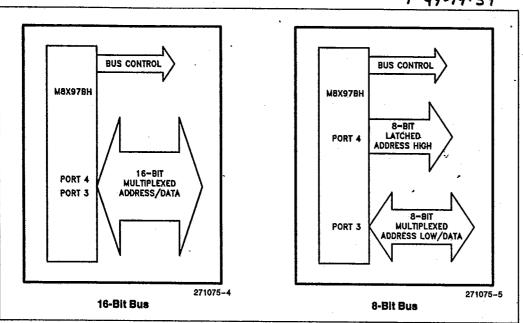

The M8097BH external bus width can be run-time configured to operate as a standard 16-bit multiplexed address/data bus, or as an M8088 minimum mode type 16-bit address/ 8-bit data bus.

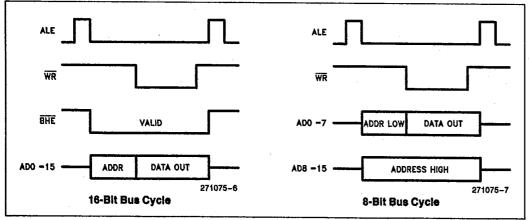

During 16-bit bus cycles, Ports 3 and 4 contain the address multiplexed with data using ALE to latch the address. In 8-bit bus cycles, Port 3 is multiplexed address/data while Port 4 is address bits 8 through 15. The address bits on Port 4 are valid throughout an 8-bit bus cycle. Figure 4 shows the two options,

The bus width can be changed each bus cycle and is controlled using bit 1 of the CCR with the BUS-WIDTH pin. If either CCR.1 or BUSWIDTH is a 0, external accesses will be over a 16-bit address/8-bit data bus. If both CCR.1 and BUSWIDTH are 1s, external accesses will be over a 16-bit address/16-bit data bus. Internal accesses are always 16-bits wide.

The bus width can be changed every external bus cycle if a 1 was loaded into CCR bit 1 at reset. If this is the case, changing the value of the BUSWIDTH pin at run-time will dynamically select the bus width. For example, the user could feed the INST line into the BUSWIDTH pin, thus causing instruction accesses to be word wide from EPROMs while data accesses are byte wide to and from RAMs. A second example would be to place an inverted version of address bit 15 on the BUSWIDTH pin. This would make half of external memory word wide, while half is byte wide.

Since BUSWIDTH is sampled after address decoding has had time to occur, even more complex memory maps could be constructed. See the timing specifications for an exact description of BUSWIDTH timings. The bus width will be determined by bit 1 of the CCR alone on 48-pin parts since they do not have a BUSWIDTH pin.

When using an 8-bit bus, some performance degradation is to be expected. On the M8097BH, instruction execution times with an 8-bit bus will slow down if any of three conditions occur. First, word writes to external memory will cause the executing instruction to take two extra state times to complete. Second, word reads from external memory will cause a one state time extension of instruction execution time. Finally, if the prefetch queue is empty when an instruction fetch is requested, instruction execution is lengthened by one state time for each byte that must be externally acquired (worst case is the number of bytes in the instruction minus one).

T 49-19-16 T 99-19-59

Figure 4. Bus Width Options

#### **BUS CONTROL**

The M8097BH can be made to provide bus control signals of several types. Three control lines have dual functions designed to reduce external hardware. Bits 2 and 3 of the CCR specify the functions performed by these control lines.

#### Standard Bus Control

If CCR bits 2 and 3 are 1s, then the standard M8097BH control signals WR, BHE and ALE are provided (Figure 5). WR will come out for every write. BHE will be valid throughout the bus cycle and can be combined with WR and address line 0 to form WRL and WRH. ALE will rise as the address starts to come out, and will fall to provide the signal to externally latch the address.

Figure 5. Standard Bus Control

#### Write Strobe Mode

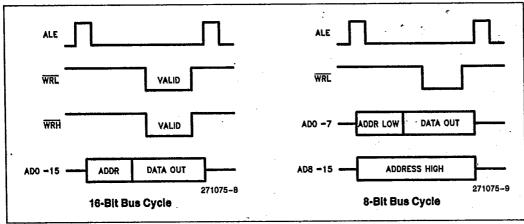

The Write Strobe Mode eliminates the necessity to externally decode for odd or even byte writes. If CCR bit 2 is a 0, and the bus is in a 16-bit cycle, WRL and WRH signals are provided in place of WR and BHE (Figure 6). WRL will go low for all byte writes to an even address and all word writes. WRH will go low for all byte writes to an odd address and all word writes.

In an 8-bit bus cycle WRL will go active for all writes.

A unique ability of the bus controller is to utilize the CCR to select at reset time the width of the  $\overline{\text{WR}}$  signal by changing the position of the falling edge relative to the memory cycle. Clearing bit 2 of the CCR to 0 will enable a shorter  $\overline{\text{WR}}$  width. This is useful when interfacing to devices that latch on the falling edge of  $\overline{\text{WR}}$ .

Figure 6. Write Strobe Mode

**inte**l

M8X97BH

ADVANCE INFORMATION

T.49.19.16 T.49.19.59

#### Address Valid Strobe Mode

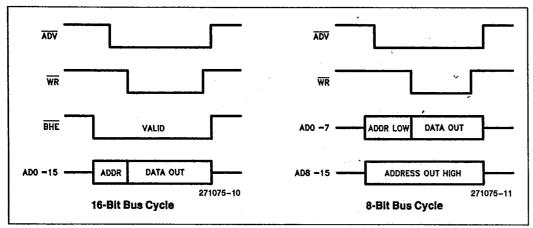

If CCR bit 3 is a 0, then an Address Valid Strobe is provided in the place of ALE (Figure 7). When the Address Valid Mode is selected, ADV will go low after an external address is set up. It will stay low until the end of the bus cycle, where it will go inactive high. This can be used to provide a chip select for external memory.

Figure 7. Address Valid Strobe Mode

#### **Address Valid with Write Strobe**

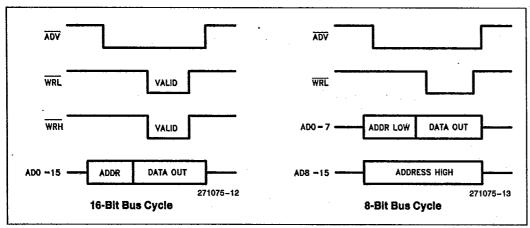

If both CCR bits 2 and 3 are 0s, both the Address Valid Strobe and the Write Strobes will be provided for bus control. Figure 8 shows these signals.

Figure 8. Write Strobe with Address Valid Strobe

ADVANCE INFORMATION

T 99-19-16 T 99-19-59

#### **READY CONTROL**

To simplify ready control, four modes of internal ready control logic have been provided. The modes are chosen by properly configuring bits 4 and 5 of the CCR.

The internal ready control logic can be used to limit the number of wait states that slow devices can insert into the bus cycle. When the READY pin is pulled low, wait states will be inserted into the bus cycle until the READY pin goes high, or the number of wait states equals the number specified by CCR bits 4 and 5, whichever comes first. Table 1 shows the number of wait states that can be selected. Internal ready control can be disabled by loading 11 into bits 4 and 5 of the CCR.

**Table 1. Internal Ready Control**

|      | IRC0 Description  O Limit to 1 Wait State  1 Limit to 2 Wait States  O Limit to 3 Wait States  1 Disable Internal Ready | •                              |  |  |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|--|--|--|--|--|

| IRC1 | IRC0                                                                                                                    | Description                    |  |  |  |  |  |  |  |  |

| 0    | 0                                                                                                                       | Limit to 1 Wait State          |  |  |  |  |  |  |  |  |

| 0    | 1                                                                                                                       | Limit to 2 Wait States         |  |  |  |  |  |  |  |  |

| 1    | 0                                                                                                                       | Limit to 3 Wait States         |  |  |  |  |  |  |  |  |

| 1    | 1                                                                                                                       | Disable Internal Ready Control |  |  |  |  |  |  |  |  |

|      |                                                                                                                         |                                |  |  |  |  |  |  |  |  |

This feature provides for simple ready control. For example, every slow memory chip select line could be ORed together and be connected to the READY pin with CCR bits 4 and 5 programmed to give the proper number of wait states to the slow devices.

#### **ROM/EPROM LOCK**

Four modes of program memory lock are available on the M8397BH and M8797BH parts. CCR bits 6 and 7 (LOC0, LOC1) select whether internal program memory can be read (or written in EPROM parts) by a program executing from external memory. The modes are shown in Table 2. Internal ROM/EPROM addresses 2020H through 3FFFH are protected from reads while 2000H through 3FFFH are protected from writes, as set by the CCR.

**Table 2. Program Lock Modes**

| LOC1 | LOC0 | Protection               |

|------|------|--------------------------|

| 0    | 0    | Read and Write Protected |

| 0    | 1    | Read Protected           |

| 1    | 0    | Write Protected          |

| 1    | 1    | No Protection            |

Only code executing from internal memory can read protected internal memory, while a write protected memory can not be written to, even from internal execution. As a result of M8097BH prefetching of instructions, however, accesses to protected memory are not allowed for instructions located above 3FFAH. Note that the interrupt vectors and the CCR are not protected.

To provide ROM/EPROM lock while allowing verification and testing, the M8397BH and M8797BH require security key verification before programming or test modes are allowed to read protected memory. More information on ROM/EPROM Lock can be found in the EPROM Characteristics section.

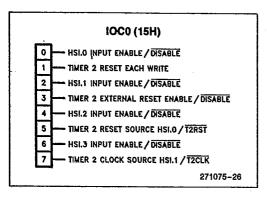

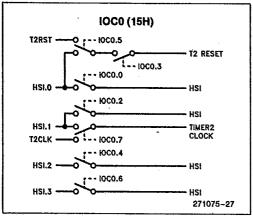

#### High Speed I/O Unit (HSIO)

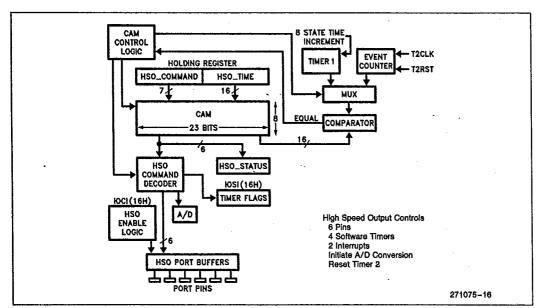

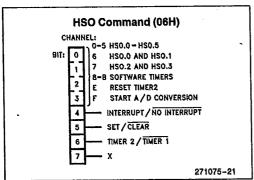

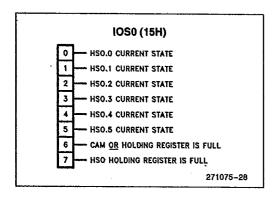

The HSIO unit consists of the High Speed Input Unit (HSI), the High Speed Output Unit (HSO), one counter and one timer. "High Speed" denotes that the units can perform functions related to the timers without CPU intervention. The HSI records times when events occur and the HSO triggers events at pre-programmed times.

All actions within the HSIO unit are synchronized to the timers. The two 16-bit timer/counter registers in the HSIO unit are cleared on chip reset and can be programmed to generate an interrupt on overflow. The Timer 1 register is automatically incremented every 8 state times (every 2.0  $\mu s$ , with a 12 MHz clock). The Timer 2 register can be programmed to count transitions on either the T2CLK pin or HSI.1 pin. It is incremented on both positive and negative edges of the selected input line. In addition to being cleared by reset, Timer 2 can also be cleared in software or by signals from input pins T2RST or HSI.0. Neither of these timers is required for either the Watchdog Timer or the serial port.

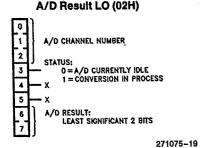

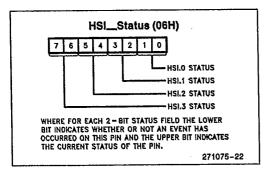

The High Speed Input (HSI) unit can detect transitions on any of its 4 input lines. When one occurs it records the time (from Timer 1) and which input lines made the transition. This information is recorded with 2  $\mu$ s (12 MHz system) resolution and stored in an 8-level FIFO. The unit can be programmed to look for four types of events, as shown in Figure 9. It can activate the HSI Data Available interrupt either when the Holding Register is loaded or the 6th FIFO entry has been made. Each input line can be individually enabled or disabled to the HSI unit by software.

## M8X97BH ADVANCE INFORMATION

T.49.19.16 T.49.19.59 **HSI Trigger Options** HI TO LO FIFO INTERRUPT TIMER HSI ENABLE CONTROL LOGIC LO TO HE LOGIC 4\$ DIVIDE BY 8 COUNTER INPUT CHANGE DETECTOR 7×20 BIT FIFO PORT BUFFERS 무무무무 20 HSI\_MODE HSI\_STATUS HOLDING REGISTER EVERY EIGHTH POSITIVE TRANSITION 16. 271075-14 HSI\_TIME 271075-15

Figure 9. High Speed Input Unit

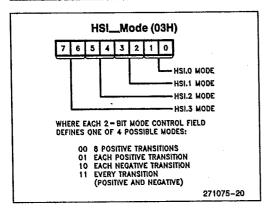

The High Speed Output (HSO) unit is shown in Figure 10. It can be programmed to set or clear any of its 6 output lines, reset Timer 2, trigger an A/D conversion, or set one of 4 Software Timer flags at a programmed time. An interrupt can be enabled for any of these events. Either Timer 1 or Timer 2 can be referenced for the programmed time value and up to 8 commands for preset actions can be stored

in the CAM (Content Addressable Memory) file at any one time. As each action is carried out at its preset time that command is removed from the CAM making space for another command. HSO.4 and HSO.5 are shared with the HSI unit as HSI.2 and HSI.3, and can be individually enabled or disabled as outputs.

Figure 10. High Speed Output Unit

49-19-16

interprocessor communication.

#### Standard I/O Ports

There are 5 8-bit I/O ports on the M8097BH in addition to the High Speed I/O lines.

Port 0 is an input-only port which shares its pins with the analog inputs to the A/D converter. The port can be read digitally and/or, by writing to the A/D Command Register, one of the lines can be selected as the input to the A/D converter. Port 0 is also used to input mode information on EPROM parts operating in the Programming Mode.

Port 1 is a quasi-bidirectional I/O port. "Quasi-bidirectional" means the port pin has a weak internal pullup that is always active and an internal pulldown which can either be on (to output a 0) or off (to output a 1). This configuration allows the pin to be used as either an input or an output without using a data direction register. In parallel with the weak internal pullup is a much stronger internal pullup that is activated for one state time when the pin is internally driven from 0 to 1. This is done to speed up the 0-to-1 transition time.

Port 2 is a multi-functional port. Two of the pins (P2.6, 2.7) are quasi-bidirectional while the remaining six are shared with other functions in the M8097BH, as shown in Table 3. Port 2 is also used for control signals by EPROM parts operating in the Programming Mode.

**Table 3. Port 2 Pin Functions**

| Port | Function. | Alternate Function           |   |

|------|-----------|------------------------------|---|

| P2.0 | Output    | TXD (Serial Port Transmit)   |   |

| P2.1 | Input     | RXD (Serial Port Receive)    |   |

| P2.2 | Input     | EXTINT (External Interrupt)  |   |

| P2.3 | Input     | T2CLK (Timer 2 Clock)        | - |

| P2.4 | Input     | T2RST (Timer 2 Reset)        |   |

| P2.5 | Output    | PWM (Pulse Width Modulation) |   |

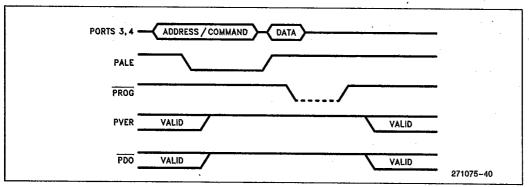

Ports 3 and 4 are bi-directional I/O ports with open drain outputs. These pins are also used as the multiplexed address/data bus when accessing external memory, in which case they have strong internal pullups. The internal pullups are only used during external memory read or write cycles when the pins are outputting address or data bits. At any other time, the internal pullups are disabled. When used as a system bus, Ports 3 and 4 can be configured to be either a multiplexed 16-bit address/data bus or a multiplexed 16-bit address/ 8-bit data bus. EPROM parts also use Ports 3 and 4 to pass programming commands, addresses, data and status.

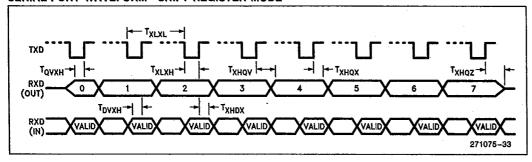

#### **Serial Port**

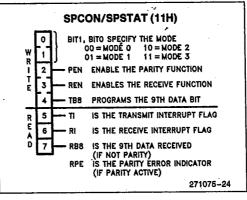

The serial port is compatible with the MCS-51 family, (M8051, M8031 etc.), serial port. It is full duplex, and

double-buffered on receive. There are 3 asynchronous modes and 1 synchronous mode of operation for the serial port. The asynchronous modes allow for 8 or 9 bits of data with even parity optionally inserted for one of the data bits, Selective interrupts based on the 9th data bit are available to support

Baud rates in all modes are determined by an independent 16-bit on-chip baud rate generator. Either the XTAL1 pin or the T2CLK pin can be used as the input to the baud rate generator. The maximum baud rate in the asynchronous mode is 187.5 KBaud. The maximum baud rate in the synchronous mode is 1.5 MBaud.

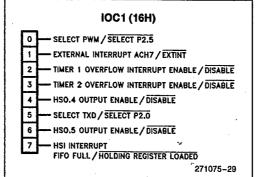

#### **Pulse Width Modulator (PWM)**

The PWM output shares a pin with port bit P2.5. When the PWM output is selected, this pin outputs a pulse train having a fixed period of 256 state times, and a programmable width of 0 to 255 state times. The width is programmed by loading the desired value, in state times, to the PWM Control Register.

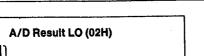

#### A/D Converter with Sample and Hold

The on-chip analog-to-digital acquisition system is a monotonic successive approximation converter with the sample and hold, multiplexer, and D/A ladder circuits built into the silicon. This system can multiplex up to eight channels of conversion to 10 bits of resolution (1024 unique codes). It has a fixed conversion time of 88 state times which includes the 4 state time sample window. With a 12 MHz clock the conversion would take 22 µs, of which one microsecond is the sample window. The sample window period begins 4 state times after the conversion is triggered. A 2 pF capacitance is charged from the input signal during this sample window period.

In many applications it is less critical to record the absolute accuracy of an input, than it is to resolve that some determinable change has occurred. This is an acceptable approach as long as the converter is guaranteed to be monotonic and has no missing codes, as is the case for the M8X97BH. This means that increasing input voltages produce adjacent and unique output codes that are also increasing. Decreasing input voltages are guaranteed to produce adjacent and unique output codes that are also decreasing. There exists on the M8X97BH for each 10-bit output code a unique input voltage range that produces that code only, with a repeatability of typically  $\pm 0.25$  LSB's (1.5 mV).

The M8X97BH datasheet guarantees that the maximum Differential Non-Linearity will be 2 analog LSB's, or 10 mV (the minimum is zero). Differential

ADVANCE INFORMATION

T.49.19.16 T.49.19.59

non-linearity specifies the maximum difference between the actual code widths seen in a converter and what those code widths would be in an ideal (perfect) converter. In the M8X97BH 10-bit converter, the code widths are ideally 5 mV (5.12 VREF/ 1024). If such a converter is specified to have a maximum Differential Non-Linearity of 10 mV, then the maximum code width will be no greater than 10 mV larger than ideal, or 15 mV. This indicates to the user how much the input voltage may have changed under worst case conditions to produce a one count change in a particular 10-bit conversion. Due to the fact that the M8X97BH converter has no missing codes, the minimum code width will always be greater than zero. The differential non-linearity error on a particular code width is compensated for by other code widths in the transfer function such that 1024 unique steps occur. The actual code widths in the M8X97BH converter typically vary from about 2.5 mV to 7.5 mV.

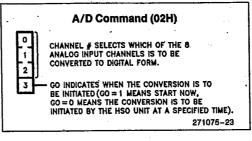

The analog input must be in the range of zero to  $V_{REF}$  (nominally,  $V_{REF}=5V$ ). This input can be selected from 8 analog inputs which connect to the same pins as PORT 0. A conversion can be initiated either by setting the control bit in the A/D Command Register (Address 02Hex), or by programming the High Speed Output CAM to trigger the conversion at some specified time with sampling intervals occurring accurate to  $\pm 50$  ns. (See AP-406, "MCS-96 Analog Acquisition Primer" for further information.)

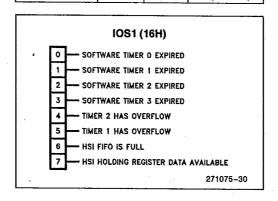

#### Interrupts

The M8097BH has 20 interrupt sources which vector through 8 interrupt vectors. A 0-to-1 transition from any of the sources sets a corresponding bit in the

Interrupt Pending register. The content of the Interrupt Mask register determines if a pending interrupt will be serviced or not. If it is to be serviced, the CPU pushes the current Program Counter onto the stack and reloads it with the vector corresponding to the desired interrupt, The interrupt vectors are located in addresses 2000H through 2011H, as shown in Figure 11.

The maximum transition speed of the interrupt inputs is limited to one transition per state time (250 ns at 12 MHz). Since interrupt recognition is based up on a zero to one transition on the pin, a normally high signal must go low for one state time, and then transition high in a subsequent state time. A normally low input signal must go high for one state time, and not return low until a subsequent state time.

|                            | Vector         | Location      |                |

|----------------------------|----------------|---------------|----------------|

| Vector                     | (High<br>Byte) | (Low<br>Byte) | Priority       |

| Software                   | 2011H          | 2010H         | Not Applicable |

| Extint                     | 200FH          | 200EH         | 7 (Highest)    |

| Serial Port                | 200DH          | .200CH        | 6              |

| Software<br>Timers         | 200BH          | 200AH         | 5              |

| HSI.0                      | 2009H          | 2008H         | 4              |

| High Speed<br>Outputs      | 2007H          | 2006H         | 3              |

| HSI Data<br>Available      | 2005H          | 2004H         | 2              |

| A/D Conversion<br>Complete | 2003H          | 2002H         | 1              |

| Timer Overflow             | 2001H          | 2000H         | 0 (Lowest)     |

Figure 11. Interrupt Vectors

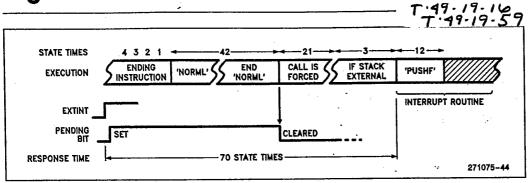

Figure 11a. Interrupt Response Time

At the end of the interrupt routine the RET instruction pops the program counter from the stack and execution continues where it left off. It is not necessary to store and replace registers during interrupt routines as each routine can be set up to use a different section of the Register File. This feature of the architecture provides for very fast context switching. While the M8097BH has a single priority level in the sense that any interrupt may itself be interrupted, a priority structure exists for resolving simultaneously pending interrupts, as indicated in Figure 11a. Since the interrupt pending and interrupt mask registers can be manipulated in software, it is possible to dynamically alter the interrupt priorities to suit the users software.

#### **Watchdog Timer**

The Watchdog Timer is a 16-bit counter which, once started, is incremented every state time. If not

cleared before it overflows, the RESET pin will be pulled down for two state times, causing the system to be reinitialized. In a 12 MHz system, the Watchdog Timer overflows after 16 ms.

This feature is provided as a means of graceful recovery from a software upset. The counter must be cleared by the software before it overflows, or else the system assumes an upset has occurred and activates RESET. Once the Watchdog Timer is started it cannot be turned off by software. The filp-flop which enables the Watchdog Timer has been designed to maintain its state through  $V_{\rm CC}$  glitches to as low as 0V or as high as 7V for 1  $\mu s$  to 1 ms.

To start the Watchdog Timer, or to clear it, one writes 1EH followed by 0E1H to the WDT address (000AH). The Watchdog cannot be stopped once it is started unless the system is reset.

ADVANCE INFORMATION

intel

M8X97BH

T.49.19.16 T.49.19.59

#### **PACKAGING**

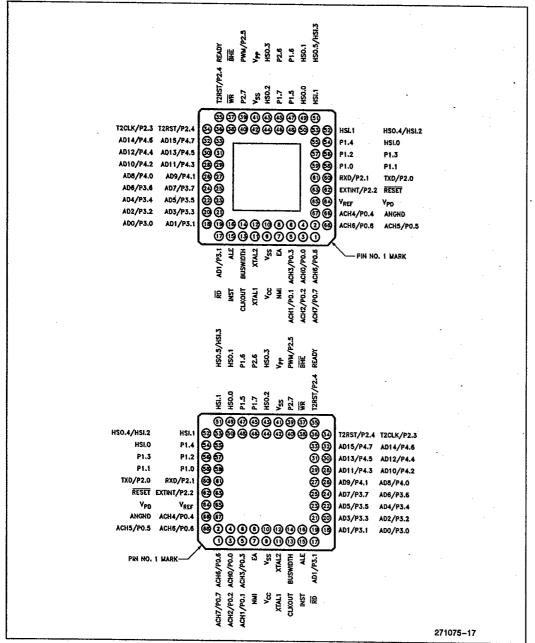

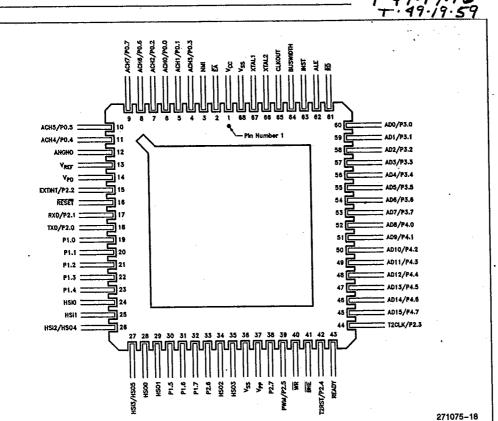

The M8X97BH family is available in a ceramic pin grid array, shown in Figure 12, and a leaded ceramic quad pack shown in Figure 13. A comparison of the pinouts for both of these package types is shown in Figure 14.

Figure 12. Pin Grid Array Pinout

advance information

intel

Figure 13. 68-Lead Ceramic Quad Pack Pinout

| PGA              | CQP    | Description              | PGA  | CQP | Description                | PGA      | CQP | Description |

|------------------|--------|--------------------------|------|-----|----------------------------|----------|-----|-------------|

| 1                | 9      | ACH7/P0.7                | 24   | 54  | AD6/P3,6                   | 47       | 31  | P1.6        |

| ا و ا            | ă      | ACH6/P0.6                | 25   | 53  | AD7/P3.7                   | 48       | 30  | P1.5        |

| 2                | 8<br>7 | ACH2/P0.2                | 26   | 52  | AD8/P4.0                   | 49       | 29  | HSO.1       |

|                  | 6      | ACH0/P0.0                | 27   | 51  | AD9/P4.1                   | 50       | 28  | HSO.0       |

| 5                | 6<br>5 | ACH1/P0.1                | 28   | 50  | AD10/P4.2                  | 51       | 27  | HSO.5/HSI.3 |

| 4<br>5<br>6<br>7 | 4      | ACH3/P0.3                | 29   | 49  | AD11/P4.3                  | 52       | 26  | HSO.4/HSI.2 |

| 1 7              | з      | NMI                      | 30   | 48  | AD12/P4.4                  | 53       | 25  | HSI.1       |

| l à              | ž      | EA                       | 31   | 47  | AD13/P4.5                  | 54       | 24  | HSI.0       |

| 8                | 1      | V <sub>CC</sub>          | 32   | 46  | AD14/P4.6                  | 55       | 23  | P1.4        |

| 10               | 68     | Vee                      | 33   | 45  | AD15/P4.7                  | 56       | 22  | P1.3        |

| 111              | 67     | V <sub>SS</sub><br>XTAL1 | 34   | 44  | T2CLK/P2.3                 | 57       | 21  | P1.2        |

| 12               | 66     | XTAL2                    | 35   | 43  | READY                      | 58       | 20  | P1.1        |

| 13               | 65     | CLKOUT                   | 36   | 42  | T2RST/P2.4                 | 59       | 19  | P1.0        |

| 14               | 64     | BUSWIDTH                 | 37   | 41  | BHE                        | 60       | 18  | TXD/P2.0    |

| 15               | 63     | INST                     | 38   | 40  | WR                         | 61       | 17  | RXD/P2.1    |

| 16               | 62     | ALE                      | 39   | 39  | PWM/P2.5                   | 62       | 16  | RESET       |

| 17               | 61     | RD                       | 40   | 38  | P2.7                       | 63       | 15  | EXTINT/P2.2 |

| 18               | 60     | AD0/P3.0                 | 41   | 37  | Vpp                        | 64       | 14  | $V_{PD}$    |

| 19               | 59     | AD1/P3.1                 | 42   | 36  | V <sub>SS</sub> `<br>HSO.3 | 65       | 13  | VREF        |

| 20               | 58     | AD2/P3.2                 | 43   | 35  | HŠŌ.3                      | 66       | 12  | ANGND       |

| 21               | 57     | AD3/P3.3                 | 44   | 34  | HSO.2                      | 67       | 11  | ACH4/P0.4   |

| 22               | 56     | AD4/P3.4                 | 45   | 33  | P2.6                       | 68       | 10  | ACH5/P0.5   |

| 23               | 55     | AD5/P3.5                 | 46 _ | 32  | P1.7                       | <u> </u> |     |             |

Figure 14. PGA & CQP Comparison Pinout

20E **D M8X97BH**  **=** 4826175 0081919 5 **=**

ADVANCE INFORMATION

T.49.19.16 T.49.19.59

## PIN DESCRIPTIONS

| Symbol            | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc               | Main supply voltage (5V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Vss               | Digital circuit ground (0V). There are two VSS pins, both of which must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>PD</sub> ´ | RAM standby supply voltage (5V). This voltage must be present during normal operation. In a Power Down condition (i.e. $V_{CC}$ drops to zero), if RESET is activated before $V_{CC}$ drops below spec and $V_{PD}$ continues to be held within spec., the top 16 bytes in the Register File will retain their contents. RESET must be held low during the Power Down and should not be brought high until $V_{CC}$ is within spec and the oscillator has stabilized.                                                                   |

| V <sub>REF</sub>  | Reference voltage for the A/D converter (5V). V <sub>REF</sub> is also the supply voltage to the analog portion of the A/D converter and the logic used to read Port 0.                                                                                                                                                                                                                                                                                                                                                                 |

| ANGND             | Reference ground for the A/D converter. Must be held at nominally the same potential as Vss.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>PP</sub>   | Programming voltage for the EPROM parts, it should be + 12.75V for programming. This pin must be left floating in the application circuit.                                                                                                                                                                                                                                                                                                                                                                                              |

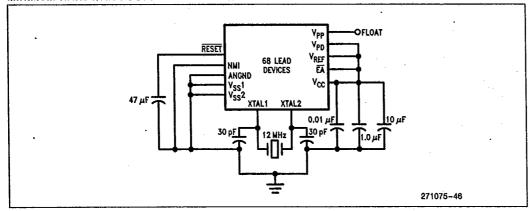

| XTAL1             | Input of the oscillator inverter and of the internal clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| XTAL2             | Output of the oscillator inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CLKOUT            | Output of the internal clock generator. The frequency of CLKOUT is 1/3 the oscillator frequency. It has a 33% duty cycle.                                                                                                                                                                                                                                                                                                                                                                                                               |

| RESET             | Reset input to the chip. Input low for at least 2 state times to reset the chip. The subsequent low-to-high transition re-synchronizes CLKOUT and commences a 10-state-time sequence in which the PSW is cleared, a byte read from 2018H loads CCR, and a jump to location 2080H is executed. Input high for normal operation. RESET has an internal pullup.                                                                                                                                                                            |

| BUSWIDTH          | Input for bus width selection. If CCR bit 1 is a one, this pin selects the bus width for the bus cycle in progress. If BUSWIDTH is a 1, a 16-bit bus cycle occurs. If BUSWIDTH is a 0 an 8-bit cycle occurs. If CCR bit 1 is a 0, the bus is always an 8-bit bus. This pin is the TEST pin on M8X97 parts. Systems with TEST tied to VCC do not need to change. If this pin is left unconnected, it will rise to VCC.                                                                                                                   |

| NMI               | A positive transition causes a vector to external memory location 0000H. External memory from 00H through 0FFH is reserved for Intel development systems.                                                                                                                                                                                                                                                                                                                                                                               |

| INST              | Output high during an external memory read indicates the read is an instruction fetch. INST is valid throughout the bus cycle.                                                                                                                                                                                                                                                                                                                                                                                                          |

| ĒĀ                | Input for memory select (External Access). EA equal to a TTL-high causes memory accesses to locations 2000H through 3FFFH to be directed to on-chip ROM/EPROM. EA equal to a TTL-low causes accesses to these locations to be directed to off-chip memory. EA = +12.5V causes execution to begin in the Programming Mode. EA has an internal pulldown, so it goes to 0 unless driven otherwise.                                                                                                                                         |

| ALE/ĀĎŸ           | Address Latch Enable or Address Valid output, as selected by CCR. Both pin options provide a latch to demultiplex the address from the address/data bus. When the pin is ADV, it goes inactive high at the end of the bus cycle. ADV can be used as a chip select for external memory. ALE/ADV is activated only during external memory accesses.                                                                                                                                                                                       |

| RD                | Read signal output to external memory. RD is activated only during external memory reads.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| WR/WRC            | Write and Write Low output to external memory, as selected by the CCR. WR will go low for every external write, while WRL will go low only for external writes where an even byte is being written. WR/WRL is activated only during external memory writes.                                                                                                                                                                                                                                                                             |

| BHE/WAH           | Bus High Enable or Write High output to external memory, as selected by the CCR. BHE = 0 selects the bank of memory that is connected to the high byte of the data bus. A0 = 0 selects the bank of memory that is connected to the low byte of the data bus. Thus accesses to a 16-bit wide memory can be to the low byte only (A0 = 0, BHE = 1), to the high byte only (A0 = 1, BHE = 0), or both bytes (A0 = 0, BHE = 0). If the WRH function is selected, the pin will go low if the bus cycle is writing to an odd memory location. |

intel

**M8X97BH**

ADVANCE INFORMATION

T.49.19.16 T.49.19.59

#### PIN DESCRIPTIONS (Continued)

| Symbol        | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READY         | Ready input to lengthen external memory cycles, for interfacing to slow or dynamic memory, or for bus sharing. If the pin is high, CPU operation continues in a normal manner. If the pin is low prior to the falling edge of CLKOUT, the memory controller goes into a wait mode until the next positive transition in CLKOUT occurs with READY high. The bus cycle can be lengthened by up to 1 µs. When the external memory is not being used, READY has no effect. Internal control of the number of wait states inserted into a bus cycle held not ready is available through configuration of CCR, READY has a weak internal pullup, so it goes to 1 unless externally pulled low. |

| HSI           | Inputs to High Speed Input Unit. Four HSI pins are available: HSI.0, HSI.1, HSI.2, and HSI.3. Two of them (HSI.2 and HSI.3) are shared with the HSO Unit. The HSI pins are also used as inputs by EPROM parts in Programming Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| HSO           | Outputs from High Speed Output Unit. Six HSO pins are available: HSO.0, HSO.1, HSO.2, HSO.3, HSO.4, and HSO.5. Two of them (HSO.4 and HSO.5) are shared with the HSI Unit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Port 0        | 8-bit high impedance input-only port. These pins can be used as digital inputs and/or as analog inputs to the on-chip A/D converter. These pins are also a mode input to EPROM parts in the Programming Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Port 1        | 8-bit quasi-bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Port 2        | 8-bit multi-functional port. Six of its pins are shared with other functions in the M8097BH, the remaining 2 are quasi-bidirectional. These pins are also used to input and output control signals on EPROM parts in Programming Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Ports 3 and 4 | 8-bit bi-directional I/O ports with open drain outputs. These pins are shared with the multiplexed<br>address/data bus which has strong internal pullups. Ports 3 and 4 are also used as a command;<br>address and data path by EPROM parts operating in the Programming Mode.                                                                                                                                                                                                                                                                                                                                                                                                           |

#### INSTRUCTION SET

The M8097BH instruction set makes use of six addressing modes as described below:

**DIRECT**—The operand is specified by an 8-bit address field in the instruction. The operand must be in the Register File or SFR space (locations 0000H through 00FFH).

**IMMEDIATE**—The operand itself follows the opcode in the instruction stream as immediate data. The immediate data can be either 8-bits or 16-bits as required by the opcode.

INDIRECT—An 8-bit address field in the instruction gives the word address of a word register in the Register File which contains the 16-bit address of the operand. The operand can be anywhere in memory

INDIRECT WITH AUTO-INCREMENT—Same as Indirect, except that, after the operand is referenced, the word register that contains the operand's address is incremented by 1 if the operand is a byte, or by 2 if the operand is a word.

INDEXED (LONG AND SHORT)—The instruction contains an 8-bit address field and either an 8-bit or a 16-bit displacement field. The 8-bit address field gives the word address of a word register in the Register File which contains a 16-bit base address. The 8- or 16-bit displacement field contains a signed displacement that will be added to the base address to produce the address of the operand. The operand can be anywhere in memory.

The M8097BH contains a zero register at word address 0000H (and which contains 0000H). This register is available for performing comparisons and for use as a base register in indexed addressing. This effectively provides direct addressing to all 64K of memory.

In the M8097BH, the Stack Pointer is at word address 0018H in the Register File. If the 8-bit address field contains 18H, the Stack Pointer becomes the base register. This allows direct accessing of variables in the stack.

The following tables list the M8097BH instructions, their opcodes, and execution times.

intal

**M8X97BH**

## ADVANCE INFORMATION

T·49-19-16 T·49-19-59

#### **Instruction Summary**

| Mnemonic        | Oper- | Operation (Note 1)                                                                      |          |          | FI | ngs      |          |          | Notes |

|-----------------|-------|-----------------------------------------------------------------------------------------|----------|----------|----|----------|----------|----------|-------|

|                 | ands  | opeanon (Note 1)                                                                        | Z        | N        | C  | ٧        | VΤ       | ST       | HOIES |

| ADD/ADDB        | 2     | D ← D + A                                                                               | 1        | 10       | 1  | 10       | 1        | -        |       |

| ADD/ADDB        | 3     | D ← B + A                                                                               | <b>1</b> | ~        | 10 | 10       | 1        | ı        |       |

| ADDC/ADDCB      | 2     | $D \leftarrow D + A + C$                                                                | 1        | 7        | 1  | 10       | 1        | 1        |       |

| SUB/SUBB        | 2     | D ← D – A                                                                               | V        | 1        | 1  | 11       | 1        | _        |       |

| SUB/SUBB        | 3     | D ← B − A                                                                               | 10       | 1        | 10 | 10       | 1        | -        | -     |

| SUBC/SUBCB      | 2     | $D \leftarrow D - A + C - 1$                                                            | 1        | 1        | 1  | 1        | 1        |          |       |

| CMP/CMPB        | 2     | D – A                                                                                   | 10       | 1        | 10 | 11       | 1        | ı        |       |

| MUL/MULU        | 2     | D, D + 2 ← D * A                                                                        | _        | 1        | _  | _        | _        | ٠?       | 2     |

| MUL/MULU        | 3     | D, D + 2 ← B * A                                                                        | _        | _        | _  | <b>—</b> | _        | ?        | 2     |

| MULB/MULUB      | 2     | D, D + 1 ← D*A                                                                          | _        | _        | _  | _        | _        | ?        | 3     |

| MULB/MULUB      | 3     | D, D + 1 ← B * A                                                                        | _        | _        |    |          | _        | ?        | 3     |

| DIVU            | 2     | $D \leftarrow (D, D + 2)/A, D + 2 \leftarrow remainder$                                 |          | _        | _  | 10       | <b>↑</b> | -        | 2     |

| DIVUB           | 2     | $D \leftarrow (D, D + 1)/A, D + 1 \leftarrow remainder$                                 | _        | -        | _  | 10       | 1        | _        | 3     |

| DIV             | 2     | $D \leftarrow (D, D + 2)/A, D + 2 \leftarrow remainder$                                 | _        | _        | _  | ?        | Ť        | _        |       |

| DIVB            | 2     | $D \leftarrow (D, D + 1)/A, D + 1 \leftarrow remainder$                                 |          |          | _  | ?        | 1        | _        |       |

| AND/ANDB        | 2     | D ← D and A                                                                             | 10       | 10       | 0  | 0        | _        | _        |       |

| AND/ANDB        | 3     | D ← B and A                                                                             | 10       | 11       | 0  | 0        | -        | _        |       |

| OR/ORB          | 2     | D ← DorA                                                                                | 10       | 10       | 0  | 0        | _        | _        |       |

| XOR/XORB        | 2     | D ← D (excl. or) A                                                                      | 1        | 10       | 0  | 0        | _        |          |       |

| LO/LOB          | 2     | D ← A                                                                                   | _        | _        | _  | _        | _        | _        |       |

| ST/STB          | 2     | A ← D                                                                                   | _        | _        | _  | _        |          | _        |       |

| LDBSE           | 2     | $D \leftarrow A; D + 1 \leftarrow SIGN(A)$                                              | _        | _        |    |          | _        |          | 3, 4  |

| LDBZE           | 2     | D ← A; D + 1 ← 0                                                                        | _        | _        | _  | _        | _        | _        | 3.4   |

| PUSH            | . 1   | SP ← SP - 2; (SP) ← A                                                                   | _        | -        | _  | _        | _        | _        |       |

| POP             | 1     | A ← (SP); SP ← SP + 2                                                                   |          |          | _  | _        | _        | _        |       |

| PUSHF           | 0     | $SP \leftarrow SP - 2; (SP) \leftarrow PSW;$<br>$PSW \leftarrow 0000H$ $I \leftarrow 0$ | 0        | 0        | 0  | 0        | 0        | 0        |       |

| POPF            | 0     | $PSW \leftarrow (SP); SP \leftarrow SP + 2; l \leftarrow \nu$                           | 11       | 10       | 10 | 10       | 10       | V        |       |

| SJMP            | 1     | PC ← PC + 11-bit offset                                                                 | _        | _        | _  | _        | _        | _        | 5     |

| LJMP -          | 1     | PC ← PC + 16-bit offset                                                                 | _        | _        | _  | _        | _        | _        | 5     |

| BR [indirect]   | 1     | PC ← (A)                                                                                | _        | _        | _  | _        | _        |          |       |

| SCALL           | 1     | SP ← SP - 2; (SP) ← PC;<br>PC ← PC + 11-bit offset                                      | -        | -        | _  | _        | _        | -        | 5     |

| LCALL           | 1     | SP ← SP - 2; (SP) ← PC;<br>PC ← PC + 16-bit offset                                      | -        | _        | _  | -        | -        | -        | 5     |

| RET             | 0     | PC ← (SP); SP ← SP + 2                                                                  | <u> </u> | _        | 1_ | Ι_       |          | <u> </u> |       |

| J (conditional) | 1     | PC ← PC + 8-bit offset (if taken)                                                       | <b> </b> | <u> </u> |    | <u> </u> | _        | _        | 5     |

| JC              | 1     | Jump if C = 1                                                                           |          | _        | _  |          | _        |          | 5     |

| JNC             | 1     | Jump if C = 0                                                                           | _        | _        | _  | _        |          |          | ` 5   |

| JE              | 1     | Jump if Z = 1                                                                           |          | _        | _  |          | T        |          | 5     |

NOTES:

1. If the mnemonic ends in "B", a byte operation is performed, otherwise a word operation is done. Operands D, B, and A must conform to the alignment rules for the required operand type. D and B are locations in the Register File; A can be bocated anywhere in memory.

2. D, D + 2 are consecutive WORDS in memory; D is DOUBLE-WORD aligned.

3. D, D + 1 are consecutive BYTES in memory; D is WORD aligned.

4. Changes a byte to a word.

<sup>5.</sup> Offset is a 2's complement number.

intel

**M8X97BH**

## ADVANCE INFORMATION

#### **Instruction Summary** (Continued)

| Mnemonic         | Oper- | Operation (Note 1)                                                           |    |    | Fla        | ıgs      |            |          | Notes |

|------------------|-------|------------------------------------------------------------------------------|----|----|------------|----------|------------|----------|-------|

| MITEMONIC        | ands  | Operation (Note 1)                                                           | Z  | N  | С          | ٧        | VT         | ST       |       |

| JNE              | 1     | Jump if Z = 0                                                                | _  | _  | _          | _        | _          |          | . 5   |

| JGE              | 1     | Jump if N = 0                                                                | _  | _  | =          | _        | _          |          | 5     |

| JLT              | 1     | Jump if N = 1                                                                |    | _  | =          | _        | _          |          | 5     |

| JGT              | 1     | Jump if $N = 0$ and $Z = 0$                                                  | _  |    | _          | _        |            | _        | 5     |

| JLE              | 1     | Jump if $N = 1$ or $Z = 1$                                                   | _  |    | _          | _        | _          | _        | 5     |

| JH               | 1     | Jump if C = 1 and Z = 0                                                      | _  |    | _          | -        | -          | _        | 5     |

| JNH              | 1     | Jump if C = 0 or Z = 1                                                       |    | -  | _          |          | 4          | _        | 5     |

| ٦٧               | 1     | Jump if V = 1                                                                | 1  | -  | ÷          | _        | _          |          | 5     |

| JNV              | 1     | Jump if V = 0                                                                | -  | 1  | _          |          |            | -        | 5     |

| JVT              | 1     | Jump if VT = 1; Clear VT                                                     | ł  | -  | _          |          | 0          |          | 5     |

| JNVT             | 1     | Jump if VT = 0; Clear VT                                                     | 1  |    |            | ļ        | 0          | <u> </u> | 5     |

| JST              | 1     | Jump if ST = 1                                                               | _  | _  |            | _        | _          | <u> </u> | 5     |

| JNST             | 1     | Jump if ST = 0                                                               | _  | -  | I          |          | -          | _        | 5     |

| JBS              | 3     | Jump if Specified Bit = 1                                                    | -  | _  | _          | I        |            | _        | 5, 6  |

| JBC              | 3     | Jump if Specified Bit = 0                                                    | _  |    | _          | -        | _          | _        | 5, 6  |

| DJNZ             | 1     | $D \leftarrow D - 1$ ; if $D \neq 0$ then $PC \leftarrow PC + 8$ -bit offset | _  | _  |            | _        |            | _        | 5     |

| DEC/DECB         | 1     | D ← D − 1                                                                    | 11 | 10 | 10         | 10       | 1          | =        |       |

| NEG/NEGB         | 1     | D ← 0 − D                                                                    | 1  | 1  | 1          | 11       | 1          | _        |       |

| INC/INCB         | 1     | D ← D + 1                                                                    | 1  | 10 | 1          | 10       | 1          | <b> </b> |       |

| EXT              | 1     | $D \leftarrow D; D + 2 \leftarrow Sign(D)$                                   | 10 | 10 | 0          | 0        | _          | T_       | 2     |

| EXTB             | 1     | $D \leftarrow D; D + 1 \leftarrow Sign(D)$                                   | 10 | 10 | 0          | 0        | _          |          | 3     |

| NOT/NOTB         | 1     | D ← Logical Not (D)                                                          | 10 | 10 | 0          | 0        | _          | Ι_       |       |

| CLR/CLRB         | 1     | D ← 0                                                                        | 1  | 0  | 0          | 0        | _          | 1-       |       |

| SHL/SHLB/SHLL    | 2     | C ← msb lsb ← 0                                                              | 10 | ?  | 11         | 1        | 1          | 1 –      | 7     |

| SHR/SHRB/SHRL    | 2     | $0 \rightarrow \text{msb} \text{lsb} \rightarrow C$                          | 1  | ?  | 10         | 0        | _          | 11       | 7     |

| SHRA/SHRAB/SHRAL | 2     | $msb \rightarrow msb lsb \rightarrow C$                                      | 10 | 10 | 10         | 0        | 1-         | 1        | 7     |

| SETC             | 0     | C ← 1                                                                        | -  | T- | 1          |          | 1          | 1-       |       |

| CLRC             | 0     | C ← 0                                                                        | Τ_ | 1- | 0          | -        |            | 1-       |       |

| CLRVT            | 0     | VT ← 0                                                                       | T- | 1- | T-         | <b>—</b> | 0          | _        |       |

| RST              | 0     | PC ← 2080H                                                                   | 0  | 0  | 0          | 0        | 0          | 0        | 8     |

| DI               | 0     | Disable All Interrupts (I ← 0)                                               | _  | 1- | _          | T —      | T          | 1-       |       |

| El               | 0     | Enable All Interrupts (I ← 1)                                                | T  | _  | Γ_         | <u> </u> |            | T —      |       |

| NOP              | 0     | PC ← PC + 1                                                                  | T- | _  | _          | 1-       | T —        |          |       |

| SKIP             | 0     | PC ← PC + 2                                                                  |    |    | <b> </b> – | -        | T -        | _        |       |

| NORML            | 2     | Left shift till msb = 1; D ← shift count                                     | 10 | ?  | 0          | T-       | 1-         | 1-       | 7     |

| TRAP             | 0     | SP ← SP - 2; (SP) ← PC<br>PC ← (2010H)                                       | _  | T_ |            | _        | <b> </b> _ | _        | 9     |

#### NOTES:

NOTES:

1. If the mnemonic ends in "B", a byte operation is performed, otherwise a word operation is done. Operands D, B and A must conform to the alignment rules for the required operand type. D and B are locations in the Register File; A can be located anywhere in memory.

5. Offset is a 2's complement number.

6. Specified bit is one of the 2048 bits in the register file.

7. The "L" (Long) suffix indicates double-word operation.

8. Initiates a Reset by pulling RESET low. Software should re-initialize all the necessary registers with code starting at 2080H.

9. The assembler will not accept this mnemonic.

ADVANCE INFORMATION

#### **Opcode and State Time Listing**

| ····     |          |        |       |                |           |       | ·      |        |       |        |       |                  |        |       |                    |          |                    |

|----------|----------|--------|-------|----------------|-----------|-------|--------|--------|-------|--------|-------|------------------|--------|-------|--------------------|----------|--------------------|

|          |          | C      | HRE   | CT             | IMMEDIATE |       |        |        |       | NDIREC | т⊙    |                  |        |       | NDEXE              | ე@       |                    |

|          |          |        |       |                | 1,111     |       |        | NORMAL |       |        | AU    | TO-INC.          |        | SHO   | RT                 | L        | ONG                |

| MNEMONIC | OPERANDS | OPCODE | BYTES | STATE<br>TIMES | OPCODE    | BYTES | STATE  | OPCODE | BYTES | STATE® | BYTES | STATE®<br>TIMES  | OPCODE | BYTES | STATE()<br>TIMES() | BYTES    | STATE()<br>TIMES() |

|          |          |        |       |                |           | AF    | RITHME | TIC IN | IST   | RUCTIO | NS    | -, -, -, -, -, - |        |       |                    | <u>.</u> |                    |

| ADD      | 2        | 64     | 3     | 4              | 65        | 4     | 5      | 66     | 3     | 6/11   | 3     | 7/12             | 67     | 4.    | 6/11-              | 5        | 7/12               |

| ADD      | 3        | 44     | 4     | 5              | 45        | 5     | 6      | 46     | 4     | 7/12   | 4     | 8/13             | 47     | 5     | 7/12               | 6.       | 8/13               |

| ADDB     | 2        | 74     | 3     | 4              | 75        | 3     | 4      | 76     | 3     | 6/11   | 3     | 7/12             | 77     | 4     | 6/11               | 5        | 7/12               |

| ADDB     | 3        | 54     | 4     | 5              | 55        | 4     | 5      | 56     | 4     | 7/12   | 4     | 8/13             | 57     | 5     | 7/12               | 6        | 8/13               |

| ADDC     | 2        | A4     | 3     | 4              | A5        | 4     | 5      | A6     | 3     | 6/11   | 3     | 7/12             | A7     | 4     | 6/11               | 5        | 7/12               |

| ADDCB    | 2        | B4     | 3     | 4              | B5        | 3     | 4      | B6     | 3     | 6/11   | 3     | 7/12             | B7     | 4     | 6/11               | 5        | 7/12               |

| SUB      | 2        | 68     | 3     | 4              | 69        | 4     | 5      | 6A     | 3     | 6/11   | 3.    | 7/12             | 6B     | 4     | 6/11               | 5        | 7/12               |

| SUB      | 3        | 48     | 4     | 5              | 49        | 5     | 6      | 4A     | 4     | 7/12   | 4     | 8/13             | 4B     | 5     | 7/12               | 6        | 8/13               |

| SUBB     | 2        | 78     | 3     | 4              | 79        | 3     | 4      | 7A     | 3     | 6/11   | 3     | 7/12             | 7B     | 4     | 6/11               | 5        | 7/12               |

| SUBB     | 3        | 58     | 4     | 5              | 59        | 4     | 5      | 5A     | 4     | 7/12   | 4     | 8/13             | 5B     | 5     | 7/12               | 6        | 8/13               |

| SUBC     | 2        | A8     | 3     | 4              | A9        | 4     | 5      | AA     | 3     | 6/11   | 3     | 7/12             | AB     | 4     | 6/11               | 5        | 7/12               |

| SUBCB    | 2        | B8     | 3     | 4              | В9        | 3     | 4      | BA     | 3     | 6/11   | 3     | 7/12             | BB     | 4     | 6/11               | 5        | 7/12               |

| CMP      | 2        | 88     | 3     | 4              | 89        | 4     | 5      | 8A     | 3     | 6/11   | 3     | 7/12             | 8B     | 4     | 6/11               | 5        | 7/12               |

| CMPB     | 2        | 98     | 3     | 4              | 99        | 3     | 4      | 9A     | 3     | 6/11   | 3     | 7/12             | 9B     | 4     | 6/11               | 5        | 7/12               |

|          | L        |        |       |                |           | L     |        |        |       |        |       |                  |        |       |                    |          |                    |

| MULU     | 2        | 6C     | 3     | 25             | 6D        | 4     | 26     | 6E     | 3     | 27/32  | 3     | 28/33            | 6F     | 4     | 27/32              | 5        | 28/33              |

| MULU     | 3        | 4C     | 4     | 26             | 4D        | 5     | 27     | 4E     | 4     | 28/33  | 4     | 29/34            | 4F     | 5     | 28/33              | 6        | 29/34              |

| MULUB    | 2        | 7C     | 3     | 17             | 7D        | 3     | 17     | 7E     | 3     | 19/24  | 3     | 20/25            | ·7F    | 4     | 19/24              | 5        | 20/25              |

| MULUB    | 3        | 5C     | 4     | 18             | 5D        | 4     | 18     | 5E     | 4     | 20/25  | 4     | 21/26            | 5F     | 5     | 20/25              | 6        | 21/26              |

| MUL      | 2        | 2      | 4     | 29             | 0         | 5     | 30     | 2      | 4     | 31/36  | 4     | 32/37            | 2      | 5     | 31/36              | 6        | 32/37              |

| MUL.     | 3        | 2      | 5     | 30             | 0         | 6     | 31     | 2      | 5     | 32/37  | 5     | 33/38            | 2      | 6     | 32/37              | 7        | 33/38              |

| MULB     | 2        | 2      | 4     | 21             | 0         | 4     | 21     | 2      | 4     | 23/28  | 4     | 24/29            | 2      | 5     | 23/28              | 6        | 24/29              |

| MULB     | 3        | 0      | 5     | 22             | 2         | 5     | 22     | 2      | 5     | 24/29  | 5     | 25/30            | 2      | 6     | 24/29              | 7        | 25/30              |

| DIVU     | 2        | 8C     | 3     | 25             | 8D        | 4     | 26     | 8E     | 3     | 28/32  | 3     | 29/33            | 8F     | 4     | 28/32              | 5        | 29/33              |

| DIVUB    | 2        | 9C     | 3     | 17             | 9D        | 3     | 17     | 9E     | 3     | 20/24  | 3     | 21/25            | 9F     | 4     | 20/24              | 5        | 21/25              |

| DIV      | 2        | 2      | 4     | 29             | 2         | 5     | 30     | 2      | 4     | 32/36  | 4     | 33/37            | 2      | 5     | 32/36              | 6        | 33/37              |

| DIVB     | 2        | 0      | 4     | 21             | 2         | 4     | 21     | 0      | 4     | 24/28  | 4     | 25/29            | 2      | 5     | 24/28              | 6        | 25/29              |

271075-47

NOTES:

\*Long indexed and Indirect + instructions have identical opcodes with Short indexed and Indirect modes, respectively. The second byte of instructions using any Indirect or indexed addressing mode specifies the exact mode used. If the second byte is even, use Indirect or Short indexed. If it is odd, use Indirect + or Long indexed. In all cases the second byte of the instruction always specifies an even (word) location for the address referenced.

② Number of state times shown for internal/external operands.