# MM54C30, MM74C30

## 8-Input NAND Gate

The logical gate employs complementary MOS (CMOS) to achieve wide power supply operating range, low power consumption and high noise immunity. Function and pin out compatibility with series 54/74 devices minimizes design time for those designers familiar with the standard 54/74 logic family. All inputs are protected from damage due to static discharge by diode clamps to V<sub>CC</sub> and GND.

### Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

# National Semiconductor

# MM54C30/MM74C30 8-Input NAND Gate

#### **General Description**

The logical gate employs complementary MOS (CMOS) to achieve wide power supply operating range, low power consumption and high noise immunity. Function and pin out compatibility with series 54/74 devices minimizes design time for those designers familiar with the standard 54/74 logic family.

All inputs are protected from damage due to static discharge by diode clamps to  $V_{CC}$  and GND.

## Features

- Wide supply voltage range

Guaranteed noise margin

- Guaranteeu noise mai

Uist seise immunity

- High noise immunityLow power

- TTL compatibility

3.0V to 15V 1.0V 0.45 V<sub>CC</sub> (typ.) Fan out of 2 driving 74L

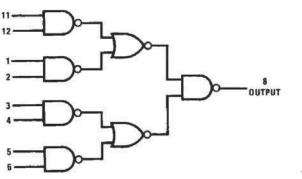

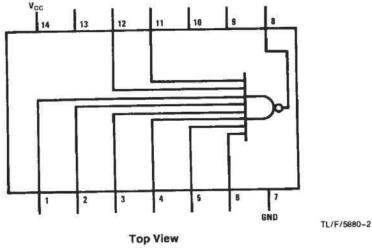

### Logic and Connection Diagrams

TL/F/5880-1

**Dual-In-Line Package**

#### Order Number MM54C30\* or MM74C30\*

\*Please look into Section 8, Appendix D for availability of various package types.

6-20

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Voltage at any Pin                            | -0.3V to V <sub>CC</sub> + 0.3V |

|-----------------------------------------------|---------------------------------|

| Operating Temperature Range (T <sub>A</sub> ) |                                 |

| MM54C30                                       | -55°C to +125°C                 |

| MM74C30                                       | -40°C to +85°C                  |

|                                               |                                 |

| Storage Temperature Range (TS)                   | -65°C to +150°C |

|--------------------------------------------------|-----------------|

| Power Dissipation (PD)                           |                 |

| Dual-In-Line                                     | 700 mW          |

| Small Outline                                    | 500 mW          |

| Operating V <sub>CC</sub> Range                  | 3.0V to 15V     |

| Absolute Maximum V <sub>CC</sub>                 | 18V             |

| Lead Temperature (TL)<br>(Soldering, 10 seconds) | 260°C           |

### DC Electrical Characteristics Min/Max limits apply across temperature range unless otherwise noted

| Symbol                           | Parameter                            | Conditions                                              | Min                   | Тур                 | Max          | Units |

|----------------------------------|--------------------------------------|---------------------------------------------------------|-----------------------|---------------------|--------------|-------|

| MOS TO CI                        | MOS                                  |                                                         |                       |                     |              |       |

| VIN(1) Logical "1" Input Voltage | Logical "1" Input Voltage            | $V_{CC} = 5V$                                           | 3.5                   |                     |              | V     |

|                                  | $V_{CC} = 10V$                       | 8.0                                                     |                       |                     | v            |       |

| VIN(0)                           | Logical "0" Input Voltage            | $V_{\rm CC} = 5V$                                       |                       |                     | 1.5          | v     |

|                                  |                                      | $V_{CC} = 10V$                                          |                       |                     | 2.0          | v     |

| V <sub>OUT(1)</sub>              | Logical "1" Output Voltage           | $V_{CC} = 5V, I_O = -10 \ \mu A$                        | 4.5                   | - Add               |              | v     |

|                                  |                                      | $V_{CC} = 10V, I_O = -10 \ \mu A$                       | 9.0                   | 1 2 2 4 5 1 1<br>2) |              | v     |

| VOUT(0)                          | Logical "0" Output Voltage           | $V_{CC} = 5V, I_O = 10 \ \mu A$                         |                       |                     | 0.5          | V     |

|                                  |                                      | $V_{CC} = 10V, I_O = 10 \ \mu A$                        |                       |                     | 1.0          | ٧     |

| IIN(1)                           | Logical "1" Input Current            | $V_{CC} = 15V, V_{IN} = 15V$                            |                       | 0.005               | 1.0          | μΑ    |

| IIN(0)                           | Logical "0" Input Current            | $V_{CC} = 15V, V_{IN} = 0V$                             | -1.0                  | -0.005              |              | μΑ    |

| Icc                              | Supply Current                       | $V_{CC} = 15V$                                          |                       | 0.01                | 15           | μΑ    |

| MOS/LPTT                         | L INTERFACE                          |                                                         |                       |                     |              |       |

| V <sub>IN(1)</sub>               | Logical "1" Input Voltage            | 54C, $V_{CC} = 4.5V$                                    | V <sub>CC</sub> - 1.5 |                     |              | ٧     |

|                                  |                                      | 74C, $V_{CC} = 4.75V$                                   | V <sub>CC</sub> - 1.5 |                     |              | v     |

| V <sub>IN(0)</sub>               | Logical "0" Input Voltage            | 54C, V <sub>CC</sub> = 4.5V                             |                       |                     | 0.8          | v     |

|                                  |                                      | 74C, $V_{CC} = 4.75V$                                   | 7.53-25.448           | 5 6.5 M             | 0.8          | v     |

| V <sub>OUT(1)</sub>              | Logical "1" Output Voltage           | 54C, $V_{CC} = 4.5V$ , $I_O = -360 \mu A$               | 2.4                   |                     |              | v     |

|                                  |                                      | 74C, $V_{CC} = 4.75V$ , $I_0 = -360 \mu A$              | 2.4                   |                     |              | v     |

| Vout(0)                          | Logical "0" Output Voltage           | $54C, V_{CC} = 4.5V, I_O = 360\mu A$                    | 2008/01               |                     | 0.4          | v     |

|                                  |                                      | 74C, $V_{CC} = 4.75V$ , $I_O = 360\mu A$                |                       |                     | 0.4          | v     |

| UTPUT DR                         | IVE (See 54C/74C Family Char         | acteristics Data Sheet) (short circuit o                | current)              |                     |              |       |

| ISOURCE                          | Output Source Current<br>(P-Channel) | $V_{CC} = 5V, V_{OUT} = 0V$<br>$T_A = 25^{\circ}C$      | -1.75                 | -3.3                |              | mA    |

| ISOURCE                          | Output Source Current<br>(P-Channel) | $V_{CC} = 10V, V_{OUT} = 0V$<br>$T_A = 25^{\circ}C$     | -8.0                  | - 15                | 0.0000000000 | mA    |

| I <sub>SINK</sub>                | Output Sink Current<br>(N-Channel)   | $V_{CC} = 5V, V_{OUT} = V_{CC}$<br>$T_A = 25^{\circ}C$  | 1.75                  | 3.6                 |              | mA    |

| ISINK                            | Output Sink Current<br>(N-Channel)   | $V_{CC} = 10V, V_{OUT} = V_{CC}$<br>$T_A = 25^{\circ}C$ | 8.0                   | 16                  |              | mA    |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

I

| Symbol                                              | Parameter                     | Conditions        | Min | Тур | Max | Units |

|-----------------------------------------------------|-------------------------------|-------------------|-----|-----|-----|-------|

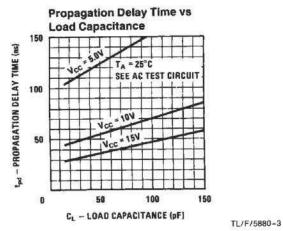

| tpd Propagation Delay Time to<br>Logical "1" or "0" | Propagation Delay Time to     | $V_{CC} = 5V$     |     | 125 | 180 | ns    |

|                                                     | $V_{\rm CC} = 10V$            |                   | 55  | 90  | ns  |       |

| CIN                                                 | Input Capacitance             | (Note 2)          |     | 4.0 |     | pF    |

| CPD                                                 | Power Dissipation Capacitance | (Note 3) Per Gate |     | 26  |     | pF    |

\*AC Parameters are guaranteed by DC correlated testing.

Note 2: Capacitance is guaranteed by periodic testing.

Note 3: GPD determines the no load ac power consumption of any CMOS device. For complete explanation, see 54C/74C Family Characteristics, application note-AN-90.

## **Typical Performance Characteristics**

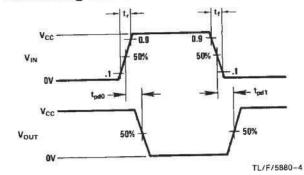

### Switching Time Waveforms

Note: Delays Measured with Input  $t_{\rm r},\,t_{\rm f}\,=\,20$  ns.

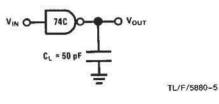

#### **AC Test Circuit**

6-22

1