#### MM74C48

### BCD-to-7 Segment Decoder

The MM74C48 BCD-to-7 segment decoder is a monolithic complementary MOS (CMOS) integrated circuit constructed with N- and P-channel enhancement transistors. Seven NAND gates and one driver are connected in pairs to make binary-coded decimal (BCD) data and its complement available to the seven decoding AND-OR-INVERT gates. The remaining NAND gate and three input buffers provide test-blanking input/ripple-blanking output, and ripple-blanking inputs.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

#### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

October 1987 Revised May 2002

# MM74C48 BCD-to-7 Segment Decoder

#### **General Description**

The MM74C48 BCD-to-7 segment decoder is a monolithic complementary MOS (CMOS) integrated circuit constructed with N- and P-channel enhancement transistors. Seven NAND gates and one driver are connected in pairs to make binary-coded decimal (BCD) data and its complement available to the seven decoding AND-OR-INVERT gates. The remaining NAND gate and three input buffers provide test-blanking input/ripple-blanking output, and ripple-blanking inputs.

#### **Features**

- Wide supply voltage range: 3.0V to 15V

- Guaranteed noise margin: 1.0V

- High noise immunity: 0.45 V<sub>CC</sub> (typ.)

- Low power TTL compatibility: fan out of 2 driving 74L

- High current sourcing output (up to 50 mA)

- Ripple blanking for leading or trailing zeros (optional)

- Lamp test provision

#### **Ordering Code:**

| Order Number Package Number |      | Package Description                                                    |  |  |  |  |  |

|-----------------------------|------|------------------------------------------------------------------------|--|--|--|--|--|

| MM74C48N                    | N16E | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide |  |  |  |  |  |

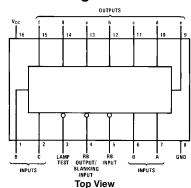

#### **Connection Diagrams**

#### Segment Identification

#### Numerical Designations and Resultant Displays

#### **Truth Table**

| Decimal  |    |     | Inp | uts |   |   |          |   |   | ( | Output | s |   |   |          |

|----------|----|-----|-----|-----|---|---|----------|---|---|---|--------|---|---|---|----------|

| or       |    |     |     |     |   |   | BI/RBO   |   |   |   |        |   |   |   | Note     |

| Function | LT | RBI | D   | С   | В | Α | (Note 1) | а | b | С | d      | е | f | g | Î        |

| 0        | Н  | Н   | L   | L   | L | L | Н        | Н | Н | Н | Н      | Н | Н | L | (Note 2) |

| 1        | Н  | Х   | L   | L   | L | Н | Н        | L | Н | Н | L      | L | L | L | (Note 2) |

| 2        | Н  | Х   | L   | L   | Н | L | Н        | Н | Н | L | Н      | Н | L | Н |          |

| 3        | Н  | Х   | L   | L   | Н | Н | Н        | Н | Н | Н | Н      | L | L | Н |          |

| 4        | Н  | Χ   | L   | Н   | L | L | Н        | L | Н | Н | L      | L | Н | Н |          |

| 5        | Н  | Х   | L   | Н   | L | Н | Н        | Н | L | Н | Н      | L | Н | Н |          |

| 6        | Н  | Х   | L   | Н   | Н | L | Н        | L | L | Н | Н      | Н | Н | Н |          |

| 7        | Н  | Х   | L   | Н   | Н | Н | Н        | Н | Н | Н | L      | L | L | L |          |

| 8        | Н  | Х   | Н   | L   | L | L | Н        | Н | Н | Н | Н      | Н | Н | Н |          |

| 9        | Н  | Х   | Н   | L   | L | Н | Н        | Н | Н | Н | L      | L | Н | Н |          |

| 10       | Н  | Х   | Н   | L   | Н | L | Н        | L | L | L | Н      | Н | L | Н |          |

| 11       | Н  | Х   | Н   | L   | Н | Н | Н        | L | L | Н | Н      | L | L | Н |          |

| 12       | Н  | Х   | Н   | Н   | L | L | Н        | L | Н | L | L      | L | Н | Н |          |

| 13       | Н  | Χ   | Н   | Н   | L | Н | Н        | Н | L | L | Н      | L | Н | Н |          |

| 14       | Н  | Х   | Н   | Н   | Н | L | Н        | L | L | L | Н      | Н | Н | Н |          |

| 15       | Н  | Х   | Н   | Н   | Н | Н | Н        | L | L | L | L      | L | L | L |          |

| BI       | Χ  | Х   | Χ   | Χ   | Χ | Х | L        | L | L | L | L      | L | L | L | (Note 3) |

| RBI      | Н  | L   | L   | L   | L | L | L        | L | L | L | L      | L | L | L | (Note 4) |

| LT       | L  | Х   | Χ   | Χ   | Χ | Χ | Н        | Н | Н | Н | Н      | Н | Н | Н | (Note 5) |

H = HIGH Level

Note 2: The blanking input (BI) must be open when output functions 0–15 are desired. The ripple-blanking input (RBI) must be HIGH, if blanking of a decimal zero is not desired.

Note 3: When a LOW logic level is applied directly to the blanking input (BI), all segment outputs are LOW regardless of the level of any other input.

Note 4: When ripple-blanking input (RBI) and inputs A, B, C, and D are at a LOW level with the lamp-test input HIGH, all segment outputs go LOW and the ripple-blanking output (RBO) goes to a LOW level (response condition).

Note 5: When the blanking input/ripple-blanking output (BI/RBO) is open and a LOW is applied to the lamp-test input, all segment outputs are HIGH.

L = LOW Level X = Irrelevant

Note 1: One BI/RBO is wire-AND logic serving as blanking input (BI) and/or ripple-blanking output (RBO).

#### Absolute Maximum Ratings(Note 6)

Voltage at Any Pin -0.3V to  $V_{CC} + 0.3V$ -55°C to +125°C Operating Temperature Range -65°C to +150°C Storage Temperature Range

Power Dissipation

Dual-In-Line 700 mW

Small Outline 500 mW

Operating V<sub>CC</sub> Range 3.0V to 15V

Absolute Maximum  $V_{\rm CC}$ 18V Lead Temperature

(Soldering, 10 seconds) 260°C Note 6: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The Electrical Characteristics table provides conditions for actual device operation.

**DC Electrical Characteristics**

| Symbol              | Parameter                           | Conditions                                                | Min                   | Тур      | Max   | Units |

|---------------------|-------------------------------------|-----------------------------------------------------------|-----------------------|----------|-------|-------|

| CMOS to C           | MOS                                 | •                                                         | '                     | <u> </u> |       |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage           | V <sub>CC</sub> = 5.0V                                    | 3.5                   |          |       | V     |

|                     |                                     | V <sub>CC</sub> = 10V                                     | 8.0                   |          |       | ľ     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage           | V <sub>CC</sub> = 5.0V                                    |                       |          | 1.5   | V     |

| . ,                 |                                     | V <sub>CC</sub> = 10V                                     |                       |          | 2.0   | v     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage          | $V_{CC} = 5.0V, I_{O} = -10 \mu A$                        | 4.5                   |          |       | V     |

|                     | (RB Output Only)                    | $V_{CC} = 10V, I_{O} = -10 \mu A$                         | 9.0                   |          |       | ľ     |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage          | $V_{CC} = 5.0V, I_{O} = 10 \mu A$                         |                       |          | 0.5   | V     |

|                     |                                     | $V_{CC} = 10V, I_{O} = 10 \mu A$                          |                       |          | 1.0   | ľ     |

| I <sub>IN(1)</sub>  | Logical "1" Input Current           | V <sub>CC</sub> = 15.0V, V <sub>IN</sub> = 15V            |                       | 0.005    | 1.0   | μΑ    |

| I <sub>IN(0)</sub>  | Logical "0" Input Current           | $V_{CC} = 15.0V, V_{IN} = 0V$                             | -1.0                  | -0.005   |       | μΑ    |

| I <sub>CC</sub>     | Supply Current                      | V <sub>CC</sub> = 15V                                     |                       | 0.05     | 300   | μΑ    |

| CMOS/LPT            | TL INTERFACE                        | •                                                         |                       | <u> </u> |       |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage           | V <sub>CC</sub> = 4.75V                                   | V <sub>CC</sub> – 1.5 |          |       | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage           | V <sub>CC</sub> = 4.75V                                   |                       |          | 0.8   | V     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage          | $V_{CC} = 4.75V, I_{O} = -50 \mu A$                       | 2.4                   |          |       | V     |

|                     | (RB Output Only)                    |                                                           |                       |          |       |       |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage          | $V_{CC} = 4.75V, I_{O} = 360 \mu A$                       |                       |          | 0.4   | V     |

| OUTPUT D            | RIVE (See Family Characteristics Da | ta Sheet)                                                 |                       | <u> </u> |       |       |

| I <sub>SOURCE</sub> | Output Source Current               | V <sub>CC</sub> = 4.75V, V <sub>OUT</sub> = 0.4V          |                       |          | -0.80 | mA    |

|                     | (P-Channel) (RB Output Only)        | $V_{CC} = 10V, V_{OUT} = 0.5V$                            |                       |          | -4.0  | mA    |

| I <sub>SINK</sub>   | Output Sink Current                 | $V_{CC} = 5.0V$ , $V_{OUT} = V_{CC}$                      | 1.75                  | 3.6      |       | mA    |

|                     | (N-Channel)                         | T <sub>A</sub> = 25°C                                     |                       |          |       |       |

| I <sub>SINK</sub>   | Output Sink Current                 | V <sub>CC</sub> = 10V, V <sub>OUT</sub> = V <sub>CC</sub> | 8.0                   | 16       |       | mA    |

|                     | (N-Channel)                         | T <sub>A</sub> = 25°C                                     |                       |          |       |       |

| I <sub>SOURCE</sub> | Output Source Current               | V <sub>CC</sub> = 5.0V, V <sub>OUT</sub> = 3.4V           | -20                   | -50      |       |       |

|                     | (NPN Bipolar)                       | $V_{CC} = 5.0V, V_{OUT} = 3.0V$                           |                       | -65      |       | A     |

|                     |                                     | V <sub>CC</sub> = 10V, V <sub>OUT</sub> = 8.4V            | -20                   | -50      |       | mA.   |

|                     |                                     | V <sub>CC</sub> = 10V, V <sub>OUT</sub> = 8.0V            |                       | -65      |       | 1     |

#### AC Electrical Characteristics (Note 7)

$T_A = 25^{\circ}C,\ C_L = 50\ \text{pF},$  unless otherwise specified

| Symbol                              | Parameter                            | Conditions             | Min | Тур | Max  | Units |

|-------------------------------------|--------------------------------------|------------------------|-----|-----|------|-------|

| t <sub>pd0</sub> , t <sub>pd1</sub> | Propagation Delay to a "1" or "0" on | V <sub>CC</sub> = 5.0V |     | 450 | 1500 | ns    |

|                                     | Segment Outputs from Data Inputs     | V <sub>CC</sub> = 10V  |     | 160 | 500  | 115   |

| t <sub>pd0</sub>                    | Propagation Delay to a "0" on        | V <sub>CC</sub> = 5.0V |     | 500 | 1600 | ns    |

|                                     | Segment Outputs from RB Input        | V <sub>CC</sub> = 10V  |     | 180 | 550  | 115   |

| t <sub>pd0</sub>                    | Propagation Delay to a "0" on        | V <sub>CC</sub> = 5.0V |     | 350 | 1200 | ns    |

|                                     | Segment Outputs from Blanking Input  | V <sub>CC</sub> = 10V  |     | 140 | 450  | 115   |

| t <sub>pd1</sub>                    | Propagation Delay to a "1" on        | V <sub>CC</sub> = 5.0V |     | 450 | 1500 | ns    |

|                                     | Segment Outputs from Lamp Test       | V <sub>CC</sub> = 10V  |     | 160 | 500  | 113   |

| t <sub>pd1</sub>                    | Propagation Delay to a "1" on RB     | V <sub>CC</sub> = 5.0V |     | 600 | 2000 | ns    |

|                                     | Output from RB Input                 | V <sub>CC</sub> = 10V  |     | 250 | 800  | 115   |

| t <sub>pd0</sub>                    | Propagation Delay to a "0" on RB     | V <sub>CC</sub> = 5.0V |     | 140 | 450  | ns    |

|                                     | Output from RB Input                 | V <sub>CC</sub> = 10V  |     | 50  | 150  | 113   |

Note 7: AC Parameters are guaranteed by DC correlated testing.

#### **Typical Applications**

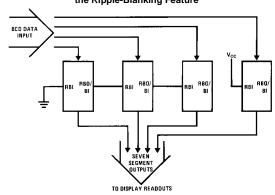

## Typical Connection Utilizing the Ripple-Blanking Feature

First three stages will blank leading zeros, the fourth stage will not blank zeros.

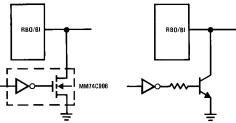

#### Blanking Input Connection Diagram

When RBO/BI is forced LOW, all segment outputs are off regardless of the state of any other input condition.

# **Light Emitting Diode (LED) Readout** COMMON CATHODE LED Incandescent Readout Fluorescent Readout DIRECT (LOW BRIGHTNESS) FILAMENT SUPPLY GND OR APPROPRIATE VOLTAGE BELOW GND \*\*A filament pre-warm resistor is recommended to reduce filament thermal shock and increase the effective cold resistance of the filament. **Gas Discharge Readout** Liquid Crystal (LC) Readout EXCITATION (SQUARE WAVE, V<sub>CC</sub> TO GND) APPROPRIATE VOLTAGE MM74C86 Direct DC drive of LC's not recommended for life of LC readouts.

#### Physical Dimensions inches (millimeters) unless otherwise noted 0.740 - 0.780 0.090 (18.80 - 19.81)(2.286)<u>16 15 14 13 12 11 10 9</u> 16 15 INDEX AREA 0.250 ± 0.010 $(6.350 \pm 0.254)$ PIN NO. 1 PIN NO. 1 2 3 4 5 6 7 8 1 2 IDENT IDENT OPTION 01 OPTION 02 0.065 0.130 ± 0.005 $\frac{0.060}{(1.524)}$ 4º TYP 0.300 - 0.320 (1.651) $\overline{(3.302 \pm 0.127)}$ OPTIONAL (7.620 - 8.128) 0.145 - 0.200 (3.683 - 5.080) 95°±5° $\frac{0.008 - 0.016}{(0.203 - 0.406)}$ TYP 90° ± 4° TYP 0.020 MIN 0.280 (0.508) $\frac{0.125 - 0.150}{(3.175 - 3.810)}$ (7.112) MIN $(0.762 \pm 0.381)$ 0.014 - 0.023 $0.100 \pm 0.010$ (0.325 +0.040 -0.015 (0.356 - 0.584) $(2.540 \pm 0.254)$ 0.050 ± 0.010 (1.270 ± 0.254) N16E (REV F) TYP

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com