# SN74ALS992, SN74ALS993

## 9-Bit D-Type Transparent Read-Back Latches with 3-State Outputs

These 9-bit latches are designed specifically for storing the contents of the input data bus plus providing the capability of reading-back the stored data onto the input data bus. In addition, they provide a 3-state buffer-type output and are easily implemented in parity applications.

The nine latches of the 'ALS992 and 'ALS993 are transparent D-type. While the enable (C) is high, the Q outputs of the 'ALS992 will follow the data (D) inputs. For the 'ALS993, the  $\overline{\mathbb{Q}}$  outputs will provide the complement of what is applied to its data (D) inputs. On both devices, the Q or  $\overline{\mathbb{Q}}$  outputs will be in the 3-state condition when output enable  $\overline{\mathsf{OEQ}}$  is high.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## 25E D 8961723 0083558 3

#### SN74ALS992, SN74ALS993 9-BIT D-TYPE TRANSPARENT READ-BACK LATCHES WITH 3-STATE OUTPUTS

D2836, APRIL 1984 - REVISED JANUARY 1986

- 3-State I/O-Type Read-Back Inputs

- Bus-Structured Pinout

- Choice of True or Inverting Logic 'ALS992 . . . True Outputs 'ALS993 . . . Inverting Outputs

- Designed with 9 Bits for Parity Applications

- Package Options Include Plastic "Small Outline" Packages, Both Plastic and Ceramic Chip Carriers, and Standard Plastic and Ceramic 300-mil DIPs

- Dependable Texas Instruments Quality and Reliability

#### description

These 9-bit latches are designed specifically for storing the contents of the input data bus plus providing the capability of reading-back the stored data onto the input data bus. In addition, they provide a 3-state buffer-type output and are easily implemented in parity applications.

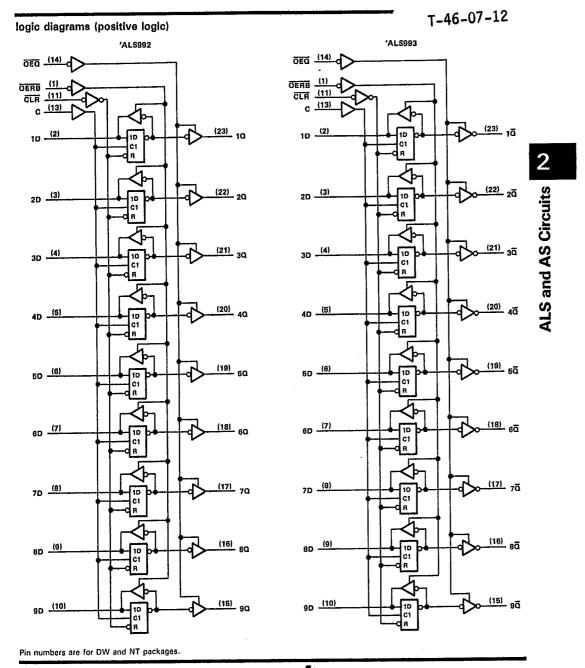

The nine latches of the 'ALS992 and 'ALS993 are transparent D-type. While the enable (C) is high, the Q outputs of the 'ALS992 will follow the data (D) inputs. For the 'ALS993, the  $\overline{\mathbf{Q}}$  outputs will provide the complement of what is applied to its data (D) inputs. On both devices, the Q or  $\overline{\mathbf{Q}}$  outputs will be in the 3-state condition when output enable  $\overline{\mathbf{QEQ}}$  is high.

Read-back is provided through the read-back control input (OERB). When the control is taken low, the data present at the output of the data latches will be allowed to pass back onto the input data bus. When it is taken high, the output of the data latches will be isolated from the data (D) inputs. The read-back control does not affect the internal operation of the latches; however, precautions should be taken not to create a busconflict situation.

The SN74ALS992 and SN74ALS993 are characterized for operation from 0°C to 70°C.

SN74ALS992...DW OR NT PACKAGE

(TOP VIEW) T-46-07-12

SN74ALS992 . . . FN PACKAGE (TOP VIEW)

SN74ALS993 ... DW OR NT PACKAGE (TOP VIEW)

SN74ALS993 . . . FN PACKAGE (TOP VIEW)

NC-No internal connection

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Taxas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 1984, Texas Instruments Incorporated

2-803

S and AS Circuits

3070 B-13

POST OFFICE BOX 655012 . DALLAS, TEXAS 75265

# SN74ALS992, SN74ALS993

9-BIT D-TYPE TRANSPARENT READ-BACK LATCHES WITH 3-STATE OUTPUTS

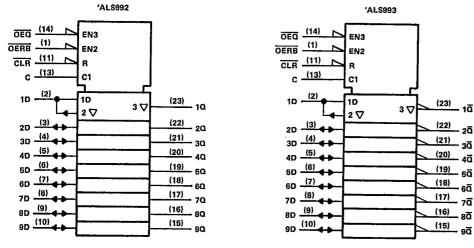

logic symbols†

<sup>†</sup>These symbols are in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers are for DW and NT packages.

2-804

3071

B-14

Texas VI

POST OFFICE BOX 655012 . DALLAS, TEXAS 75265

ALS and AS Circuits

TEXAS INSTRUMENTS POST OFFICE BOX 655012 . DALLAS, TEXAS 75265

2-805

T-46-07-12

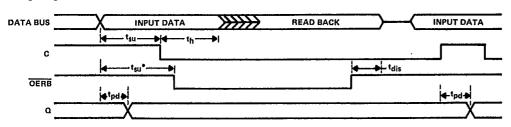

#### timing diagram

25E D

CLR = H, OEQ =L

\*This setup time ensures the readback circuit will not create a conflict on the input data bus.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC                                         | <br><i></i>        |

|-------------------------------------------------------------|--------------------|

| Input voltage, (OERB, OE, CLR, and C inputs)                | <br>7 V            |

| Voltage applied to D inputs and to disabled 3-state outputs | <br>5.5 V          |

| Operating free-air temperature range                        | <br>,. 0°C to 70°C |

| Storage temperature range                                   | <br>-65°C to 150°C |

#### recommended operating conditions

|                 |                                |                  | MIN | NOM | MAX  | UNIT |  |

|-----------------|--------------------------------|------------------|-----|-----|------|------|--|

| Vcc             | Supply voltage                 | 4.5              | 5   | 5.5 | ٧    |      |  |

| ViH             | High-level input voltage       | 2                |     |     | V    |      |  |

| VIL             | Low-level input voltage        |                  |     | 0.8 | V    |      |  |

|                 | High-level output current      | Q or Q           |     |     | -2.6 |      |  |

| ЮН              |                                | D                |     |     | -0.4 | mΑ   |  |

| loL             | Low-level output current       | Q or Q           |     |     | 24   | ^    |  |

|                 |                                | D                |     |     | 8    | mA   |  |

| t <sub>W</sub>  | Pulse duration                 | Enable C high    | 10  |     |      |      |  |

|                 |                                | CLR low          | 10  |     |      | ns   |  |

| t <sub>su</sub> | Setup time                     | Data before CI   | 10  |     |      | ns   |  |

|                 |                                | Data before OERB | 10  |     |      |      |  |

| th              | Hold time                      | Data after C‡    | 5   | -   |      | กร   |  |

| TA              | Operating free-air temperature |                  | 0   |     | 70   | °C   |  |

c-02 3073

2-806

electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER |                       | TEST CONDI                                                     | MIN TYP                         | t MAX              | UNIT  |          |  |

|-----------|-----------------------|----------------------------------------------------------------|---------------------------------|--------------------|-------|----------|--|

| VIK       | HAVETER               | V <sub>CC</sub> = 4.5 V,                                       | I <sub>i</sub> = -18 mA         |                    | -1.2  | ٧        |  |

|           | All outputs           | VCC = 4.5 V to 5.5 V,                                          | I <sub>OH</sub> = -0.4 mA       | V <sub>CC</sub> -2 |       | V        |  |

| ٧ОН       | QorQ                  | VCC = 4.5 V,                                                   | I <sub>OH</sub> = −2.6 mA       | 2.4 3              |       |          |  |

|           |                       | V <sub>CC</sub> = 4.5 V,                                       | loL = 4 mA                      | 0.2                |       |          |  |

|           | D                     | VCC = 4.5 V,                                                   | IOL = 8 mA                      | 0.3                | 5 0.5 | l v      |  |

| VOL       |                       | V <sub>CC</sub> = 4.5 V <sub>r</sub>                           | IOL = 12 mA                     | 0.2                | 5 0.4 | ]        |  |

|           | O or O                | V <sub>CC</sub> = 4.5 V,                                       | IOL = 24 mA                     | 0.3                | 5 0.5 | <u> </u> |  |

| lozh      | <del> </del>          | V <sub>CC</sub> = 5.5 V,                                       | V <sub>O</sub> = 2.7 V          |                    | 20    | μΑ       |  |

| IOZL      | Q or a                | V <sub>CC</sub> = 5.5 V,                                       | $V_0 = 0.4 \text{ V}$           |                    | - 20  | <i></i>  |  |

|           | D inputs              | V <sub>CC</sub> = 5.5 V,                                       | V <sub>I</sub> = 5.5 V          |                    | 0,1   | mA       |  |

| lį –      | All other             | V <sub>CC</sub> = 5.5 V,                                       | V <sub>I</sub> = 7 V            |                    | 0.1   |          |  |

| D inp     | D inputs‡             | V <sub>CC</sub> = 5.5 V,                                       |                                 |                    | 20    | μΑ       |  |

|           | All other             |                                                                | $V_1 = 2.7 V$                   |                    | 20    | μΑ.      |  |

|           | D inputs <sup>‡</sup> |                                                                | <del>,,,,,,</del>               |                    | -0.1  | Τ.       |  |

| lu        |                       | $V_{CC} = 5.5 V$                                               | $V_{\parallel} = 0.4 \text{ V}$ |                    | -0.1  | mA       |  |

|           | All other             | V - 55V                                                        | V <sub>O</sub> = 2.25 V         | -30                | -112  | mA       |  |

| lo§       |                       | V <sub>CC</sub> = 5.5 V,                                       | Q outputs high                  |                    | 0 50  |          |  |

|           | 'ALS992               | $V_{CC} = 6.5 \text{ V, } \overline{\text{OERB}} \text{ high}$ | Q outputs low                   |                    | 0 80  | mA       |  |

|           |                       |                                                                | Q outputs disabled              |                    | 5 55  | 1        |  |

| lcc       | 'ALS993               | 'ALS993 . V <sub>CC</sub> = 5.5 V, <u>DÉRB</u> high            |                                 | ···                | 30 50 |          |  |

|           |                       |                                                                | outputs high                    |                    | 2 82  | mA.      |  |

|           |                       |                                                                |                                 |                    | 10 60 |          |  |

|           |                       |                                                                | Qoutputs disabled               |                    | ,0 00 | <u> </u> |  |

ALS and AS Circuits N

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25 °C. ‡ For I/O ports, the parameters I<sub>IH</sub> and I<sub>IL</sub> include the off-state output current. § The output conditions have been chosen to produce a current that closely approximates one half the true short-circuit output current, I<sub>OS</sub>.

T-46-07-12

'ALS992 switching characteristics (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | 0   | V <sub>CC</sub> = 5 V.<br>C <sub>L</sub> = 50 pF,<br>T <sub>A</sub> = 25°C |     |     | V <sub>CC</sub> = 4.5 V to 5.5 V,<br>C <sub>L</sub> = 50 pF,<br>T <sub>A</sub> = 0°C to 70°C |       |

|------------------|-----------------|----------------|-----|----------------------------------------------------------------------------|-----|-----|----------------------------------------------------------------------------------------------|-------|

|                  | . 1             |                | MIN | TYP                                                                        | MAX | MIN | MAX                                                                                          | ]     |

| <sup>t</sup> PLH | D               | a              |     | 7                                                                          | 10  | 3   | 14                                                                                           | ns    |

| tPHL.            | 1               | u              |     | 9                                                                          | 13  | 4   | 16                                                                                           | ] ''* |

| t <sub>PLH</sub> | С               | Q              |     | 12                                                                         | 15  | 6   | 20                                                                                           | T     |

| tPHL.            | 1               | u              |     | 15                                                                         | 19  | 8   | 25                                                                                           | ns    |

| <sup>t</sup> PHL | CLR             | Q              |     | 12                                                                         | 16  | 6   | 20                                                                                           | 1     |

| <sup>t</sup> PHL | CLN             | D              |     | 15                                                                         | 22  | 8   | 26                                                                                           | ns    |

| t <sub>en</sub>  | OERB            | D              |     | 11                                                                         | 17  | 4   | 21                                                                                           | T     |

| t <sub>dis</sub> |                 | U              |     | 6                                                                          | 11  | 2   | 14                                                                                           | ns    |

| ten              | ŌĒŌ             | ŌĒĠ Q          |     | 11                                                                         | 16  | 4   | 18                                                                                           | T     |

| t <sub>dis</sub> |                 | u              |     | 6                                                                          | 10  | 1   | 14                                                                                           | ns    |

### 'ALS993 switching characteristics (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | V <sub>CC</sub> = 5 V,<br>C <sub>L</sub> = 50 pF,<br>T <sub>A</sub> = 25 °C |     |     | V <sub>CC</sub> = 4.5 V to 5.5 V,<br>C <sub>L</sub> = 50 pF,<br>T <sub>A</sub> = 0°C to 70°C |     | UNIT |

|------------------|-----------------|----------------|-----------------------------------------------------------------------------|-----|-----|----------------------------------------------------------------------------------------------|-----|------|

|                  |                 |                | MIN                                                                         | TYP | MAX | MIN                                                                                          | MAX | 1    |

| tplH             | D               | δ              |                                                                             | 11  | 14  | 6                                                                                            | 20  | T    |

| tpHL             | 7 "             | ų.             |                                                                             | 8   | 11  | 4                                                                                            | 15  | ns   |

| <sup>t</sup> PLH | С               | ₫              |                                                                             | 16  | 20  | 9                                                                                            | 28  | 1    |

| tpHL .           | L1              | <u>u</u>       |                                                                             | 13  | 16  | 7                                                                                            | 22  | ns   |

| tPLH .           | CLR .           | ₫              |                                                                             | 10  | 13  | 5                                                                                            | 17  | T    |

| t <sub>PLH</sub> | Cru -           | D              |                                                                             | 15  | 22  | 8                                                                                            | 26  | ns   |

| t <sub>en</sub>  | OERB            | D              |                                                                             | 11  | 17  | 4                                                                                            | 21  |      |

| <sup>t</sup> dis | VERB            | U              |                                                                             | 6   | 11  | 2                                                                                            | 14  | ns   |

| ten              | ਨਵਰ             | ÖEĞ Ğ          |                                                                             | 11  | 16  | 4                                                                                            | 20  |      |

| <sup>t</sup> dis | UEU .           | u              |                                                                             | 6   | 10  | 1                                                                                            | 12  | ns   |

ten = tpzH or tpzL tdis = tpHz or tpLz

2-808

3075

C-04

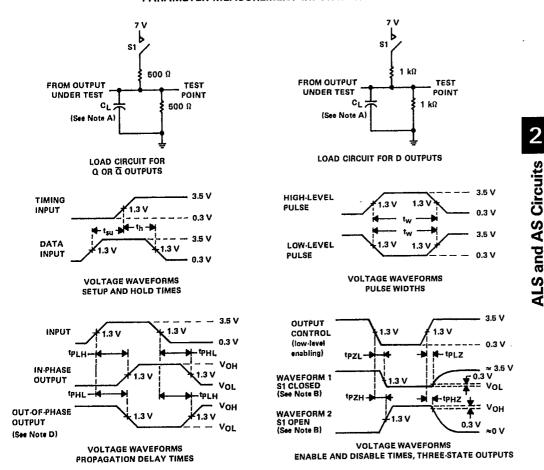

#### PARAMETER MEASUREMENT INFORMATION

T-46-07-12

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- C. All input pulses have the following characteristics: PRR  $\leq$  1 MHz,  $t_r = t_f = 2$  ns, duty cycle = 50%.

- D. When measuring propagation delay times of 3-state outputs, switch S1 is open.

FIGURE 1

TEXAS INSTRUMENTS